Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c716-20i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin                       | PIC16C712/716 |        | Pin        | Buffer    |                                                                                                               |

|---------------------------|---------------|--------|------------|-----------|---------------------------------------------------------------------------------------------------------------|

| Name                      | DIP, SOIC     | SSOP   | Туре       | Туре      | Description                                                                                                   |

|                           |               |        |            |           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT<br>RB0<br>INT     | 6             | 7      | I/O<br>I   | TTL<br>ST | Digital I/O<br>External Interrupt                                                                             |

| RB1/T1OSO/T1CKI<br>RB1    | 7             | 8      |            |           |                                                                                                               |

| T1OSO<br>T1CKI            |               |        | I/O<br>O   | TTL       | Digital I/O<br>Timer1 oscillator output. Connects to                                                          |

|                           |               | _      | I          | ST        | crystal in oscillator mode.<br>Timer1 external clock input.                                                   |

| RB2/T1OSI<br>RB2<br>T1OSI | 8             | 9      | I/O<br>I   | TTL<br>—  | Digital I/O<br>Timer1 oscillator input. Connects to<br>crystal in oscillator mode.                            |

| RB3/CCP1<br>RB3<br>CCP1   | 9             | 10     | I/O<br>I/O | TTL<br>ST | Digital I/O<br>Capture1 input, Compare1 output,<br>PWM1 output.                                               |

| RB4                       | 10            | 12     | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB5                       | 11            | 12     | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB6                       | 12            | 13     | I/O        | TTL       | Digital I/O<br>Interrupt on change pin.                                                                       |

| RB7                       | 13            | 14     | l<br>I/O   | ST<br>TTL | ICSP programming clock.<br>Digital I/O                                                                        |

|                           |               |        | I/O        | ST        | Interrupt on change pin.<br>ICSP programming data.                                                            |

| Vss                       | 5             | 5, 6   | Р          | —         | Ground reference for logic and I/O pins.                                                                      |

| Vdd                       | 14            | 15, 16 | Р          | _         | Positive supply for logic and I/O pins.                                                                       |

| TABLE 1-1: | PIC16C712/716 PINOUT DESCRIPTION (CONTINUE) | D) |

|------------|---------------------------------------------|----|

|            |                                             | -, |

**Legend:** TTL = TTL-compatible input CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up PU = Weak internal pull-up

No-P diode = No P-diode to VDD AN = Analog input or output

I = input O = output

P = Power L = LCD Driver

NOTES:

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0      | R/W-0       | R/W-0                                       | R/W-0       | R/W-0        | R/W-0        | R/W-x        |                                                                                                                                                 |

|-------------|------------|-------------|---------------------------------------------|-------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE       | TOIE        | INTE                                        | RBIE        | TOIF         | INTF         | RBIF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>-n = Value at POR Reset</li> </ul> |

| bit 7:      | 1 = Enabl  |             | pt Enable<br>nasked int<br>errupts          |             |              |              |              |                                                                                                                                                 |

| bit 6:      | 1 = Enabl  | les all unn | terrupt En<br>nasked pe<br>ipheral int      | ripheral in | terrupts     |              |              |                                                                                                                                                 |

| bit 5:      | 1 = Enabl  | les the TM  | ow Interruj<br>1R0 interru<br>/IR0 interru  | ıpt         | bit          |              |              |                                                                                                                                                 |

| bit 4:      |            | les the RE  | ternal Inte<br>80/INT exte<br>30/INT ext    | ernal inter | rupt         |              |              |                                                                                                                                                 |

| bit 3:      | 1 = Enabl  | les the RE  | nge Interr<br>8 port char<br>3 port cha     | ige interru | pt           |              |              |                                                                                                                                                 |

| bit 2:      | 1 = TMR0   | ) register  | ow Interrup<br>has overflo<br>did not ove   | owed (mus   | st be cleare | ed in softwa | are)         |                                                                                                                                                 |

| bit 1:      | 1 = The F  | RB0/INT e   | ernal Inter<br>xternal inte<br>xternal inte | errupt occ  | urred (mus   | t be cleare  | d in softwar | re)                                                                                                                                             |

| bit 0:      | 1 = At lea | st one of   |                                             | B4 pins cl  |              |              | e cleared in | software)                                                                                                                                       |

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

- Register file 05 contains the value 10h

- Register file 06 contains the value 0Ah

- · Load the value 05 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 06)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

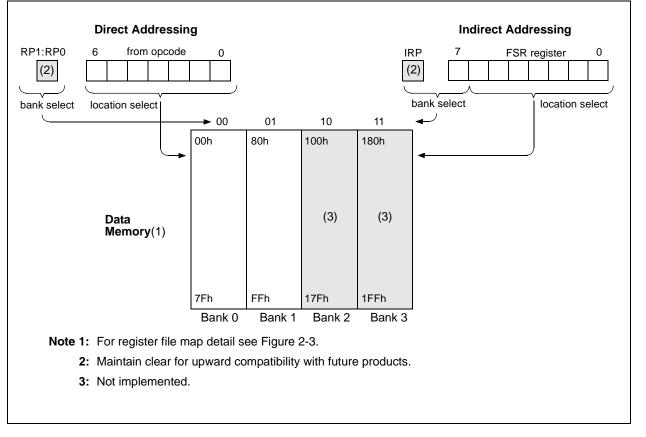

#### FIGURE 2-10: DIRECT/INDIRECT ADDRESSING

#### 2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | CLRF<br>INCF<br>BTFSS | FSR<br>INDF<br>FSR<br>FSR,4 | ;inc pointer<br>;all done?        |

|----------|-----------------------|-----------------------------|-----------------------------------|

| CONTINUE | GOTO<br>:             | NEXT                        | ;NO, clear next<br>;YES, continue |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-10. However, IRP is not used in the PIC16C712/716.

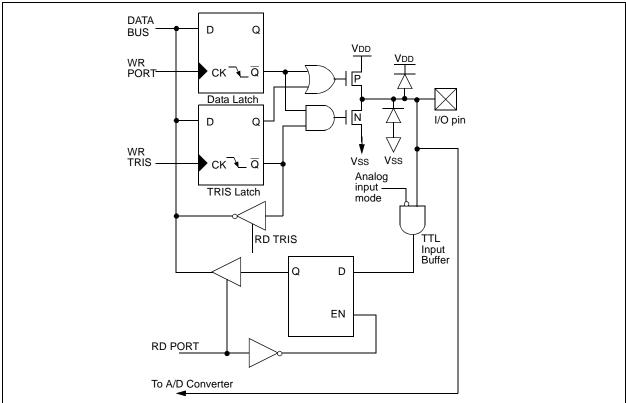

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0

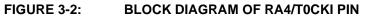

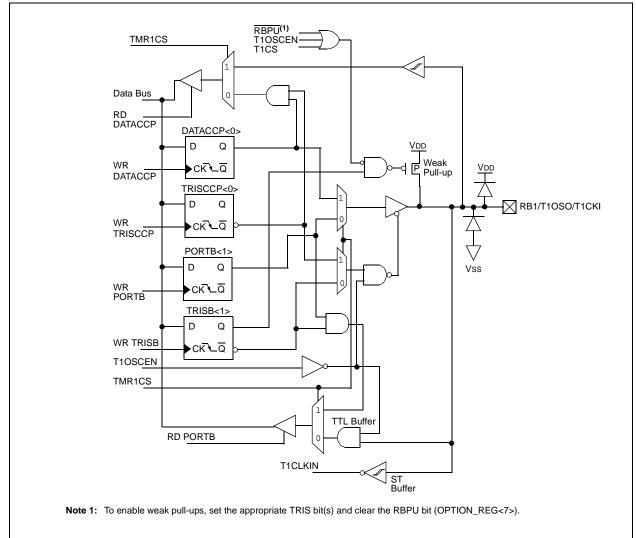

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

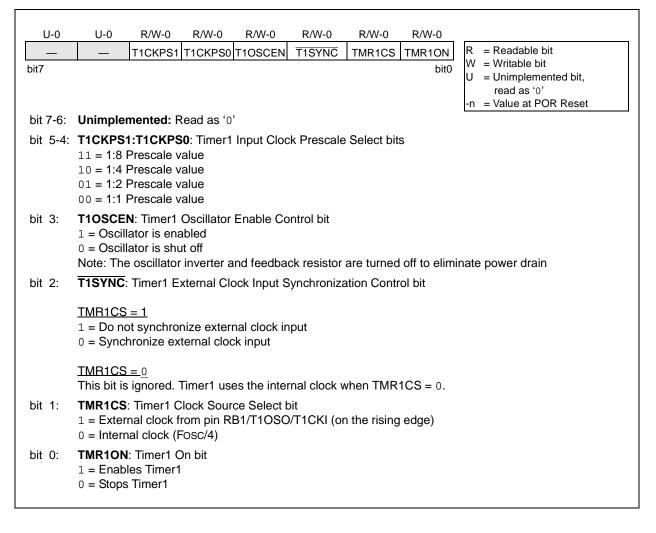

## 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- · Readable and writable (Both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### 5.1 Timer1 Operation

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB2/T1OSI and RB1/T1OSO/T1CKI pins become inputs. That is, the TRISB<2:1> value is ignored.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see Section 7.0 "Capture/Compare/PWM (CCP) Module(s)").

#### FIGURE 5-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

NOTES:

### 7.4 CCP1 Module and PORTB Operation

When the CCP module is disabled, PORTB<3> operates as a normal I/O pin. When the CCP module is enabled, PORTB<3> operation is affected. Multiplexing details of the CCP1 module are shown on PORTB<3>, refer to Figure 3.6.

Table 7-5 below shows the effects of the CCP module operation on PORTB<3>

| CCP1<br>Module<br>Mode | Control Bits                     | CCP1 Module Operation                                                                                                                                            | PORTB<3> Operation                                                                                                                           |  |  |  |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Off                    | CCP1CON =xx 0000                 | Off                                                                                                                                                              | PORTB<3> functions as normal I/O.                                                                                                            |  |  |  |

| Capture                | CCP1CON =xx 01xx<br>TRISCCP =1-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>an external circuit. The DCCP bit can<br>read the signal on the RB3/CCP1 pin. | PORTB<3> always reads '0' when<br>configured as input. If PORTB<3> is<br>configured as output, reading<br>PORTB<3> will read the data latch. |  |  |  |

|                        | CCP1CON =xx 01xx<br>TRISCCP =0-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>the DCCP bit. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.        | Writing to PORTB<3> will always store the result in the data latch, but it does not drive the RB3/CCP1 pin.                                  |  |  |  |

| Compare                | CCP1CON =xx 10xx<br>TRISCCP =0-x | The CCP1 module produces an output<br>on the RB3/CCP1 pin when a compare<br>event occurs. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.               |                                                                                                                                              |  |  |  |

| PWM                    | CCP1CON =xx 11xx<br>TRISCCP =0-x | The CCP1 module produces the PWM signal on the RB3/CCP1 pin. The DCCP bit can read the signal on the RB3/CCP1 pin.                                               |                                                                                                                                              |  |  |  |

TABLE 7-5: CCP1 MODULE AND PORTB OPERATION

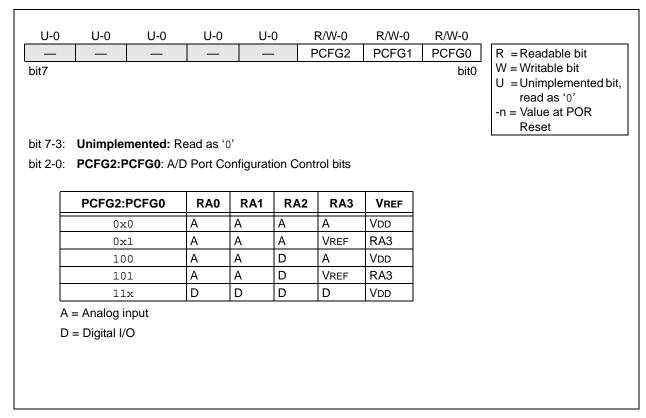

## 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has four inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. Additional information on the A/D module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The ADCON0 register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                     | R/W-0                                                    | R/W-0                | R/W-0      | R/W-0                             | U-0       | R/W-0        |                                                                                                          |

|---------------|-------------------------------------------|----------------------------------------------------------|----------------------|------------|-----------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------|

| ADCS1<br>bit7 | ADCS0                                     | CHS2                                                     | CHS1                 | CHS0       | GO/DONE                           |           | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset |

| bit 7-6:      | 00 = Fos<br>01 = Fos<br>10 = Fos          | c/2<br>c/8<br>c/32                                       |                      |            | s Select bits<br>al ADC RC os     | cillator) |              |                                                                                                          |

| bit 5-3:      |                                           | annel 0, (F<br>annel 1, (F<br>annel 2, (F<br>annel 3, (F | RA2/AN2)<br>RA3/AN3) | I Select b | its                               |           |              |                                                                                                          |

| bit 2:        | GO/DON                                    | E: A/D Co                                                | nversion S           | Status bit |                                   |           |              |                                                                                                          |

|               |                                           | onversion<br>conversio                                   | on not in            |            | this bit starts<br>(This bit is a |           |              | by hardware when the A/D                                                                                 |

| bit 1:        | Unimpler                                  | mented: F                                                | Read as '0           | ,          |                                   |           |              |                                                                                                          |

| bit 0:        | <b>ADON</b> : A<br>1 = A/D c<br>0 = A/D c | onverter r                                               | nodule is d          |            |                                   |           |              |                                                                                                          |

FIGURE 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

### FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

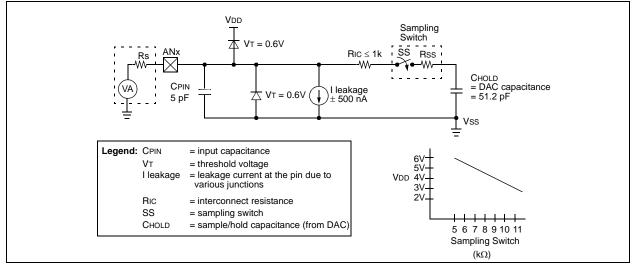

## 8.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the Charge Holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023). This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

#### FIGURE 8-4: ANALOG INPUT MODEL

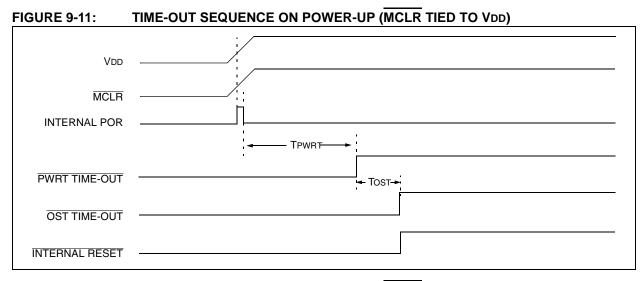

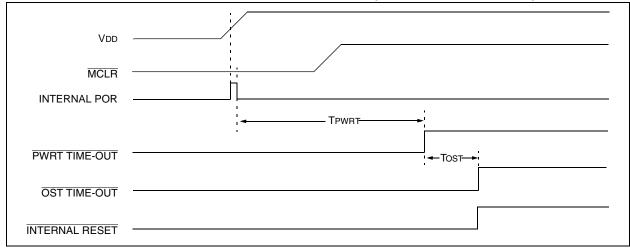

FIGURE 9-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

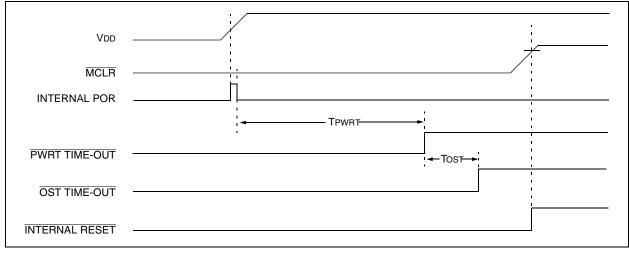

### FIGURE 9-13: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

### 11.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

## 11.12 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

### 12.1 DC Characteristics: PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712/716-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS    |                |                                                                                                                                                  | Standard Operating Conc<br>Operating temperature |                           |                      |                          | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                      |

|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------|----------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Sym.           | Characteristic                                                                                                                                   | Min.                                             | Тур†                      | Max.                 | Units                    | Conditions                                                                                                                                                                 |

| D001<br>D001A         | Vdd            | Supply Voltage                                                                                                                                   | 4.0<br>4.5<br>VBOR*                              | -                         | 5.5<br>5.5<br>5.5    | V<br>V<br>V              | XT, RC and LP osc mode<br>HS osc mode<br>BOR enabled <sup>(7)</sup>                                                                                                        |

| D002*                 | Vdr            | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                        | _                                                | 1.5                       |                      | V                        |                                                                                                                                                                            |

| D003                  | VPOR           | VDD Start Voltage to ensure inter-<br>nal Power-on Reset signal                                                                                  | —                                                | Vss                       | —                    | V                        | See section on Power-on Reset for details                                                                                                                                  |

| D004*<br>D004A*       | SVDD           | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                        | 0.05<br>TBD                                      | _                         | _                    | V/ms                     | PWRT enabled (PWRTE bit clear)<br>PWRT disabled (PWRTE bit set)<br>See section on Power-on Reset for details                                                               |

| D005                  | VBOR           | Brown-out Reset<br>voltage trip point                                                                                                            | 3.65                                             | —                         | 4.35                 | V                        | BODEN bit set                                                                                                                                                              |

| D010<br>D013          | IDD            | Supply Current <sup>(2,5)</sup>                                                                                                                  | _                                                | 0.8<br>4.0                | 2.5<br>8.0           | mA<br>mA                 | Fosc = 4 MHz, VDD = 4.0V<br>Fosc = 20 MHz, VDD = 4.0V                                                                                                                      |

| D020<br>D021<br>D021B | IPD            | Power-down Current <sup>(3,5)</sup>                                                                                                              | <br>                                             | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ     | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, 0°C to +70°C<br>VDD = 4.0V, WDT disabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D022*<br>D022A*       | ΔİWDT<br>ΔİBOR | Module Differential Current <sup>(6)</sup><br>Watchdog Timer<br>Brown-out Reset                                                                  |                                                  | 6.0<br>TBD                | 20<br>200            | μΑ<br>μΑ                 | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                                                                                                                      |

| 1A                    | Fosc           | LP Oscillator Operating Frequency<br>RC Oscillator Operating Frequency<br>XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0<br>0<br>0<br>0                                 | <br>                      | 200<br>4<br>4<br>20  | KHz<br>MHz<br>MHz<br>MHz | All temperatures<br>All temperatures<br>All temperatures<br>All temperatures                                                                                               |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD,

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD and Vss.

4: For RC Osc mode, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

7: This is the voltage where the device enters the Brown-out Reset. When BOR is enabled, the device will operate correctly to this trip point.

| DC CHA       | RACTE | RISTICS                                                | Operating<br>Operating<br>" <b>DC Char</b> | voltage | ature<br>-4<br>-4<br>VDD rang<br><b>tics: PIC1</b> | 0°C ≤<br>0°C ≤<br>0°C ≤<br>le as de<br>6C712/ |                                                                   |

|--------------|-------|--------------------------------------------------------|--------------------------------------------|---------|----------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------|

|              |       |                                                        | Extended<br>716-04 (C                      |         |                                                    |                                               | Characteristics: PIC16LC712/                                      |

| Param<br>No. | Sym.  | Characteristic                                         | Min.                                       | Typ†    | Max.                                               | Units                                         | Conditions                                                        |

| D080         | Vol   | Output Low Voltage<br>I/O ports                        |                                            | _       | 0.6                                                | V                                             | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                       |

|              |       |                                                        | —                                          | —       | 0.6                                                | V                                             | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |

| D083         |       | OSC2/CLKOUT<br>(RC Osc mode)                           | —                                          | —       | 0.6                                                | V                                             | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                       |

|              |       |                                                        | —                                          | —       | 0.6                                                | V                                             | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                      |

| D090         | Vон   | Output High Voltage<br>I/O ports (Note 3)              | Vdd-0.7                                    | _       | _                                                  | V                                             | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                      |

|              |       |                                                        | Vdd-0.7                                    | —       | _                                                  | V                                             | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                     |

| D092         |       | OSC2/CLKOUT (RC Osc<br>mode)                           | Vdd-0.7                                    | —       | _                                                  | V                                             | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                      |

|              |       |                                                        | Vdd-0.7                                    | —       | —                                                  | V                                             | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                     |

| D150*        | Vod   | Open-Drain High Voltage                                | _                                          | _       | 8.5                                                | V                                             | RA4 pin                                                           |

| D100         | Cosc2 | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin |                                            | _       | 15                                                 | pF                                            | In XT, HS and LP modes when external clock is used to drive OSC1. |

| D101         | Сю    | All I/O pins and OSC2 (in RC mode)                     | _                                          | —       | 50                                                 | pF                                            |                                                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC Oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

#### TABLE 12-8: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                       |                  | Min.     | Тур†     | Max. | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|------------------------------------------------------|------------------|----------|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

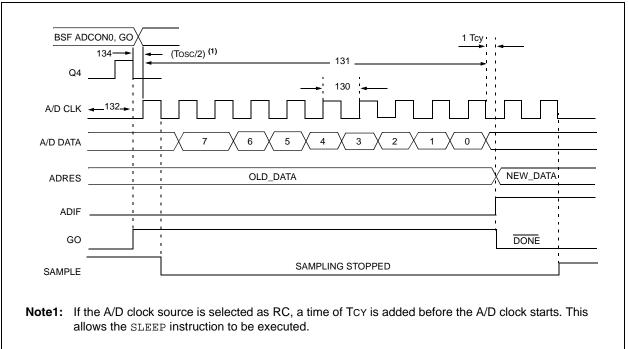

| 130          | TAD  | A/D clock period                                     | Standard         | 1.6      |          | _    | μS    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                  |

|              |      |                                                      | Extended (LC)    | 2.0      | —        | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                                      | Standard         | 2.0      | 4.0      | 6.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                                      | Extended (LC)    | 3.0      | 6.0      | 9.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (not including S/H time)<br>(Note 1) |                  | 11       | —        | 11   | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                                     |                  | (Note 2) | 20       | —    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                      |                  | 5*       | _        | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |                  | _        | Tosc/2 § | _    |       | If the A/D clock source is selected<br>as RC, a time of Tcy is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from conve                                 | rt Æ sample time | 1.5 §    | _        | _    | TAD   |                                                                                                                                                                                                                               |

: \* These parameters are characterized but not tested.

: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

: § This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 9.1 "Configuration Bits" for min. conditions.

## APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2/99 | This is a new data sheet. How-<br>ever, the devices described in this<br>data sheet are the upgrades to<br>the devices found in the<br><i>PIC16C6X Data Sheet</i> ,<br>DS30234, and the <i>PIC16C7X</i><br><i>Data Sheet</i> , DS30390. |

| В       | 9/05 | Removed Preliminary Status.                                                                                                                                                                                                             |

| С       | 1/13 | Added a note to each package outline drawing.                                                                                                                                                                                           |

## APPENDIX B: CONVERSION CONSIDERATIONS

There are no previous versions of this device.

## APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different Reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from Sleep through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight-bit register.

- 15. "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON STATUS register is added with a Poweron Reset Status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by Configuration Word bit BODEN. Brown-out Reset ensures the device is placed in a Reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16CXXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change Reset vector to 0000h.

## PIC16C712/716 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br> <br>Device Fi | <u>-XX X</u><br>     <br>requency Temperatur<br>Range Range                                                                                          | /XX<br> <br>e Package         | XXX<br> <br>Pattern | Í F<br>P  | •<br>PIC16C716 – 04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>attern #301.                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                    | PIC16C712 <sup>(1)</sup> , PIC16C7<br>PIC16LC712 <sup>(1)</sup> , PIC16L<br>PIC16C716 <sup>(1)</sup> , PIC16C7<br>PIC16LC716 <sup>(1)</sup> , PIC16L | C712T <sup>(2)</sup> :VDD rar | nge 2.5V to 5.5V    | р<br>с) F | PIC16LC712 – 04I/SO = Industrial temp., SOIC<br>vackage, 200 kHz, Extended VDD limits.<br>PIC16C712 – 20I/P = Industrial temp., PDIP<br>vackage, 20MHz, normal VDD limits. |

| Frequency Range:           | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                            |                               |                     | Note 1    | : C = CMOS<br>LC = Low Power CMOS<br>I: T = in tape and reel – SOIC, SSOP<br>packages only.                                                                                |

| Temperature<br>Range:      | blank = $0^{\circ}$ C to<br>I = -40^{\circ}C to +1<br>E = -40^{\circ}C to +12                                                                        |                               | I)                  |           | LC extended temperature device is not<br>offered.     LC is not offered at 20 MHz                                                                                          |

| Package:                   | JW = Windowed<br>SO = SOIC<br>P = PDIP<br>SS = SSOP                                                                                                  | CERDIP                        |                     |           |                                                                                                                                                                            |

| Pattern:                   | QTP, SQTP, Code or Sp<br>(blank otherwise)                                                                                                           | ecial Requiremer              | nts                 |           |                                                                                                                                                                            |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)