Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | <u> </u>                                                                     |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc712t-04i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C712/716

NOTES:

# 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the  $PIC^{\mbox{\tiny R}}$  Mid-Range Reference Manual, (DS33023).

## 2.1 Program Memory Organization

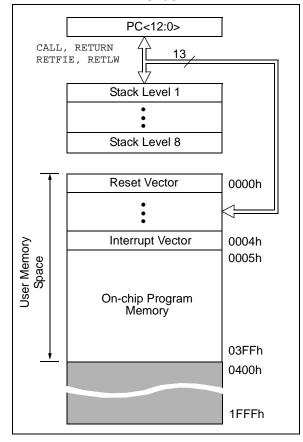

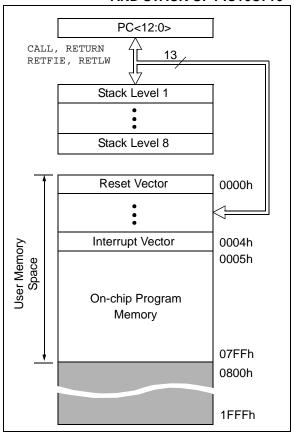

The PIC16C712/716 has a 13-bit Program Counter (PC) capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

#### FIGURE 2-2: PROGRAM MEMORY MAP AND STACK OF PIC16C716

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

## FIGURE 2-5: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1<br>RBPU | R/W-1                                                                                         | R/W-1<br>T0CS | R/W-1<br>T0SE | R/W-1<br>PSA | R/W-1<br>PS2           | R/W-1<br>PS1 | R/W-1<br>PS0 | R = Readable bit |  |  |

|---------------|-----------------------------------------------------------------------------------------------|---------------|---------------|--------------|------------------------|--------------|--------------|------------------|--|--|

| it7           | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR Reset |               |               |              |                        |              |              |                  |  |  |

| oit 7:        | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE                                                    | 3 pull-ups    | are disal     | oled         | lividual port          | latch valu   | es           |                  |  |  |

| oit 6:        | <b>INTEDG</b> : I<br>1 = Interru<br>0 = Interru                                               | pt on rising  | g edge of     | f RB0/INT    |                        |              |              |                  |  |  |

| oit 5:        | <b>TOCS</b> : TMI<br>1 = Transit<br>0 = Interna                                               | ion on RA     | 4/T0CKI       | pin          | (OUT)                  |              |              |                  |  |  |

| bit 4:        |                                                                                               | ent on hig    | h-to-low      | transition   | on RA4/T0<br>on RA4/T0 |              |              |                  |  |  |

| bit 3:        | <b>PSA</b> : Pres<br>1 = Presca<br>0 = Presca                                                 | ler is assi   | gned to t     | he WDT       | module                 |              |              |                  |  |  |

| bit 2-0:      | <b>PS2:PS0</b> :                                                                              | Prescaler     | Rate Sel      | ect bits     |                        |              |              |                  |  |  |

|               | Bit Value                                                                                     | TMR0 Ra       | te WD         | Γ Rate       |                        |              |              |                  |  |  |

|               | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                        |               |               |              |                        |              |              |                  |  |  |

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                               | R/W-0                                      | R/W-0       | R/W-0    | R/W-0 | R/W-x |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|----------|-------|-------|--|--|

| GIE<br>bit7 | PEIE     TOIE     INTE     RBIE     TOIF     INTF     RBIF       bit0     F     W     Writable bit       U     Unimplemented bit, read as '0'       -n     Value at POR Reset |                                                                                                                                                                                                                                                                     |                                            |             |          |       |       |  |  |

| bit 7:      | 1 = Enabl                                                                                                                                                                     |                                                                                                                                                                                                                                                                     | pt Enable<br>nasked int<br>errupts         |             |          |       |       |  |  |

| bit 6:      | 1 = Enabl                                                                                                                                                                     | les all unn                                                                                                                                                                                                                                                         | terrupt En<br>nasked pe<br>ipheral int     | ripheral in | terrupts |       |       |  |  |

| bit 5:      | 1 = Enabl                                                                                                                                                                     | les the TM                                                                                                                                                                                                                                                          | ow Interruj<br>1R0 interru<br>/IR0 interru | ıpt         | bit      |       |       |  |  |

| bit 4:      | IINTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                     |                                                                                                                                                                                                                                                                     |                                            |             |          |       |       |  |  |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                    |                                                                                                                                                                                                                                                                     |                                            |             |          |       |       |  |  |

| bit 2:      | <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                        |                                                                                                                                                                                                                                                                     |                                            |             |          |       |       |  |  |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur    |                                                                                                                                                                                                                                                                     |                                            |             |          |       |       |  |  |

| bit 0:      | 1 = At lea                                                                                                                                                                    | <ul> <li>The RB0/INT external interrupt did not occur</li> <li><b>RBIF</b>: RB Port Change Interrupt Flag bit</li> <li>At least one of the RB7:RB4 pins changed state (must be cleared in software)</li> <li>None of the RB7:RB4 pins have changed state</li> </ul> |                                            |             |          |       |       |  |  |

# 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

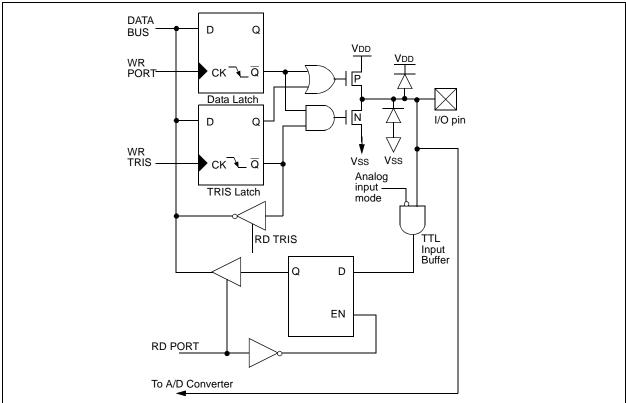

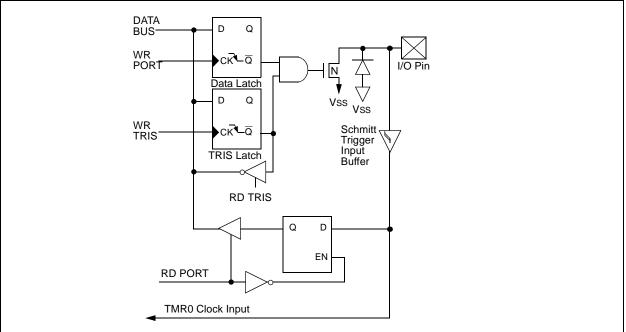

## 3.1 PORTA and the TRISA Register

PORTA is a 5-bit wide bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input, (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified, and then written to the port data latch. Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

PORTA pins, RA3:0, are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are     |

|-------|-----------------------------------------|

|       | configured as analog inputs and read as |

|       | ʻ0'.                                    |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, RPO | ;                       |

|-------|-------------|-------------------------|

| CLRF  | PORTA       | ; Initialize PORTA by   |

|       |             | ; clearing output       |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | OxEF        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISA       | ; Set RA<3:0> as inputs |

|       |             | ; RA<4> as outputs      |

| BCF   | STATUS, RPO | ; Return to Bank 0      |

# PIC16C712/716

## FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0

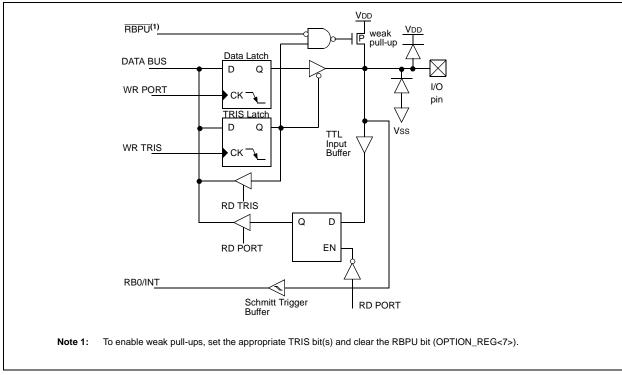

#### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input, (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output, (i.e., put the contents of the output latch on the selected pin).

| BCF   | STATUS, RPO | i                       |

|-------|-------------|-------------------------|

| CLRF  | PORTB       | ; Initialize PORTB by   |

|       |             | ; clearing output       |

|       |             | ; data latches          |

| BSF   | STATUS, RPO | ; Select Bank 1         |

| MOVLW | 0xCF        | ; Value used to         |

|       |             | ; initialize data       |

|       |             | ; direction             |

| MOVWF | TRISB       | ; Set RB<3:0> as inputs |

|       |             | ; RB<5:4> as outputs    |

|       |             | ; RB<7:6> as inputs     |

|       |             |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 3-3: BLOCK DIAGRAM OF RB0 PIN

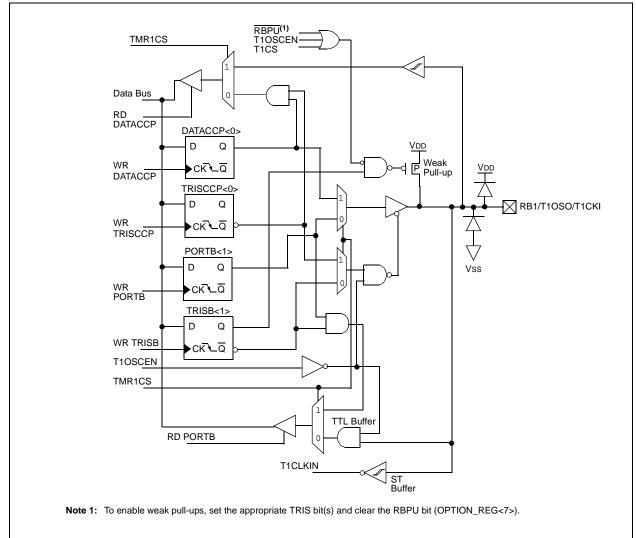

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

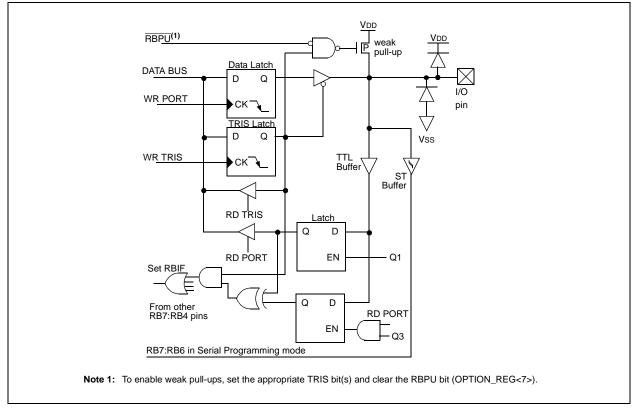

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

#### FIGURE 3-7: BLOCK DIAGRAM OF RB7:RB4 PINS

#### TABLE 3-3: PORTB FUNCTIONS

| Name                | Bit#  | Buffer                | Function                                                                                                                                                              |

|---------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT             | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                                            |

| RB1/T1OS0/<br>T1CKI | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator output, or Timer1 clock input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.          |

| RB2/T1OSI           | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.                                  |

| RB3/CCP1            | bit 3 | TTL/ST <sup>(1)</sup> | Input/output pin or Capture 1 input, or Compare 1 output, or PWM1 output.<br>Internal software programmable weak pull-up. See CCP1 section for<br>detailed operation. |

| RB4                 | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB5                 | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB6                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                   |

| RB7                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                    |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or peripheral input.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

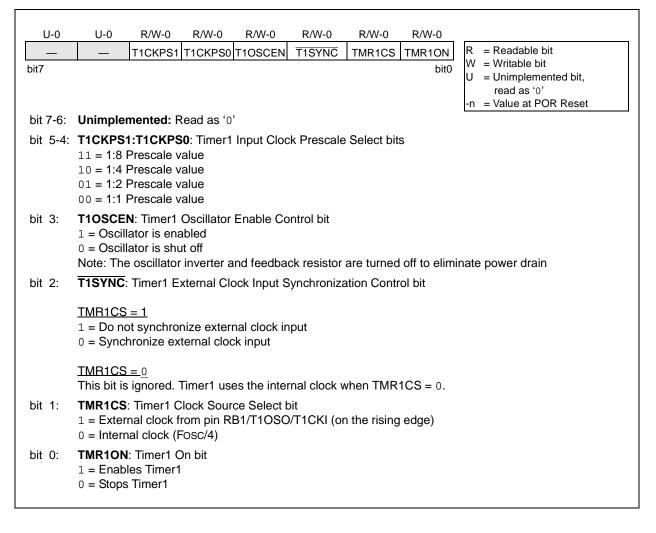

## 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- · Readable and writable (Both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### 5.1 Timer1 Operation

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB2/T1OSI and RB1/T1OSO/T1CKI pins become inputs. That is, the TRISB<2:1> value is ignored.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see Section 7.0 "Capture/Compare/PWM (CCP) Module(s)").

#### FIGURE 5-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

NOTES:

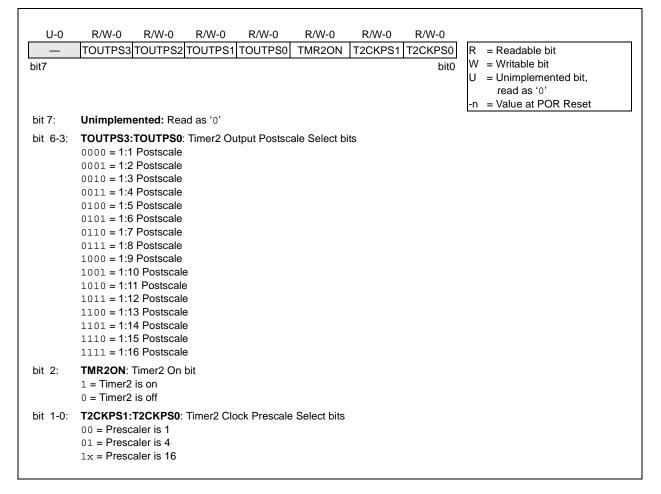

# 6.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

Timer2 has a control register, shown in Figure 6-1. Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

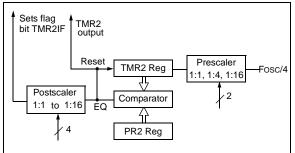

Figure 6-2 is a simplified block diagram of the Timer2 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

## FIGURE 6-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

#### FIGURE 6-2: TIMER2 BLOCK DIAGRAM

#### 8.4 A/D Conversions

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/ DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4   | Bit 3     | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|---------|-----------|---------------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  |          | _           | (1)   | RA4     | RA3       | RA2           | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE    | RBIE      | TOIF          | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | —       | —         | CCP1IF        | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ult Registe | er    |         |           |               |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1    | CHS0      | GO/DONE       | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA I | Data Dire | ction Registe | r      |        | 1 1111                  | 1 1111                    |

| 8Ch     | PIE1   | _        | ADIE        | _     | —       | —         | CCP1IE        | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     | _       | _         | PCFG2         | PCFG1  | PCFG0  | 000                     | 000                       |

TABLE 8-2: SUMMARY OF A/D REGISTERS

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** Reserved bits: Do Not Use.

DS41106C-page 50

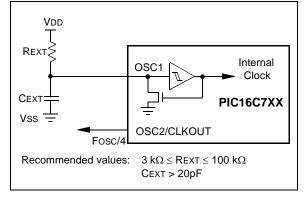

## 9.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit-to-unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 9-4 shows how the R/C combination is connected to the PIC16CXXX.

#### 9.3 Reset

The PIC16CXXX differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- WDT Reset (during normal operation)

- WDT Wake-up (during Sleep)

- Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during Sleep and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-6 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset circuit is shown in Figure 9-6.

The PIC microcontrollers have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

$\underline{\text{It should}}$  be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

## 9.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (to a level of 1.5V-2.1V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (parameter D004). For a slow rise time, see Figure 9-5.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

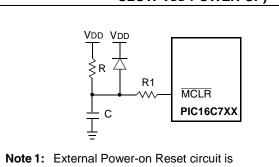

## FIGURE 9-5:

#### RESET CIRCUIT (FOR SLOW VDD POWER-UP)

EXTERNAL POWER-ON

- Def 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- **2:** R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 9.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33), on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

## 9.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

## 9.7 Brown-Out Reset (BOR)

The PIC16C712/716 members have on-chip Brownout Reset circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V, refer to VBOR parameter D005(VBOR) for a time greater than parameter (TBOR) in Table 12-6. The brown-out situation will reset the chip. A Reset is not guaranteed to occur if VDD falls below 4.0V for less than parameter (TBOR).

On any Reset (Power-on, Brown-out, Watchdog, etc.) the chip will remain in Reset until VDD rises above VBOR. The Power-up Timer will now be invoked and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

For operations where the desired brown-out voltage is other than 4V, an external brown-out circuit must be used. Figure 9-8, 9-9 and 9-10 show examples of external brown-out protection circuits.

## 11.2 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for all PIC MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 11.3 MPLAB C18 and MPLAB C30 C Compilers

The MPLAB C18 and MPLAB C30 Code Development Systems are complete ANSI C compilers for Microchip's PIC18 family of microcontrollers and dsPIC30F family of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 11.5 MPLAB ASM30 Assembler, Linker and Librarian

MPLAB ASM30 Assembler produces relocatable machine code from symbolic assembly language for dsPIC30F devices. MPLAB C30 C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire dsPIC30F instruction set

- · Support for fixed-point and floating-point data

- · Command line interface

- Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

## 11.6 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, as well as internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C18 and MPLAB C30 C Compilers, and the MPASM and MPLAB ASM30 Assemblers. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent, economical software development tool.

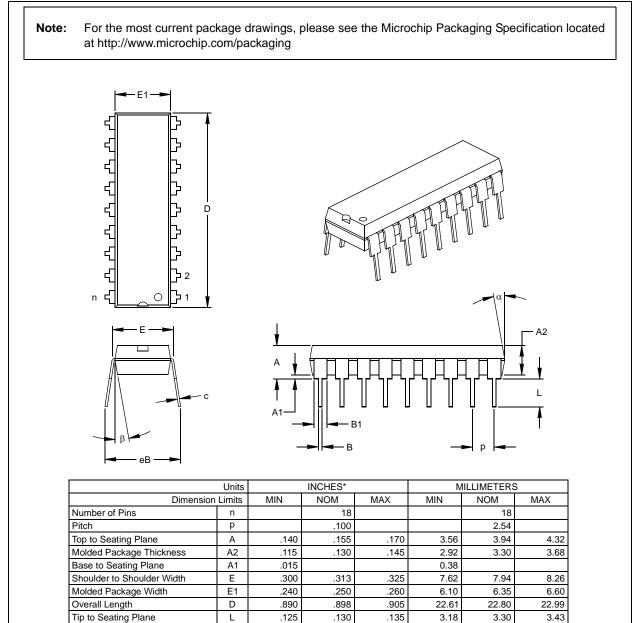

#### 13.2 Package Details

The following sections give the technical details of the packages.

### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

.008

.045

.014

.310

5

5

.012

.058

.018

.370

10

10

.015

.070

.022

.430

15

15

0.20

1.14

0.36

7.87

5

5

0.29

1.46

0.46

9.40

10

10

0.38

1.78

0.56

10.92

15

15

С

B1

В

eВ

α

β

δ

JEDEC Equivalent: MS-001

Drawing No. C04-007

Lead Thickness

Upper Lead Width

Lower Lead Width

**Overall Row Spacing**

Mold Draft Angle Top

Mold Draft Angle Bottom

\* Controlling Parameter § Significant Characteristic

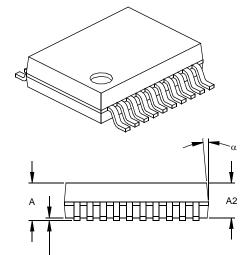

## 20-Lead Plastic Shrink Small Outline (SS) – 209 mil, 5.30 mm (SSOP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |           | INCHES* |      | MILLIMETERS |      |        |        |

|--------------------------|-----------|---------|------|-------------|------|--------|--------|

| Dimensio                 | on Limits | MIN     | NOM  | MAX         | MIN  | NOM    | MAX    |

| Number of Pins           | n         |         | 20   |             |      | 20     |        |

| Pitch                    | р         |         | .026 |             |      | 0.65   |        |

| Overall Height           | А         | .068    | .073 | .078        | 1.73 | 1.85   | 1.98   |

| Molded Package Thickness | A2        | .064    | .068 | .072        | 1.63 | 1.73   | 1.83   |

| Standoff §               | A1        | .002    | .006 | .010        | 0.05 | 0.15   | 0.25   |

| Overall Width            | Е         | .299    | .309 | .322        | 7.59 | 7.85   | 8.18   |

| Molded Package Width     | E1        | .201    | .207 | .212        | 5.11 | 5.25   | 5.38   |

| Overall Length           | D         | .278    | .284 | .289        | 7.06 | 7.20   | 7.34   |

| Foot Length              | L         | .022    | .030 | .037        | 0.56 | 0.75   | 0.94   |

| Lead Thickness           | С         | .004    | .007 | .010        | 0.10 | 0.18   | 0.25   |

| Foot Angle               | φ         | 0       | 4    | 8           | 0.00 | 101.60 | 203.20 |

| Lead Width               | В         | .010    | .013 | .015        | 0.25 | 0.32   | 0.38   |

| Mold Draft Angle Top     | α         | 0       | 5    | 10          | 0    | 5      | 10     |

| Mold Draft Angle Bottom  | β         | 0       | 5    | 10          | 0    | 5      | 10     |

| * Controlling Decomptor  |           |         |      |             |      |        |        |

A1

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

# APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 2/99 | This is a new data sheet. How-<br>ever, the devices described in this<br>data sheet are the upgrades to<br>the devices found in the<br><i>PIC16C6X Data Sheet</i> ,<br>DS30234, and the <i>PIC16C7X</i><br><i>Data Sheet</i> , DS30390. |

| В       | 9/05 | Removed Preliminary Status.                                                                                                                                                                                                             |

| С       | 1/13 | Added a note to each package outline drawing.                                                                                                                                                                                           |

# APPENDIX B: CONVERSION CONSIDERATIONS

There are no previous versions of this device.

# APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different Reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from Sleep through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight-bit register.

- 15. "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON STATUS register is added with a Poweron Reset Status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by Configuration Word bit BODEN. Brown-out Reset ensures the device is placed in a Reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16CXXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change Reset vector to 0000h.

## PIC16C712/716 PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br> <br>Device Fi | <u>-XX X</u><br>     <br>requency Temperatur<br>Range Range                                                                                          | /XX<br> <br>e Package         | XXX<br> <br>Pattern | Í F<br>P  | •<br>PIC16C716 – 04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>attern #301.                                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                    | PIC16C712 <sup>(1)</sup> , PIC16C7<br>PIC16LC712 <sup>(1)</sup> , PIC16L<br>PIC16C716 <sup>(1)</sup> , PIC16C7<br>PIC16LC716 <sup>(1)</sup> , PIC16L | C712T <sup>(2)</sup> :VDD rar | nge 2.5V to 5.5V    | р<br>с) F | PIC16LC712 – 04I/SO = Industrial temp., SOIC<br>vackage, 200 kHz, Extended VDD limits.<br>PIC16C712 – 20I/P = Industrial temp., PDIP<br>vackage, 20MHz, normal VDD limits. |

| Frequency Range:           | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                            |                               |                     | Note 1    | : C = CMOS<br>LC = Low Power CMOS<br>I: T = in tape and reel – SOIC, SSOP<br>packages only.                                                                                |

| Temperature<br>Range:      | blank = $0^{\circ}$ C to<br>I = -40^{\circ}C to +1<br>E = -40^{\circ}C to +12                                                                        |                               | I)                  |           | LC extended temperature device is not<br>offered.     LC is not offered at 20 MHz                                                                                          |

| Package:                   | JW = Windowed<br>SO = SOIC<br>P = PDIP<br>SS = SSOP                                                                                                  | CERDIP                        |                     |           |                                                                                                                                                                            |

| Pattern:                   | QTP, SQTP, Code or Sp<br>(blank otherwise)                                                                                                           | ecial Requiremer              | nts                 |           |                                                                                                                                                                            |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)