Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 4x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc712t-04i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PIC<sup>®</sup> microcontroller devices. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the  $PIC^{\mbox{\tiny R}}$  Mid-Range Reference Manual, (DS33023).

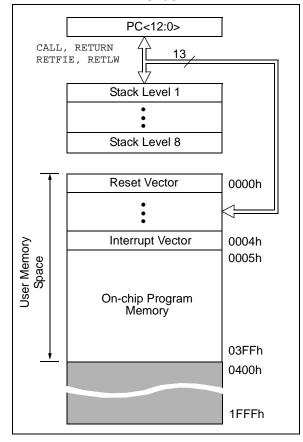

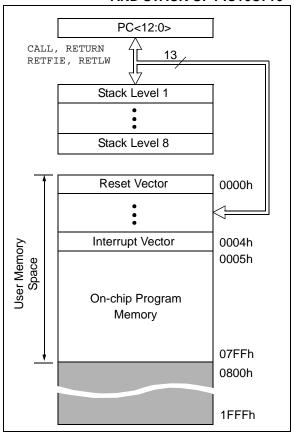

### 2.1 Program Memory Organization

The PIC16C712/716 has a 13-bit Program Counter (PC) capable of addressing an 8K x 14 program memory space. PIC16C712 has 1K x 14 words of program memory and PIC16C716 has 2K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The Reset vector is at 0000h and the interrupt vector is at 0004h.

### FIGURE 2-2: PROGRAM MEMORY MAP AND STACK OF PIC16C716

### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 2-6: INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0       | R/W-0      | R/W-0       | R/W-0                                       | R/W-0       | R/W-0        | R/W-0        | R/W-x        |                                                                                                                                                 |

|-------------|------------|-------------|---------------------------------------------|-------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE       | TOIE        | INTE                                        | RBIE        | TOIF         | INTF         | RBIF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>-n = Value at POR Reset</li> </ul> |

| bit 7:      | 1 = Enabl  |             | pt Enable<br>nasked int<br>errupts          |             |              |              |              |                                                                                                                                                 |

| bit 6:      | 1 = Enabl  | les all unn | terrupt En<br>nasked pe<br>ipheral int      | ripheral in | terrupts     |              |              |                                                                                                                                                 |

| bit 5:      | 1 = Enabl  | les the TM  | ow Interruj<br>1R0 interru<br>/IR0 interru  | ıpt         | bit          |              |              |                                                                                                                                                 |

| bit 4:      |            | les the RE  | ternal Inte<br>80/INT exte<br>30/INT ext    | ernal inter | rupt         |              |              |                                                                                                                                                 |

| bit 3:      | 1 = Enabl  | les the RE  | nge Interr<br>8 port char<br>3 port cha     | ige interru | pt           |              |              |                                                                                                                                                 |

| bit 2:      | 1 = TMR0   | ) register  | ow Interrup<br>has overflo<br>did not ove   | owed (mus   | st be cleare | ed in softwa | are)         |                                                                                                                                                 |

| bit 1:      | 1 = The F  | RB0/INT e   | ernal Inter<br>xternal inte<br>xternal inte | errupt occ  | urred (mus   | t be cleare  | d in softwar | re)                                                                                                                                             |

| bit 0:      | 1 = At lea | st one of   |                                             | B4 pins cl  |              |              | e cleared in | software)                                                                                                                                       |

# PIC16C712/716

### 2.2.2.4 PIE1 Register

This register contains the individual enable bits for the peripheral interrupts.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### FIGURE 2-7: PIE1 REGISTER (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                             | U-0       | U-0        | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                  |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|--------|--------|--------|------------------|--|--|--|--|--|--|

|          | ADIE                                                                                                                              | —         |            | —          | CCP1IE | TMR2IE | TMR1IE | R = Readable bit |  |  |  |  |  |  |

| bit7     | U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset                                                                  |           |            |            |        |        |        |                  |  |  |  |  |  |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                        |           |            |            |        |        |        |                  |  |  |  |  |  |  |

| bit 6:   |                                                                                                                                   |           |            |            |        |        |        |                  |  |  |  |  |  |  |

| bit 5-3: | Unimplemented: Read as '0'                                                                                                        |           |            |            |        |        |        |                  |  |  |  |  |  |  |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enabl<br>0 = Disab                                                                                       | es the CC | P1 interru | pt         |        |        |        |                  |  |  |  |  |  |  |

| bit 1:   | TMR2IE:<br>1 = Enabl<br>0 = Disab                                                                                                 | es the TM | R2 to PR   | 2 match in | •      |        |        |                  |  |  |  |  |  |  |

| bit 0:   | TMR1IE: TMR1 Overflow Interrupt Enable bit<br>1 = Enables the TMR1 overflow interrupt<br>0 = Disables the TMR1 overflow interrupt |           |            |            |        |        |        |                  |  |  |  |  |  |  |

|          |                                                                                                                                   |           |            |            |        |        |        |                  |  |  |  |  |  |  |

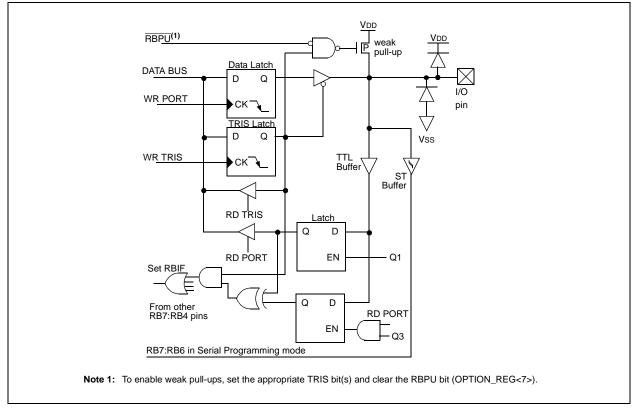

### FIGURE 3-7: BLOCK DIAGRAM OF RB7:RB4 PINS

### TABLE 3-3: PORTB FUNCTIONS

| Name                | Bit#  | Buffer                | Function                                                                                                                                                              |

|---------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT             | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                                            |

| RB1/T1OS0/<br>T1CKI | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator output, or Timer1 clock input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.          |

| RB2/T1OSI           | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.                                  |

| RB3/CCP1            | bit 3 | TTL/ST <sup>(1)</sup> | Input/output pin or Capture 1 input, or Compare 1 output, or PWM1 output.<br>Internal software programmable weak pull-up. See CCP1 section for<br>detailed operation. |

| RB4                 | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB5                 | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                             |

| RB6                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                                   |

| RB7                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                                    |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or peripheral input.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

# PIC16C712/716

NOTES:

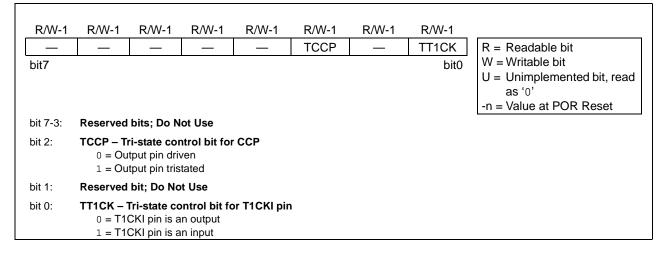

## 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' -n = Value at POR Reset bit 7-6: Unimplemented: Read as '0' bit 5-4: DC1B1:DC1B0: PWM Least Significant bits Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits 0000 = Capture/Compare/PWM off (resets CCP1 module) 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, set output on match (CCP1IF bit is set) 1001 = Compare mode, clear output on match (CCP1IF bit is set) 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected) 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled)) 11xx = PWM mode

### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

# TABLE 7-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

|          |                |

## 8.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) Converter module has four inputs.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator. Additional information on the A/D module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off, and any conversion is aborted.

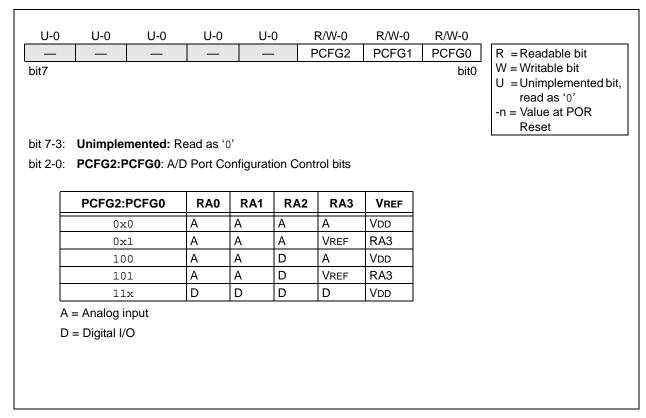

The ADCON0 register, shown in Figure 8-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 8-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                               | R/W-0                  | R/W-0       | R/W-0      | R/W-0                             | U-0       | R/W-0        |                                                                                                          |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------------------------------|-----------|--------------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADCS1<br>bit7 | ADCS0                                                                                                                                                                                                                                                               | CHS2                   | CHS1        | CHS0       | GO/DONE                           |           | ADON<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR Reset |  |  |  |  |

| bit 7-6:      | 00 = Fos<br>01 = Fos<br>10 = Fos                                                                                                                                                                                                                                    | c/2<br>c/8<br>c/32     |             |            | s Select bits<br>al ADC RC os     | cillator) |              |                                                                                                          |  |  |  |  |

| bit 5-3:      | 11 = FRC (clock derived from the internal ADC RC oscillator)<br><b>CHS2:CHS0</b> : Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>1xx = reserved, do not use |                        |             |            |                                   |           |              |                                                                                                          |  |  |  |  |

| bit 2:        | GO/DON                                                                                                                                                                                                                                                              | E: A/D Co              | nversion S  | Status bit |                                   |           |              |                                                                                                          |  |  |  |  |

|               |                                                                                                                                                                                                                                                                     | onversion<br>conversio | on not in   |            | this bit starts<br>(This bit is a |           |              | by hardware when the A/D                                                                                 |  |  |  |  |

| bit 1:        | Unimpler                                                                                                                                                                                                                                                            | mented: F              | Read as '0  | ,          |                                   |           |              |                                                                                                          |  |  |  |  |

| bit 0:        | <b>ADON</b> : A<br>1 = A/D c<br>0 = A/D c                                                                                                                                                                                                                           | onverter r             | nodule is d |            |                                   |           |              |                                                                                                          |  |  |  |  |

FIGURE 8-1: ADCON0 REGISTER (ADDRESS 1Fh)

# PIC16C712/716

### FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

### 8.4 A/D Conversions

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/ DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4   | Bit 3     | Bit 2         | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|---------|-----------|---------------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  |          | _           | (1)   | RA4     | RA3       | RA2           | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE    | RBIE      | TOIF          | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | —       | —         | CCP1IF        | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ult Registe | er    |         |           |               |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1    | CHS0      | GO/DONE       | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA I | Data Dire | ction Registe |        | 1 1111 | 1 1111                  |                           |

| 8Ch     | PIE1   | _        | ADIE        | _     | —       | —         | CCP1IE        | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     | _       | _         | PCFG2         | PCFG1  | PCFG0  | 000                     | 000                       |

TABLE 8-2: SUMMARY OF A/D REGISTERS

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** Reserved bits: Do Not Use.

DS41106C-page 50

### FIGURE 9-1: CONFIGURATION WORD

|        |                                                                                                                  |        |         |          |          |         |                |        |         |           |           |       | •           |                        |

|--------|------------------------------------------------------------------------------------------------------------------|--------|---------|----------|----------|---------|----------------|--------|---------|-----------|-----------|-------|-------------|------------------------|

| CP1    | CPO                                                                                                              | CP1    | CP0     | CP1      | CP0      | —       | BODEN          | CP1    | CP0     | PWRTE     | WDTE      | FOSC1 | FOSC0       | Register:CONFIG        |

| bit13  |                                                                                                                  |        |         |          |          |         |                |        |         |           |           |       | bit0        | Address2007h           |

| bit 12 | 0 0 5                                                                                                            |        |         | Codo     | Droto    | otion k | oite (2)       |        |         |           |           |       |             |                        |

| DILTO  | bit 13-8, 5-4: CP1:CP0: Code Protection bits <sup>(2)</sup><br>Code Protection for 2K Program memory (PIC16C716) |        |         |          |          |         |                |        |         |           |           |       |             |                        |

|        | 11 = Programming code protection off                                                                             |        |         |          |          |         |                |        |         |           |           |       |             |                        |

|        | 10 = 0400h-07FFh code protected                                                                                  |        |         |          |          |         |                |        |         |           |           |       |             |                        |

|        | 01 = 0200h-07FFh code protected                                                                                  |        |         |          |          |         |                |        |         |           |           |       |             |                        |

|        | 01 = 02001-07FFh code protected<br>00 = 0000h-07FFh code protected                                               |        |         |          |          |         |                |        |         |           |           |       |             |                        |

| bit 13 | 3-8, 5                                                                                                           | -4:    |         |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | Coc    | le Prot | ection   | for 1k   | (Prog   | ram mem        | ory bi | ts (PIC | C16C712)  |           |       |             |                        |

|        |                                                                                                                  | 11:    | = Prog  | rammi    | ing coo  | de pro  | tection of     | f      |         |           |           |       |             |                        |

|        |                                                                                                                  |        | •       |          | •        | •       | tection of     | f      |         |           |           |       |             |                        |

|        |                                                                                                                  |        | = 0200  |          |          | •       |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 00 :   | = 0000  | h-03F    | Fh coo   | de-pro  | tected         |        |         |           |           |       |             |                        |

| bit 7  |                                                                                                                  | 11     |         |          | J. D     | -l ()   | .,             |        |         |           |           |       |             |                        |

| bit 6  | -                                                                                                                |        |         |          |          |         | ı<br>nable bit | (1)    |         |           |           |       |             |                        |

| DIL U. | •                                                                                                                |        | BOR 6   |          |          |         |                | ( )    |         |           |           |       |             |                        |

|        |                                                                                                                  | _      | BOR     |          |          |         |                |        |         |           |           |       |             |                        |

| bit 3  |                                                                                                                  | -      |         |          |          | ner Fr  | hable bit (    | 1)     |         |           |           |       |             |                        |

| 511 0  | •                                                                                                                |        | PWRT    |          | •        |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | -      | PWRT    |          |          |         |                |        |         |           |           |       |             |                        |

| bit 2  | :                                                                                                                | WD     | TE: W   | atchdo   | og Tim   | er Ena  | able bit       |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 1 =    | WDT (   | enable   | ed       |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 0 =    | WDT (   | disable  | əd       |         |                |        |         |           |           |       |             |                        |

| bit 1- | -0:                                                                                                              | FOS    | SC1:F   | OSC0:    | : Oscill | ator S  | election b     | oits   |         |           |           |       |             |                        |

|        |                                                                                                                  | 11:    | = RC c  | oscillat | or       |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 10:    | = HS o  | scillat  | or       |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 01:    | = XT o  | scillato | or       |         |                |        |         |           |           |       |             |                        |

|        |                                                                                                                  | 00:    | = LP o  | scillato | or       |         |                |        |         |           |           |       |             |                        |

| Note   | 4.                                                                                                               | Enabli | na Bra  |          |          | st outo | matically      | onabl  |         |           | mor (D\// |       | diace of th |                        |

| note   |                                                                                                                  |        | -       |          |          |         |                |        |         | vn-out Re |           | , .   | uiess 01 (f | he value of bit PWRTE. |

|        | 2:                                                                                                               |        |         |          |          |         |                |        |         |           |           |       | ntection s  | cheme listed.          |

|        | ۷.                                                                                                               |        |         | 1.01 0   | Pairs    | nave    | o bo give      | in une | Same    |           |           |       |             |                        |

### 12.3 DC Characteristics: PIC16C712/716-04 (Commercial, Industrial, Extended) PIC16C712716-20 (Commercial, Industrial, Extended) PIC16LC712/716-04 (Commercial, Industrial)

| Standard Operating Conditions (unless otherwise stated) |       |                                       |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

|---------------------------------------------------------|-------|---------------------------------------|--------------------------------------------------------------------------------------------------|---------|------------|----------------|-------------------------------------------------------------------|--|--|--|--|--|

|                                                         |       |                                       | Operating                                                                                        |         | rature     | 0°C ≤<br>0°C ≤ | $TA \leq +70^{\circ}C$ for commercial                             |  |  |  |  |  |

|                                                         |       |                                       |                                                                                                  |         | -4(        | ≥ O°C          | $TA \leq +125^{\circ}C$ for extended                              |  |  |  |  |  |

| DC CHA                                                  | RACTE | RISTICS                               | Operating                                                                                        | voltage | e VDD rang | e as de        | escribed in DC spec Section 12.1                                  |  |  |  |  |  |

|                                                         |       |                                       | "DC Characteristics: PIC16C712/716-04 (Commercial, Industrial                                    |         |            |                |                                                                   |  |  |  |  |  |

|                                                         |       |                                       | Extended) PIC16C712/716-20 (Commercial, Industrial,                                              |         |            |                |                                                                   |  |  |  |  |  |

|                                                         |       |                                       | Extended)" and Section 12.2 "DC Characteristics: PIC16LC712/<br>716-04 (Commercial, Industrial)" |         |            |                |                                                                   |  |  |  |  |  |

| _                                                       |       |                                       |                                                                                                  |         | -          |                |                                                                   |  |  |  |  |  |

| Param<br>No.                                            | Sym.  | Characteristic                        | Min.                                                                                             | Тур†    | Max.       | Units          | Conditions                                                        |  |  |  |  |  |

| NO.                                                     |       |                                       |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

|                                                         |       | Input Low Voltage                     |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

|                                                         | VIL   | I/O ports                             |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

| D030                                                    |       | with TTL buffer                       | Vss                                                                                              | —       | 0.8V       | V              | $4.5V \le VDD \le 5.5V$                                           |  |  |  |  |  |

| D030A                                                   |       |                                       | Vss                                                                                              | _       | 0.15VDD    | V              | otherwise                                                         |  |  |  |  |  |

| D031                                                    |       | with Schmitt Trigger buffer           | Vss                                                                                              | —       | 0.2VDD     | V              |                                                                   |  |  |  |  |  |

| D032                                                    |       | MCLR, OSC1 (in RC mode)               | Vss                                                                                              | —       | 0.2VDD     | V              |                                                                   |  |  |  |  |  |

| D033                                                    |       | OSC1 (in XT, HS and LP modes)         | Vss                                                                                              | _       | 0.3Vdd     | V              | (Note 1)                                                          |  |  |  |  |  |

|                                                         |       | Input High Voltage                    |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

|                                                         | Viн   | I/O ports                             |                                                                                                  | —       |            |                |                                                                   |  |  |  |  |  |

| D040                                                    |       | with TTL buffer                       | 2.0                                                                                              | —       | Vdd        | V              | $4.5V \leq V\text{DD} \leq 5.5V$                                  |  |  |  |  |  |

| D040A                                                   |       |                                       | 0.25Vdd                                                                                          | —       | Vdd        | V              | otherwise                                                         |  |  |  |  |  |

|                                                         |       |                                       | + 0.8V                                                                                           |         |            |                |                                                                   |  |  |  |  |  |

| D041                                                    |       | with Schmitt Trigger buffer           | 0.8Vdd                                                                                           | _       | Vdd        | V              | For entire VDD range                                              |  |  |  |  |  |

| D042                                                    |       | MCLR                                  | 0.8Vdd                                                                                           | —       | Vdd        | V              |                                                                   |  |  |  |  |  |

| D042A                                                   |       | OSC1 (XT, HS and LP modes)            | 0.7Vdd                                                                                           | —       | Vdd        | V              | (Note 1)                                                          |  |  |  |  |  |

| D043                                                    |       | OSC1 (in RC mode)                     | 0.9Vdd                                                                                           | —       | Vdd        | V              |                                                                   |  |  |  |  |  |

|                                                         |       | Input Leakage Current<br>(Notes 2, 3) |                                                                                                  |         |            |                |                                                                   |  |  |  |  |  |

| D060                                                    | lı∟   | I/O ports                             |                                                                                                  | _       | ±1         | μA             | $V \textbf{s} \textbf{s} \leq V \textbf{PIN} \leq V \textbf{DD},$ |  |  |  |  |  |

|                                                         |       |                                       |                                                                                                  |         |            |                | Pin at high-impedance                                             |  |  |  |  |  |

| D061                                                    |       | MCLR, RA4/T0CKI                       | —                                                                                                | —       | ±5         | μA             | $Vss \leq VPIN \leq VDD$                                          |  |  |  |  |  |

| D063                                                    |       | OSC1                                  | —                                                                                                | —       | ±5         | μA             | $Vss \leq VPIN \leq VDD$ ,                                        |  |  |  |  |  |

|                                                         |       |                                       |                                                                                                  |         | 4.5.5      |                | XT, HS and LP osc modes                                           |  |  |  |  |  |

| D070                                                    | IPURB | PORTB weak pull-up current            | 50                                                                                               | 250     | 400        | μΑ             | VDD = 5V, VPIN = VSS                                              |  |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC Oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

| DC CHA       | RACTE | RISTICS                                                | Standard Operating Conditions (unless otherwise stated)         Operating temperature       0°C       ≤ TA ≤       +70°C       for commercial         -40°C       ≤ TA ≤       +85°C       for industrial         -40°C       ≤ TA ≤       +125°C       for extended         Operating voltage VDD range as described in DC spec Section 12.1       "DC Characteristics: PIC16C712/716-04 (Commercial, Industrial         Extended) PIC16C712/716-20 (Commercial, Industrial, |      |      |       |                                                                   |  |  |  |  |  |  |

|--------------|-------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------|--|--|--|--|--|--|

|              |       |                                                        | Extended)" and Section 12.2 "DC Characteristics: PIC16LC712/<br>716-04 (Commercial, Industrial)"                                                                                                                                                                                                                                                                                                                                                                              |      |      |       |                                                                   |  |  |  |  |  |  |

| Param<br>No. | Sym.  | Characteristic                                         | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Typ† | Max. | Units | Conditions                                                        |  |  |  |  |  |  |

| D080         | Vol   | Output Low Voltage<br>I/O ports                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _    | 0.6  | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |  |  |  |

|              |       |                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —    | 0.6  | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |  |  |  |

| D083         |       | OSC2/CLKOUT<br>(RC Osc mode)                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —    | 0.6  | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |  |  |  |

|              |       |                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —    | 0.6  | V     | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |  |  |  |

| D090         | Vон   | Output High Voltage<br>I/O ports (Note 3)              | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _    | _    | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —    | _    | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                     |  |  |  |  |  |  |

| D092         |       | OSC2/CLKOUT (RC Osc<br>mode)                           | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —    | _    | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —    | —    | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                     |  |  |  |  |  |  |

| D150*        | Vod   | Open-Drain High Voltage                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | 8.5  | V     | RA4 pin                                                           |  |  |  |  |  |  |

| D100         | Cosc2 | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _    | 15   | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |  |  |

| D101         | Сю    | All I/O pins and OSC2 (in RC mode)                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —    | 50   | pF    |                                                                   |  |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC Oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

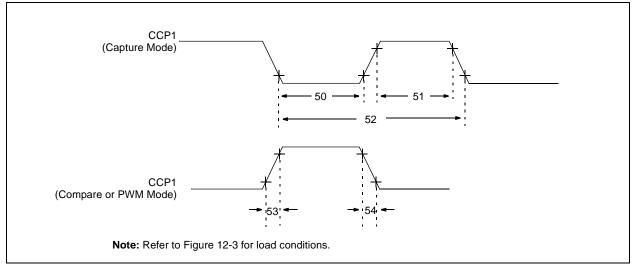

### TABLE 12-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym.                                           | Characteristic      |                |               | Min                   | Тур† | Max | Units | Conditions                         |

|--------------|------------------------------------------------|---------------------|----------------|---------------|-----------------------|------|-----|-------|------------------------------------|

| 50*          | <sup>)*</sup> TccL CCP1 input low No Prescaler |                     |                | 0.5TCY + 20   | -                     | _    | ns  |       |                                    |

|              |                                                | time                | With Prescaler | Standard      | 10                    | -    | _   | ns    |                                    |

|              |                                                |                     |                | Extended (LC) | 20                    | -    | _   | ns    |                                    |

| 51*          | 51* TccH CCP1 input hig                        |                     | No Prescaler   | 0.5Tcy + 20   | —                     |      | ns  |       |                                    |

|              |                                                | time                | With Prescaler | Standard      | 10                    | -    | _   | ns    |                                    |

|              |                                                |                     |                | Extended (LC) | 20                    | -    | _   | ns    |                                    |

| 52*          | TccP                                           | CCP1 input period   |                |               | <u>3Tcy + 40</u><br>N | —    | _   | ns    | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR                                           | CCP1 output rise ti | me             | Standard      | —                     | 10   | 25  | ns    |                                    |

|              |                                                |                     |                | Extended (LC) | —                     | 25   | 45  | ns    |                                    |

| 54*          |                                                |                     | ne             | Standard      | —                     | 10   | 25  | ns    |                                    |

|              |                                                |                     | Extended (LC)  | —             | 25                    | 45   | ns  |       |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 12-7:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C712/716-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C712/716-20 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC712/716-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym. | Characteristic                                    |               | Min.      | Тур†                   | Max.       | Units | Conditions                                                                                                                         |

|--------------|------|---------------------------------------------------|---------------|-----------|------------------------|------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                        |               | _         | _                      | 8-bits     | bit   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A02          | EABS | Total Absolute error                              |               | _         | _                      | < ± 1      | LSb   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A03          | EIL  | Integral linearity error                          |               | —         | -                      | < ± 1      | LSb   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A04          | Edl  | Differential linearity erro                       | or            | _         | _                      | < ± 1      | LSb   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A05          | Efs  | Full scale error                                  |               | —         | _                      | < ± 1      | LSb   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A06          | EOFF | Offset error                                      |               | —         | _                      | < ± 1      | LSb   | VREF = VDD = 5.12V,<br>VSS £ VAIN £ VREF                                                                                           |

| A10          | —    | Monotonicity                                      |               | _         | guaranteed<br>(Note 3) | _          | _     | VSS £ VAIN £ VREF                                                                                                                  |

| A20          | VREF | Reference voltage                                 |               | 2.5V      | _                      | Vdd + 0.3  | V     |                                                                                                                                    |

| A25          | VAIN | Analog input voltage                              |               | Vss - 0.3 |                        | Vref + 0.3 | V     |                                                                                                                                    |

| A30          | ZAIN | Recommended impedance of<br>analog voltage source |               | —         | _                      | 10.0       | kΩ    |                                                                                                                                    |

| A40          | IAD  |                                                   | Standard      | _         | 180                    | _          | μΑ    | Average current consump-                                                                                                           |

|              |      | rent (VDD)                                        | Extended (LC) | —         | 90                     | _          | μΑ    | tion when A/D is on.<br><b>(Note 1)</b>                                                                                            |

| A50          | IREF | VREF input current (Not                           | e 2)          | 10        | _                      | 1000       | μA    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 9.1<br>"Configuration Bits". |

|              |      |                                                   |               | —         | _                      | 10         | μΑ    | During A/D Conversion cycle                                                                                                        |

2: \* These parameters are characterized but not tested.

3: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the Input Voltage, and has no missing codes.

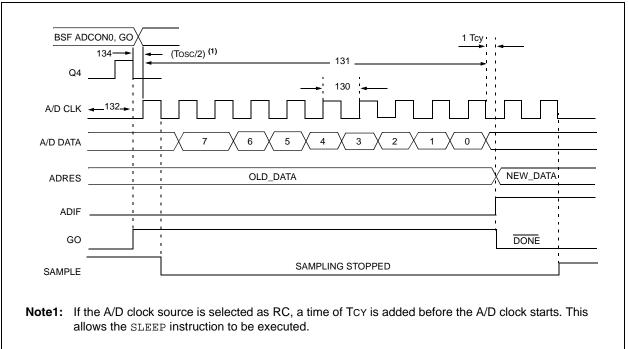

### TABLE 12-8: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                       |               | Min.     | Тур†     | Max. | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|------------------------------------------------------|---------------|----------|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                     | Standard      | 1.6      |          | _    | μS    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                  |

|              |      |                                                      | Extended (LC) | 2.0      | —        | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                                      | Standard      | 2.0      | 4.0      | 6.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                                      | Extended (LC) | 3.0      | 6.0      | 9.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (not including S/H time)<br>(Note 1) |               | 11       | —        | 11   | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                                     |               | (Note 2) | 20       | _    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                      |               | 5*       | _        | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |               | _        | Tosc/2 § | _    |       | If the A/D clock source is selected<br>as RC, a time of Tcy is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from conve                                 | 1.5 §         | —        | _        | TAD  |       |                                                                                                                                                                                                                               |

: \* These parameters are characterized but not tested.

: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

: § This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 9.1 "Configuration Bits" for min. conditions.

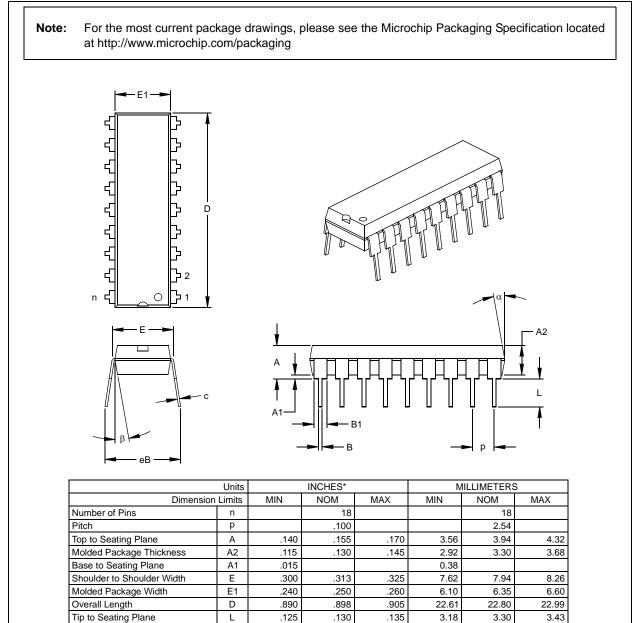

## **13.0 PACKAGING INFORMATION**

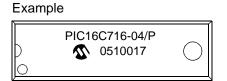

### 13.1 Package Marking Information

### 18-Lead PDIP

### 18-Lead CERDIP Windowed

### 18-Lead SOIC (.300")

### 20-Lead SSOP

### Example

### Example

### Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                              | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note: | In the event the full Microchip part number cannot be marked on one line, it wind be carried over to the next line, thus limiting the number of availabl characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

### 13.2 Package Details

The following sections give the technical details of the packages.

### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

.008

.045

.014

.310

5

5

.012

.058

.018

.370

10

10

.015

.070

.022

.430

15

15

0.20

1.14

0.36

7.87

5

5

0.29

1.46

0.46

9.40

10

10

0.38

1.78

0.56

10.92

15

15

С

B1

В

eВ

α

β

δ

JEDEC Equivalent: MS-001

Drawing No. C04-007

Lead Thickness

Upper Lead Width

Lower Lead Width

**Overall Row Spacing**

Mold Draft Angle Top

Mold Draft Angle Bottom

\* Controlling Parameter § Significant Characteristic

## APPENDIX A: REVISION HISTORY

| Version Date |      | Revision Description                                                                                                                                                                                                                    |  |  |  |  |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| A            | 2/99 | This is a new data sheet. How-<br>ever, the devices described in this<br>data sheet are the upgrades to<br>the devices found in the<br><i>PIC16C6X Data Sheet</i> ,<br>DS30234, and the <i>PIC16C7X</i><br><i>Data Sheet</i> , DS30390. |  |  |  |  |

| В            | 9/05 | Removed Preliminary Status.                                                                                                                                                                                                             |  |  |  |  |

| С            | 1/13 | Added a note to each package outline drawing.                                                                                                                                                                                           |  |  |  |  |

# APPENDIX B: CONVERSION CONSIDERATIONS

There are no previous versions of this device.

# APPENDIX C: MIGRATION FROM BASE-LINE TO MID-RANGE DEVICES

This section discusses how to migrate from a baseline device (i.e., PIC16C5X) to a mid-range device (i.e., PIC16CXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION\_REG and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different Reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from Sleep through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight-bit register.

- 15. "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON STATUS register is added with a Poweron Reset Status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by Configuration Word bit BODEN. Brown-out Reset ensures the device is placed in a Reset condition if VDD dips below a fixed setpoint.

To convert code written for PIC16C5X to PIC16CXXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change Reset vector to 0000h.

# PIC16C712/716

| TMR1L Register 11, 31                    |

|------------------------------------------|

| Timer2                                   |

| Block Diagram 36                         |

| Postscaler. See Postscaler, Timer2       |

| PR2 Register 12, 36, 42                  |

| Prescaler. See Prescaler, Timer2         |

| T2CON Register 11, 36                    |

| TMR2 Register 11, 36                     |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 |

| TMR2 to PR2 Match Flag (TMR2IF Bit)      |

| TMR2 to PR2 Match Interrupt 36, 37, 42   |

| Timing Diagrams                          |

| Time-out Sequence on Power-up60          |

| Wake-up from Sleep via Interrupt         |

| Timing Diagrams and Specifications       |

| A/D Conversion                           |

| Brown-out Reset (BOR) 83                 |

| Capture/Compare/PWM (CCP) 85             |

| CLKOUT and I/O                           |

| External Clock                           |

| Oscillator Start-up Timer (OST)          |

| Power-up Timer (PWRT)                    |

| Reset                                    |

| Timer0 and Timer1                        |

| Watchdog Timer (WDT)                     |

|                                          |

### W

| W Register                             |   |

|----------------------------------------|---|

| Wake-up from Sleep                     |   |

| Wake-up from Sleep                     |   |

| Interrupts                             |   |

| MCLR Reset 59                          |   |

| Timing Diagram 65                      | 5 |