Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 4x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc716-04-p |

| Key Features<br>PIC <sup>®</sup> Mid-Range Reference Manual (DS33023) | PIC16C712            | PIC16C716            |

|-----------------------------------------------------------------------|----------------------|----------------------|

| Operating Frequency                                                   | DC – 20 MHz          | DC – 20 MHz          |

| Resets (and Delays)                                                   | POR, BOR (PWRT, OST) | POR, BOR (PWRT, OST) |

| Program Memory (14-bit words)                                         | 1K                   | 2K                   |

| Data Memory (bytes)                                                   | 128                  | 128                  |

| Interrupts                                                            | 7                    | 7                    |

| I/O Ports                                                             | Ports A,B            | Ports A,B            |

| Timers                                                                | 3                    | 3                    |

| Capture/Compare/PWM modules                                           | 1                    | 1                    |

| 8-bit Analog-to-Digital Module                                        | 4 input channels     | 4 input channels     |

### **PIC16C7XX FAMILY OF DEVICES**

|             |                                                                               | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C712                           | PIC16C715                           | PIC16C716                           | PIC16C72A                  | PIC16C73B                      |

|-------------|-------------------------------------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|----------------------------|--------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)                                          | 20                                  | 20                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                         | 20                             |

| Memory      | EPROM Program<br>Memory<br>(x14 words)                                        | 512                                 | 1K                  | 1K                                  | 1K                                  | 2K                                  | 2K                                  | 2K                         | 4K                             |

|             | Data Memory (bytes)                                                           | 36                                  | 36                  | 68                                  | 128                                 | 128                                 | 128                                 | 128                        | 192                            |

|             | Timer Module(s)                                                               | TMR0                                | TMR0                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0                                | TMR0<br>TMR1<br>TMR2                | TMR0<br>TMR1<br>TMR2       | TMR0<br>TMR1<br>TMR2           |

| Peripherals | Capture/Compare/<br>PWM Module(s)                                             | _                                   | _                   | _                                   | 1                                   | _                                   | 1                                   | 1                          | 2                              |

|             | Serial Port(s)<br>(SPI <sup>TM</sup> /I <sup>2</sup> C <sup>TM</sup> , USART) | _                                   | _                   | _                                   | _                                   | _                                   | _                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C,<br>USART |

|             | A/D Converter (8-bit)<br>Channels                                             | 4                                   | 4                   | 4                                   | 4                                   | 4                                   | 4                                   | 5                          | 5                              |

|             | Interrupt Sources                                                             | 4                                   | 4                   | 4                                   | 7                                   | 4                                   | 7                                   | 8                          | 11                             |

|             | I/O Pins                                                                      | 13                                  | 13                  | 13                                  | 13                                  | 13                                  | 13                                  | 22                         | 22                             |

|             | Voltage Range (Volts)                                                         | 2.5-6.0                             | 3.0-6.0             | 2.5-6.0                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                    | 2.5-5.5                        |

| Features    | In-Circuit Serial<br>Programming™                                             | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Brown-out Reset                                                               | Yes                                 | _                   | Yes                                 | Yes                                 | Yes                                 | Yes                                 | Yes                        | Yes                            |

|             | Packages                                                                      | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC           |

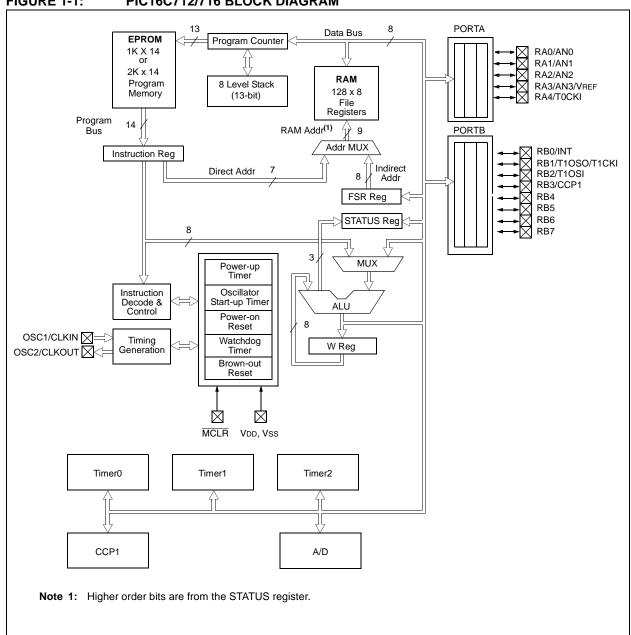

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the  $PIC^{\otimes}$  Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are two devices (PIC16C712, PIC16C716) covered by this data sheet.

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

FIGURE 1-1: PIC16C712/716 BLOCK DIAGRAM

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is give in Table 2-1. The Special Function Registers can be classified into two sets; core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in that peripheral feature section.

TABLE 2-1: SPECIAL FUNCTION REGISTER SUMMARY

| Addr    | Name                    | Bit 7                                     | Bit 6                               | Bit 5         | Bit 4            | Bit 3         | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets (4) |

|---------|-------------------------|-------------------------------------------|-------------------------------------|---------------|------------------|---------------|-----------------|---------------|---------|--------------------------|-------------------------------------|

| Bank 0  | Bank 0                  |                                           |                                     |               |                  |               |                 |               |         |                          |                                     |

| 00h     | INDF <sup>(1)</sup>     | Addressing                                | this location                       | uses conten   | ts of FSR to ac  | ddress data r | nemory (not     | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 01h     | TMR0                    | Timer0 Mod                                | lule's Registe                      | er            |                  |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 02h     | PCL <sup>(1)</sup>      | Program Co                                | ounter's (PC)                       | Least Signif  | icant Byte       |               |                 |               |         | 0000 0000                | 0000 0000                           |

| 03h     | STATUS <sup>(1)</sup>   | IRP <sup>(4)</sup>                        | RP1 <sup>(4)</sup>                  | RP0           | TO               | PD            | Z               | DC            | С       | rr01 1xxx                | rr0q quuu                           |

| 04h     | FSR <sup>(1)</sup>      | Indirect Data                             | a Memory Ad                         | dress Pointe  | er               |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 05h     | PORTA <sup>(5,6)</sup>  | _                                         | _                                   | (7)           | PORTA Data       | Latch when    | written: POR    | TA pins wher  | n read  | xx xxxx                  | xu uuuu                             |

| 06h     | PORTB <sup>(5,6)</sup>  | PORTB Dat                                 | a Latch whe                         | n written: PC | RTB pins whe     | n read        |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 07h     | DATACCP                 | (7)                                       | (7)                                 | (7)           | (7)              | (7)           | DCCP            | (7)           | DT1CK   | xxxx xxxx                | xxxx xuxu                           |

| 08h-09h | _                       | Unimpleme                                 | nted                                |               |                  |               |                 |               |         | -                        | -                                   |

| 0Ah     | PCLATH <sup>(1,2)</sup> | _                                         | _                                   | _             | Write Buffer fo  | or the upper  | 5 bits of the F | Program Cou   | ınter   | 0 0000                   | 0 0000                              |

| 0Bh     | INTCON <sup>(1)</sup>   | GIE                                       | PEIE                                | TOIE          | INTE             | RBIE          | TOIF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch     | PIR1                    | _                                         | ADIF                                | ı             | _                | _             | CCP1IF          | TMR2IF        | TMR1IF  | -0 0000                  | -0 0000                             |

| 0Dh     | -                       | Unimpleme                                 | nted                                |               |                  |               |                 |               |         | -                        | -                                   |

| 0Eh     | TMR1L                   | Holding Reg                               | gister for the                      | Least Signifi | cant Byte of th  | e 16-bit TMF  | 1 Register      |               |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh     | TMR1H                   | Holding Reg                               | gister for the                      | Most Signific | cant Byte of the | e 16-bit TMR  | 1 Register      |               |         | xxxx xxxx                | uuuu uuuu                           |

| 10h     | T1CON                   | _                                         | -                                   | T1CKPS1       | T1CKPS0          | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h     | TMR2                    | Timer2 Mod                                | lule's Registe                      | er            |                  |               |                 |               |         | 0000 0000                | 0000 0000                           |

| 12h     | T2CON                   | _                                         | TOUTPS3                             | TOUTPS2       | TOUTPS1          | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h-14h |                         |                                           |                                     |               |                  |               |                 |               |         |                          |                                     |

| 15h     | CCPR1L                  | Capture/Compare/PWM Register1 (LSB)       |                                     |               |                  |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 16h     | CCPR1H                  | Capture/Co                                | Capture/Compare/PWM Register1 (MSB) |               |                  |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 17h     | CCP1CON                 | - DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 |                                     |               |                  |               |                 |               | 00 0000 | 00 0000                  |                                     |

| 18h-1Dh | _                       | Unimplemented                             |                                     |               |                  |               |                 |               |         | -                        | -                                   |

| 1Eh     | ADRES                   | A/D Result                                | Register                            |               |                  |               |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 1Fh     | ADCON0                  | ADCS1                                     | ADCS0                               | CHS2          | CHS1             | CHS0          | GO/DONE         |               | ADON    | 0000 00-0                | 0000 00-0                           |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0', Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non Power-up) Resets include: external Reset through MCLR and the Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved. Always maintain these bits clear.

- 5: On any device Reset, these pins are configured as inputs.

- 6: This is the value that will be in the port output latch.

- 7: Reserved bits; Do Not Use.

#### 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

#### 3.1 PORTA and the TRISA Register

PORTA is a 5-bit wide bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

PORTA pins, RA3:0, are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### **EXAMPLE 3-1: INITIALIZING PORTA**

| DOE   | CHIAMIIC DDO |                         |

|-------|--------------|-------------------------|

| BCF   | STATUS, RP0  | ;                       |

| CLRF  | PORTA        | ; Initialize PORTA by   |

|       |              | ; clearing output       |

|       |              | ; data latches          |

| BSF   | STATUS, RPO  | ; Select Bank 1         |

| MOVLW | 0xEF         | ; Value used to         |

|       |              | ; initialize data       |

|       |              | ; direction             |

| MOVWF | TRISA        | ; Set RA<3:0> as inputs |

|       |              | ; RA<4> as outputs      |

| BCF   | STATUS, RPO  | ; Return to Bank 0      |

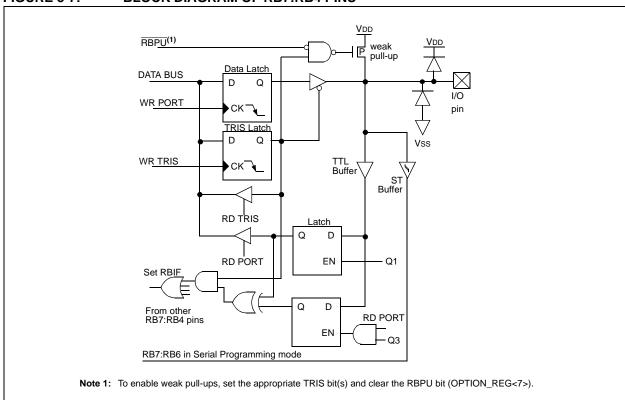

FIGURE 3-7: BLOCK DIAGRAM OF RB7:RB4 PINS

TABLE 3-3: PORTB FUNCTIONS

| Name                | Bit#  | Buffer                | Function                                                                                                                                                        |

|---------------------|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT             | bit 0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                                      |

| RB1/T1OS0/<br>T1CKI | bit 1 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator output, or Timer1 clock input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.    |

| RB2/T1OSI           | bit 2 | TTL/ST <sup>(1)</sup> | Input/output pin or Timer1 oscillator input. Internal software programmable weak pull-up. See Timer1 section for detailed operation.                            |

| RB3/CCP1            | bit 3 | TTL/ST <sup>(1)</sup> | Input/output pin or Capture 1 input, or Compare 1 output, or PWM1 output. Internal software programmable weak pull-up. See CCP1 section for detailed operation. |

| RB4                 | bit 4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                       |

| RB5                 | bit 5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                                       |

| RB6                 | bit 6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock.                                             |

| RB7                 | bit 7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data.                                              |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt or peripheral input.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name       | Bit 7   | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------|---------|-------------------------------|-------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------|

| 06h     | PORTB      | RB7     | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1       | RB0       | xxxx xxxx                | uuuu uuuu                 |

| 86h     | TRISB      | PORTB I | PORTB Data Direction Register |       |       |       |       | 1111 1111 | 1111 1111 |                          |                           |

| 81h     | OPTION_REG | RBPU    | INTEDG                        | T0CS  | T0SE  | PSA   | PS2   | PS1       | PS0       | 1111 1111                | 1111 1111                 |

**Legend:** x = unknown, u = unchanged. Shaded cells are not used by PORTB.

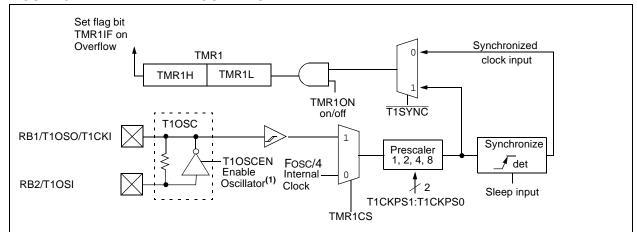

#### FIGURE 5-2: TIMER1 BLOCK DIAGRAM

Note 1: When the T1OSCEN bit is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

## 5.2 Timer1 Module and PORTB Operation

When Timer1 is configured as timer running from the main oscillator, PORTB<2:1> operate as normal I/O lines. When Timer1 is configured to function as a counter however, the clock source selection may affect the operation of PORTB<2:1>. Multiplexing details of the Timer1 clock selection on PORTB are shown in Figure 3-4 and Figure 3-5.

The clock source for Timer1 in the Counter mode can be from one of the following:

- External circuit connected to the RB1/T1OSO/ T1CKI pin

- 2. Firmware controlled DATACCP<0> bit, DT1CKI

- 3. Timer1 oscillator

Table 5-1 shows the details of Timer1 mode selections, control bit settings, TMR1 and PORTB operations.

#### 5.3 Timer1 Oscillator

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 200 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 5-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 5-2: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type | Freq.   | C1    | C2    |

|----------|---------|-------|-------|

| LP       | 32 kHz  | 33 pF | 33 pF |

|          | 100 kHz | 15 pF | 15 pF |

|          | 200 kHz | 15 pF | 15 pF |

#### These values are for design guidance only.

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

### 5.4 Timer1 Interrupt

The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

### 5.5 Resetting Timer1 using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "Special Event Trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1 and start an A/D conversion (if the A/D module is enabled).

| Note: | The Special Event Triggers from th        | e  |

|-------|-------------------------------------------|----|

|       | CCP1 module will not set interrupt flag b | it |

|       | TMR1IF (PIR1<0>).                         |    |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger from CCP1, the write will take precedence.

In this mode of operation, the CCPR1H:CCPR1L registers pair effectively becomes the period register for Timer1.

TABLE 5-3: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address | Name        | Bit 7  | Bit 6   | Bit 5          | Bit 4         | Bit 3          | Bit 2        | Bit 1     | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------------|--------|---------|----------------|---------------|----------------|--------------|-----------|--------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON      | GIE    | PEIE    | TOIE           | INTE          | RBIE           | TOIF         | INTF      | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1        | _      | ADIF    | _              | 1             | 1              | CCP1IF       | TMR2IF    | TMR1IF | -0000                   | -0000                           |

| 8Ch     | PIE1        | _      | ADIE    | _              | 1             | 1              | CCP1IE       | TMR2IE    | TMR1IE | -0000                   | -0000                           |

| 0Eh     | TMR1L       | Holdir | ng Regi | ster for the I | Least Signifi | cant Byte of   | the 16-bit   | TMR1 Regi | ster   | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H       | Holdir | ng Regi | ster for the I | Most Signific | cant Byte of t | the 16-bit T | MR1 Regis | ter    | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON       | _      | _       | T1CKPS1        | T1CKPS0       | T1OSCEN        | T1SYNC       | TMR1CS    | TMR10N | 00 0000                 | uu uuuu                         |

| 07h     | DATACC<br>P | _      | _       | _              | _             | _              | DCCP         | _         | DT1CK  | x-x                     | u-u                             |

| 87h     | TRISCCP     | _      | _       | _              | _             | _              | TCCP         | _         | TT1CK  | 1-1                     | 1-1                             |

$\textbf{Legend:} \quad \textbf{x} = \text{unknown, u} = \text{unchanged, } \\ \textbf{--} = \text{unimplemented read as '0'}. \\ \textbf{Shaded cells are not used by the Timer1 module.}$

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

TABLE 7-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

|          |                                                              |                                                                                                               |                                                                                                                                           |                                                                                                     | <u> </u>                                                                              |                                          |                        |                                                                             |

|----------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------|------------------------|-----------------------------------------------------------------------------|

| U-0      | U-0                                                          | R/W-0<br>DC1B1                                                                                                | R/W-0<br>DC1B0                                                                                                                            | R/W-0<br>CCP1M3                                                                                     | R/W-0<br>CCP1M2                                                                       | R/W-0                                    | R/W-0<br>CCP1M0        | R = Readable bit                                                            |

| bit 7-6: | Unim                                                         | plemente                                                                                                      |                                                                                                                                           |                                                                                                     | CCF IIVIZ                                                                             | CCPTIVIT                                 | bit0                   | W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR Reset |

|          | DC1E<br>Captu<br>Comp                                        | 31:DC1B0<br>Ire Mode:<br>are Mode                                                                             | : PWM Le<br>Unused<br>: Unused                                                                                                            | ast Significa                                                                                       |                                                                                       | PWM duty c                               | ycle. The eig          | ght MSbs are found in CCPR1L.                                               |

| bit 3-0: | 0000<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010 | = Capture<br>= Capture<br>= Capture<br>= Capture<br>= Capture<br>= Compai<br>= Compai<br>= Compai<br>= Compai | e/Compare<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>re mode, s<br>re mode, g<br>re mode, g<br>re mode, t<br>sion (if A/E | very falling of very rising every 4th rising every 16th rise set output occlear output lenerate sof | resets CCP dedge and gedge sing edge an match (CC on match (tware interruial event (C | CP1IF bit is<br>CCP1IF bit iupt on matcl | is set)<br>h (CCP1IF b | it is set, CCP1 pin is unaffected)<br>resets TMR1 and starts an A/D         |

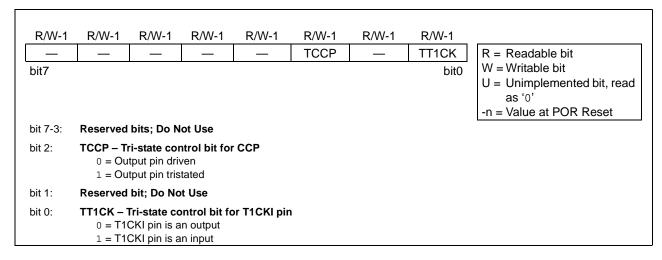

### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISCCP<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 7-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 7-4: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address | Name    | Bit 7     | Bit 6        | Bit 5        | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|---------|-----------|--------------|--------------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 07h     | DATACCP | _         | _            | _            | _       | _       | DCCP   | _       | DT1CK   | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON  | GIE       | PEIE         | TOIE         | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | _         | ADIF         | _            | _       | _       | CCP1IF | TMR2IF  | TMR1IF  | -0000                   | -0000                           |

| 11h     | TMR2    | Timer2 Mo | dule's Regis | ter          |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON   | _         | TOUTPS3      | TOUTPS2      | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 15h     | CCPR1L  | Capture/C | ompare/PWI   | M Register 1 | (LSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/C | ompare/PWI   | M Register 1 | (MSB)   |         |        |         |         | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON | _         | _            | DC1B1        | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP | _         | _            | _            | _       | _       | TCCP   | _       | TT1CK   | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1    | _         | ADIE         | _            | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                   | -0000                           |

| 92h     | PR2     | Timer2 Mo | dule's Perio | d Register   |         |         |        |         |         | 1111 1111               | 1111 1111                       |

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

### FIGURE 8-2: ADCON1 REGISTER (ADDRESS 9Fh)

|     |     |     |     |     | PCFG2 | DCEC1 | DCEC0 |

|-----|-----|-----|-----|-----|-------|-------|-------|

| U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

bit7

R = Readable bit

W = Writable bit

bit0

U = Unimplemented bit, read as '0'

-n = Value at POR Reset

bit 7-3: Unimplemented: Read as '0'

bit 2-0: PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA3  | VREF |

|-------------|-----|-----|-----|------|------|

| 0x0         | Α   | Α   | Α   | Α    | Vdd  |

| 0x1         | Α   | Α   | Α   | VREF | RA3  |

| 100         | Α   | Α   | D   | Α    | VDD  |

| 101         | Α   | Α   | D   | VREF | RA3  |

| 11x         | D   | D   | D   | D    | Vdd  |

A = Analog input

D = Digital I/O

### 8.1 A/D Acquisition Requirements

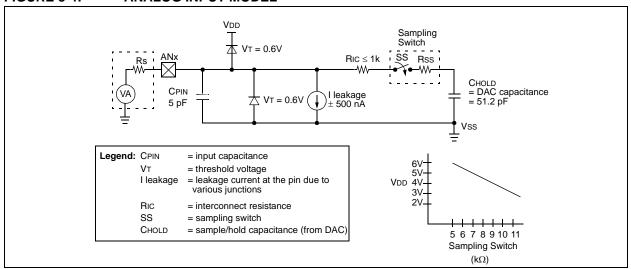

For the A/D converter to meet its specified accuracy, the Charge Holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 8-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10  $k\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023). This equation calculates the acquisition time to within 1/2 LSb error (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

When the conversion is started, the holding capacitor is disconnected from the input pin.

FIGURE 8-4: ANALOG INPUT MODEL

Note:

## 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit, BOR. If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset.

The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            |           | 72 ms            | _            |  |

TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

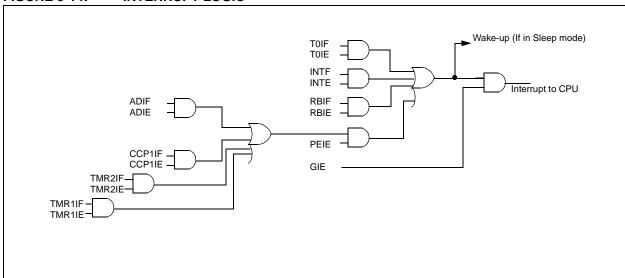

#### 9.10 Interrupts

The PIC16C712/716 devices have up to 7 sources of interrupt. The Interrupt Control Register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

**Note:** Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on Reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the Special Function Registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in Special Function Registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in Special Function Register, INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

FIGURE 9-14: INTERRUPT LOGIC

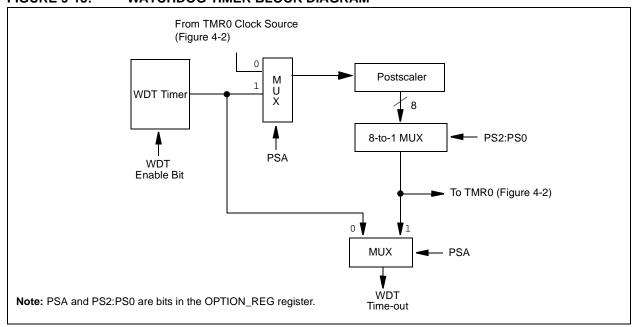

### 9.12 Watchdog Timer (WDT)

The Watchdog Timer is as a free running, on-chip, RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device have been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT Time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

The WDT can be permanently disabled by clearing Configuration bit WDTE (Section 9.1 "Configuration Bits").

WDT time-out period values may be found in the Electrical Specifications section under TWDT (parameter #31). Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

Note: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

Note:

#### FIGURE 9-16: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bits 13:8 | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-----------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | (1)       | -     | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | N/A       | RBPU  | INTEDG               | T0CS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 9-1 for operation of these bits.

#### 9.13 Power-down Mode (Sleep)

Power-Down mode is entered by executing a  ${\tt SLEEP}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, powerdown the A/D and the disable external clocks. Pull all I/O pins, that are high-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 9.13.1 WAKE-UP FROM SLEEP

The device can wake up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some peripheral interrupts.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT Time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from Sleep:

- TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- Special Event Trigger (Timer1 in Asynchronous mode using an external clock).

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

**NOTES:**

**NOTES:**

### **INDEX**

| A                                                 |        | Enable (CCP1IE Bit)                            |         |    |

|---------------------------------------------------|--------|------------------------------------------------|---------|----|

| A/D                                               | 45     | Flag (CCP1IF Bit)                              |         | 17 |

| A/D Converter Enable (ADIE Bit)                   |        | PWM Mode. See PWM                              |         |    |

| A/D Converter Flag (ADIF Bit)                     |        | Timer Resources                                |         | 39 |

| A/D Converter Interrupt, Configuring              |        | Timing Diagram                                 |         | 85 |

| ADCON0 Register                                   |        | CCP1CON Register                               |         | 39 |

| ADCON1 Register                                   |        | CCP1M3:CCP1M0 Bits                             |         | 39 |

| ADRES Register                                    |        | CCP1X:CCP1Y Bits                               |         | 39 |

|                                                   |        | Code Protection                                | 51,     | 65 |

| Analog Port Pins, Configuring                     |        | CP1:CP0 Bits                                   |         | 52 |

| Block Diagram Analog Innut Model                  |        | Compare (CCP Module)                           |         |    |

| Block Diagram, Analog Input Model                 |        | Block Diagram                                  |         |    |

| Channel Select (CHS2:CHS0 Bits)                   |        | CCP Pin Configuration                          |         |    |

| Clock Select (ADCS1:ADCS0 Bits)                   |        | CCPR1H:CCPR1L Registers                        |         |    |

| Configuring the Module                            |        | Software Interrupt                             |         |    |

| Conversion Clock (Tad)                            |        | Special Event Trigger                          |         |    |

| Conversion Status (GO/DONE Bit)                   |        | Timer1 Mode Selection                          |         |    |

| Conversions                                       |        | Configuration Bits                             |         |    |

| Converter Characteristics                         |        | Conversion Considerations                      |         |    |

| Module On/Off (ADON Bit)                          |        | Customer Change Notification Service           |         |    |

| Port Configuration Control (PCFG2:PCFG0           |        | Customer Notification Service                  |         |    |

| Sampling Requirements                             |        |                                                |         |    |

| Special Event Trigger (CCP)                       | 41, 50 | Customer Support                               | 1       | UI |

| Timing Diagram                                    | 87     | D                                              |         |    |

| Absolute Maximum Ratings                          | 73     | Poto Momoni                                    |         | 40 |

| ADCON0 Register                                   | 11, 45 | Data Memory                                    |         |    |

| ADCS1:ADCS0 Bits                                  |        | Bank Select (RP1:RP0 Bits)                     |         |    |

| ADON Bit                                          | 45     | General Purpose Registers                      |         |    |

| CHS2:CHS0 Bits                                    | 45     | Register File Map                              |         |    |

| GO/DONE Bit                                       |        | Special Function Registers                     |         |    |

| ADCON1 Register                                   | •      | DC Characteristics                             |         |    |

| PCFG2:PCFG0 Bits                                  |        | Development Support                            |         |    |

| ADRES Register                                    |        | Direct Addressing                              |         | 20 |

| Analog-to-Digital Converter. See A/D Architecture |        | E                                              |         |    |

| PIC16C712/716 Block Diagram                       |        | <del>-</del>                                   |         |    |

| Assembler                                         |        | Electrical Characteristics                     |         |    |

| MPASM Assembler                                   | 70     | Errata                                         |         |    |

| WII AGWI AGGCIIIDIGI                              | 70     | External Power-on Reset Circuit                |         | 55 |

| В                                                 |        | F                                              |         |    |

| Banking, Data Memory                              | 10 13  | •                                              |         |    |

| BOR. See Brown-out Reset                          | 10, 13 | Family of Devices                              |         |    |

| Brown-Out Reset (BOR)                             | 55     | PIC16C7XX                                      |         |    |

| Brown-out Reset (BOR)                             |        | Firmware Instructions                          |         | 67 |

| BOR Enable (BODEN Bit)                            |        | 1                                              |         |    |

|                                                   |        | 1                                              |         |    |

| BOR Status (BOR Bit)                              |        | I/O Ports                                      |         |    |

| Timing Diagram                                    | 83     | ID Locations                                   | 51,     | 65 |

| C                                                 |        | In-Circuit Serial Programming™ (ICSP™)         | 51,     | 65 |

|                                                   |        | Indirect Addressing                            |         | 20 |

| C Compilers                                       | 70     | FSR Register                                   | 10, 11, | 20 |

| MPLAB C18                                         | _      | INDF Register                                  |         | 11 |

| MPLAB C30                                         |        | Instruction Format                             |         |    |

| Capture (CCP Module)                              |        | Instruction Set                                |         | 67 |

| Block Diagram                                     |        | Summary Table                                  |         | 68 |

| CCP Pin Configuration                             | 40     | INT Interrupt (RB0/INT). See Interrupt Sources |         |    |

| CCPR1H:CCPR1L Registers                           | 40     | INTCON Register                                | 11.     | 15 |

| Changing Between Capture Prescalers               | 40     | GIE Bit                                        |         |    |

| Software Interrupt                                |        | INTE Bit                                       |         |    |

| Timer1 Mode Selection                             | 40     | INTE Bit                                       |         |    |

| Capture/Compare/PWM (CCP)                         | 39     | PEIE Bit                                       |         |    |

| Capture Mode. See Capture                         |        | RBIE Bit                                       |         |    |

| CCP1CON Register                                  | 11, 39 | RBIF Bit                                       |         |    |

| CCPR1H Register                                   |        | TOIE Bit                                       | ,       |    |

| CCPR1L Register                                   |        |                                                |         |    |

| Compare Mode. See Compare                         | •      | TOIF Bit                                       |         |    |

| •                                                 |        | Internet Address                               | 1       | UI |

| PORTC                                    | Brown-out Reset (BOR). See Brown-out Reset (BOR) |            |

|------------------------------------------|--------------------------------------------------|------------|

| TRISC Register 12                        | MCLR Reset. See MCLR                             |            |

| Postscaler, Timer2                       | Power-on Reset (POR). See Power-on Reset (POR)   |            |

| Select (TOUTPS3:TOUTPS0 Bits)            | Reset Conditions for All Registers 5             | 59         |

| Postscaler, WDT                          | Reset Conditions for PCON Register 5             | 58         |

| Assignment (PSA Bit) 14, 29              | Reset Conditions for Program Counter5            |            |

| Block Diagram30                          | Reset Conditions for STATUS Register 5           |            |

| Rate Select (PS2:PS0 Bits) 14, 29        | Timing Diagram8                                  |            |

| Switching Between Timer0 and WDT 30      | WDT Reset. See Watchdog Timer (WDT)              |            |

| Power-down Mode. See Sleep               | Revision History9                                | <b>)</b> 5 |

| Power-on Reset (POR) 51, 54, 55, 58, 59  | ·                                                |            |

| Oscillator Start-up Timer (OST)          | S                                                |            |

| POR Status (POR Bit)                     | Sleep 6                                          | 34         |

| Power Control (PCON) Register 58         | Sleep                                            |            |

| Power-down (PD Bit)                      | Software Simulator (MPLAB SIM)                   |            |

| Power-on Reset Circuit, External         | Special Event Trigger. See Compare               | •          |

| ·                                        | Special Features of the CPU                      | :1         |

| Power-up Timer (PWRT)                    | Special Function Registers                       |            |

| PWRT Enable (PWRTE Bit)                  |                                                  |            |

| Time-out (TO Bit)                        | Speed, Operating                                 |            |

| Time-out Sequence 57                     | Stack                                            |            |

| Time-out Sequence on Power-up 60         | STATUS Register 11, 13, 6                        |            |

| Timing Diagram 83                        | C Bit                                            |            |

| Prescaler, Capture 40                    | DC Bit 1                                         |            |

| Prescaler, Timer0                        | <u>IRP</u> Bit 1                                 | 13         |

| Assignment (PSA Bit) 14, 29              | PD Bit 13, 5                                     |            |

| Block Diagram 30                         | RP1:RP0 Bits 1                                   | 13         |

| Rate Select (PS2:PS0 Bits) 14, 29        | TO Bit 13, 5                                     | 54         |

| Switching Between Timer0 and WDT 30      | Z Bit 1                                          | 13         |

| Prescaler, Timer1                        | <u> </u>                                         |            |

| Select (T1CKPS1:T1CKPS0 Bits)            | Т                                                |            |

| Prescaler, Timer2                        | T1CON Register 11, 3                             | 31         |

| Select (T2CKPS1:T2CKPS0 Bits)            | T1CKPS1:T1CKPS0 Bits                             |            |

|                                          | T1OSCEN Bit                                      |            |

| Product Identification System            | T1SYNC Bit                                       |            |

| Program Counter                          | TMR1CS Bit                                       |            |

| PCL Register                             | TMR1ON Bit                                       |            |

| PCLATH Register 11, 19, 62               |                                                  |            |

| Reset Conditions 58                      | T2CON Register                                   |            |

| Program Memory 9                         | T2CKPS1:T2CKPS0 Bits                             |            |

| Interrupt Vector9                        | TMR2ON Bit                                       |            |

| Paging 9, 19                             | TOUTPS3:TOUTPS0 Bits                             |            |

| Program Memory Map 9                     | Timer0 2                                         |            |

| Reset Vector 9                           | Block Diagram2                                   |            |

| Program Verification 65                  | Clock Source Edge Select (T0SE Bit) 14, 2        | 29         |

| Programming, Device Instructions 67      | Clock Source Select (T0CS Bit) 14, 2             | 29         |

| PWM (CCP Module) 42                      | Overflow Enable (T0IE Bit) 1                     | 5          |

| Block Diagram 42                         | Overflow Flag (T0IF Bit) 15, 6                   | 32         |

| CCPR1H:CCPR1L Registers                  | Overflow Interrupt                               | 32         |

| Duty Cycle                               | Prescaler. See Prescaler, Timer0                 |            |

| Example Frequencies/Resolutions          | Timing Diagram 8                                 | 34         |

|                                          | TMR0 Register 1                                  |            |

| Output Diagram                           | Timer1                                           |            |

| Period                                   | Block Diagram                                    |            |

| Set-Up for PWM Operation                 | Capacitor Selection                              |            |

| TMR2 to PR2 Match36, 42                  |                                                  |            |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 | Clock Source Select (TMR1CS Bit)                 |            |

| TMR2 to PR2 Match Flag (TMR2IF Bit)17    | External Clock Input Sync (T1SYNC Bit)           |            |

| 0                                        | Module On/Off (TMR1ON Bit)                       |            |

| Q                                        | Oscillator                                       |            |

| Q-Clock                                  | Oscillator Enable (T1OSCEN Bit)                  |            |

| R                                        | Overflow Enable (TMR1IE Bit) 1                   |            |

|                                          | Overflow Flag (TMR1IF Bit)1                      |            |

| RAM. See Data Memory                     | Overflow Interrupt 31, 3                         | 34         |

| Reader Response                          | Prescaler. See Prescaler, Timer1                 |            |

| Register File                            | Special Event Trigger (CCP)                      | ļ1         |

| Register File Map 10                     | T1CON Register 11, 3                             |            |

| Reset51, 54                              | Timing Diagram 8                                 |            |

| Block Diagram56                          | TMR1H Register                                   |            |

| 5                                        |                                                  |            |