Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc716-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

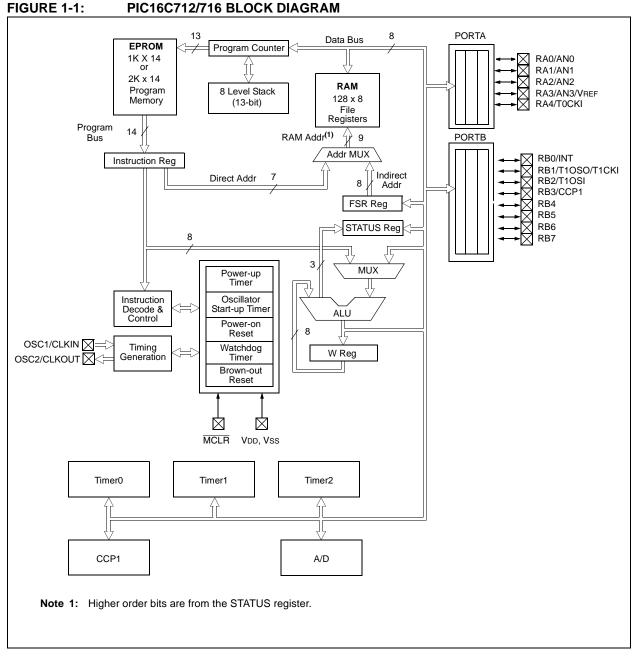

#### 1.0 **DEVICE OVERVIEW**

This document contains device-specific information. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

| С  | <u> </u> | JRE | 4 4 |   |

|----|----------|-----|-----|---|

| гι | GL       | лсс |     | - |

There are two devices (PIC16C712, PIC16C716) covered by this data sheet.

Figure 1-1 is the block diagram for both devices. The pinouts are listed in Table 1-1.

| Name         | Bit#  | Buffer | Function                                        |

|--------------|-------|--------|-------------------------------------------------|

| RA0/AN0      | bit 0 | TTL    | Input/output or analog input                    |

| RA1/AN1      | bit 1 | TTL    | Input/output or analog input                    |

| RA2/AN2      | bit 2 | TTL    | Input/output or analog input                    |

| RA3/AN3/VREF | bit 3 | TTL    | Input/output or analog input or VREF            |

|              |       |        | Input/output or external clock input for Timer0 |

| RA4/T0CKI    | bit 4 | ST     | Output is open drain type                       |

#### TABLE 3-1: PORTA FUNCTIONS

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1    | Bit 0   | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|-------|-------|-------|-------|--------|-----------|----------|---------|-------------------------|---------------------------|

| 05h     | PORTA  |       |       | _(1)  | RA4   | RA3    | RA2       | RA1      | RA0     | xx xxxx                 | xu uuuu                   |

| 85h     | TRISA  | _     | —     | _(1)  | PORT  | A Data | Direction | Register | 11 1111 | 11 1111                 |                           |

| 9Fh     | ADCON1 | _     |       |       |       |        | PCFG2     | PCFG1    | PCFG0   | 000                     | 000                       |

Legend: x = unknown, u = unchanged, — = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: Reserved bits; Do Not Use.

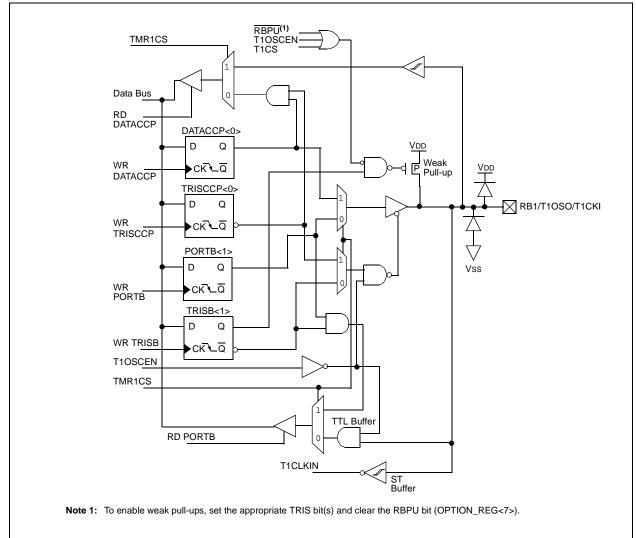

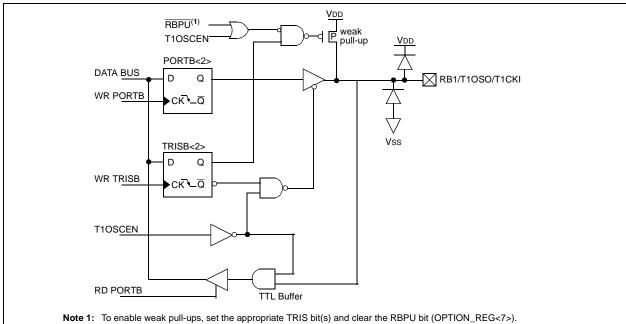

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

## PIC16C712/716

#### FIGURE 3-5: BLOCK DIAGRAM OF RB2/T10SI PIN

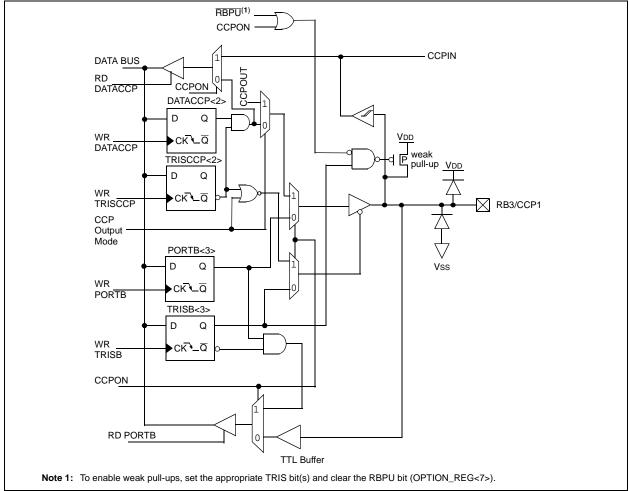

### FIGURE 3-6: BLOCK DIAGRAM OF RB3/CCP1 PIN

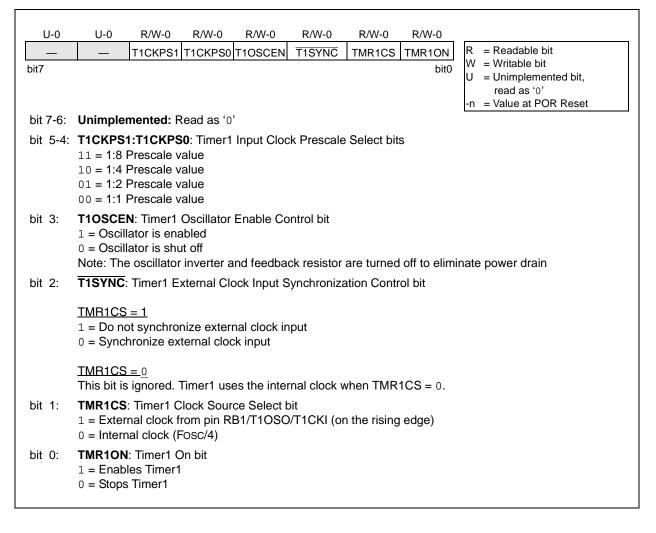

## 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- · Readable and writable (Both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-2 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

#### 5.1 Timer1 Operation

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- · As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB2/T1OSI and RB1/T1OSO/T1CKI pins become inputs. That is, the TRISB<2:1> value is ignored.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see Section 7.0 "Capture/Compare/PWM (CCP) Module(s)").

#### FIGURE 5-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

#### 6.1 Timer2 Operation

Timer2 can be used as the PWM time base for PWM mode of the CCP module.

The TMR2 register is readable and writable, and is cleared on any device Reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### 6.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

| TABLE 6-1:         REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

| Address | Name                              | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------|-------|---------|---------|---------|---------|--------|---------|---------|-------------------------|---------------------------------|

| 0Bh,8Bh | INTCON                            | GIE   | PEIE    | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1                              | —     | ADIF    |         |         | _       | CCP1IF | TMR2IF  | TMR1IF  | -00000                  | 0000 -000                       |

| 8Ch     | PIE1                              | _     | ADIE    | _       | _       | _       | CCP1IE | TMR2IE  | TMR1IE  | -0000                   | 0000 -000                       |

| 11h     | 11h TMR2 Timer2 Module's Register |       |         |         |         |         |        |         |         | 0000 0000               | 0000 0000                       |

| 12h     | T2CON                             | _     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000               | -000 0000                       |

| 92h     | n PR2 Timer2 Period Register      |       |         |         |         |         |        |         |         | 1111 1111               | 1111 1111                       |

Legend: x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

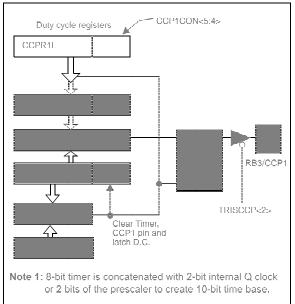

### 7.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISCCP<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the CCP1 PWM output latch to the default |

|       | low level. This is neither the PORTB I/O |

|       | data latch nor the DATACCP latch.        |

Figure 7-5 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 7.3.3** "**Set-Up for PWM Operation**".

#### FIGURE 7-5: SIMPLIFIED PWM BLOCK DIAGRAM

A PWM output (Figure 7-6) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/ period).

#### FIGURE 7-6: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 6.0    |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | "Timer2 Module") is not used in the       |  |  |  |  |  |  |  |

|       | determination of the PWM frequency. The   |  |  |  |  |  |  |  |

|       | postscaler could be used to have a servo  |  |  |  |  |  |  |  |

|       | update rate at a different frequency than |  |  |  |  |  |  |  |

|       | the PWM output.                           |  |  |  |  |  |  |  |

#### 7.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

**Note:** If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

For an example PWM period and duty cycle calculation, see the  $PIC^{\textcircled{B}}$  Mid-Range Reference Manual, (DS33023).

#### 8.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 8-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## 8.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN3:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

### TABLE 8-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock          | Source (TAD) | Device Frequency        |                         |                         |                       |  |  |  |  |

|-------------------|--------------|-------------------------|-------------------------|-------------------------|-----------------------|--|--|--|--|

| Operation         | ADCS1:ADCS0  | 20 MHz                  | 5 MHz                   | 1.25 MHz                | 333.33 kHz            |  |  |  |  |

| 2Tosc             | 00           | 100 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6 μs                  |  |  |  |  |

| 8Tosc             | 01           | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6.4 μs                  | 24 μs <sup>(3)</sup>  |  |  |  |  |

| 32Tosc            | 10           | 1.6 μs                  | 6.4 μs                  | 25.6 μs <sup>(3)</sup>  | 96 μs <b>(3)</b>      |  |  |  |  |

| RC <sup>(5)</sup> | 11           | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1)</sup> |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

- **2:** These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for Sleep operation only.

5: For extended voltage devices (LC), please refer to Electrical Specifications section.

#### 8.4 A/D Conversions

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/ DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4                         | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|-------------------------------|-------|---------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  |          | _           | (1)   | RA4                           | RA3   | RA2     | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE                          | RBIE  | TOIF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | —                             | —     | CCP1IF  | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ult Registe | er    |                               |       |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1                          | CHS0  | GO/DONE | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA Data Direction Register |       |         |        |        | 1 1111                  | 1 1111                    |

| 8Ch     | PIE1   | _        | ADIE        | _     | —                             | —     | CCP1IE  | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     | _                             | _     | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

TABLE 8-2: SUMMARY OF A/D REGISTERS

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** Reserved bits: Do Not Use.

DS41106C-page 50

## 9.0 SPECIAL FEATURES OF THE CPU

The PIC16C712/716 devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These are:

- OSC Selection

- Reset:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code protection

- ID locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

These devices have a Watchdog Timer, which can be shut off only through Configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay on power-up only and is designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry. Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of Configuration bits are used to select various options.

Additional information on special features is available in the  $PIC^{®}$  Mid-Range Reference Manual, (DS33023).

## 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h-3FFFh), which can be accessed only during programming.

| Register             | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------------------|------------------------------------|--------------------------|---------------------------------|

| W                    | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| INDF                 | N/A                                | N/A                      | N/A                             |

| TMR0                 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PCL                  | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>           |

| STATUS               | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR                  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA <sup>(4)</sup> | 0x 0000                            | xx xxxx                  | xu uuuu                         |

| PORTB <sup>(5)</sup> | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| DATACCP              | x-x                                | u-u                      | u-u                             |

| PCLATH               | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON               | 0000 -00x                          | 0000 -00u                | uuuu –uuu <b>(1)</b>            |

|                      | 0000                               | 0000                     | uuuu <b>(1)</b>                 |

| PIR1                 | -0 0000                            | -0 0000                  | -u uuuu <b>(1)</b>              |

| TMR1L                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON                | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2                 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON                | -000 0000                          | -000 0000                | -uuu uuuu                       |

| CCPR1L               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H               | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON              | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRES                | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0               | 0000 00-0                          | 0000 00-0                | uuuu uu-u                       |

| OPTION_REG           | 1111 1111                          | 1111 1111                | นนนน นนนน                       |

| TRISA                | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB                | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISCCP              | xxxx x1x1                          | xxxx x1x1                | xxxx xuxu                       |

|                      | 0000                               | 0000                     | uuuu                            |

| PIE1                 | -0 0000                            | -0 0000                  | -u uuuu                         |

| PCON                 | 0q                                 | uq                       | uq                              |

| PR2                  | 1111 1111                          | 1111 1111                | 1111 1111                       |

| ADCON1               | 000                                | 000                      | uuu                             |

#### TABLE 9-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS OF THE PIC16C712/716

**Legend:** u = unchanged, x = unknown, -= unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 9-5 for Reset value for specific condition.

4: On any device Reset, these pins are configured as inputs.

5: This is the value that will be in the port output latch.

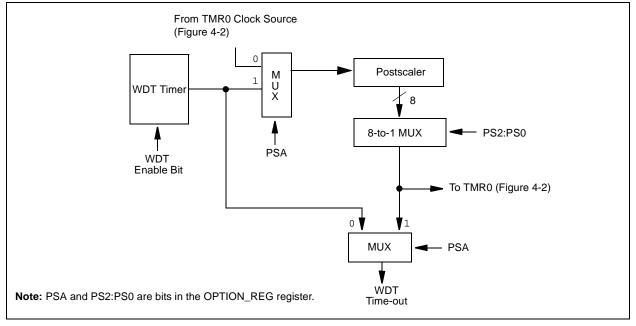

### 9.12 Watchdog Timer (WDT)

The Watchdog Timer is as a free running, on-chip, RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device have been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT Time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

The WDT can be permanently disabled by clearing Configuration bit WDTE (**Section 9.1 "Configuration Bits**").

WDT time-out period values may be found in the Electrical Specifications section under TwDT (parameter #31). Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 9-16: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bits 13:8 | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-----------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | (1)       |       | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | N/A       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

**Legend:** Shaded cells are not used by the Watchdog Timer. **Note 1:** See Figure 9-1 for operation of these bits.

#### 9.13 Power-down Mode (Sleep)

Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, powerdown the A/D and the disable external clocks. Pull all I/ O pins, that are high-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 9.13.1 WAKE-UP FROM SLEEP

The device can wake up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some peripheral interrupts.

External MCLR Reset will cause a device Reset. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT Time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. CCP Capture mode interrupt.

- 3. Special Event Trigger (Timer1 in Asynchronous mode using an external clock).

Other peripherals cannot generate interrupts, since during Sleep, no on-chip clocks are present.

## 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

#### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## PIC16C712/716

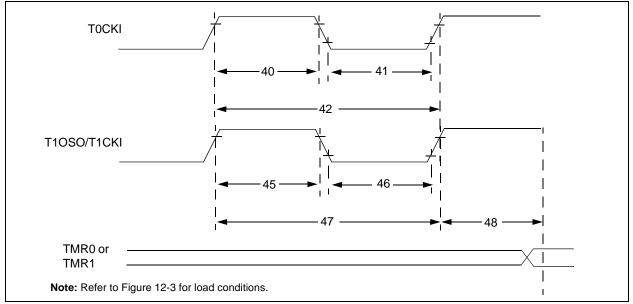

#### FIGURE 12-8: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 12-5:         TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| Param<br>No. | Sym.                                                                                       | Characteristic             |                            |                | Min.                                             | Тур† | Max.  | Units | Conditions                         |  |

|--------------|--------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------|--------------------------------------------------|------|-------|-------|------------------------------------|--|

| 40*          | Tt0H                                                                                       | T0CKI High Pulse Width No  |                            | No Prescaler   | 0.5TCY + 20                                      | _    | _     | ns    | Must also meet                     |  |

|              |                                                                                            |                            |                            | With Prescaler | 10                                               | _    | _     | ns    | parameter 42                       |  |

| 41*          | Tt0L                                                                                       | T0CKI Low Pulse Width No P |                            |                | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |  |

|              |                                                                                            |                            |                            | With Prescaler | 10                                               | —    | _     | ns    | parameter 42                       |  |

| 42*          | Tt0P                                                                                       | T0CKI Period               | TCY + 40                   | —              | —                                                | ns   |       |       |                                    |  |

|              |                                                                                            |                            |                            | With Prescaler | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | —     | ns    | N = prescale value<br>(2, 4,, 256) |  |

| 45*          | Tt1H                                                                                       | T1CKI High Time            | Synchronous, P             | Prescaler = 1  | 0.5TCY + 20                                      | -    | _     | ns    | Must also meet                     |  |

|              |                                                                                            | -                          | Synchronous,               | Standard       | 15                                               | —    | —     | ns    | parameter 47                       |  |

|              |                                                                                            |                            | Prescaler =<br>2,4,8       | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |  |

|              |                                                                                            |                            | Asynchronous               | Standard       | 30                                               | —    | —     | ns    |                                    |  |

|              |                                                                                            |                            |                            | Extended (LC)  | 50                                               | —    | _     | ns    |                                    |  |

| 46*          | Tt1L                                                                                       | T1CKI Low Time             | Synchronous, Prescaler = 1 |                | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |  |

|              |                                                                                            |                            | Synchronous,               | Standard       | 15                                               | —    |       | ns    | parameter 47                       |  |

|              |                                                                                            |                            | Prescaler =<br>2,4,8       | Extended (LC)  | 25                                               | —    | —     | ns    |                                    |  |

|              |                                                                                            |                            | Asynchronous               | Standard       | 30                                               | —    |       | ns    |                                    |  |

|              |                                                                                            |                            |                            | Extended (LC)  | 50                                               | —    |       | ns    |                                    |  |

| 47*          | Tt1P                                                                                       | T1CKI input period         | Synchronous                | Standard       | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                                                                                            |                            |                            | Extended (LC)  | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |  |

|              |                                                                                            |                            | Asynchronous               | Standard       | 60                                               | -    | —     | ns    |                                    |  |

|              |                                                                                            |                            |                            | Extended (LC)  | 100                                              | —    |       | ns    |                                    |  |

|              | Ft1 Timer1 oscillator input frequency range<br>(oscillator enabled by setting bit T1OSCEN) |                            |                            | DC             | —                                                | 200  | kHz   |       |                                    |  |

| 48           | TCKEZtmr'                                                                                  | Delay from external        | clock edge to tir          | ner increment  | 2Tosc                                            | —    | 7Tosc | —     |                                    |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

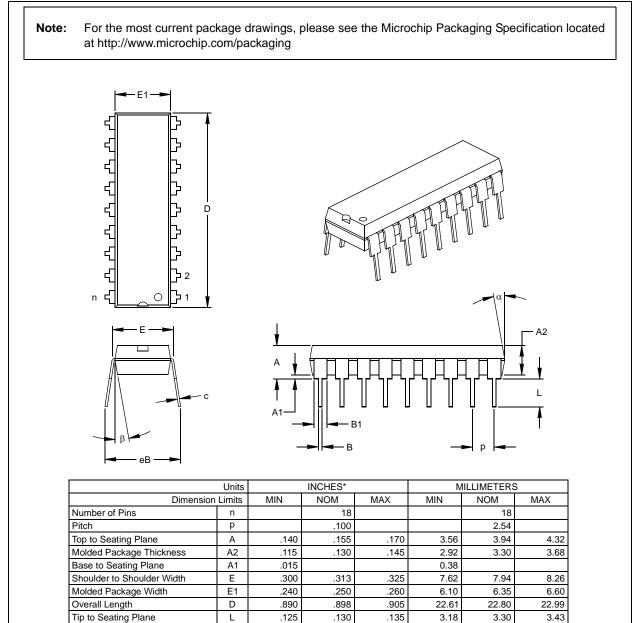

#### 13.2 Package Details

The following sections give the technical details of the packages.

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

.008

.045

.014

.310

5

5

.012

.058

.018

.370

10

10

.015

.070

.022

.430

15

15

0.20

1.14

0.36

7.87

5

5

0.29

1.46

0.46

9.40

10

10

0.38

1.78

0.56

10.92

15

15

С

B1

В

eВ

α

β

δ

JEDEC Equivalent: MS-001

Drawing No. C04-007

Lead Thickness

Upper Lead Width

Lower Lead Width

**Overall Row Spacing**

Mold Draft Angle Top

Mold Draft Angle Bottom

\* Controlling Parameter § Significant Characteristic

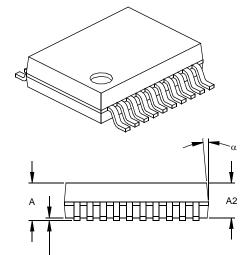

## 20-Lead Plastic Shrink Small Outline (SS) – 209 mil, 5.30 mm (SSOP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |           | INCHES* |      | MILLIMETERS |      |        |        |

|--------------------------|-----------|---------|------|-------------|------|--------|--------|

| Dimensio                 | on Limits | MIN     | NOM  | MAX         | MIN  | NOM    | MAX    |

| Number of Pins           | n         |         | 20   |             |      | 20     |        |

| Pitch                    | р         |         | .026 |             |      | 0.65   |        |

| Overall Height           | А         | .068    | .073 | .078        | 1.73 | 1.85   | 1.98   |

| Molded Package Thickness | A2        | .064    | .068 | .072        | 1.63 | 1.73   | 1.83   |

| Standoff §               | A1        | .002    | .006 | .010        | 0.05 | 0.15   | 0.25   |

| Overall Width            | Е         | .299    | .309 | .322        | 7.59 | 7.85   | 8.18   |

| Molded Package Width     | E1        | .201    | .207 | .212        | 5.11 | 5.25   | 5.38   |

| Overall Length           | D         | .278    | .284 | .289        | 7.06 | 7.20   | 7.34   |

| Foot Length              | L         | .022    | .030 | .037        | 0.56 | 0.75   | 0.94   |

| Lead Thickness           | С         | .004    | .007 | .010        | 0.10 | 0.18   | 0.25   |

| Foot Angle               | ¢         | 0       | 4    | 8           | 0.00 | 101.60 | 203.20 |

| Lead Width               | В         | .010    | .013 | .015        | 0.25 | 0.32   | 0.38   |

| Mold Draft Angle Top     | α         | 0       | 5    | 10          | 0    | 5      | 10     |

| Mold Draft Angle Bottom  | β         | 0       | 5    | 10          | 0    | 5      | 10     |

| * Controlling Decomptor  |           |         |      |             |      |        |        |

A1

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

# PIC16C712/716

| TMR1L Register 11, 31                    |

|------------------------------------------|

| Timer2                                   |

| Block Diagram 36                         |

| Postscaler. See Postscaler, Timer2       |

| PR2 Register 12, 36, 42                  |

| Prescaler. See Prescaler, Timer2         |

| T2CON Register 11, 36                    |

| TMR2 Register 11, 36                     |

| TMR2 to PR2 Match Enable (TMR2IE Bit) 16 |

| TMR2 to PR2 Match Flag (TMR2IF Bit)      |

| TMR2 to PR2 Match Interrupt 36, 37, 42   |

| Timing Diagrams                          |

| Time-out Sequence on Power-up60          |

| Wake-up from Sleep via Interrupt         |

| Timing Diagrams and Specifications       |

| A/D Conversion                           |

| Brown-out Reset (BOR) 83                 |

| Capture/Compare/PWM (CCP) 85             |

| CLKOUT and I/O                           |

| External Clock                           |

| Oscillator Start-up Timer (OST)          |

| Power-up Timer (PWRT)                    |

| Reset                                    |

| Timer0 and Timer1                        |

| Watchdog Timer (WDT)                     |

|                                          |

#### W

| W Register                             |   |

|----------------------------------------|---|

| Wake-up from Sleep                     |   |

| Wake-up from Sleep                     |   |

| Interrupts                             |   |

| MCLR Reset 59                          |   |

| Timing Diagram 65                      | 5 |

| WDT Reset 59                           | ) |

| Watchdog Timer (WDT) 51, 63            | 3 |

| Block Diagram 63                       | 3 |

| Enable (WDTE Bit) 52, 63               | 3 |

| Postscaler. See Postscaler, WDT        |   |

| Programming Considerations 63          | - |

| RC Oscillator 63                       |   |

| Time-out Period 63                     | 3 |

| Timing Diagram 83                      | 3 |

| WDT Reset, Normal Operation 54, 58, 59 | ) |

| WDT Reset, Sleep 54, 58, 59            | ) |

| WWW Address 101                        | L |

| WWW, On-Line Support 3                 | 3 |

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                               | Total Pages Sent                       |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------|----------------------------------------|--|--|--|--|--|

| Fro        | m: Name                                                                       |                                        |  |  |  |  |  |

|            | Company                                                                       |                                        |  |  |  |  |  |

|            | Address                                                                       |                                        |  |  |  |  |  |

|            | City / State / ZIP / Country                                                  |                                        |  |  |  |  |  |

|            | Telephone: ()                                                                 | FAX: ()                                |  |  |  |  |  |

|            | lication (optional):                                                          |                                        |  |  |  |  |  |

| Wo         | uld you like a reply?YN                                                       |                                        |  |  |  |  |  |

| Dev        | rice: PIC16C712/716                                                           | Literature Number: DS41106C            |  |  |  |  |  |

| Que        | ostions:                                                                      |                                        |  |  |  |  |  |

| 1.         | What are the best features of this document?                                  |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 2.         | How does this document meet your hardware and soft                            | ware development needs?                |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 3.         | 3. Do you find the organization of this document easy to follow? If not, why? |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 1          | What additions to the document do you think would er                          | phance the structure and subject?      |  |  |  |  |  |

| 4.         | what additions to the document do you think would en                          |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 5.         | What deletions from the document could be made with                           | nout affecting the overall usefulness? |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what                        | and where)?                            |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

| 7.         | How would you improve this document?                                          |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

|            |                                                                               |                                        |  |  |  |  |  |

NOTES: