Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | · ·                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | ·                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 4x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc716-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: P       | IC16C712/71 |         | DESCRIP  |                     |                                                                 |

|--------------------|-------------|---------|----------|---------------------|-----------------------------------------------------------------|

| Pin                | PIC16C      | 712/716 | Pin      | Buffer              |                                                                 |

| Name               | DIP, SOIC   | SSOP    | Туре     | Туре                | Description                                                     |

| MCLR/VPP           | 4           | 4       |          |                     |                                                                 |

| MCLR               |             |         | I        | ST                  | Master clear (Reset) input. This pin is                         |

| VPP                |             |         | Р        |                     | an active low Reset to the device.<br>Programming voltage input |

| OSC1/CLKIN         | 16          | 18      | Г        |                     |                                                                 |

| OSCI/CLKIN<br>OSCI | 10          | 10      | 1        | ST                  | Oscillator crystal input or external clock                      |

| 0001               |             |         |          | 01                  | source input. ST buffer when config-                            |

|                    |             |         |          |                     | ured in RC mode. CMOS otherwise.                                |

| CLKIN              |             |         | I        | CMOS                | External clock source input.                                    |

|                    |             |         |          |                     |                                                                 |

| OSC2/CLKOUT        | 15          | 17      |          |                     |                                                                 |

| OSC2               |             |         | 0        | _                   | Oscillator crystal output. Connects to                          |

|                    |             |         |          |                     | crystal or resonator in crystal oscillator mode.                |

| CLKOUT             |             |         | 0        |                     | In RC mode, OSC2 pin outputs                                    |

| GEROOT             |             |         | Ŭ        |                     | CLKOUT which has 1/4 the frequency                              |

|                    |             |         |          |                     | of OSC1, and denotes the instruction                            |

|                    |             |         |          |                     | cycle rate.                                                     |

|                    |             |         |          |                     | PORTA is a bidirectional I/O port.                              |

| RA0/AN0            | 17          | 19      |          |                     |                                                                 |

| RA0                |             |         | I/O      | TTL                 | Digital I/O                                                     |

| AN0                |             |         | I        | Analog              | Analog input 0                                                  |

| RA1/AN1            | 18          | 20      | 1/0      |                     |                                                                 |

| RA1<br>AN1         |             |         | I/O<br>I | TTL<br>Analog       | Digital I/O<br>Analog input 1                                   |

|                    |             | 4       | I        | Analog              | Analog input 1                                                  |

| RA2/AN2<br>RA2     | 1           | 1       | I/O      | TTL                 | Digital I/O                                                     |

| AN2                |             |         | 1/0      | Analog              | Analog input 2                                                  |

| RA3/AN3/VREF       | 2           | 2       | •        | ,                   |                                                                 |

| RA3                | 2           | £       | I/O      | TTL                 | Digital I/O                                                     |

| AN3                |             |         | I        | Analog              | Analog input 3                                                  |

| VREF               |             |         | I        | Analog              | A/D Reference Voltage input.                                    |

| RA4/T0CKI          | 3           | 3       |          |                     |                                                                 |

| RA4                |             |         | I/O      | ST/OD               | Digital I/O. Open drain when configured                         |

| TOOK               |             |         |          | OT                  | as output.                                                      |

| TOCKI              |             | input C | I        | ST<br>OS compatible | Timer0 external clock input                                     |

#### TABLE 1-1: PIC16C712/716 PINOUT DESCRIPTION

Legend:

TTL = TTL-compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

OD = Open drain output

SM = SMBus compatible input. An external resistor is required if this pin is used as an output

NPU = N-channel pull-up

PU = Weak internal pull-up

No-P diode = No P-diode to VDD

AN = Analog input or output

I = input

O = output

P = Power

L = LCD Driver

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

#### FIGURE 2-5: OPTION\_REG REGISTER (ADDRESS 81h)

| R/W-1<br>RBPU | R/W-1                                                | R/W-1<br>T0CS                                                               | R/W-1<br>T0SE | R/W-1<br>PSA | R/W-1<br>PS2           | R/W-1<br>PS1 | R/W-1<br>PS0 | R = Readable bit                                                                      |

|---------------|------------------------------------------------------|-----------------------------------------------------------------------------|---------------|--------------|------------------------|--------------|--------------|---------------------------------------------------------------------------------------|

| it7           | INTEDG                                               | 1003                                                                        | 1032          | FGA          | F 32                   | -31          | bit0         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR Reset |

| oit 7:        | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE           | 3 pull-ups                                                                  | are disal     | oled         | lividual port          | latch valu   | es           |                                                                                       |

| oit 6:        | <b>INTEDG</b> : I<br>1 = Interru<br>0 = Interru      | pt on rising                                                                | g edge of     | f RB0/INT    |                        |              |              |                                                                                       |

| oit 5:        | <b>TOCS</b> : TMI<br>1 = Transit<br>0 = Interna      | ion on RA                                                                   | 4/T0CKI       | pin          | (OUT)                  |              |              |                                                                                       |

| bit 4:        |                                                      | ent on hig                                                                  | h-to-low      | transition   | on RA4/T0<br>on RA4/T0 |              |              |                                                                                       |

| bit 3:        | <b>PSA</b> : Pres<br>1 = Presca<br>0 = Presca        | ler is assi                                                                 | gned to t     | he WDT       | module                 |              |              |                                                                                       |

| bit 2-0:      | <b>PS2:PS0</b> :                                     | Prescaler                                                                   | Rate Sel      | ect bits     |                        |              |              |                                                                                       |

|               | Bit Value                                            | TMR0 Ra                                                                     | te WD         | Γ Rate       |                        |              |              |                                                                                       |

|               | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1 :<br>3 1 :  | 2            |                        |              |              |                                                                                       |

#### 2.2.2.5 PIR1 Register

This register contains the individual flag bits for the peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-8: PIR1 REGISTER (ADDRESS 0Ch)

| U-0      | R/W-0                                                                                                                                                                                                                                                                                                                                                                       | U-0       | U-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |                         |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|-------|-------|-------|-------------------------|--|--|

| <br>bit7 | ADIF — — — CCP1IF TMR2IF TMR1IF<br>bit0 R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'                                                                                                                                                                                                                                                       |           |           |       |       |       |       |                         |  |  |

| bit 7:   | Unimpler                                                                                                                                                                                                                                                                                                                                                                    | nented: R | ead as '0 | ,     |       |       |       | -n = Value at POR Reset |  |  |

| bit 6:   |                                                                                                                                                                                                                                                                                                                                                                             |           |           |       |       |       |       |                         |  |  |

| bit 5-3: | Unimpler                                                                                                                                                                                                                                                                                                                                                                    | nented: R | ead as '0 | ,     |       |       |       |                         |  |  |

| bit 2:   | bit 2: CCP1IF: CCP1 Interrupt Flag bit<br><u>Capture Mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode:</u><br>Unused in this mode |           |           |       |       |       |       |                         |  |  |

| bit 1:   | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                   |           |           |       |       |       |       |                         |  |  |

| bit 0:   | TMR1IF: TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow                                                                                                                                                                                                                                |           |           |       |       |       |       |                         |  |  |

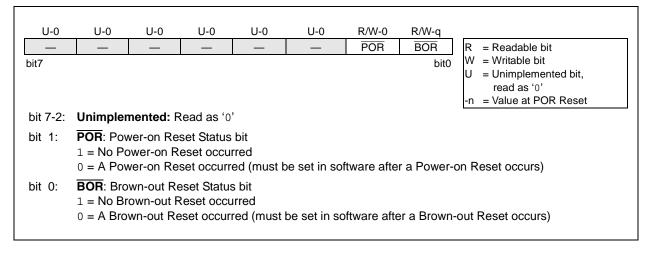

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. These devices contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition. Note: If the BODEN Configuration bit is set, BOR is '1' on Power-on Reset. If the BODEN Configuration bit is clear, BOR is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is

not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent resets to see if it is clear, indicating a brown-out has occurred.

#### FIGURE 2-9: PCON REGISTER (ADDRESS 8Eh)

| TMR1<br>Module<br>Mode | Clock Source      | Control Bits                   | TMR1 Module Operation                                                                                                                                                                                                                                                                    | PORTB<2:1> Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|------------------------|-------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Off                    | N/A               | T1CON =xx 0x00                 | Off                                                                                                                                                                                                                                                                                      | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Timer                  | Fosc/4            | T1CON =xx 0x01                 | TMR1 module uses the main<br>oscillator as clock source.<br>TMR1ON can turn on or turn off<br>Timer1.                                                                                                                                                                                    | PORTB<2:1> function as normal I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Counter                | External circuit  | T1CON =xx 0x11<br>TR1SCCP =x-1 | TMR1 module uses the external<br>signal on the RB1/T1OSO/<br>T1CKI pin as a clock source.<br>TMR1ON can turn on or turn off<br>Timer1. DT1CK can read the<br>signal on the RB1/T1OSO/<br>T1CKI pin.                                                                                      | PORTB<2> functions as normal<br>I/O. PORTB<1> always reads '0'<br>when configured as input. If<br>PORTB<1> is configured as out-<br>put, reading PORTB<1> will<br>read the data latch. Writing to<br>PORTB<1> will always store the                                                                                                                                                                                                                                                                          |  |  |

|                        | Firmware          | T1CON =xx 0x11<br>TR1SCCP =x-0 | DATACCP<0> bit drives RB1/<br>T1OSO/T1CKI and produces<br>the TMR1 clock source.<br>TMR1ON can turn on or turn off<br>Timer1. The DATACCP<0> bit,<br>DT1CK, can read and write to<br>the RB1/T1OSO/T1CKI pin.                                                                            | result in the data latch, but not to<br>the RB1/T1OSO/T1CKI pin. If<br>the TMR1CS bit is cleared<br>(TMR1 reverts to the timer<br>mode), then pin PORTB<1> will<br>be driven with the value in the<br>data latch.                                                                                                                                                                                                                                                                                            |  |  |

|                        | Timer1 oscillator | T1CON =xx 1x11                 | RB1/T1OSO/T1CKI and RB2/<br>T1OSI are configured as a 2 pin<br>crystal oscillator. RB1/T1OSI/<br>T1CKI is the clock input for<br>TMR1. TMR1ON can turn on or<br>turn off Timer1. DATACCP<1><br>bit, DT1CK, always reads '0' as<br>input and can not write to the<br>RB1/T1OSO/T1CK1 pin. | PORTB<2:1> always read '0'<br>when configured as inputs. If<br>PORTB<2:1> are configured as<br>outputs, reading PORTB<2:1><br>will read the data latches. Writ-<br>ing to PORTB<2:1> will always<br>store the result in the data<br>latches, but not to the RB2/<br>T1OSI and RB1/T1OSO/T1CKI<br>pins. If the TMR1CS and<br>T1OSCEN bits are cleared<br>(TMR1 reverts to the timer mode<br>and TMR1 oscillator is disabled),<br>then pin PORTB<2:1> will be<br>driven with the value in the data<br>latches. |  |  |

TABLE 5-1: TMR1 MODULE AND PORTB OPERATION

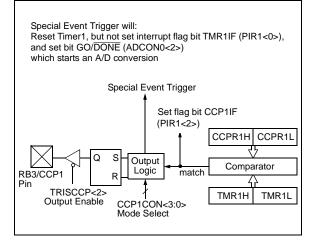

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is either:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 7-4: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as the CCP output by clearing the TRISCCP<2> bit.

| Note: | Clearing the CCP1CON register will force<br>the RB3/CCP1 compare output latch to<br>the default low level. This is neither the<br>CORTE I/O data latch part the DATACCE |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PORTB I/O data latch nor the DATACCP latch.                                                                                                                             |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP1 also starts an A/D conversion (if the A/D module is enabled).

**Note:** The Special Event Trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

#### TABLE 7-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name                                                                              | Bit 7                                | Bit 6   | Bit 5        | Bit 4        | Bit 3         | Bit 2       | Bit 1      | Bit 0     | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------------|--------------------------------------|---------|--------------|--------------|---------------|-------------|------------|-----------|-------------------------|---------------------------------|

| 07h     | DATACCP                                                                           | —                                    | —       | —            | —            | _             | DCCP        | _          | DT1CK     | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON                                                                            | GIE                                  | PEIE    | TOIE         | INTE         | RBIE          | TOIF        | INTF       | RBIF      | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1                                                                              | —                                    | ADIF    | —            | _            | _             | CCP1IF      | TMR2IF     | TMR1IF    | -0000                   | -0000                           |

| 0Eh     | TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                                      |         |              |              |               |             |            | ter       | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H                                                                             | Holding                              | Registe | r for the Mo | st Significa | nt Byte of th | e 16-bit TN | IR1 Regist | er        | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON                                                                             |                                      |         | T1CKPS1      | T1CKPS0      | T1OSCEN       | T1SYNC      | TMR1CS     | TMR10N    | 00 0000                 | uu uuuu                         |

| 15h     | CCPR1L                                                                            | Capture/                             | /Compa  | re/PWM Re    | gister 1 (LS | 6B)           |             |            |           | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H                                                                            | Capture/Compare/PWM Register 1 (MSB) |         |              |              |               |             |            | xxxx xxxx | uuuu uuuu               |                                 |

| 17h     | CCP1CON                                                                           |                                      | —       | DC1B1        | DC1B0        | CCP1M3        | CCP1M2      | CCP1M1     | CCP1M0    | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP                                                                           | _                                    | _       | —            | —            | —             | TCCP        | _          | TT1CK     | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1                                                                              | —                                    | ADIE    | _            | —            | _             | CCP1IE      | TMR2IE     | TMR1IE    | -0000                   | -0000                           |

Legend: x = unknown, u = unchanged, -- = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

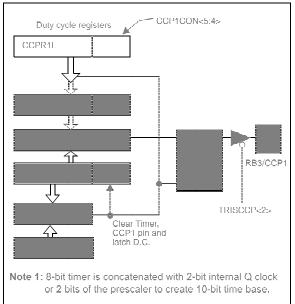

#### 7.3 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTB data latch, the TRISCCP<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the CCP1 PWM output latch to the default |

|       | low level. This is neither the PORTB I/O |

|       | data latch nor the DATACCP latch.        |

Figure 7-5 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see **Section 7.3.3** "**Set-Up for PWM Operation**".

#### FIGURE 7-5: SIMPLIFIED PWM BLOCK DIAGRAM

A PWM output (Figure 7-6) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/ period).

#### FIGURE 7-6: PWM OUTPUT

#### 7.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 6.0    |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | "Timer2 Module") is not used in the       |  |  |  |  |

|       | determination of the PWM frequency. The   |  |  |  |  |

|       | postscaler could be used to have a servo  |  |  |  |  |

|       | update rate at a different frequency than |  |  |  |  |

|       | the PWM output.                           |  |  |  |  |

#### 7.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

**Note:** If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

For an example PWM period and duty cycle calculation, see the  $PIC^{\textcircled{B}}$  Mid-Range Reference Manual, (DS33023).

#### 7.4 CCP1 Module and PORTB Operation

When the CCP module is disabled, PORTB<3> operates as a normal I/O pin. When the CCP module is enabled, PORTB<3> operation is affected. Multiplexing details of the CCP1 module are shown on PORTB<3>, refer to Figure 3.6.

Table 7-5 below shows the effects of the CCP module operation on PORTB<3>

| CCP1<br>Module<br>Mode | Control Bits                     | CCP1 Module Operation                                                                                                                                            | PORTB<3> Operation                                                                                                                           |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Off                    | CCP1CON =xx 0000                 | Off                                                                                                                                                              | PORTB<3> functions as normal I/O.                                                                                                            |

| Capture                | CCP1CON =xx 01xx<br>TRISCCP =1-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>an external circuit. The DCCP bit can<br>read the signal on the RB3/CCP1 pin. | PORTB<3> always reads '0' when<br>configured as input. If PORTB<3> is<br>configured as output, reading<br>PORTB<3> will read the data latch. |

|                        | CCP1CON =xx 01xx<br>TRISCCP =0-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>the DCCP bit. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.        | Writing to PORTB<3> will always store the result in the data latch, but it does not drive the RB3/CCP1 pin.                                  |

| Compare                | CCP1CON =xx 10xx<br>TRISCCP =0-x | The CCP1 module produces an output<br>on the RB3/CCP1 pin when a compare<br>event occurs. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.               |                                                                                                                                              |

| PWM                    | CCP1CON =xx 11xx<br>TRISCCP =0-x | The CCP1 module produces the PWM signal on the RB3/CCP1 pin. The DCCP bit can read the signal on the RB3/CCP1 pin.                                               |                                                                                                                                              |

TABLE 7-5: CCP1 MODULE AND PORTB OPERATION

#### 9.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (to a level of 1.5V-2.1V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (parameter D004). For a slow rise time, see Figure 9-5.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

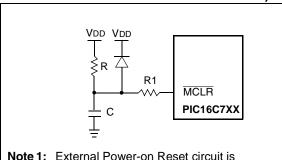

#### FIGURE 9-5:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- te1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- **2:** R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 9.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33), on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 9.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### 9.7 Brown-Out Reset (BOR)

The PIC16C712/716 members have on-chip Brownout Reset circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V, refer to VBOR parameter D005(VBOR) for a time greater than parameter (TBOR) in Table 12-6. The brown-out situation will reset the chip. A Reset is not guaranteed to occur if VDD falls below 4.0V for less than parameter (TBOR).

On any Reset (Power-on, Brown-out, Watchdog, etc.) the chip will remain in Reset until VDD rises above VBOR. The Power-up Timer will now be invoked and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

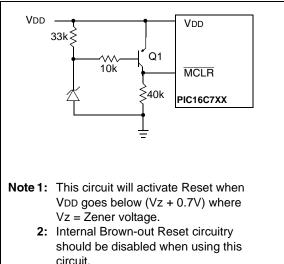

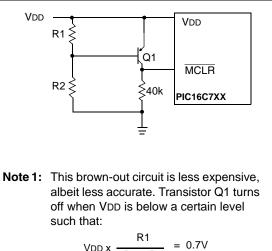

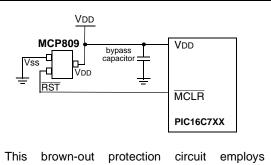

For operations where the desired brown-out voltage is other than 4V, an external brown-out circuit must be used. Figure 9-8, 9-9 and 9-10 show examples of external brown-out protection circuits.

**EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2**

$$\frac{R1}{R1 + R2} = 0$$

- 2: Internal Brown-out Reset should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### **FIGURE 9-10: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3**

Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active Reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems

#### 9.8 **Time-out Sequence**

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 9-11, Figure 9-12, and Figure 9-13 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (Figure 9-13). This is useful for testing purposes or to synchronize more than one PIC16CXXX device operating in parallel.

Table 9-5 shows the Reset conditions for some Special Function Registers, while Table 9-6 shows the Reset conditions for all the registers.

#### 9.16 In-Circuit Serial Programming™

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details on serial programming, please refer to the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) Guide, (DS30277).

#### 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB™ Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB ICE 4000 In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

#### 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 11.11 PICSTART Plus Development Programmer

The PICSTART Plus Development Programmer is an easy-to-use, low-cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. The PICSTART Plus Development Programmer supports most PIC devices in DIP packages up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus Development Programmer is CE compliant.

#### 11.12 Demonstration, Development and Evaluation Boards

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart<sup>®</sup> battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Check the Microchip web page (www.microchip.com) and the latest *"Product Selector Guide"* (DS00148) for the complete list of demonstration, development and evaluation kits.

#### 12.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55°C to +125°C                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Ambient temperature under bias<br>Storage temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65°C to +150°C                                          |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.3V to (VDD + 0.3V)                                    |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0.3V to +7.5V                                           |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0V to +13.25V                                           |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0V to +8.5V                                             |

| Total power dissipation (Note 1) (PDIP and SOIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.0W                                                    |

| Total power dissipation (Note 1) (SSOP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                         |

| Maximum current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 300 mA                                                  |

| Maximum current into VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ±20 mA                                                  |