# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc716-04i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3 PCL and PCLATH

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Mid-range devices have an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

#### 2.4 Program Memory Paging

The CALL and GOTO instructions provide 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper bit of the address is provided by PCLATH<3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bit is programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> bit is not required for the return instructions (which POPs the address from the stack).

## PIC16C712/716

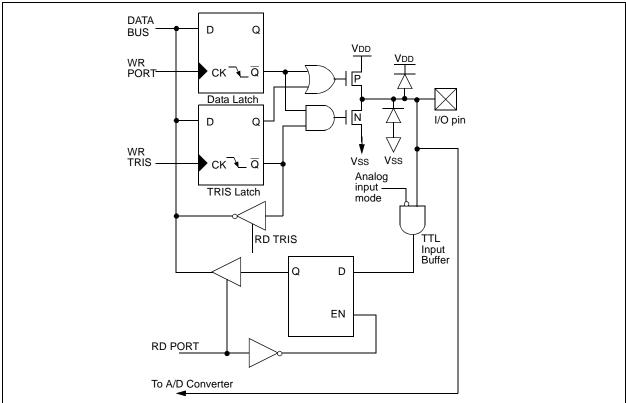

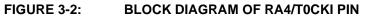

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0

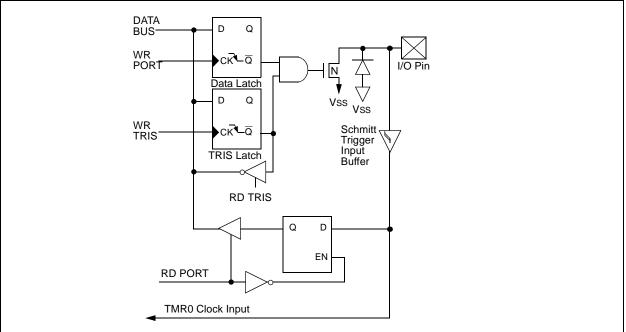

PORTB pins RB3:RB1 are multiplexed with several peripheral functions (Table 3-3). PORTB pins RB3:RB0 have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTB pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modifywrite instructions (BSF, BCF, XORWF) with TRISB as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins, RB7:RB4, are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

FIGURE 3-4: BLOCK DIAGRAM OF RB1/T10S0/T1CKI PIN

### 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register, which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 DC1B1 DC1B0 CCP1M3 CCP1M2 CCP1M1 CCP1M0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' -n = Value at POR Reset bit 7-6: Unimplemented: Read as '0' bit 5-4: DC1B1:DC1B0: PWM Least Significant bits Capture Mode: Unused Compare Mode: Unused PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L. bit 3-0: CCP1M3:CCP1M0: CCP1 Mode Select bits 0000 = Capture/Compare/PWM off (resets CCP1 module) 0100 = Capture mode, every falling edge 0101 = Capture mode, every rising edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, set output on match (CCP1IF bit is set) 1001 = Compare mode, clear output on match (CCP1IF bit is set) 1010 = Compare mode, generate software interrupt on match (CCP1IF bit is set, CCP1 pin is unaffected) 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP1 resets TMR1 and starts an A/D conversion (if A/D module is enabled)) 11xx = PWM mode

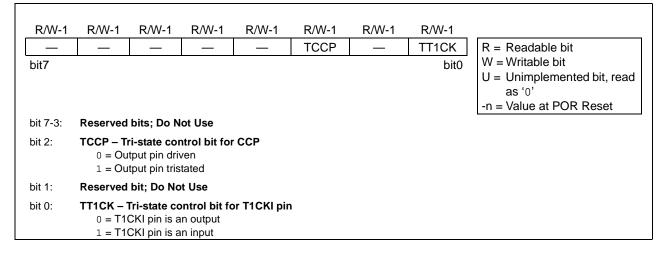

#### FIGURE 7-2: TRISCCP REGISTER (ADDRESS 87H)

Additional information on the CCP module is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

## TABLE 7-1:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

|          |                |

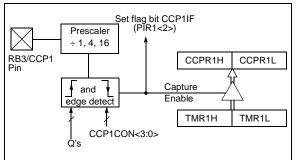

#### 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### FIGURE 7-3:

#### CAPTURE MODE OPERATION BLOCK DIAGRAM

### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCP output must be disabled by setting the TRISCCP<2> bit.

**Note:** If the RB3/CCP1 is configured as an output by clearing the TRISCCP<2> bit, a write to the DCCP bit can cause a capture condition.

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is either:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

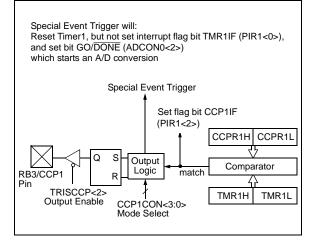

#### FIGURE 7-4: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as the CCP output by clearing the TRISCCP<2> bit.

| Note: | Clearing the CCP1CON register will force<br>the RB3/CCP1 compare output latch to<br>the default low level. This is neither the<br>CORTE I/O data latch part the DATACCE |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PORTB I/O data latch nor the DATACCP latch.                                                                                                                             |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The Special Event Trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The Special Event Trigger output of CCP1 also starts an A/D conversion (if the A/D module is enabled).

**Note:** The Special Event Trigger from the CCP1 module will not set interrupt flag bit TMR1IF (PIR1<0>).

#### TABLE 7-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address | Name    | Bit 7    | Bit 6   | Bit 5         | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0  | Value on<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|---------|----------|---------|---------------|---------------|----------------|--------------|------------|--------|-------------------------|---------------------------------|

| 07h     | DATACCP | —        | —       | —             | —             | _              | DCCP         | _          | DT1CK  | xxxx xxxx               | xxxx xuxu                       |

| 0Bh,8Bh | INTCON  | GIE      | PEIE    | TOIE          | INTE          | RBIE           | TOIF         | INTF       | RBIF   | 0000 000x               | 0000 000u                       |

| 0Ch     | PIR1    | —        | ADIF    | —             | _             | _              | CCP1IF       | TMR2IF     | TMR1IF | -0000                   | -0000                           |

| 0Eh     | TMR1L   | Holding  | Registe | r for the Lea | ast Significa | int Byte of th | ne 16-bit TI | MR1 Regis  | ter    | xxxx xxxx               | uuuu uuuu                       |

| 0Fh     | TMR1H   | Holding  | Registe | r for the Mo  | st Significa  | nt Byte of th  | e 16-bit TN  | IR1 Regist | er     | xxxx xxxx               | uuuu uuuu                       |

| 10h     | T1CON   |          |         | T1CKPS1       | T1CKPS0       | T1OSCEN        | T1SYNC       | TMR1CS     | TMR10N | 00 0000                 | uu uuuu                         |

| 15h     | CCPR1L  | Capture/ | /Compa  | re/PWM Re     | gister 1 (LS  | 6B)            |              |            |        | xxxx xxxx               | uuuu uuuu                       |

| 16h     | CCPR1H  | Capture/ | /Compa  | re/PWM Re     | gister 1 (M   | SB)            |              |            |        | xxxx xxxx               | uuuu uuuu                       |

| 17h     | CCP1CON |          | —       | DC1B1         | DC1B0         | CCP1M3         | CCP1M2       | CCP1M1     | CCP1M0 | 00 0000                 | 00 0000                         |

| 87h     | TRISCCP | _        | _       | —             | —             | —              | TCCP         | _          | TT1CK  | xxxx x1x1               | xxxx x1x1                       |

| 8Ch     | PIE1    | —        | ADIE    | _             | —             | _              | CCP1IE       | TMR2IE     | TMR1IE | -0000                   | -0000                           |

Legend: x = unknown, u = unchanged, -- = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

#### 7.4 CCP1 Module and PORTB Operation

When the CCP module is disabled, PORTB<3> operates as a normal I/O pin. When the CCP module is enabled, PORTB<3> operation is affected. Multiplexing details of the CCP1 module are shown on PORTB<3>, refer to Figure 3.6.

Table 7-5 below shows the effects of the CCP module operation on PORTB<3>

| CCP1<br>Module<br>Mode | Control Bits                     | CCP1 Module Operation                                                                                                                                            | PORTB<3> Operation                                                                                                                           |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Off                    | CCP1CON =xx 0000                 | Off                                                                                                                                                              | PORTB<3> functions as normal I/O.                                                                                                            |

| Capture                | CCP1CON =xx 01xx<br>TRISCCP =1-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>an external circuit. The DCCP bit can<br>read the signal on the RB3/CCP1 pin. | PORTB<3> always reads '0' when<br>configured as input. If PORTB<3> is<br>configured as output, reading<br>PORTB<3> will read the data latch. |

|                        | CCP1CON =xx 01xx<br>TRISCCP =0-x | The CCP1 module will capture an event<br>on the RB3/CCP1 pin which is driven by<br>the DCCP bit. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.        | Writing to PORTB<3> will always store the result in the data latch, but it does not drive the RB3/CCP1 pin.                                  |

| Compare                | CCP1CON =xx 10xx<br>TRISCCP =0-x | The CCP1 module produces an output<br>on the RB3/CCP1 pin when a compare<br>event occurs. The DCCP bit can read<br>the signal on the RB3/CCP1 pin.               |                                                                                                                                              |

| PWM                    | CCP1CON =xx 11xx<br>TRISCCP =0-x | The CCP1 module produces the PWM signal on the RB3/CCP1 pin. The DCCP bit can read the signal on the RB3/CCP1 pin.                                               |                                                                                                                                              |

TABLE 7-5: CCP1 MODULE AND PORTB OPERATION

#### 8.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 9.5TAD per 8-bit conversion. The source of the A/D conversion clock is software selectable. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal RC oscillator

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 8-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

### 8.3 Configuring Analog Port Pins

The ADCON1 and TRISA registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- 2: Analog levels on any pin that is defined as a digital input (including the AN3:AN0 pins), may cause the input buffer to consume current that is out of the devices specification.

#### TABLE 8-1: TAD vs. DEVICE OPERATING FREQUENCIES

| AD Clock          | Source (TAD) | Device Frequency        |                         |                         |                       |  |  |  |  |

|-------------------|--------------|-------------------------|-------------------------|-------------------------|-----------------------|--|--|--|--|

| Operation         | ADCS1:ADCS0  | 20 MHz                  | 5 MHz                   | 1.25 MHz                | 333.33 kHz            |  |  |  |  |

| 2Tosc             | 00           | 100 ns <sup>(2)</sup>   | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6 μs                  |  |  |  |  |

| 8Tosc             | 01           | 400 ns <sup>(2)</sup>   | 1.6 μs                  | 6.4 μs                  | 24 μs <sup>(3)</sup>  |  |  |  |  |

| 32Tosc            | 10           | 1.6 μs                  | 6.4 μs                  | 25.6 μs <b>(3)</b>      | 96 μs <b>(3)</b>      |  |  |  |  |

| RC <sup>(5)</sup> | 11           | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1)</sup> |  |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The RC source has a typical TAD time of 4  $\mu$ s.

- **2:** These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When device frequency is greater than 1 MHz, the RC A/D conversion clock source is recommended for Sleep operation only.

5: For extended voltage devices (LC), please refer to Electrical Specifications section.

#### 8.4 A/D Conversions

| Note: | The GO/DONE bit should NOT be set in        |

|-------|---------------------------------------------|

|       | the same instruction that turns on the A/D. |

#### 8.5 Use of the CCP Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "Special Event Trigger" sets the GO/ DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

| Address | Name   | Bit 7    | Bit 6       | Bit 5 | Bit 4   | Bit 3                         | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|----------|-------------|-------|---------|-------------------------------|---------|--------|--------|-------------------------|---------------------------|

| 05h     | PORTA  |          | _           | (1)   | RA4     | RA3                           | RA2     | RA1    | RA0    | xx xxxx                 | xu uuuu                   |

| 0Bh,8Bh | INTCON | GIE      | PEIE        | TOIE  | INTE    | RBIE                          | TOIF    | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch     | PIR1   | _        | ADIF        | _     | —       | —                             | CCP1IF  | TMR2IF | TMR1IF | -0000                   | -0000                     |

| 1Eh     | ADRES  | A/D Resu | ult Registe | er    |         |                               |         |        |        | xxxx xxxx               | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1    | ADCS0       | CHS2  | CHS1    | CHS0                          | GO/DONE | _      | ADON   | 0000 00-0               | 0000 00-0                 |

| 85h     | TRISA  | _        | _           | (1)   | PORTA I | PORTA Data Direction Register |         |        |        | 1 1111                  | 1 1111                    |

| 8Ch     | PIE1   | _        | ADIE        | _     | —       | —                             | CCP1IE  | TMR2IE | TMR1IE | -0000                   | -0 0000                   |

| 9Fh     | ADCON1 |          | _           | _     | _       | _                             | PCFG2   | PCFG1  | PCFG0  | 000                     | 000                       |

TABLE 8-2: SUMMARY OF A/D REGISTERS

**Legend:** x = unknown, u = unchanged, — = unimplemented read as '0'. Shaded cells are not used for A/D conversion. **Note 1:** Reserved bits: Do Not Use.

DS41106C-page 50

#### FIGURE 9-1: CONFIGURATION WORD

|        |                                                             |        |                                      |          |          |         |                |        |         |           |           |       | •           |                        |

|--------|-------------------------------------------------------------|--------|--------------------------------------|----------|----------|---------|----------------|--------|---------|-----------|-----------|-------|-------------|------------------------|

| CP1    | CPO                                                         | CP1    | CP0                                  | CP1      | CP0      | —       | BODEN          | CP1    | CP0     | PWRTE     | WDTE      | FOSC1 | FOSC0       | Register:CONFIG        |

| bit13  |                                                             |        | bit0 Address2007h                    |          |          |         |                |        |         |           |           |       |             |                        |

| bit 12 | bit 13-8, 5-4: CP1:CP0: Code Protection bits <sup>(2)</sup> |        |                                      |          |          |         |                |        |         |           |           |       |             |                        |

| DILTO  | Code Protection for 2K Program memory (PIC16C716)           |        |                                      |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             |        | 11 = Programming code protection off |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             |        | = 0400                               |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             |        | = 0200                               |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             |        | = 0000                               |          |          | •       |                |        |         |           |           |       |             |                        |

| bit 13 | 3-8, 5                                                      | -4:    |                                      |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             | Coc    | le Prot                              | ection   | for 1k   | (Prog   | ram mem        | ory bi | ts (PIC | C16C712)  |           |       |             |                        |

|        |                                                             | 11:    | = Prog                               | rammi    | ing coo  | de pro  | tection of     | f      |         |           |           |       |             |                        |

|        |                                                             |        | •                                    |          | •        | •       | tection of     | f      |         |           |           |       |             |                        |

|        |                                                             |        | = 0200                               |          |          | •       |                |        |         |           |           |       |             |                        |

|        |                                                             | 00 :   | = 0000                               | h-03F    | Fh coo   | de-pro  | tected         |        |         |           |           |       |             |                        |

| bit 7  |                                                             | 11     |                                      |          | J. D     | -l ()   | .,             |        |         |           |           |       |             |                        |

| bit 6  | -                                                           |        |                                      |          |          |         | ı<br>nable bit | (1)    |         |           |           |       |             |                        |

| DIL U. | •                                                           |        | BOR 6                                |          |          |         |                | ( )    |         |           |           |       |             |                        |

|        |                                                             | _      | BOR                                  |          |          |         |                |        |         |           |           |       |             |                        |

| bit 3  |                                                             | -      |                                      |          |          | ner Fr  | hable bit (    | 1)     |         |           |           |       |             |                        |

| 511 0  | •                                                           |        | PWRT                                 |          | •        |         |                |        |         |           |           |       |             |                        |

|        |                                                             | -      | PWRT                                 |          |          |         |                |        |         |           |           |       |             |                        |

| bit 2  | :                                                           | WD     | TE: W                                | atchdo   | og Tim   | er Ena  | able bit       |        |         |           |           |       |             |                        |

|        |                                                             | 1 =    | WDT (                                | enable   | ed       |         |                |        |         |           |           |       |             |                        |

|        |                                                             | 0 =    | WDT (                                | disable  | əd       |         |                |        |         |           |           |       |             |                        |

| bit 1- | -0:                                                         | FOS    | SC1:F                                | OSC0:    | : Oscill | ator S  | election b     | oits   |         |           |           |       |             |                        |

|        |                                                             | 11:    | = RC c                               | oscillat | or       |         |                |        |         |           |           |       |             |                        |

|        |                                                             | 10:    | = HS o                               | scillat  | or       |         |                |        |         |           |           |       |             |                        |

|        |                                                             | 01:    | 01 = XT oscillator                   |          |          |         |                |        |         |           |           |       |             |                        |

|        |                                                             | 00:    | = LP o                               | scillato | or       |         |                |        |         |           |           |       |             |                        |

| Note   | 4.                                                          | Enabli | na Bro                               |          |          | st outo | matically      | onabl  |         |           | mor (D\// |       | dloce of th |                        |

| note   |                                                             |        | -                                    |          |          |         |                |        |         | vn-out Re |           | , .   | uiess 01 (f | he value of bit PWRTE. |

|        | 2:                                                          |        |                                      |          |          |         |                |        |         |           |           |       | ntection s  | cheme listed.          |

|        | ۷.                                                          |        |                                      | 1.01 0   | Pairs    | nave    | o bo give      | in une | Same    |           |           |       |             |                        |

#### 9.4 Power-On Reset (POR)

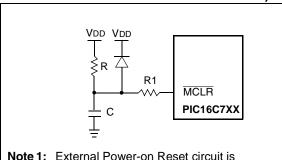

A Power-on Reset pulse is generated on-chip when VDD rise is detected (to a level of 1.5V-2.1V). To take advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified (parameter D004). For a slow rise time, see Figure 9-5.

When the device starts normal operation (exits the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

#### FIGURE 9-5:

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- te1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- **2:** R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- **3:**  $R1 = 100\Omega$  to  $1 k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 9.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed nominal time-out (parameter #33), on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A Configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 9.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter #32). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### 9.7 Brown-Out Reset (BOR)

The PIC16C712/716 members have on-chip Brownout Reset circuitry. A Configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V, refer to VBOR parameter D005(VBOR) for a time greater than parameter (TBOR) in Table 12-6. The brown-out situation will reset the chip. A Reset is not guaranteed to occur if VDD falls below 4.0V for less than parameter (TBOR).

On any Reset (Power-on, Brown-out, Watchdog, etc.) the chip will remain in Reset until VDD rises above VBOR. The Power-up Timer will now be invoked and will keep the chip in Reset an additional 72 ms.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-Up Timer will execute a 72 ms Reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 9-7 shows typical Brown-out situations.

For operations where the desired brown-out voltage is other than 4V, an external brown-out circuit must be used. Figure 9-8, 9-9 and 9-10 show examples of external brown-out protection circuits.

#### 9.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON has two bits.

Bit 0 is Brown-out Reset Status bit,  $\overline{\text{BOR}}$ . If the BODEN Configuration bit is set,  $\overline{\text{BOR}}$  is '1' on Power-on Reset. If the BODEN Configuration bit is clear,  $\overline{\text{BOR}}$  is unknown on Power-on Reset. The BOR Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (the BODEN Configuration bit is clear). BOR must then be set by the user and checked on subsequent Resets to see if it is clear, indicating a brown-out has occurred.

Bit 1 is  $\overrightarrow{\text{POR}}$  (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 9-3:TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up              | Brown-out        | Wake-up from |  |

|--------------------------|------------------|------------------|------------------|--------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0 | <b>PWRTE</b> = 1 | Brown-out        | Sleep        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc         | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms            | _                | 72 ms            | —            |  |

#### TABLE 9-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                                         |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | x   | 0  | x  | legal, TO is set on POR                                 |  |  |  |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | ICLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |

#### TABLE 9-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

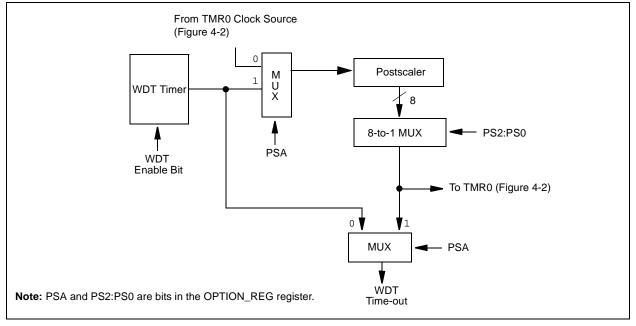

#### 9.12 Watchdog Timer (WDT)

The Watchdog Timer is as a free running, on-chip, RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device have been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT Time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

The WDT can be permanently disabled by clearing Configuration bit WDTE (**Section 9.1 "Configuration Bits**").

WDT time-out period values may be found in the Electrical Specifications section under TwDT (parameter #31). Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

**Note:** The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset condition.

**Note:** When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 9-15: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 9-16: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bits 13:8 | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-----------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h   | Config. bits | (1)       |       | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION_REG   | N/A       | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

**Legend:** Shaded cells are not used by the Watchdog Timer. **Note 1:** See Figure 9-1 for operation of these bits.

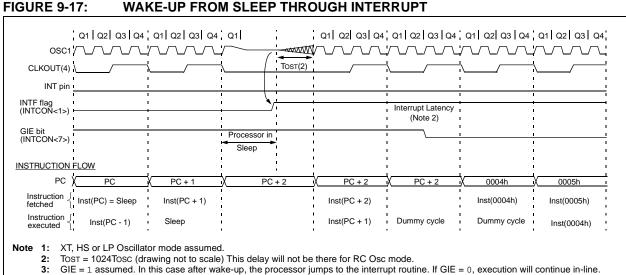

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### WAKE-UP USING INTERRUPTS 9.13.2

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

· If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the  $\overline{TO}$  bit will not be set and  $\overline{PD}$  bits will not be cleared.

• If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the  $\overline{PD}$  bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a **SLEEP** instruction.

4:

CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 9.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip  | does   | not   | recommend | code |

|-------|------------|--------|-------|-----------|------|

|       | protecting | window | ved c | levices.  |      |

#### **ID** Locations 9.15

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

### 12.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings (†)

| Ambient temperature under bias                                          | 55°C to +125°C                                          |

|-------------------------------------------------------------------------|---------------------------------------------------------|

| Ambient temperature under bias<br>Storage temperature                   | 65°C to +150°C                                          |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)      | 0.3V to (VDD + 0.3V)                                    |

| Voltage on VDD with respect to Vss                                      | 0.3V to +7.5V                                           |

| Voltage on MCLR with respect to Vss (Note 2)                            | 0V to +13.25V                                           |

| Voltage on RA4 with respect to Vss                                      | 0V to +8.5V                                             |

| Total power dissipation (Note 1) (PDIP and SOIC)                        | 1.0W                                                    |

| Total power dissipation (Note 1) (SSOP)                                 |                                                         |

| Maximum current out of Vss pin                                          | 300 mA                                                  |

| Maximum current into VDD pin                                            |                                                         |

| Input clamp current, Iк (VI < 0 or VI > VDD)                            | ±20 mA                                                  |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                          | ±20 mA                                                  |

| Maximum output current sunk by any I/O pin                              |                                                         |

| Maximum output current sourced by any I/O pin                           | 25 mA                                                   |

| Maximum current sunk by PORTA and PORTB (combined)                      | 200 mA                                                  |

| Maximum current sourced by PORTA and PORTB (combined)                   | 200 mA                                                  |

| Note 4. Deven discipation is calculated as follows: Ddis (IDD (IDD (IDD | $\lambda(a, y) = \{a, y\} = \sum \{\lambda(a, y) = x\}$ |

- **Note 1:** Power dissipation is calculated as follows:  $Pdis = VDD \times \{IDD \sum IOH\} + \sum \{(VDD-VOH) \times IOH\} + \sum (VOI \times IOL)$ **2:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latch-up.

- Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the MCLR/VPP pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CHA       | RACTE | RISTICS                                                | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for extendedOperating voltage VDD range as described in DC spec Section 12.1"DC Characteristics: PIC16C712/716-04 (Commercial, Industrial,Extended) PIC16C712/716-20 (Commercial, Industrial, |            |     |    |                                                                   |  |  |  |  |

|--------------|-------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|----|-------------------------------------------------------------------|--|--|--|--|

|              |       |                                                        | Extended)" and Section 12.2 "DC Characteristics: PIC16LC712<br>716-04 (Commercial, Industrial)"                                                                                                                                                                                                                                                                                                                                    |            |     |    |                                                                   |  |  |  |  |

| Param<br>No. | Sym.  | Characteristic                                         | Min.                                                                                                                                                                                                                                                                                                                                                                                                                               | Conditions |     |    |                                                                   |  |  |  |  |

| D080         | Vol   | Output Low Voltage<br>I/O ports                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | _          | 0.6 | V  | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |  |

|              |       |                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                  | —          | 0.6 | V  | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |  |

| D083         |       | OSC2/CLKOUT<br>(RC Osc mode)                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                  | -          | 0.6 | V  | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                       |  |  |  |  |

|              |       |                                                        | —                                                                                                                                                                                                                                                                                                                                                                                                                                  | —          | 0.6 | V  | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |  |

| D090         | Vон   | Output High Voltage<br>I/O ports (Note 3)              | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                            | _          | _   | V  | ІОн = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                            | -          | _   | V  | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                     |  |  |  |  |

| D092         |       | OSC2/CLKOUT (RC Osc<br>mode)                           | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                            | -          | _   | V  | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                      |  |  |  |  |

|              |       |                                                        | Vdd-0.7                                                                                                                                                                                                                                                                                                                                                                                                                            | —          | —   | V  | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                     |  |  |  |  |

| D150*        | Vod   | Open-Drain High Voltage                                | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | _          | 8.5 | V  | RA4 pin                                                           |  |  |  |  |

| D100         | Cosc2 | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | _          | 15  | pF | In XT, HS and LP modes when external clock is used to drive OSC1. |  |  |  |  |

| D101         | Сю    | All I/O pins and OSC2 (in RC mode)                     | _                                                                                                                                                                                                                                                                                                                                                                                                                                  | —          | 50  | pF |                                                                   |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC Oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC MCU be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

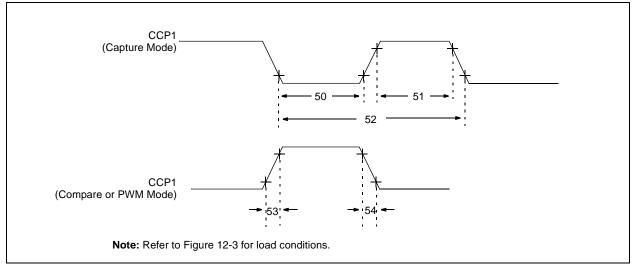

#### TABLE 12-6: CAPTURE/COMPARE/PWM REQUIREMENTS

| Param<br>No. | Sym. | Characteristic       | Characteristic      |               |             | Тур† | Max | Units | Conditions                         |

|--------------|------|----------------------|---------------------|---------------|-------------|------|-----|-------|------------------------------------|

| 50*          | TccL | CCP1 input low       | No Prescaler        |               | 0.5TCY + 20 | -    | _   | ns    |                                    |

|              |      | time                 | With Prescaler      | Standard      | 10          | -    | _   | ns    |                                    |

|              |      |                      |                     | Extended (LC) | 20          | -    | _   | ns    |                                    |

| 51*          | TccH | CCP1 input high      | No Prescaler        | ·             | 0.5Tcy + 20 | —    |     | ns    |                                    |

|              | time |                      | With Prescaler      | Standard      | 10          | -    | _   | ns    |                                    |

|              |      |                      |                     | Extended (LC) | 20          | -    | _   | ns    |                                    |

| 52*          | TccP | CCP1 input period    |                     |               |             |      | _   | ns    | N = prescale value<br>(1,4, or 16) |

| 53*          | TccR | CCP1 output rise ti  | me                  | Standard      | —           | 10   | 25  | ns    |                                    |

|              |      |                      | Extended (LC)       | —             | 25          | 45   | ns  |       |                                    |

| 54*          | TccF | CCP1 output fall tir | P1 output fall time |               | —           | 10   | 25  | ns    |                                    |

|              |      |                      |                     | Extended (LC) | —           | 25   | 45  | ns    |                                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

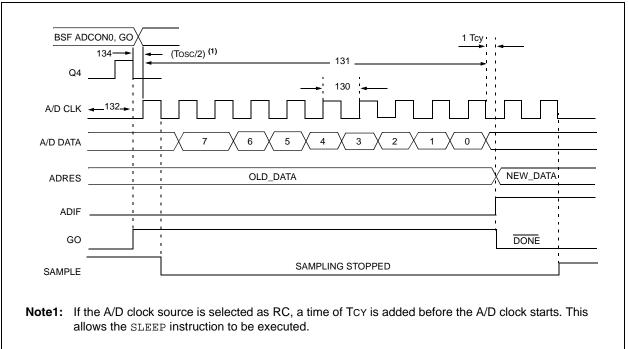

#### TABLE 12-8: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym. | Characteristic                                       |                  | Min.     | Тур†     | Max. | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|------------------------------------------------------|------------------|----------|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                     | Standard         | 1.6      |          | _    | μS    | Tosc based, VREF $\geq$ 3.0V                                                                                                                                                                                                  |

|              |      |                                                      | Extended (LC)    | 2.0      | —        | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                                      | Standard         | 2.0      | 4.0      | 6.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                                      | Extended (LC)    | 3.0      | 6.0      | 9.0  | μS    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (not including S/H time)<br>(Note 1) |                  | 11       | —        | 11   | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                                     |                  | (Note 2) | 20       | —    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                      |                  | 5*       | _        | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |                  | _        | Tosc/2 § | _    |       | If the A/D clock source is selected<br>as RC, a time of Tcy is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from conve                                 | rt Æ sample time | 1.5 §    | —        | _    | TAD   |                                                                                                                                                                                                                               |

: \* These parameters are characterized but not tested.

: † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

: § This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 9.1 "Configuration Bits" for min. conditions.

## PIC16C712/716

NOTES:

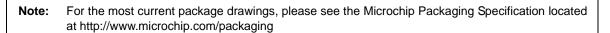

|                          | Units |      | INCHES* |      | MILLIMETERS |       |       |  |

|--------------------------|-------|------|---------|------|-------------|-------|-------|--|

| Dimensi                  | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |  |

| Number of Pins           | n     |      | 18      |      |             | 18    |       |  |

| Pitch                    | р     |      | .050    |      |             | 1.27  |       |  |

| Overall Height           | А     | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2    | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1    | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | Е     | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1    | .291 | .295    | .299 | 7.39        | 7.49  | 7.59  |  |

| Overall Length           | D     | .446 | .454    | .462 | 11.33       | 11.53 | 11.73 |  |

| Chamfer Distance         | h     | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |  |

| Foot Length              | L     | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |  |

| Foot Angle               | ¢     | 0    | 4       | 8    | 0           | 4     | 8     |  |

| Lead Thickness           | С     | .009 | .011    | .012 | 0.23        | 0.27  | 0.30  |  |

| Lead Width               | В     | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |  |

| Mold Draft Angle Top     | α     | 0    | 12      | 15   | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom  | β     | 0    | 12      | 15   | 0           | 12    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051