Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             |                                                                           |

| Core Size                  | -                                                                         |

| Speed                      | -                                                                         |

| Connectivity               | -                                                                         |

| Peripherals                | -                                                                         |

| Number of I/O              | -                                                                         |

| Program Memory Size        | -                                                                         |

| Program Memory Type        |                                                                           |

| EEPROM Size                |                                                                           |

| RAM Size                   | ·                                                                         |

| Voltage - Supply (Vcc/Vdd) |                                                                           |

| Data Converters            | ·                                                                         |

| Oscillator Type            | -                                                                         |

| Operating Temperature      |                                                                           |

| Mounting Type              | ·                                                                         |

| Package / Case             | -                                                                         |

| Supplier Device Package    | -                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11u34fbd48-421 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 32-bit ARM Cortex-M0 microcontroller

| Type number        | Package |                                                                                    |          |

|--------------------|---------|------------------------------------------------------------------------------------|----------|

|                    | Name    | Description                                                                        | Version  |

| LPC11U36FBD64/401  | LQFP64  | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |

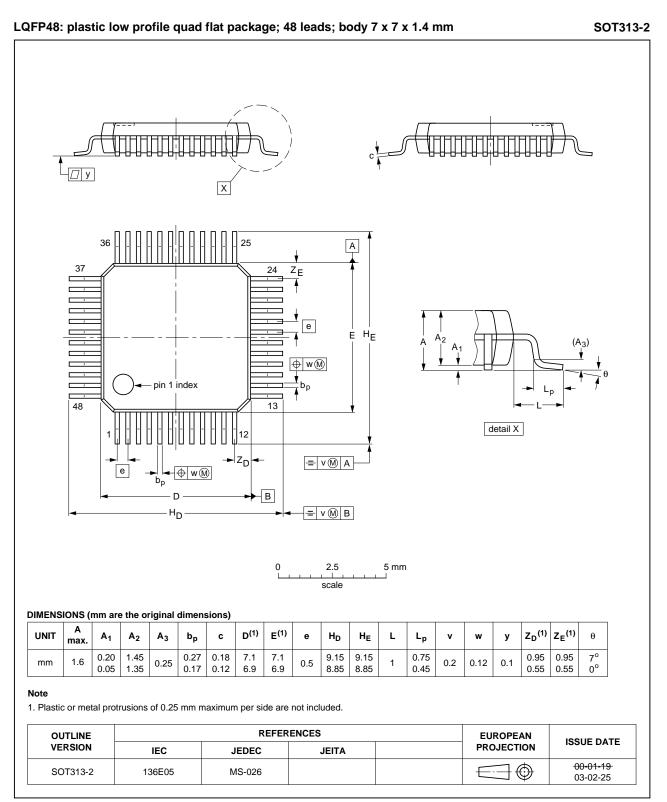

| LPC11U37FBD48/401  | LQFP48  | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm   | SOT313-2 |

| LPC11U37HFBD64/401 | LQFP64  | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |

| LPC11U37FBD64/501  | LQFP64  | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |

## Table 1. Ordering information ...continued

## 4.1 Ordering options

### Table 2. Ordering options

| Type number        |             |              |             | B              |              |                                |             |       |                          |     |            |              |           |

|--------------------|-------------|--------------|-------------|----------------|--------------|--------------------------------|-------------|-------|--------------------------|-----|------------|--------------|-----------|

|                    | Flash in kB | EEPROM in kB | SRAM0 in kB | USB SRAM in kB | SRAM1 in kB  | Total<br>SRAM in kB <u>[1]</u> | I/O Handler | USART | l <sup>2</sup> C-bus FM+ | SSP | USB device | ADC channels | GPIO pins |

| LPC11U34FHN33/311  | 40          | 4            | 8           | -              | -            | 8                              | no          | 1     | 1                        | 2   | 1          | 8            | 26        |

| LPC11U34FBD48/311  | 40          | 4            | 8           | -              | -            | 8                              | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U34FHN33/421  | 48          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 26        |

| LPC11U34FBD48/421  | 48          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U35FHN33/401  | 64          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 26        |

| LPC11U35FBD48/401  | 64          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U35FBD64/401  | 64          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 54        |

| LPC11U35FHI33/501  | 64          | 4            | 8           | 2              | 2 <u>[1]</u> | 12                             | no          | 1     | 1                        | 2   | 1          | 8            | 26        |

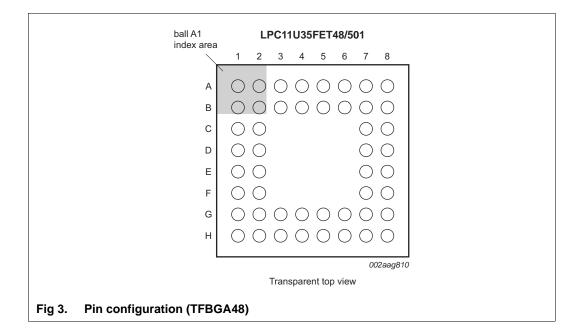

| LPC11U35FET48/501  | 64          | 4            | 8           | 2              | 2 <u>[1]</u> | 12                             | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U36FBD48/401  | 96          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U36FBD64/401  | 96          | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 54        |

| LPC11U37FBD48/401  | 128         | 4            | 8           | 2              | -            | 10                             | no          | 1     | 1                        | 2   | 1          | 8            | 40        |

| LPC11U37HFBD64/401 | 128         | 4            | 8           | 2              | 2 <u>[2]</u> | 10                             | yes         | 1     | 1                        | 2   | 1          | 8            | 54        |

| LPC11U37FBD64/501  | 128         | 4            | 8           | 2              | 2 <u>[1]</u> | 12                             | no          | 1     | 1                        | 2   | 1          | 8            | 54        |

[1] For general-purpose use.

[2] For I/O Handler use only.

### 32-bit ARM Cortex-M0 microcontroller

Product data sheet

### 32-bit ARM Cortex-M0 microcontroller

## **NXP Semiconductors**

# LPC11U3x

## 32-bit ARM Cortex-M0 microcontroller

### Table 3.Pin description

| Symbol              | Pin HVQFN33 | Pin TFBGA48 | Pin LQFP48 | Pin LQFP64 |            | Reset<br>state<br>[1] | Туре | Description                                                                                                                                                                       |

|---------------------|-------------|-------------|------------|------------|------------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

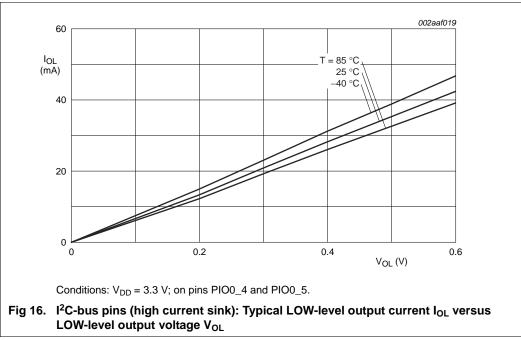

| PIO0_4/SCL/IOH_2    | 10          | G3          | 15         | 20         | <u>[4]</u> | I; IA                 | I/O  | <b>PIO0_4</b> — General purpose digital input/output pin (open-drain).                                                                                                            |

|                     |             |             |            |            |            | -                     | I/O  | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is<br>selected in the I/O configuration register. |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_2</b> — I/O Handler input/output 2.<br>LPC11U37HFBD64/401 only.                                                                                                            |

| PIO0_5/SDA/IOH_3    | 11          | H3          | 16         | 21         | <u>[4]</u> | I; IA                 | I/O  | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                            |

|                     |             |             |            |            |            | -                     | I/O  | <b>SDA</b> — I <sup>2</sup> C-bus data input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.     |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_3</b> — I/O Handler input/output 3.<br>LPC11U37HFBD64/401 only.                                                                                                            |

| PIO0_6/USB_CONNECT/ | 15          | H6          | 22         | 29         | [3]        | I; PU                 | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                                                                                |

| SCK0/IOH_4          |             |             |            |            |            | -                     | 0    | <b>USB_CONNECT</b> — Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature.                                     |

|                     |             |             |            |            |            | -                     | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                                     |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_4</b> — I/O Handler input/output 4.<br>LPC11U37HFBD64/401 only.                                                                                                            |

| PIO0_7/CTS/IOH_5    | 16          | G7          | 23         | 30         | [5]        | I; PU                 | I/O  | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                            |

|                     |             |             |            |            |            | -                     | I    | <b>CTS</b> — Clear To Send input for USART.                                                                                                                                       |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_5</b> — I/O Handler input/output 5.<br>(LPC11U37HFBD64/401 only.)                                                                                                          |

| PIO0_8/MISO0/       | 17          | F8          | 27         | 36         | [3]        | I; PU                 | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                                |

| CT16B0_MAT0/R/IOH_6 |             |             |            |            |            | -                     | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                             |

|                     |             |             |            |            |            | -                     | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                  |

|                     |             |             |            |            |            | -                     | -    | Reserved.                                                                                                                                                                         |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_6</b> — I/O Handler input/output 6.<br>(LPC11U37HFBD64/401 only.)                                                                                                          |

| PIO0_9/MOSI0/       | 18          | F7          | 28         | 37         | [3]        | I; PU                 | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                                |

| CT16B0_MAT1/R/IOH_7 |             |             |            |            |            | -                     | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                             |

|                     |             |             |            |            |            | -                     | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                  |

|                     |             |             |            |            |            | -                     | -    | Reserved.                                                                                                                                                                         |

|                     |             |             |            |            |            | -                     | I/O  | <b>IOH_7</b> — I/O Handler input/output 7.<br>(LPC11U37HFBD64/401 only.)                                                                                                          |

# 7. Functional description

### 7.1 On-chip flash programming memory

The LPC11U3x contain up to 128 kB on-chip flash program memory. The flash can be programmed using In-System Programming (ISP) or In-Application Programming (IAP) via the on-chip boot loader software.

The flash memory is divided into 4 kB sectors with each sector consisting of 16 pages. Individual pages can be erased using the IAP erase page command.

## 7.2 EEPROM

The LPC11U3x contain 4 kB of on-chip byte-erasable and byte-programmable EEPROM data memory. The EEPROM can be programmed using In-Application Programming (IAP) via the on-chip boot loader software.

### 7.3 SRAM

The LPC11U3x contain a total of 8 kB, 10 kB, or 12 kB on-chip static RAM memory.

On the LPC11U37HFBD64/401, the 2 kB SRAM1 region at location 0x2000 0000 to 0x2000 07FFF is used for the I/O Handler software library. Do not use this memory location for data or other user code.

## 7.4 On-chip ROM

The on-chip ROM contains the boot loader and the following Application Programming Interfaces (APIs):

- In-System Programming (ISP) and In-Application Programming (IAP) support for flash including IAP erase page command.

- IAP support for EEPROM

- USB API

- Power profiles for configuring power consumption and PLL settings

- 32-bit integer division routines

## 7.5 Memory map

The LPC11U3x incorporates several distinct memory regions, shown in the following figures. <u>Figure 6</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB (Advanced High-performance Bus) peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals. The APB (Advanced Peripheral Bus) peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kB of space. This addressing scheme allows simplifying the address decoding for each peripheral.

### 7.8.1 Features

- GPIO pins can be configured as input or output by software.

- All GPIO pins default to inputs with interrupt disabled at reset.

- Pin registers allow pins to be sensed and set individually.

- Up to eight GPIO pins can be selected from all GPIO pins to create an edge- or level-sensitive GPIO interrupt request.

- Any pin or pins in each port can trigger a port interrupt.

### 7.9 USB interface

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot-plugging and dynamic configuration of the devices. The host controller initiates all transactions.

The LPC11U3x USB interface consists of a full-speed device controller with on-chip PHY (PHYsical layer) for device functions.

**Remark:** Configure the LPC11U3x in default power mode with the power profiles before using the USB (see <u>Section 7.18.5.1</u>). Do not use the USB with the part in performance, efficiency, or low-power mode.

### 7.9.1 Full-speed USB device controller

The device controller enables 12 Mbit/s data exchange with a USB Host controller. It consists of a register interface, serial interface engine, and endpoint buffer memory. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. If enabled, an interrupt is generated.

### 7.9.1.1 Features

- Dedicated USB PLL available.

- Fully compliant with USB 2.0 specification (full speed).

- Supports 10 physical (5 logical) endpoints including one control endpoint.

- Single and double buffering supported.

- Each non-control endpoint supports bulk, interrupt, or isochronous endpoint types.

- Supports wake-up from Deep-sleep mode and Power-down mode on USB activity and remote wake-up.

- Supports SoftConnect.

## 7.10 I/O Handler (LPC11U37HFBD64/401 only)

The I/O Handler is a software library-supported hardware engine for emulating serial interfaces and off-loading the CPU for processing-intensive functions. The I/O Handler can emulate, among others, DMA and serial interfaces such as UART, I<sup>2</sup>C, or I<sup>2</sup>S with no or very low additional CPU load. The software libraries are available with supporting

# 8. Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                               | Conditions                                                         |            | Min  | Max   | Unit |

|------------------------|-----------------------------------------|--------------------------------------------------------------------|------------|------|-------|------|

| V <sub>DD</sub>        | supply voltage (core and external rail) |                                                                    | [2]        | -0.5 | +4.6  | V    |

| VI                     | input voltage                           | 5 V tolerant digital I/O pins; $V_{DD} \ge 1.8 \text{ V}$          | [5][2]     | -0.5 | +5.5  | V    |

|                        |                                         | V <sub>DD</sub> = 0 V                                              | ,          | -0.5 | +3.6  | V    |

|                        |                                         | 5 V tolerant open-drain pins<br>PIO0_4 and PIO0_5                  | [2][4]     | -0.5 | +5.5  |      |

| V <sub>IA</sub>        | analog input voltage                    | pin configured as analog input                                     | [2]<br>[3] | -0.5 | 4.6   | V    |

| I <sub>DD</sub>        | supply current                          | per supply pin                                                     |            | -    | 100   | mA   |

| I <sub>SS</sub>        | ground current                          | per ground pin                                                     |            | -    | 100   | mA   |

| I <sub>latch</sub>     | I/O latch-up current                    | $-(0.5V_{DD}) < V_{I} < (1.5V_{DD});$<br>T <sub>j</sub> < 125 °C   |            | -    | 100   | mA   |

| T <sub>stg</sub>       | storage temperature                     | non-operating                                                      | [6]        | -65  | +150  | °C   |

| T <sub>j(max)</sub>    | maximum junction<br>temperature         |                                                                    |            | -    | 150   | °C   |

| P <sub>tot(pack)</sub> | total power dissipation (per package)   | based on package heat<br>transfer, not device power<br>consumption |            | -    | 1.5   | W    |

| V <sub>ESD</sub>       | electrostatic discharge voltage         | human body model; all pins                                         | [7]        | -    | +6500 | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

c) The limiting values are stress ratings only. Operating the part at these values is not recommended, and proper operation is not guaranteed. The conditions for functional operation are specified in <u>Table 5</u>.

- [2] Maximum/minimum voltage above the maximum operating voltage (see <u>Table 5</u>) and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter lifetime of the device.

- [3] See <u>Table 6</u> for maximum operating voltage.

- [4] V<sub>DD</sub> present or not present. Compliant with the I<sup>2</sup>C-bus standard. 5.5 V can be applied to this pin when V<sub>DD</sub> is powered down.

- [5] Including voltage on outputs in 3-state mode.

- [6] The maximum non-operating storage temperature is different than the temperature for required shelf life which should be determined based on required shelf lifetime. Please refer to the JEDEC spec (J-STD-033B.1) for further details.

- [7] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

# 9. Static characteristics

#### Table 5.Static characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol           | Parameter                               | Conditions                                                                       |                        | Min                | Typ <u>[1]</u> | Max                | Unit |

|------------------|-----------------------------------------|----------------------------------------------------------------------------------|------------------------|--------------------|----------------|--------------------|------|

| V <sub>DD</sub>  | supply voltage (core and external rail) |                                                                                  | [2]                    | 1.8                | 3.3            | 3.6                | V    |

| I <sub>DD</sub>  | supply current                          | Active mode; $V_{DD} = 3.3 V$ ;<br>$T_{amb} = 25 °C$ ; code                      |                        |                    |                |                    |      |

|                  |                                         | while(1){}                                                                       |                        |                    |                |                    |      |

|                  |                                         | executed from flash;                                                             |                        |                    |                |                    |      |

|                  |                                         | system clock = 12 MHz                                                            | [3][4][5]<br>[6][7][8] | -                  | 2              | -                  | mA   |

|                  |                                         | system clock = 50 MHz                                                            | [4][5][6]<br>[7][8][9] | -                  | 7              | -                  | mA   |

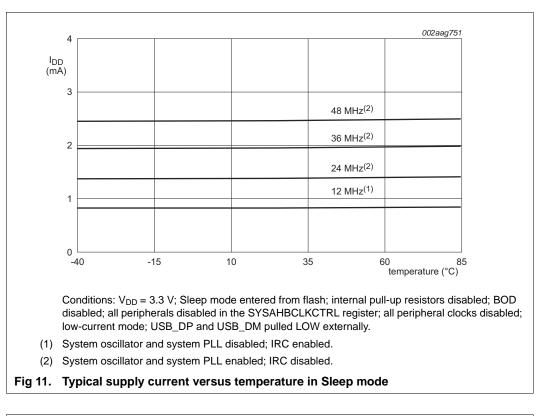

|                  |                                         | Sleep mode;<br>V <sub>DD</sub> = 3.3 V; T <sub>amb</sub> = 25 °C;                | [3][4][5]<br>[6][7][8] | -                  | 1              | -                  | mA   |

|                  |                                         | system clock = 12 MHz                                                            |                        |                    |                |                    |      |

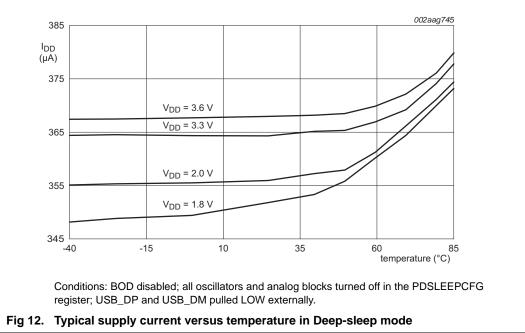

|                  |                                         | Deep-sleep mode; $V_{DD} = 3.3 V$ ;<br>T <sub>amb</sub> = 25 °C                  | [4][7]                 | -                  | 300            | -                  | μA   |

|                  |                                         | Power-down mode; $V_{DD} = 3.3 V$ ;<br>T <sub>amb</sub> = 25 °C                  |                        | -                  | 2              | -                  | μA   |

|                  |                                         | Deep power-down mode;<br>V <sub>DD</sub> = 3.3 V; T <sub>amb</sub> = 25 °C       | [10]                   | -                  | 220            | -                  | nA   |

| Standard         | l port pins, RESET                      |                                                                                  |                        | 1                  |                | <b>I</b>           |      |

| IIL              | LOW-level input current                 | V <sub>I</sub> = 0 V; on-chip pull-up resistor<br>disabled                       |                        | -                  | 0.5            | 10                 | nA   |

| I <sub>IH</sub>  | HIGH-level input<br>current             | $V_I = V_{DD}$ ; on-chip pull-down resistor disabled                             |                        | -                  | 0.5            | 10                 | nA   |

| I <sub>OZ</sub>  | OFF-state output<br>current             | $V_O = 0 V$ ; $V_O = V_{DD}$ ; on-chip<br>pull-up/down resistors disabled        |                        | -                  | 0.5            | 10                 | nA   |

| VI               | input voltage                           | pin configured to provide a digital function; $V_{DD} \ge 1.8 \text{ V}$         | [11]<br>[12]           | 0                  | -              | 5.0                | V    |

|                  |                                         | $V_{DD} = 0 V$                                                                   |                        | 0                  | -              | 3.6                | V    |

| Vo               | output voltage                          | output active                                                                    |                        | 0                  | -              | V <sub>DD</sub>    | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                |                                                                                  |                        | 0.7V <sub>DD</sub> | -              | -                  | V    |

| V <sub>IL</sub>  | LOW-level input voltage                 |                                                                                  |                        | -                  | -              | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                      |                                                                                  |                        | -                  | 0.4            | -                  | V    |

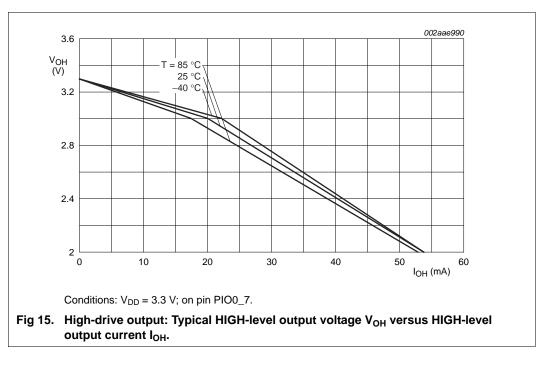

| V <sub>OH</sub>  | HIGH-level output                       | $2.0~V \leq V_{DD} \leq 3.6~V;~I_{OH} = -4~mA$                                   |                        | $V_{DD}-0.4$       | -              | -                  | V    |

|                  | voltage                                 | 1.8 V $\leq$ V <sub>DD</sub> < 2.0 V; I <sub>OH</sub> = -3 mA                    |                        | $V_{DD}-0.4$       | -              | -                  | V    |

| V <sub>OL</sub>  | LOW-level output                        | $2.0~\text{V} \leq \text{V}_{DD} \leq 3.6~\text{V};~\text{I}_{OL} = 4~\text{mA}$ |                        | -                  | -              | 0.4                | V    |

|                  | voltage                                 | 1.8 V $\leq$ V <sub>DD</sub> < 2.0 V; I <sub>OL</sub> = 3 mA                     |                        | -                  | -              | 0.4                | V    |

| I <sub>OH</sub>  | HIGH-level output                       | $V_{OH} = V_{DD} - 0.4 \text{ V};$                                               |                        | -4                 | -              | -                  | mA   |

|                  | current                                 | $2.0~V \leq V_{DD} \leq 3.6~V$                                                   |                        |                    |                |                    |      |

|                  |                                         | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.0 \text{ V}$                        |                        | -3                 | -              | -                  | mA   |

Product data sheet

### 32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

# 9.4 Electrical pin characteristics

#### 32-bit ARM Cortex-M0 microcontroller

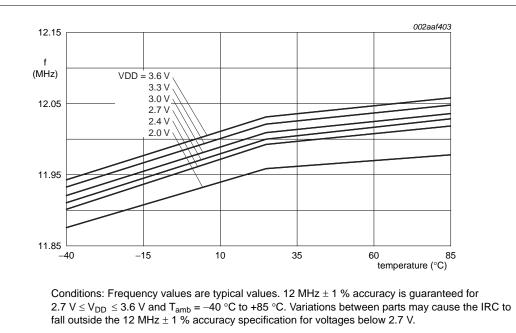

### 10.3 Internal oscillators

#### Table 12. Dynamic characteristics: IRC

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C; 2.7 \ V \le V_{DD} \le 3.6 \ V^{[1]}.$

| Symbol               | Parameter                           | Conditions | Min   | Typ[2] | Max   | Unit |

|----------------------|-------------------------------------|------------|-------|--------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency | -          | 11.88 | 12     | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

Fig 22. Internal RC oscillator frequency versus temperature

#### Table 13. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter | Conditions                                                  |        | Min | Typ[1] | Max | Unit |

|-----------------------|-----------|-------------------------------------------------------------|--------|-----|--------|-----|------|

| f <sub>osc(int)</sub> |           | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 9.4    | -   | kHz  |

|                       |           | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 2300   | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

### 32-bit ARM Cortex-M0 microcontroller

- [2] The typical frequency spread over processing and temperature (T<sub>amb</sub> =  $-40 \degree C$  to +85  $\degree C$ ) is ±40 %.

- [3] See the LPC11Uxx user manual.

## 10.4 I/O pins

#### Table 14. Dynamic characteristics: I/O pins<sup>[1]</sup>

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 3.0 \text{ V} \le V_{DD} \le 3.6 \text{ V}.$

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin configured as output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin configured as output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard port pins and RESET pin.

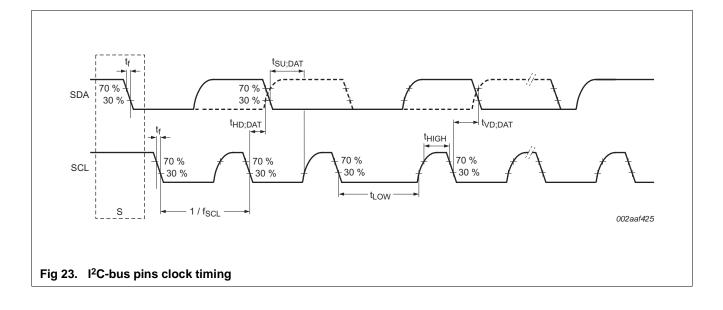

### 10.5 I<sup>2</sup>C-bus

#### Table 15. Dynamic characteristic: I<sup>2</sup>C-bus pins<sup>[1]</sup>

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C.$

| Symbol              | Parameter                     |              | Conditions                  | Min                   | Max | Unit |

|---------------------|-------------------------------|--------------|-----------------------------|-----------------------|-----|------|

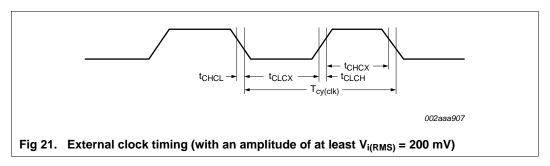

| f <sub>SCL</sub>    | SCL clock                     |              | Standard-mode               | 0                     | 100 | kHz  |

|                     | frequency                     |              | Fast-mode                   | 0                     | 400 | kHz  |

|                     |                               |              | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time                     | [4][5][6][7] | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                               |              | Standard-mode               |                       |     |      |

|                     |                               |              | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                               |              | Fast-mode Plus              | -                     | 120 | ns   |

| t <sub>LOW</sub>    | N LOW period of the SCL clock |              | Standard-mode               | 4.7                   | -   | μS   |

|                     |                               |              | Fast-mode                   | 1.3                   | -   | μS   |

|                     |                               |              | Fast-mode Plus              | 0.5                   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of the            |              | Standard-mode               | 4.0                   | -   | μS   |

|                     | SCL clock                     |              | Fast-mode                   | 0.6                   | -   | μS   |

|                     |                               |              | Fast-mode Plus              | 0.26                  | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time                | [3][4][8]    | Standard-mode               | 0                     | -   | μS   |

|                     |                               |              | Fast-mode                   | 0                     | -   | μS   |

|                     |                               |              | Fast-mode Plus              | 0                     | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up time              | [9][10]      | Standard-mode               | 250                   | -   | ns   |

|                     |                               |              | Fast-mode                   | 100                   | -   | ns   |

|                     |                               |              | Fast-mode Plus              | 50                    | -   | ns   |

[1] See the I<sup>2</sup>C-bus specification UM10204 for details.

[2] Parameters are valid over operating temperature range unless otherwise specified.

- [3] tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

- [4] A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- [5]  $C_b$  = total capacitance of one bus line in pF.

- [6] The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

## **NXP Semiconductors**

# LPC11U3x

#### 32-bit ARM Cortex-M0 microcontroller

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode l<sup>2</sup>C-bus device can be used in a Standard-mode l<sup>2</sup>C-bus system but the requirement  $t_{SU;DAT} = 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode l<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

### 32-bit ARM Cortex-M0 microcontroller

51 of 77

### 11.8.3 I/O Handler I<sup>2</sup>C

The I/O Handler I<sup>2</sup>C library allows to have an additional I<sup>2</sup>C-bus master. I<sup>2</sup>C read, I<sup>2</sup>C write and combined I<sup>2</sup>C read/write are supported. Data is automatically read from and written to user-defined buffers.

The I/O Handler I<sup>2</sup>C library combined with the on-chip I<sup>2</sup>C module allows to have two distinct I<sup>2</sup>C buses, allowing to separate low-speed from high-speed devices or bridging two I<sup>2</sup>C buses.

### 11.8.4 I/O Handler DMA

The I/O Handler DMA library offers DMA-like functionality. Four types of transfer are supported: memory to memory, memory to peripheral, peripheral to memory and peripheral to peripheral. Supported peripherals are USART, SSP0/1, ADC and GPIO. DMA transfers can be triggered by the source/target peripheral, software, counter/timer module CT16B1, or I/O Handler pin PIO1\_6/IOH\_16.

### 32-bit ARM Cortex-M0 microcontroller

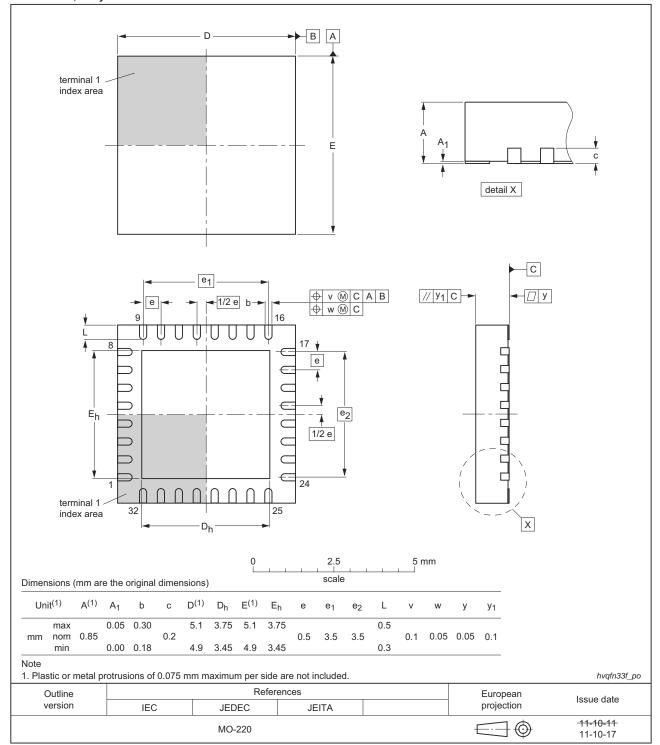

# 12. Package outline

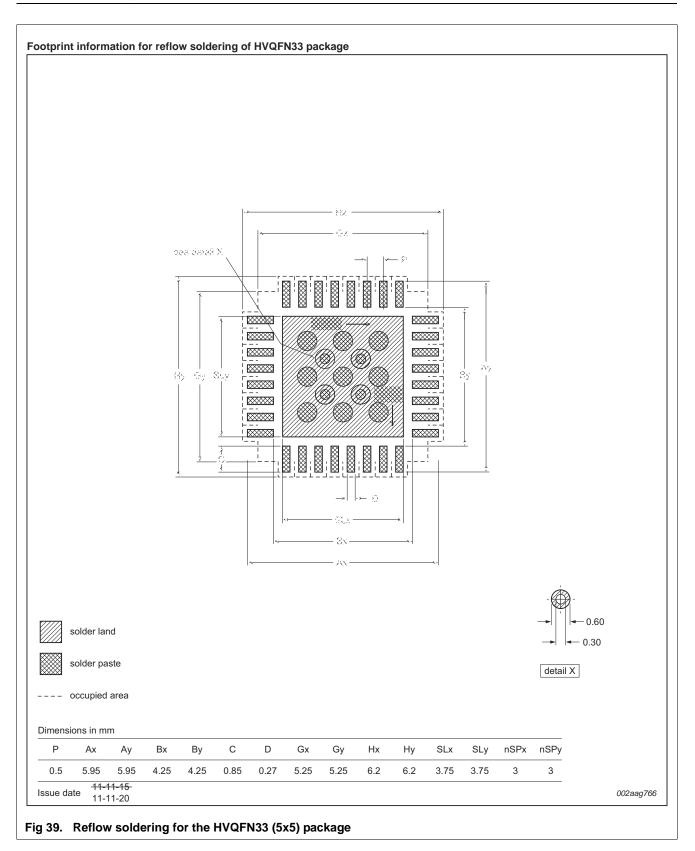

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body 5 x 5 x 0.85 mm

Fig 34. Package outline HVQFN33 (5 x 5 x 0.85 mm)

All information provided in this document is subject to legal disclaimers.

32-bit ARM Cortex-M0 microcontroller

### Fig 37. Package outline LQFP48 (SOT313-2)

All information provided in this document is subject to legal disclaimers.

### 32-bit ARM Cortex-M0 microcontroller

# 13. Soldering

LPC11U3X Product data sheet

32-bit ARM Cortex-M0 microcontroller

# 14. Abbreviations

| Table 20. Abbreviations |                                                         |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------|--|--|--|--|--|--|

| Acronym                 | Description                                             |  |  |  |  |  |  |

| A/D                     | Analog-to-Digital                                       |  |  |  |  |  |  |

| ADC                     | Analog-to-Digital Converter                             |  |  |  |  |  |  |

| AHB                     | Advanced High-performance Bus                           |  |  |  |  |  |  |

| APB                     | Advanced Peripheral Bus                                 |  |  |  |  |  |  |

| BOD                     | BrownOut Detection                                      |  |  |  |  |  |  |

| GPIO                    | General Purpose Input/Output                            |  |  |  |  |  |  |

| JTAG                    | Joint Test Action Group                                 |  |  |  |  |  |  |

| PLL                     | Phase-Locked Loop                                       |  |  |  |  |  |  |

| RC                      | Resistor-Capacitor                                      |  |  |  |  |  |  |

| SPI                     | Serial Peripheral Interface                             |  |  |  |  |  |  |

| SSI                     | Serial Synchronous Interface                            |  |  |  |  |  |  |

| SSP                     | Synchronous Serial Port                                 |  |  |  |  |  |  |

| TAP                     | Test Access Port                                        |  |  |  |  |  |  |

| USART                   | Universal Synchronous Asynchronous Receiver/Transmitter |  |  |  |  |  |  |

# 15. References

- [1] LPC11U3x User manual UM10462: http://www.nxp.com/documents/user\_manual/UM10462.pdf

- [2] LPC11U3x Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC11U3X.pdf

### 32-bit ARM Cortex-M0 microcontroller

| 15   | References             |

|------|------------------------|

| 16   | Revision history 73    |

| 17   | Legal information 74   |

| 17.1 | Data sheet status      |

| 17.2 | Definitions74          |

| 17.3 | Disclaimers            |

| 17.4 | Trademarks 75          |

| 18   | Contact information 75 |

| 19   | Contents 76            |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP Semiconductors N.V. 2017.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 8 February 2017 Document identifier: LPC11U3X