Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s4avm08ac                                             |

Table 2. i.MX 6Solo/6DualLite Modules List (continued)

| Block Mnemonic                                 | Block Name                                | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------|-------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97 Interface                    | Connectivity<br>Peripherals   | The SSI is a full-duplex synchronous interface, which is used on the AP to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options.  The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller in order to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature Monitor                       | System Control<br>Peripherals | The Temperature sensor IP is used for detecting die temperature. The temperature read out does not reflect case or ambient temperature. It reflects the temperature in proximity of the sensor location on the die.  Temperature distribution may not be uniformly distributed, therefore the read out value may not be the reflection of the temperature value of the entire die.                                                                                                                                                                                                                                        |

| TZASC                                          | Trust-Zone Address<br>Space Controller    | Security                      | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                            | Connectivity<br>Peripherals   | Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:  7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)  Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and the i.MX31 UART modules.  32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud  IrDA 1.0 support (up to SIR speed of 115200 bps)  Option to operate as 8-pins full UART, DCE, or DTE                                                                      |

| USBOH3                                         | USB 2.0 High Speed<br>OTG and 3x HS Hosts | Connectivity<br>Peripherals   | USBOH3 contains:  One high-speed OTG module with integrated HS USB PHY  One high-speed Host module with integrated HS USB PHY  Two identical high-speed Host modules connected to HSIC USB ports.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VDOA                                           | VDOA                                      | Multimedia<br>Peripherals     | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### **Modules List**

Table 3. Special Signal Considerations (continued)

| Signal Name      | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM_VREF        | When using DDR_VREF with DDR I/O, the nominal reference voltage must be half of the NVCC_DRAM supply. The user must tie DDR_VREF to a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_DRAM. Shunt each resistor with a closely-mounted 0.1 $\mu$ F capacitor.                                                                                                                                                               |

|                  | To reduce supply current, a pair of 1.5 k $\Omega$ 0.1% resistors can be used. Using resistors with recommended tolerances ensures the $\pm$ 2% DDR_VREF tolerance (per the DDR3 specification) is maintained when four DDR3 ICs plus the i.MX 6Solo/6DualLite are drawing current on the resistor divider.                                                                                                                                                                                       |

|                  | It is recommended to use regulated power supply for "big" memory configurations (more that eight devices)                                                                                                                                                                                                                                                                                                                                                                                         |

| ZQPAD            | DRAM calibration resistor 240 $\Omega$ 1% used as reference during DRAM output buffer driver calibration should be connected between this pad and GND.                                                                                                                                                                                                                                                                                                                                            |

| NVCC_LVDS2P5     | The DDR pre-drivers share the NVCC_LVDS2P5 ball with the LVDS interface. This ball can be shorted to VDDHIGH_CAP on the circuit board.                                                                                                                                                                                                                                                                                                                                                            |

| VDD_FA<br>FA_ANA | These signals are reserved for Freescale manufacturing use only. User must tie both connections to GND.                                                                                                                                                                                                                                                                                                                                                                                           |

| GPANAIO          | This signal is reserved for Freescale manufacturing use only. User must leave this connection floating.                                                                                                                                                                                                                                                                                                                                                                                           |

| JTAG_nnnn        | The JTAG interface is summarized in Table 4. Use of external resistors is unnecessary. However, if external resistors are used, the user must ensure that the on-chip pull-up/down configuration is followed. For example, do not use an external pull down on an input that has on-chip pull-up.                                                                                                                                                                                                 |

|                  | JTAG_TDO is configured with a keeper circuit such that the floating condition is eliminated if an external pull resistor is not present. An external pull resistor on JTAG_TDO is detrimental and should be avoided.                                                                                                                                                                                                                                                                              |

|                  | JTAG_MOD is referenced as SJC_MOD in the i.MX 6Solo/6DualLite reference manual. Both names refer to the same signal. JTAG_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed. JTAG_MOD set to hi configures the JTAG interface to mode compliant with IEEE1149.1 standard. JTAG_MOD set to low configures the JTAG interface for common SW debug adding all the system TAPs to the chain. |

| NC               | These signals are No Connect (NC) and should be floated by the user.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POR_B            | This cold reset negative logic input resets all modules and logic in the IC.  May be used in addition to internally generated power on reset signal (logical AND, both internal and external signals are considered active low).                                                                                                                                                                                                                                                                  |

| ONOFF            | In normal mode may be connected to ON/OFF button (De-bouncing provided at this input). Internally this pad is pulled up. Short connection to GND in OFF mode causes internal power management state machine to change state to ON. In ON mode short connection to GND generates interrupt (intended to SW controllable power down). Long above ~5s connection to GND causes "forced" OFF.                                                                                                         |

| TEST_MODE        | TEST_MODE is for Freescale factory use. This signal is internally connected to an on-chip pull-down device. The user must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                                                                              |

| PCIE_REXT        | The impedance calibration process requires connection of reference resistor 200 $\Omega$ 1% precision resistor on PCIE_REXT pad to ground.                                                                                                                                                                                                                                                                                                                                                        |

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

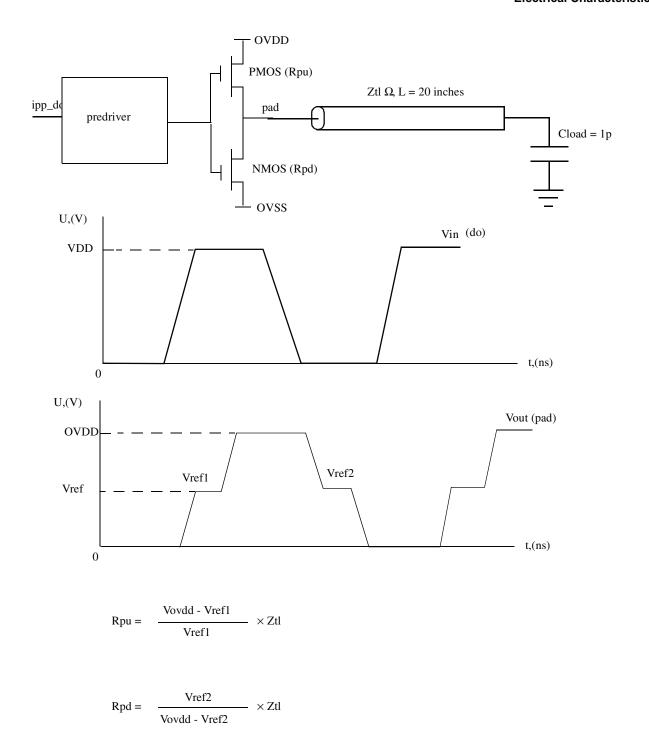

Figure 9. Impedance Matching Load for Measurement

#### **Electrical Characteristics**

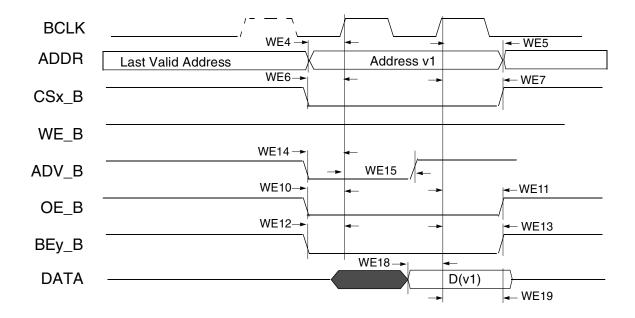

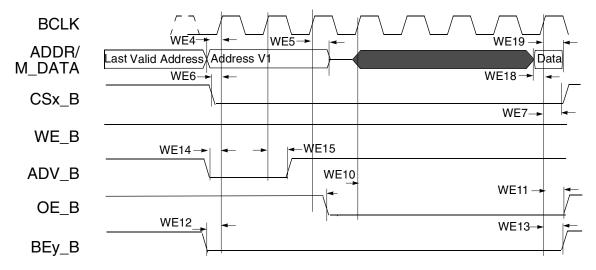

Table 43. EIM Bus Timing Parameters (continued)<sup>1</sup>

| ID   | Parameter                                  | вс  | BCD = 0 |     | BCD = 1 |     | BCD = 2 |     | BCD = 3 |  |

|------|--------------------------------------------|-----|---------|-----|---------|-----|---------|-----|---------|--|

|      | i didilietei                               | Min | Max     | Min | Max     | Min | Max     | Min | Max     |  |

| WE19 | Input Data hold<br>time from Clock<br>rise | 2   | _       | 2   | _       | _   | _       | _   | _       |  |

| WE20 | WAIT_B setup time to Clock rise            | 2   | _       | 4   | _       | _   | _       | _   | _       |  |

| WE21 | WAIT_B hold time from Clock rise           | 2   | _       | 2   | _       | _   | _       | _   | _       |  |

t is the maximal EIM logic (axi\_clk) cycle time. The maximum allowed axi\_clk frequency depends on the fixed/non-fixed latency configuration, whereas the maximum allowed BCLK frequency is:

Figure 14 to Figure 17 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 14. Synchronous Memory Read Access, WSC=1

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

<sup>-</sup>Fixed latency for both read and write is 132 MHz.

<sup>-</sup>Variable latency for read only is 132 MHz.

<sup>-</sup>Variable latency for write only is 52 MHz.

In variable latency configuration for write, if BCD = 0 & WBCDD = 1 or BCD = 1, axi\_clk must be 104 MHz.Write BCD = 1 and 104 MHz axi\_clk, will result in a BCLK of 52 MHz. When the clock branch to EIM is decreased to 104 MHz, other buses are impacted which are clocked from this source. See the CCM chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM) for a detailed clock tree description.

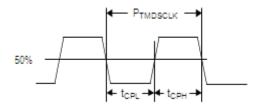

BCLK parameters are being measured from the 50% point, that is, high is defined as 50% of signal value and low is defined as 50% as signal value.

<sup>&</sup>lt;sup>3</sup> For signal measurements, "High" is defined as 80% of signal value and "Low" is defined as 20% of signal value.

Figure 17. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

### 4.9.3.5 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22, and Table 44 help you determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for the EIM programming model.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

# 4.10.3.2 Read and Write Timing

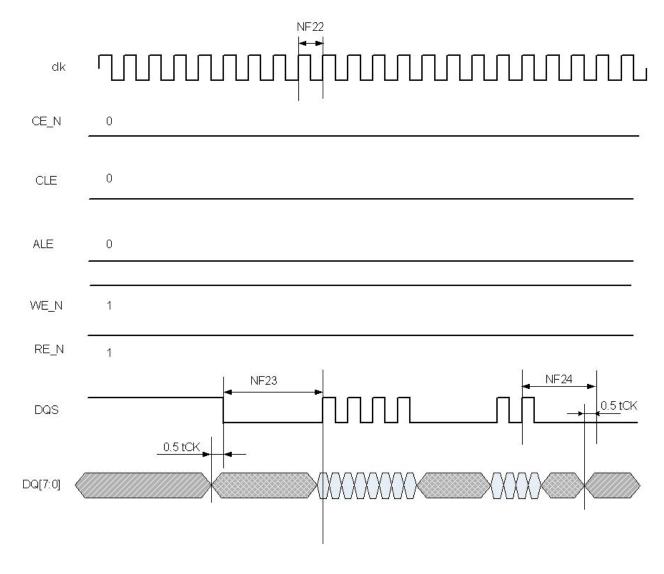

Figure 38. Samsung Toggle Mode Data Write Timing

#### **Electrical Characteristics**

# 4.11.2.1 ECSPI Master Mode Timing

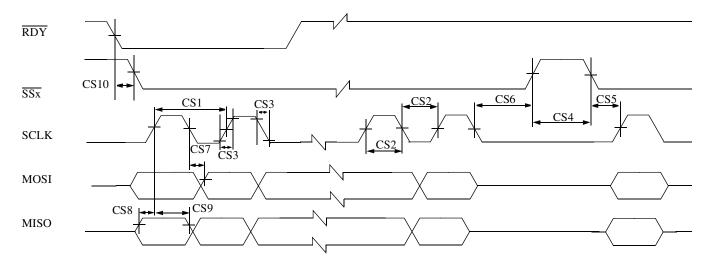

Figure 40 depicts the timing of ECSPI in master mode. Table 54 lists the ECSPI master mode timing characteristics.

Figure 40. ECSPI Master Mode Timing Diagram

**Table 54. ECSPI Master Mode Timing Parameters**

| ID   | Parameter                                                 | Symbol                 | Min                  | Max | Unit |

|------|-----------------------------------------------------------|------------------------|----------------------|-----|------|

| CS1  | SCLK Cycle Time-Read<br>SCLK Cycle Time-Write             | t <sub>clk</sub>       | 43<br>15             | _   | ns   |

| CS2  | SCLK High or Low Time-Read<br>SCLK High or Low Time-Write | t <sub>SW</sub>        | 21.5<br>7            | _   | ns   |

| CS3  | SCLK Rise or Fall <sup>1</sup>                            | t <sub>RISE/FALL</sub> | _                    | _   | ns   |

| CS4  | SSx pulse width                                           | t <sub>CSLH</sub>      | Half SCLK period     | _   | ns   |

| CS5  | SSx Lead Time (CS setup time)                             | t <sub>SCS</sub>       | Half SCLK period - 4 | _   | ns   |

| CS6  | SSx Lag Time (CS hold time)                               | t <sub>HCS</sub>       | Half SCLK period - 2 | _   | ns   |

| CS7  | MOSI Propagation Delay (C <sub>LOAD</sub> = 20 pF)        | t <sub>PDmosi</sub>    | -1                   | 1   | ns   |

| CS8  | MISO Setup Time                                           | t <sub>Smiso</sub>     | 18                   | _   | ns   |

| CS9  | MISO Hold Time                                            | t <sub>Hmiso</sub>     | 0                    | _   | ns   |

| CS10 | RDY to SSx Time <sup>2</sup>                              | t <sub>SDRY</sub>      | 5                    | _   | ns   |

<sup>&</sup>lt;sup>1</sup> See specific I/O AC parameters Section 4.7, "I/O AC Parameters."

$<sup>^2\,</sup>$  SPI\_RDY is sampled internally by ipg\_clk and is asynchronous to all other CSPI signals.

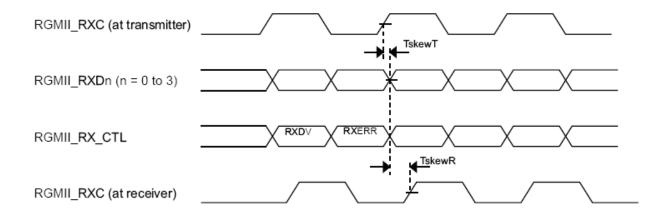

Figure 53. RGMII Receive Signal Timing Diagram Original

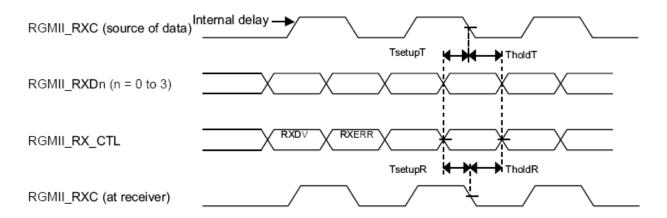

Figure 54. RGMII Receive Signal Timing Diagram with Internal Delay

# 4.11.6 Flexible Controller Area Network (FLEXCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* to see which pins expose Tx and Rx pins; these ports are named TXCAN and RXCAN, respectively.

# 4.11.7 HDMI Module Timing Parameters

# 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

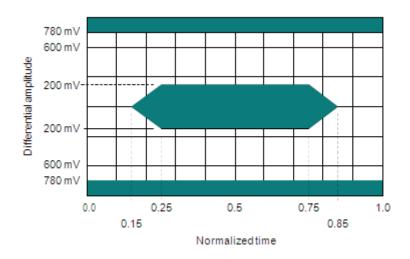

**Table 66. Electrical Characteristics**

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                          | Condition                                                                                                                                                             | Min.                 | Тур.        | Max.                 | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|----------------------|------|

|                    | I                                                                                                                                                                                                                                                                                                                                  | Operating conditions for HD                                                                                                                                           | MI                   |             |                      |      |

| avddtmds           | Termination supply voltage                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                     | 3.15                 | 3.3         | 3.45                 | V    |

| $R_T$              | Termination resistance                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                     | 45                   | 50          | 55                   | Ω    |

|                    |                                                                                                                                                                                                                                                                                                                                    | TMDS drivers DC specificati                                                                                                                                           | ons                  |             |                      |      |

| $V_{OFF}$          | Single-ended standby voltage                                                                                                                                                                                                                                                                                                       | RT = 50 Ω                                                                                                                                                             | avo                  | ddtmds ± 10 | mV                   | mV   |

| V <sub>SWING</sub> | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                  | For measurement conditions and definitions, see the first two figures above.  Compliance point TP1 as defined in the HDMI specification, version 1.3a, section 4.2.4. | 400                  | -           | 600                  | mV   |

| $V_{H}$            | Single-ended output high voltage                                                                                                                                                                                                                                                                                                   | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                   | avo                  | ddtmds ± 10 | mV                   | mV   |

|                    | For definition, see the second figure above                                                                                                                                                                                                                                                                                        | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                        | avddtmds<br>- 200 mV | -           | avddtmds<br>+ 10 mV  | mV   |

| V <sub>L</sub>     | Single-ended output low voltage                                                                                                                                                                                                                                                                                                    | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                   | avddtmds<br>- 600 mV | -           | avddtmds<br>- 400mV  | mV   |

|                    | For definition, see the second figure above                                                                                                                                                                                                                                                                                        | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                        | avddtmds<br>- 700 mV | -           | avddtmds<br>- 400 mV | mV   |

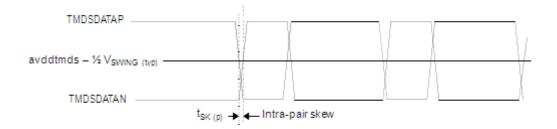

| R <sub>TERM</sub>  | Differential source termination load (inside HDMI 3D Tx PHY) Although the HDMI 3D Tx PHY includes differential source termination, the user-defined value is set for each single line (for illustration, see the third figure above).  Note: R <sub>TERM</sub> can also be configured to be open and not present on TMDS channels. | -                                                                                                                                                                     | 50                   | -           | 200                  | Ω    |

|                    |                                                                                                                                                                                                                                                                                                                                    | Hot plug detect specificatio                                                                                                                                          | ns                   |             |                      |      |

| HPD <sup>VH</sup>  | Hot plug detect high range                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                     | 2.0                  | -           | 5.3                  | V    |

| VHPD<br>VL         | Hot plug detect low range                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                     | 0                    | -           | 0.8                  | V    |

| HPD<br>Z           | Hot plug detect input impedance                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                     | 10                   | -           | -                    | kΩ   |

| HPD<br>t           | Hot plug detect time delay                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                     | -                    | -           | 100                  | μs   |

# 4.11.8 Switching Characteristics

Table 67 describes switching characteristics for the HDMI 3D Tx PHY. Figure 58 to Figure 62 illustrate various parameters specified in table.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

### **NOTE**

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

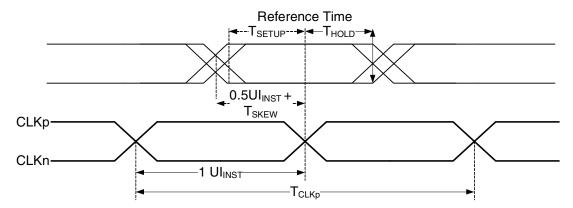

Figure 58. TMDS Clock Signal Definitions

Figure 59. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

Figure 60. Intra-Pair Skew Definition

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

### 4.11.10.1 IPU Sensor Interface Signal Mapping

The IPU supports a number of sensor input formats. Table 69 defines the mapping of the Sensor Interface Pins used for various supported interface formats.

Table 69. Camera Input Signal Cross Reference, Format, and Bits Per Cycle

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>2 cycles | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| CSIx_DAT0                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | 0                                        | C[0]                                     |

| CSIx_DAT1                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | 0                                        | C[1]                                     |

| CSIx_DAT2                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | C[0]                                     | C[2]                                     |

| CSIx_DAT3                   | _                            | _                                         | _                                         | _                            | _                                        | _                                          | _                                        | C[1]                                     | C[3]                                     |

| CSIx_DAT4                   | _                            | _                                         | _                                         | _                            | _                                        | B[0]                                       | C[0]                                     | C[2]                                     | C[4]                                     |

| CSIx_DAT5                   |                              | _                                         | _                                         | _                            | _                                        | B[1]                                       | C[1]                                     | C[3]                                     | C[5]                                     |

| CSIx_DAT6                   | _                            | _                                         | _                                         | _                            | _                                        | B[2]                                       | C[2]                                     | C[4]                                     | C[6]                                     |

| CSIx_DAT7                   | _                            | _                                         | _                                         | _                            | _                                        | B[3]                                       | C[3]                                     | C[5]                                     | C[7]                                     |

| CSIx_DAT8                   | _                            | _                                         | _                                         | _                            | _                                        | B[4]                                       | C[4]                                     | C[6]                                     | C[8]                                     |

| CSIx_DAT9                   | _                            | _                                         | _                                         | _                            | _                                        | G[0]                                       | C[5]                                     | C[7]                                     | C[9]                                     |

| CSIx_DAT10                  | _                            | _                                         | _                                         | _                            | _                                        | G[1]                                       | C[6]                                     | 0                                        | Y[0]                                     |

| CSIx_DAT11                  | _                            | _                                         | _                                         | _                            | _                                        | G[2]                                       | C[7]                                     | 0                                        | Y[1]                                     |

| CSIx_DAT12                  | B[0], G[3]                   | R[2],G[4],B[2]                            | R/G/B[4]                                  | R/G/B[0]                     | Y/C[0]                                   | G[3]                                       | Y[0]                                     | Y[0]                                     | Y[2]                                     |

| CSIx_DAT13                  | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                       | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| CSIx_DAT14                  | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                       | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| CSIx_DAT15                  | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                       | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| CSIx_DAT16                  | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                       | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| CSIx_DAT17                  | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                       | Y[5]                                     | Y[5]                                     | Y[7]                                     |

| CSIx_DAT18                  | G[1], R[3]                   | R[3],G[4],B[3]                            | R/G/B[4]                                  | R/G/B[6]                     | Y/C[6]                                   | R[3]                                       | Y[6]                                     | Y[6]                                     | Y[8]                                     |

| CSIx_DAT19                  | G[2], R[4]                   | R[4],G[5],B[4]                            | R/G/B[5]                                  | R/G/B[7]                     | Y/C[7]                                   | R[4]                                       | Y[7]                                     | Y[7]                                     | Y[9]                                     |

CSIx stands for CSI1 or CSI2

<sup>&</sup>lt;sup>2</sup> The MSB bits are duplicated on LSB bits implementing color extension

<sup>&</sup>lt;sup>3</sup> The two MSB bits are duplicated on LSB bits implementing color extension

<sup>&</sup>lt;sup>4</sup> YCbCr, 8 bits—Supported within the BT.656 protocol (sync embedded within the data stream).

<sup>&</sup>lt;sup>5</sup> RGB 16 bits— Supported in two ways: (1) As a "generic data" input, with no on-the-fly processing; (2) With on-the-fly processing, but only under some restrictions on the control protocol.

<sup>&</sup>lt;sup>6</sup> YCbCr 16 bits— Supported as a "generic-data" input, with no on-the-fly processing.

YCbCr 16 bits— Supported as a sub-case of the YCbCr, 20 bits, under the same conditions (BT.1120 protocol).

<sup>&</sup>lt;sup>8</sup> YCbCr, 20 bits, supported only within the BT.1120 protocol (syncs embedded within the data stream).

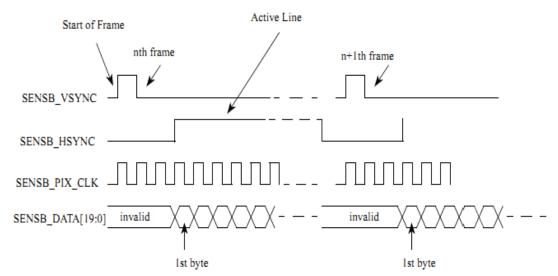

### 4.11.10.2 Sensor Interface Timings

There are three camera timing modes supported by the IPU.

#### 4.11.10.2.1 BT.656 and BT.1120 Video Mode

Smart camera sensors, which include imaging processing, usually support video mode transfer. They use an embedded timing syntax to replace the SENSB\_VSYNC and SENSB\_HSYNC signals. The timing syntax is defined by the BT.656/BT.1120 standards.

This operation mode follows the recommendations of ITU BT.656/ ITU BT.1120 specifications. The only control signal used is SENSB\_PIX\_CLK. Start-of-frame and active-line signals are embedded in the data stream. An active line starts with a SAV code and ends with a EAV code. In some cases, digital blanking is inserted in between EAV and SAV code. The CSI decodes and filters out the timing-coding from the data stream, thus recovering SENSB\_VSYNC and SENSB\_HSYNC signals for internal use. On BT.656 one component per cycle is received over the SENSB\_DATA bus. On BT.1120 two components per cycle are received over the SENSB\_DATA bus.

#### 4.11.10.2.2 Gated Clock Mode

The SENSB\_VSYNC, SENSB\_HSYNC, and SENSB\_PIX\_CLK signals are used in this mode. See Figure 64.

Figure 64. Gated Clock Mode Timing Diagram

A frame starts with a rising edge on SENSB\_VSYNC (all the timings correspond to straight polarity of the corresponding signals). Then SENSB\_HSYNC goes to high and hold for the entire line. Pixel clock is valid as long as SENSB\_HSYNC is high. Data is latched at the rising edge of the valid pixel clocks. SENSB\_HSYNC goes to low at the end of line. Pixel clocks then become invalid and the CSI stops receiving data from the stream. For next line the SENSB\_HSYNC timing repeats. For next frame the SENSB\_VSYNC timing repeats.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

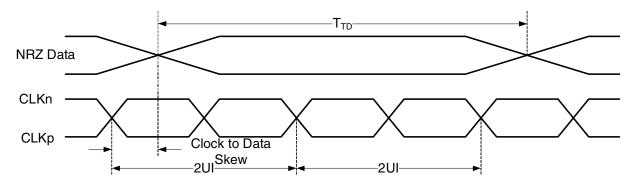

### 4.11.12.7 Forward High-Speed Data Transmission Timing

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 75:

Figure 75. Data to Clock Timing Definitions

# 4.11.12.8 Reverse High-Speed Data Transmission Timing

Figure 76. Reverse High-Speed Data Transmission Timing at Slave Side

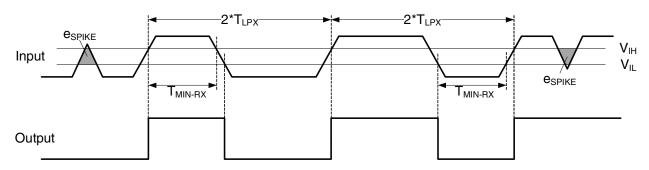

# 4.11.12.9 Low-Power Receiver Timing

Figure 77. Input Glitch Rejection of Low-Power Receivers

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

Table 81. MLB 1024 Fs Timing Parameters (continued)

| Parameter                                                          | Symbol             | Min | Max               | Unit | Comment |

|--------------------------------------------------------------------|--------------------|-----|-------------------|------|---------|

| MLBSIG/MLBDAT output high impedance from MLBCLK low                | t <sub>mcfdz</sub> | 0   | t <sub>mckl</sub> | ns   | 3       |

| Bus Hold from MLBCLK low                                           | t <sub>mdzh</sub>  | 2   | _                 | ns   | _       |

| MLBSIG/MLBDAT output valid from transition of MLBCLK (low to high) | t <sub>delay</sub> | _   | 7                 | ns   | _       |

The controller can shut off MLBCLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLBCLK.

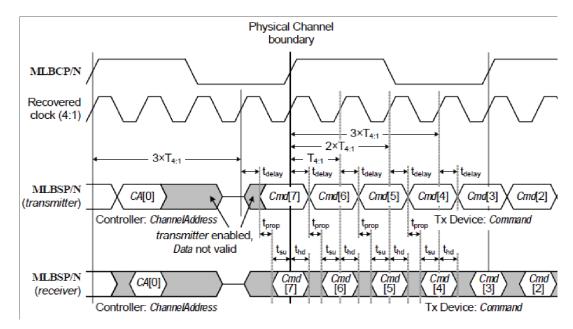

Table 82 lists the MediaLB 6-pin interface timing characteristics, and Figure 87 shows the MLB 6-pin delay, setup, and hold times.

**Table 82. MLB 6-Pin Interface Timing Parameters**

| Parameter                                                                                        | Symbol              | Min  | Max | Unit | Comment |

|--------------------------------------------------------------------------------------------------|---------------------|------|-----|------|---------|

| Cycle-to-cycle system jitter                                                                     | t <sub>jitter</sub> | _    | 600 | ps   | _       |

| Transmitter MLBSP/N (MLBDP/N) output valid from transition of MLBCP/N (low-to-high) <sup>1</sup> | t <sub>delay</sub>  | 0.6  | 1.3 | ns   |         |

| Disable turnaround time from transition of MLBCP/N (low-to-high)                                 | t <sub>phz</sub>    | 0.6  | 3.5 | ns   |         |

| Enable turnaround time from transition of MLBCP/N (low-to-high)                                  | t <sub>plz</sub>    | 0.6  | 5.6 | ns   |         |

| MLBSP/N (MLBDP/N) valid to transition of MLBCP/N (low-to-high)                                   | t <sub>su</sub>     | 0.05 | _   | ns   |         |

| MLBSP/N (MLBDP/N) hold from transition of MLBCP/N (low-to-high) <sup>2</sup>                     | t <sub>hd</sub>     | 0.6  |     |      |         |

t<sub>delay</sub>, t<sub>phz</sub>, t<sub>plz</sub>, t<sub>su</sub>, and t<sub>hd</sub> may also be referenced from a low-to-high transition of the recovered clock for 2:1 and 4:1 recovered-to-external clock ratios.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

<sup>&</sup>lt;sup>2</sup> MLBCLK low/high time includes the pulse width variation.

The MediaLB driver can release the MLBDAT/MLBSIG line as soon as MLBCLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

<sup>&</sup>lt;sup>2</sup> The transmitting device must ensure valid data on MLBSP/N (MLBDP/N) for at least t<sub>hd(min)</sub> following the rising edge of MLBCP/N; receivers must latch MLBSP/N (MLBDP/N) data within t<sub>hd(min)</sub> of the rising edge of MLBCP/N.

Figure 87. MLB 6-Pin Delay, Setup, and Hold Times

### 4.11.15 PCle PHY Parameters

The PCIe interface complies with PCIe specification Gen2 x1 lane and supports the PCI Express 1.1/2.0 standard.

# 4.11.15.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

# 4.11.16 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 88 depicts the timing of the PWM, and Table 83 lists the PWM timing parameters.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

#### **NOTE**

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

# 4.11.20 UART I/O Configuration and Timing Parameters

### 4.11.20.1 UART RS-232 I/O Configuration in Different Modes

The i.MX 6Solo/6DualLite UART interfaces can serve both as DTE or DCE device. This can be configured by the DCEDTE control bit (default 0 — DCE mode). Table 91 shows the UART I/O configuration based on the enabled mode.

| Port    |           | DTE Mode                    | DCE Mode  |                             |  |  |

|---------|-----------|-----------------------------|-----------|-----------------------------|--|--|

| Port    | Direction | Description                 | Direction | Description                 |  |  |

| RTS     | Output    | RTS from DTE to DCE         | Input     | RTS from DTE to DCE         |  |  |

| CTS     | Input     | CTS from DCE to DTE         | Output    | CTS from DCE to DTE         |  |  |

| DTR     | Output    | DTR from DTE to DCE         | Input     | DTR from DTE to DCE         |  |  |

| DSR     | Input     | DSR from DCE to DTE         | Output    | DSR from DCE to DTE         |  |  |

| DCD     | Input     | DCD from DCE to DTE         | Output    | DCD from DCE to DTE         |  |  |

| RI      | Input     | RING from DCE to DTE        | Output    | RING from DCE to DTE        |  |  |

| TXD_MUX | Input     | Serial data from DCE to DTE | Output    | Serial data from DCE to DTE |  |  |

| RXD_MUX | Output    | Serial data from DTE to DCE | Input     | Serial data from DTE to DCE |  |  |

Table 91. UART I/O Configuration vs. Mode

# 4.11.20.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

### 4.11.20.2.1 UART Transmitter

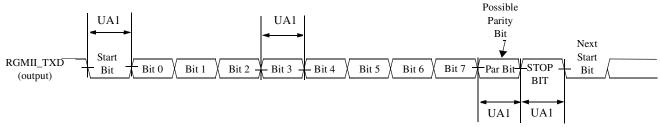

Figure 99 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 92 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 99. UART RS-232 Serial Mode Transmit Timing Diagram

Table 92. RS-232 Serial Mode Transmit Timing Parameters

| ID  | Parameter         | Symbol            | Min                                                    | Max                                                | Unit |

|-----|-------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> +<br>T <sub>ref_clk</sub> | _    |

<sup>&</sup>lt;sup>1</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

#### 4.11.20.2.2 UART Receiver

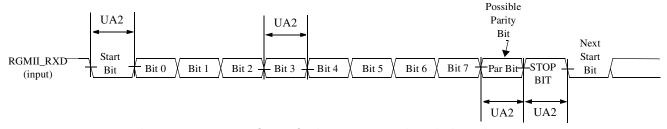

Figure 100 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 93 lists serial mode receive timing characteristics.

Figure 100. UART RS-232 Serial Mode Receive Timing Diagram

Table 93. RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Max                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | _    |

The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

<sup>&</sup>lt;sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

<sup>&</sup>lt;sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

### **Package Information and Contact Assignments**

Table 101. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

|             |      |              |              | Out of Reset Condition <sup>2</sup> |                  |                      |                |  |  |  |  |  |  |

|-------------|------|--------------|--------------|-------------------------------------|------------------|----------------------|----------------|--|--|--|--|--|--|

| Ball Name   | Ball | Power Group  | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Outpu<br>t | Value          |  |  |  |  |  |  |

| LVDS0_TX1_N | U4   | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS0_TX1_P | U3   | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS0_TX1    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS0_TX2_N | V2   | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS0_TX2_P | V1   | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS0_TX2    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS0_TX3_N | W2   | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS0_TX3_P | W1   | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS0_TX3    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS1_CLK_N | Y3   | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS1_CLK_P | Y4   | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS1_CLK    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS1_TX0_N | Y1   | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS1_TX0_P | Y2   | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS1_TX0    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS1_TX1_N | AA2  | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS1_TX1_P | AA1  | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS1_TX1    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS1_TX2_N | AB1  | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS1_TX2_P | AB2  | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS1_TX2    | Input                | Keeper         |  |  |  |  |  |  |

| LVDS1_TX3_N | AA3  | NVCC_LVDS2P5 |              |                                     |                  |                      |                |  |  |  |  |  |  |

| LVDS1_TX3_P | AA4  | NVCC_LVDS2P5 |              | ALT0                                | ldb.LVDS1_TX3    | Input                | Keeper         |  |  |  |  |  |  |

| MLB_CN      | A11  | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| MLB_CP      | B11  | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| MLB_DN      | B10  | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| MLB_DP      | A10  | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| MLB_SN      | A9   | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| MLB_SP      | В9   | VDDHIGH_CAP  |              |                                     |                  |                      |                |  |  |  |  |  |  |

| NANDF_ALE   | A16  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[8]    | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_CLE   | C15  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[7]    | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_CS0   | F15  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[11]   | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_CS1   | C16  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[14]   | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_CS2   | A17  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[15]   | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_CS3   | D16  | NVCC_NANDF   | GPIO         | ALT5                                | gpio6.GPIO[16]   | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_D0    | A18  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[0]    | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

| NANDF_D1    | C17  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[1]    | Input                | 100 kΩ pull-up |  |  |  |  |  |  |

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

### **Package Information and Contact Assignments**

Table 101. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

|               |      |              |              | Out of Reset Condition <sup>2</sup> |                              |                      |                  |  |  |  |  |  |  |

|---------------|------|--------------|--------------|-------------------------------------|------------------------------|----------------------|------------------|--|--|--|--|--|--|

| Ball Name     | Ball | Power Group  | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function             | Input/<br>Outpu<br>t | Value            |  |  |  |  |  |  |

| SD4_DAT3      | A20  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[11]               | Input                | 100 kΩ pull-up   |  |  |  |  |  |  |

| SD4_DAT4      | E18  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[12]               | Input                | 100 kΩ pull-up   |  |  |  |  |  |  |

| SD4_DAT5      | C19  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[13]               | Input                | 100 kΩ pull-up   |  |  |  |  |  |  |

| SD4_DAT6      | B20  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[14]               | Input                | 100 kΩ pull-up   |  |  |  |  |  |  |

| SD4_DAT7      | D19  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[15]               | Input                | 100 kΩ pull-up   |  |  |  |  |  |  |

| TAMPER        | E11  | VDD_SNVS_IN  | GPIO         | ALT0                                | snvs_lp_wrapper.SNVS_<br>TD1 | Input                | 100 kΩ pull-down |  |  |  |  |  |  |

| TEST_MODE     | E12  | VDD_SNVS_IN  | GPIO         | ALT0                                | tcu.TEST_MODE                | Input                | 100 kΩ pull-dowr |  |  |  |  |  |  |

| USB_H1_DN     | F10  | VDDUSB_CAP   |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| USB_H1_DP     | E10  | VDDUSB_CAP   |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| USB_OTG_CHD_B | В8   | VDDUSB_CAP   |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| USB_OTG_DN    | В6   | VDDUSB_CAP   |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| USB_OTG_DP    | A6   | VDDUSB_CAP   |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| XTALI         | A7   | NVCC_PLL_OUT |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| XTALO         | В7   | NVCC_PLL_OUT |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | A1   |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | A12  |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | A14  |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | B12  |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | B14  |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | E1   |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | E2   |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | F1   |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

| NC            | F2   |              |              |                                     |                              |                      |                  |  |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> DRAM\_D32 to DRAM\_D63 are only available for i.MX 6DualLite chip; for i.MX 6Solo chip, these pins are NC.

$<sup>^{2}\,</sup>$  The state immediately after reset and before ROM firmware or software has executed.

### **Package Information and Contact Assignments**

### Table 103. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

| z | CSI0_DAT4   | CSI0_VSYNC  | CSI0_DAT7    | CSI0_DAT6   | CSI0_DAT9 | CSI0_DAT8  | NVCC_CSI     | GND      | VDDARM_IN | GND        | VDDARM_CAP  | NC        | VDDARM_CAP | VDDARM_IN  | GND        | VDDSOC_IN | VDDPU_CAP | GND       | DIO_DISP_CLK | DIO_PIN3    | DIO_PIN15   | EIM_BCLK     | EIM_DA14    | EIM_DA15    | DIO_PIN2    | Z        |

|---|-------------|-------------|--------------|-------------|-----------|------------|--------------|----------|-----------|------------|-------------|-----------|------------|------------|------------|-----------|-----------|-----------|--------------|-------------|-------------|--------------|-------------|-------------|-------------|----------|

| ۵ | CSI0_PIXCLK | CSI0_DAT5   | CSI0_DATA_EN | CSI0_MCLK   | GPIO_19   | GPIO_18    | NVCC_GPIO    | GND      | VDDARM_IN | GND        | VDDARM_CAP  | GND       | VDDARM_CAP | VDDARM_IN  | GND        | VDDSOC_IN | VDDPU_CAP | GND       | NVCC_LCD     | DISP0_DAT4  | DISP0_DAT3  | DISP0_DAT1   | DISP0_DAT2  | DISP0_DAT0  | DIO_PIN4    | <b>a</b> |

| œ | GPIO_17     | GPIO_16     | GPIO_7       | GPIO_5      | GPIO_8    | GPIO_4     | GPIO_3       | GND      | VDDARM_IN | VDDSOC_CAP | VDDARM_CAP  | GND       | VDDARM_CAP | VDDARM_IN  | GND        | VDDSOC_IN | GND       | NVCC_DRAM | NVCC_ENET    | DISP0_DAT13 | DISP0_DAT10 | DISP0_DAT8   | DISP0_DAT6  | DISP0_DAT7  | DISP0_DAT5  | æ        |

| - | GPIO_2      | G_OIAD_9    | GPIO_6       | GPIO_1      | GPIO_0    | KEY_COL4   | KEY_ROW3     | GND      | VDDARM_IN | VDDSOC_CAP | GND         | GND       | VDDSOC_CAP | VDDSOC_CAP | GND        | VDDSOC_IN | GND       | NVCC_DRAM | GND          | DISP0_DAT21 | DISP0_DAT16 | DISP0_DAT15  | DISP0_DAT11 | DISP0_DAT12 | DISPO_DAT9  | 1        |

| n | LVDS0_TX0_P | LVDS0_TX0_N | LVDS0_TX1_P  | LVDS0_TX1_N | KEY_COL3  | KEY_ROW1   | KEY_COL1     | GND      | VDDARM_IN | VDDSOC_CAP | GND         | GND       | VDDSOC_CAP | VDDSOC_CAP | GND        | VDDSOC_IN | GND       | NVCC_DRAM | GND          | ENET_TXD0   | ENET_CRS_DV | DISP0_DAT20  | DISP0_DAT19 | DISP0_DAT17 | DISP0_DAT14 | n        |

| > | LVDS0_TX2_P | LVDS0_TX2_N | LVDS0_CLK_P  | LVDS0_CLK_N | KEY_ROW4  | KEY_ROW0   | NVCC_LVDS2P5 | GND      | NVCC_DRAM | NVCC_DRAM  | NVCC_DRAM   | NVCC_DRAM | NVCC_DRAM  | NVCC_DRAM  | NVCC_DRAM  | NVCC_DRAM | NVCC_DRAM | NVCC_DRAM | GND          | ENET_MDC    | ENET_TX_EN  | ENET_REF_CLK | ENET_MDIO   | DISP0_DAT22 | DISP0_DAT18 | >        |

| M | LVDS0_TX3_P | LVDS0_TX3_N | GND          | KEY_ROW2    | KEY_COL0  | KEY_COL2   | GND          | GND      | GND       | GND        | GND         | GND       | GND        | DRAM_A4    | GND        | GND       | GND       | GND       | GND          | ENET_TXD1   | ENET_RXD0   | ENET_RXD1    | ENET_RX_ER  | DISP0_DAT23 | DRAM_D63    | W        |

| > | LVDS1_TX0_N | LVDS1_TX0_P | LVDS1_CLK_N  | LVDS1_CLK_P | GND       | DRAM_RESET | DRAM_D20     | DRAM_D21 | DRAM_D19  | DRAM_D25   | DRAM_SDCKE0 | DRAM_A15  | DRAM_A7    | DRAM_A3    | DRAM_SDBA1 | DRAM_CS0  | DRAM_D36  | DRAM_D37  | DRAM_D40     | DRAM_D44    | DRAM_DQM7   | DRAM_D59     | DRAM_D62    | GND         | DRAM_D58    | <b>\</b> |