#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                     | Not For New Designs                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s6avm08abr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic   | Block Name                           | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENET             | Ethernet Controller                  | Connectivity<br>Peripherals | The Ethernet Media Access Controller (MAC) is<br>designed to support 10/100/1000 Mbps Ethernet/IEEE<br>802.3 networks. An external transceiver interface and<br>transceiver function are required to complete the<br>interface to the media. The module has dedicated<br>hardware to support the IEEE 1588 standard. See the<br>ENET chapter of the reference manual for details.<br><b>Note:</b> The theoretical maximum performance of 1 Gbps<br>ENET is limited to 470 Mbps (total for Tx and Rx) due to<br>internal bus throughput limitations. The actual<br>measured performance in optimized environment is up<br>to 400 Mbps. For details, see the ERR004512 erratum<br>in the i.MX 6Solo/6DualLite errata document<br>(IMX6SDLCE).                                                                                                                                                                                                                                                                                                                   |

| EPIT-1<br>EPIT-2 | Enhanced Periodic<br>Interrupt Timer | Timer Peripherals           | Each EPIT is a 32-bit "set and forget" timer that starts<br>counting after the EPIT is enabled by software. It is<br>capable of providing precise interrupts at regular<br>intervals with minimal processor intervention. It has a<br>12-bit prescaler for division of input clock frequency to<br>get the required time setting for the interrupts to occur,<br>and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ESAI             | Enhanced Serial Audio<br>Interface   | Connectivity<br>Peripherals | The Enhanced Serial Audio Interface (ESAI) provides a<br>full-duplex serial port for serial communication with a<br>variety of serial devices, including industry-standard<br>codecs, SPDIF transceivers, and other processors.<br>The ESAI consists of independent transmitter and<br>receiver sections, each section with its own clock<br>generator. All serial transfers are synchronized to a<br>clock. Additional synchronization signals are used to<br>delineate the word frames. The normal mode of<br>operation is used to transfer data at a periodic rate, one<br>word per period. The network mode is also intended for<br>periodic transfers; however, it supports up to 32 words<br>(time slots) per period. This mode can be used to build<br>time division multiplexed (TDM) networks. In contrast,<br>the on-demand mode is intended for non-periodic<br>transfers of data and to transfer data serially at high<br>speed when the data becomes available.<br>The ESAI has 12 pins for data and clocking connection<br>to external devices. |

| Table 2. i.MX 6Solo/6DualLite | Modules Li | ist (continued) |

|-------------------------------|------------|-----------------|

|-------------------------------|------------|-----------------|

## **Modules List**

| Block Mnemonic | Block Name                    | Subsystem                            | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPU            | Video Processing Unit         | Multimedia<br>Peripherals            | A high-performing video processing unit (VPU), which<br>covers many SD-level and HD-level video decoders and<br>SD-level encoders as a multi-standard video codec<br>engine as well as several important video processing,<br>such as rotation and mirroring.<br>See the i. <i>MX 6Solo/6DualLite Reference Manual</i><br>( <i>IMX6SDLRM</i> ) for complete list of VPU's<br>decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                            |

| WDOG-1         | Watch Dog                     | Timer Peripherals                    | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-2<br>(TZ) | Watch Dog (TrustZone)         | Timer Peripherals                    | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW. |

| WEIM           | NOR-Flash /PSRAM<br>interface | Connectivity<br>Peripherals          | <ul> <li>The WEIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALOSC        | Crystal Oscillator I/F        | Clocks, Resets, and<br>Power Control | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator to provide USB required frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**Electrical Characteristics**

# 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics for the i.MX 6Solo/6DualLite processors.

# 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 6 for a quick reference to the individual tables and sections.

| For these characteristics,               | Topic appears |

|------------------------------------------|---------------|

| Absolute Maximum Ratings                 | on page 22    |

| BGA Case 2240 Package Thermal Resistance | on page 23    |

| Operating Ranges                         | on page 24    |

| External Clock Sources                   | on page 26    |

| Maximal Supply Currents                  | on page 27    |

| Low Power Mode Supply Currents           | on page 29    |

| USB PHY Current Consumption              | on page 30    |

| PCIe 2.0 Power Consumption               | on page 30    |

# 4.1.1 Absolute Maximum Ratings

## Table 7. Absolute Maximum Ratings

| Parameter Description                                                 | Symbol                                | Min  | Мах                    | Unit |

|-----------------------------------------------------------------------|---------------------------------------|------|------------------------|------|

| Core supply voltages                                                  | VDDARM_IN<br>VDDSOC_IN                | -0.3 | 1.5                    | V    |

| Internal supply voltages                                              | VDDARM_CAP<br>VDDSOC_CAP<br>VDDPU_CAP | -0.3 | 1.3                    | V    |

| GPIO supply voltage                                                   | Supplies denoted as I/O supply        | -0.5 | 3.6                    | V    |

| DDR I/O supply voltage                                                | Supplies denoted as I/O supply        | -0.4 | 1.975                  | V    |

| MLB I/O supply voltage                                                | Supplies denoted as I/O supply        | -0.3 | 2.8                    | V    |

| LVDS I/O supply voltage                                               | Supplies denoted as I/O supply        | -0.3 | 2.8                    | V    |

| VDD_SNVS_IN supply voltage                                            | VDD_SNVS_IN                           | -0.3 | 3.3                    | V    |

| VDDHIGH_IN supply voltage                                             | VDDHIGH_IN                            | -0.3 | 3.6                    | V    |

| USB VBUS                                                              | VBUS                                  |      | 5.25                   | V    |

| Input voltage on USB_OTG_DP, USB_OTG_DN,<br>USB_H1_DP, USB_H1_DN pins | USB_DP/USB_DN                         | -0.3 | 3.63                   | V    |

| Input/output voltage range                                            | V <sub>in</sub> /V <sub>out</sub>     | -0.5 | OVDD <sup>1</sup> +0.3 | V    |

# 4.1.6 Low Power Mode Supply Currents

Table 13 shows the current core consumption (not including I/O) of i.MX 6Solo/6DualLite processors in selected low power modes.

| Mode                     | Test Conditions                                                                                                                                                                               | Supply            | Typical <sup>1</sup> | Units |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|-------|

| WAIT                     | • ARM, SoC, and PU LDOs are set to 1.225                                                                                                                                                      | VDDARM_IN (1.4V)  | 4.5                  | mA    |

|                          | <ul> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated.</li> </ul>                                                                                                                          | VDDSOC_IN (1.4V)  | 23                   |       |

|                          | <ul> <li>DDR is in self refresh.</li> <li>PLLs are active in bypass (24MHz)</li> </ul>                                                                                                        | VDDHIGH_IN (3.0V) | 13.5                 |       |

|                          | Supply Voltages remain ON                                                                                                                                                                     | Total             | 79                   | mW    |

| STOP_ON                  | ARM LDO set to 0.9V                                                                                                                                                                           | VDDARM_IN (1.4V)  | 4                    | mA    |

|                          | <ul> <li>SoC and PU LDOs set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> </ul>                                                                                                             | VDDSOC_IN (1.4V)  | 22                   |       |

|                          | <ul> <li>PLLs disabled</li> <li>DDR is in self refresh.</li> </ul>                                                                                                                            | VDDHIGH_IN (3.0V) | 8.5                  |       |

|                          |                                                                                                                                                                                               | Total             | 61.9                 | mW    |

| STOP_OFF                 | <ul> <li>ARM LDO set to 0.9V</li> <li>SoC LDO set to: 1.225 V</li> <li>PU LDO is power gated</li> <li>HIGH LDO set to 2.5 V</li> <li>PLLs disabled</li> <li>DDR is in self refresh</li> </ul> | VDDARM_IN (1.4V)  | 4                    | mA    |

|                          |                                                                                                                                                                                               | VDDSOC_IN (1.4V)  | 13.5                 |       |

|                          |                                                                                                                                                                                               | VDDHIGH_IN (3.0V) | 7.5                  |       |

|                          |                                                                                                                                                                                               | Total             | 47                   | mW    |

| STANDBY                  | ARM and PU LDOs are power gated                                                                                                                                                               | VDDARM_IN (0.9V)  | 0.1                  | mA    |

|                          | <ul> <li>SoC LDO is in bypass</li> <li>HIGH LDO is set to 2.5V</li> </ul>                                                                                                                     | VDDSOC_IN (0.9V)  | 5                    |       |

|                          | <ul><li>PLLs are disabled</li><li>Low Voltage</li></ul>                                                                                                                                       | VDDHIGH_IN (3.0V) | 5                    |       |

|                          | Well Bias ON     XTAL is enabled                                                                                                                                                              | Total             | 19.6                 | mW    |

| Deep Sleep Mode<br>(DSM) | ARM and PU LDOs are power gated                                                                                                                                                               | VDDARM_IN (0.9V)  | 0.1                  | mA    |

|                          | <ul> <li>SoC LDO is in bypass</li> <li>HIGH LDO is set to 2.5V</li> </ul>                                                                                                                     | VDDSoC_IN (0.9V)  | 2                    | 1     |

|                          | <ul><li>PLLs are disabled</li><li>Low Voltage</li></ul>                                                                                                                                       | VDDHIGH_IN (3.0V) | 0.5                  | ]     |

|                          | <ul><li>Well Bias ON</li><li>XTAL and bandgap are disabled</li></ul>                                                                                                                          | Total             | 3.4                  | mW    |

Table 13. Stop Mode Current and Power Consumption

The typical values shown here are for information only and are not guaranteed. These values are average values measured on a typical wafer at 25°C.

1

# 4.1.9 HDMI Power Consumption

Table 16 provides HDMI PHY currents for both Active 3D Tx with LFSR15 data and power-down modes.

| Mode       | Test Conditions      | Supply   | Max Current | Unit |

|------------|----------------------|----------|-------------|------|

| Active     | Bit rate 251.75 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.1         | mA   |

|            | Bit rate 279.27 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.2         | mA   |

|            | Bit rate 742.5 Mbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 7.5         | mA   |

|            | Bit rate 1.485 Gbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 12          | mA   |

|            | Bit rate 2.275 Gbps  | HDMI_VPH | 16          | mA   |

|            |                      | HDMI_VP  | 17          | mA   |

|            | Bit rate 2.97 Gbps   | HDMI_VPH | 19          | mA   |

|            |                      | HDMI_VP  | 22          | mA   |

| Power-down |                      | HDMI_VPH | 49          | μΑ   |

|            |                      | HDMI_VP  | 1100        | μΑ   |

## Table 16. HDMI PHY Current Drain

# 4.2 **Power Supplies Requirements and Restrictions**

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to guarantee the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor (worst-case scenario)

# 4.2.1 Power-Up Sequence

The below restrictions must be followed:

- VDD\_SNVS\_IN supply must be turned on before any other power supply or be connected (shorted) with VDDHIGH\_IN supply.

- If a coin cell is used to power VDD\_SNVS\_IN, then ensure that it is connected before any other supply is switched on.

- If VDDARM\_IN and VDDSOC\_IN are connected to different external supply sources, then the following restrictions apply:

- 2. Calibration is done against 240  $\Omega$  external reference resistor.

- 3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

# 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

# 4.8.4 MLB I/O Differential Output Impedance

Table 38 shows MLB I/O differential output impedance of the i.MX 6Solo/6DualLite processors.

## Table 38. MLB I/O Differential Output Impedance

| Parameter                     | Symbol | Test Conditions | Min   | Тур | Мах | Unit |

|-------------------------------|--------|-----------------|-------|-----|-----|------|

| Differential Output Impedance | Zo     |                 | 1.6 K |     | _   | Ω    |

# 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Solo/6DualLite processor.

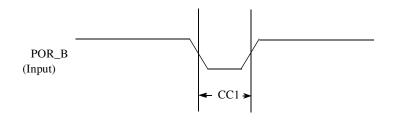

## 4.9.1 Reset Timings Parameters

Figure 10 shows the reset timing and Table 39 lists the timing parameters.

Figure 10. Reset Timing Diagram

| Table 39. Reset | Timing | Parameters |

|-----------------|--------|------------|

|-----------------|--------|------------|

| ID  | Parameter                                                       | Min | Max | Unit               |

|-----|-----------------------------------------------------------------|-----|-----|--------------------|

| CC1 | Duration of POR_B to be qualified as valid (input slope = 5 ns) | 1   |     | RTC_XTALI<br>cycle |

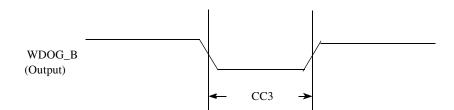

# 4.9.2 WDOG Reset Timing Parameters

Figure 11 shows the WDOG reset timing and Table 40 lists the timing parameters.

Figure 11. WDOG\_B Timing Diagram

Table 40. WDOG\_B Timing Parameters

| ID  | Parameter                    | Min | Мах | Unit               |

|-----|------------------------------|-----|-----|--------------------|

| CC3 | Duration of WDOG_B Assertion | 1   | _   | RTC_XTALI<br>cycle |

## NOTE

RTC\_XTALI is approximately 32 kHz. RTC\_XTALI cycle is one period or approximately 30  $\mu$ s.

## NOTE

WDOG\_B output signals (for each one of the Watchdog modules) do not have dedicated pins, but are muxed out through the IOMUX. See the IOMUX manual for detailed information.

# 4.9.3 External Interface Module (EIM)

The following subsections provide information on the EIM.

## 4.9.3.1 EIM Signal Cross Reference

Table 41 is a guide intended to help the user identify signals in the External Interface Module chapter of the reference manual that are identical to those mentioned in this data sheet.

| Reference Manual EIM Chapter<br>Nomenclature | Data Sheet Nomenclature, Reference Manual External Signals and Pin<br>Multiplexing Chapter, and IOMUXC Controller Chapter Nomenclature |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| BCLK                                         | EIM_BCLK                                                                                                                               |

| CSx_B                                        | EIM_CSx                                                                                                                                |

| WE_B                                         | EIM_RW                                                                                                                                 |

| OE_B                                         | EIM_OE                                                                                                                                 |

| BEy_B                                        | EIM_EBx                                                                                                                                |

## Table 41. EIM Signal Cross Reference

### **Electrical Characteristics**

| Ref No.                 | Parameter                                                                 | Determination by<br>Synchronous measured<br>parameters <sup>1</sup>               | Min                                        | Max<br>(If 132 MHz is<br>supported by SoC) | Unit |

|-------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------|------|

| WE31                    | CSx_B valid to Address Valid                                              | WE4 - WE6 - CSA <sup>2</sup>                                                      | _                                          | 3 - CSA                                    | ns   |

| WE32                    | Address Invalid to CSx_B invalid                                          | WE7 - WE5 - CSN <sup>3</sup>                                                      | _                                          | 3 - CSN                                    | ns   |

| WE32A(<br>muxed<br>A/D  | CSx_B valid to Address Invalid                                            | t <sup>4</sup> + WE4 - WE7 + (ADVN <sup>5</sup> +<br>ADVA <sup>6</sup> + 1 - CSA) | -3 + (ADVN +<br>ADVA + 1 - CSA)            | _                                          | ns   |

| WE33                    | CSx_B Valid to WE_B Valid                                                 | WE8 - WE6 + (WEA - WCSA)                                                          | _                                          | 3 + (WEA - WCSA)                           | ns   |

| WE34                    | WE_B Invalid to CSx_B Invalid                                             | WE7 - WE9 + (WEN - WCSN)                                                          | _                                          | 3 - (WEN_WCSN)                             | ns   |

| WE35                    | CSx_B Valid to OE_B Valid                                                 | WE10 - WE6 + (OEA - RCSA)                                                         |                                            | 3 + (OEA - RCSA)                           | ns   |

| WE35A<br>(muxed<br>A/D) | CSx_B Valid to OE_B Valid                                                 | WE10 - WE6 + (OEA + RADVN<br>+ RADVA + ADH + 1 - RCSA)                            | -3 + (OEA +<br>RADVN+RADVA+<br>ADH+1-RCSA) | 3 + (OEA +<br>RADVN+RADVA+AD<br>H+1-RCSA)  | ns   |

| WE36                    | OE_B Invalid to CSx_B Invalid                                             | WE7 - WE11 + (OEN - RCSN)                                                         |                                            | 3 - (OEN - RCSN)                           | ns   |

| WE37                    | CSx_B Valid to BEy_B Valid (Read access)                                  | WE12 - WE6 + (RBEA - RCSA)                                                        | —                                          | 3 + (RBEA - RCSA)                          | ns   |

| WE38                    | BEy_B Invalid to CSx_B Invalid (Read access)                              | WE7 - WE13 + (RBEN - RCSN)                                                        | —                                          | 3 - (RBEN- RCSN)                           | ns   |

| WE39                    | CSx_B Valid to ADV_B Valid                                                | WE14 - WE6 + (ADVA - CSA)                                                         |                                            | 3 + (ADVA - CSA)                           | ns   |

| WE40                    | ADV_B Invalid to CSx_B Invalid (ADVL is asserted)                         | WE7 - WE15 - CSN                                                                  | _                                          | 3 - CSN                                    | ns   |

| WE40A<br>(muxed<br>A/D) | CSx_B Valid to ADV_B Invalid                                              | WE14 - WE6 + (ADVN + ADVA<br>+ 1 - CSA)                                           | -3 + (ADVN +<br>ADVA + 1 - CSA)            | 3 + (ADVN + ADVA +<br>1 - CSA)             | ns   |

| WE41                    | CSx_B Valid to Output Data<br>Valid                                       | WE16 - WE6 - WCSA                                                                 | _                                          | 3 - WCSA                                   | ns   |

| WE41A<br>(muxed<br>A/D) | CSx_B Valid to Output Data<br>Valid                                       | WE16 - WE6 + (WADVN +<br>WADVA + ADH + 1 - WCSA)                                  | _                                          | 3 + (WADVN +<br>WADVA + ADH + 1 -<br>WCSA) | ns   |

| WE42                    | Output Data Invalid to CSx_B<br>Invalid                                   | WE17 - WE7 - CSN                                                                  | —                                          | 3 - CSN                                    | ns   |

| MAXCO                   | Output max. delay from internal driving ADDR/control FFs to chip outputs. | 10                                                                                |                                            | -                                          | ns   |

| MAXCS<br>O              | Output max. delay from CSx internal driving FFs to CSx out.               | 10                                                                                | _                                          | _                                          |      |

| MAXDI                   | DATA MAXIMUM delay from chip input data to its internal FF                | 5                                                                                 | _                                          | —                                          |      |

## Table 44. EIM Asynchronous Timing Parameters Table Relative Chip Select

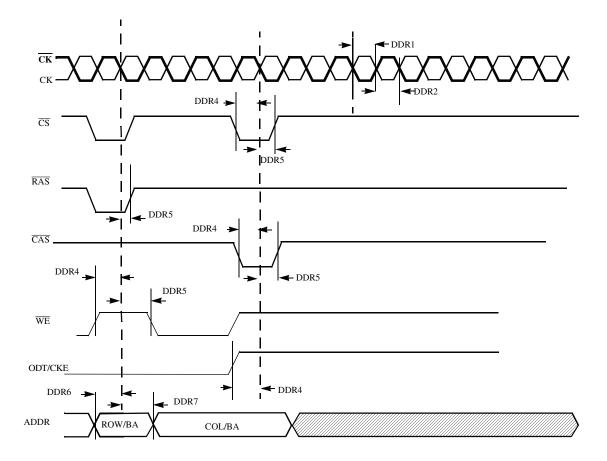

# 4.9.4 DDR SDRAM Specific Parameters (DDR3/DDR3L and LPDDR2)

## 4.9.4.1 DDR3/DDR3L Parameters

Figure 24 shows the basic timing parameters. The timing parameters for this diagram appear in Table 45.

Figure 24. DDR3 Command and Address Timing Parameters

| ID   | Parameter                             | Symbol   | CK = 40 | 00 MHz | Unit |

|------|---------------------------------------|----------|---------|--------|------|

| U    | Parameter                             | Symbol - | Min     | Мах    | Unit |

| DDR1 | CK clock high-level width             | tсн      | 0.47    | 0.53   | tск  |

| DDR2 | CK clock low-level width              | tCL      | 0.47    | 0.53   | tск  |

| DDR4 | CS, RAS, CAS, CKE, WE, ODT setup time | tis      | 800     | —      | ps   |

| DDR5 | CS, RAS, CAS, CKE, WE, ODT hold time  | tıн      | 580     | —      | ps   |

| DDR6 | Address output setup time             | tis      | 800     | _      | ps   |

| DDR7 | Address output hold time              | tін      | 580     | _      | ps   |

| Table 45. DDR3/DDR3L Timi | ing Parameter Table |

|---------------------------|---------------------|

|---------------------------|---------------------|

# 4.11.4 Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC timing

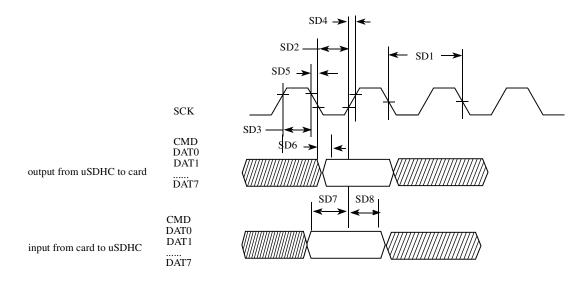

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing, eMMC4.4 (Dual Date Rate) timing and SDR104/50(SD3.0) timing.

# 4.11.4.1 SD/eMMC4.3 (Single Data Rate) AC Timing

Figure 44 depicts the timing of SD/eMMC4.3, and Table 57 lists the SD/eMMC4.3 timing characteristics.

## Figure 44. SD/eMMC4.3 Timing

| ID  | Parameter                                       | ameter Symbols Min           |      | Мах   | Unit |

|-----|-------------------------------------------------|------------------------------|------|-------|------|

|     | Card Input Clock                                | (                            |      |       |      |

| SD1 | Clock Frequency (Low Speed)                     | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |

|     | Clock Frequency (SD/SDIO Full Speed/High Speed) | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |

|     | Clock Frequency (MMC Full Speed/High Speed)     | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |

|     | Clock Frequency (Identification Mode)           | f <sub>OD</sub>              | 100  | 400   | kHz  |

| SD2 | Clock Low Time                                  | t <sub>WL</sub>              | 7    | —     | ns   |

| SD3 | Clock High Time                                 | t <sub>WH</sub>              | 7    | —     | ns   |

| SD4 | Clock Rise Time                                 | t <sub>TLH</sub>             | _    | 3     | ns   |

| SD5 | Clock Fall Time                                 | t <sub>THL</sub>             | _    | 3     | ns   |

|     | uSDHC Output/Card Inputs CMD, DA                | T (Reference to              | CLK) |       |      |

| SD6 | uSDHC Output Delay                              | t <sub>OD</sub>              | -6.6 | 3.6   | ns   |

## Table 57. SD/eMMC4.3 Interface Timing Specification

### **Electrical Characteristics**

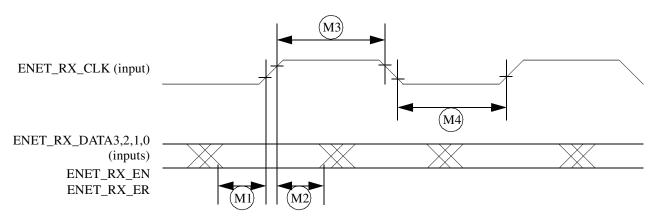

Figure 47 shows MII receive signal timings. Table 60 describes the timing parameters (M1–M4) shown in the figure.

Figure 47. MII Receive Signal Timing Diagram

Table 60. MII Receive Signal Timing

| ID | Characteristic <sup>1</sup>                                        | Min. | Max. | Unit               |

|----|--------------------------------------------------------------------|------|------|--------------------|

| M1 | ENET_RX_DATA3,2,1,0, ENET_RX_EN, ENET_RX_ER to ENET_RX_CLK setup   | 5    | _    | ns                 |

| M2 | ENET_RX_CLK to ENET_RX_DATA3,2,1,0, ENET_RX_EN,<br>ENET_RX_ER hold | 5    | _    | ns                 |

| М3 | ENET_RX_CLK pulse width high                                       | 35%  | 65%  | ENET_RX_CLK period |

| M4 | ENET_RX_CLK pulse width low                                        | 35%  | 65%  | ENET_RX_CLK period |

<sup>1</sup> ENET\_RX\_EN, ENET\_RX\_CLK, and ENET0\_RXD0 have the same timing in 10 Mbps 7-wire interface mode.

# 4.11.5.1.2 MII Transmit Signal Timing (ENET\_TX\_DATA3,2,1,0, ENET\_TX\_EN, ENET\_TX\_ER, and ENET\_TX\_CLK)

The transmitter functions correctly up to an ENET\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_TX\_CLK frequency.

# NOTE

Table 71 provides information for both the Disp0 and Disp1 ports. However, Disp1 port has reduced pinout depending on IOMUXC configuration and therefore may not support all the above configurations. See the IOMUXC table for details.

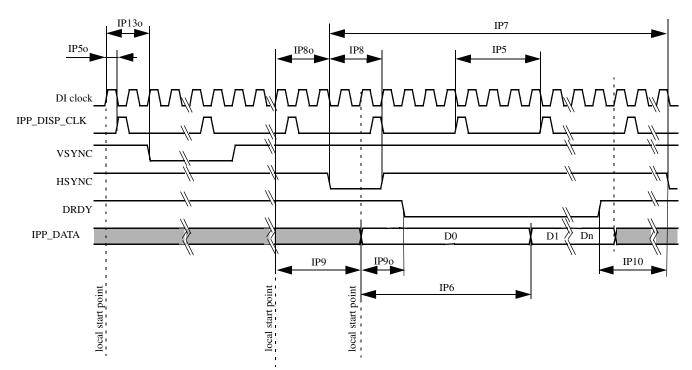

# 4.11.10.5 IPU Display Interface Timing

The IPU Display Interface supports two kinds of display accesses: synchronous and asynchronous. There are two groups of external interface pins to provide synchronous and asynchronous controls accordantly.

## 4.11.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent wave form.

There are special physical outputs to provide synchronous controls:

- The ipp\_disp\_clk is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

- The ipp\_pin\_1- ipp\_pin\_7 are general purpose synchronous pins, that can be used to provide HSYNC, VSYNC, DRDY or any else independent signal to a display.

The IPU has a system of internal binding counters for internal events (such as, HSYNC/VSYCN) calculation. The internal event (local start point) is synchronized with internal DI\_CLK. A suitable control starts from the local start point with predefined UP and DOWN values to calculate control's changing points with half DI\_CLK resolution. A full description of the counters system can be found in the IPU chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM).

## 4.11.10.5.2 Asynchronous Controls

The asynchronous control is a data-oriented signal that changes its value with an output data according to additional internal flags coming with the data.

There are special physical outputs to provide asynchronous controls, as follows:

- The ipp\_d0\_cs and ipp\_d1\_cs pins are dedicated to provide chip select signals to two displays.

- The ipp\_pin\_11- ipp\_pin\_17 are general purpose asynchronous pins, that can be used to provide WR. RD, RS or any other data oriented signal to display.

## NOTE

The IPU has independent signal generators for asynchronous signals toggling. When a DI decides to put a new asynchronous data in the bus, a new internal start (local start point) is generated. The signals generators calculate predefined UP and DOWN values to change pins states with half DI\_CLK resolution.

## 4.11.10.6.3 TFT Panel Sync Pulse Timing Diagrams

Figure 68 depicts the horizontal timing (timing of one line), including both the horizontal sync pulse and the data. All the parameters shown in the figure are programmable. All controls are started by corresponding internal events—local start points. The timing diagrams correspond to inverse polarity of the IPP\_DISP\_CLK signal and active-low polarity of the HSYNC, VSYNC, and DRDY signals.

Figure 68. TFT Panels Timing Diagram—Horizontal Sync Pulse

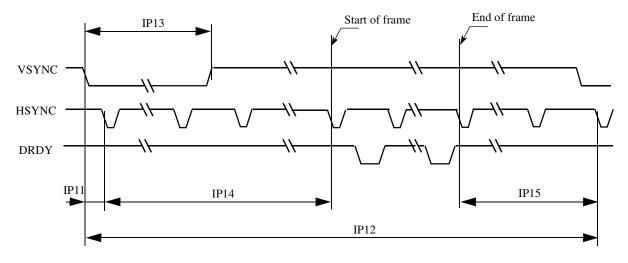

Figure 69 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

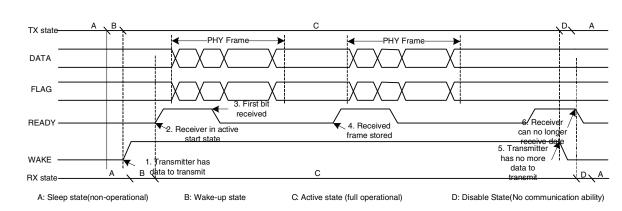

## 4.11.13.4 Synchronized Data Flow Transmission with Wake

Figure 81. Synchronized Data Flow Transmission with WAKE

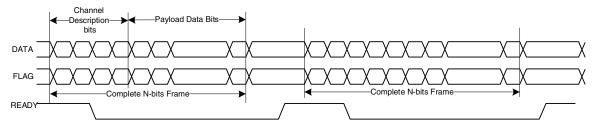

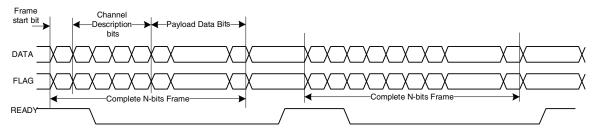

## 4.11.13.5 Stream Transmission Mode Frame Transfer

Figure 82. Stream Transmission Mode Frame Transfer (Synchronized Data Flow)

## 4.11.13.6 Frame Transmission Mode (Synchronized Data Flow)

Figure 83. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

# 4.11.14 MediaLB (MLB) Characteristics

## 4.11.14.1 MediaLB (MLB) DC Characteristics

Table 78 lists the MediaLB 3-pin interface electrical characteristics.

## Table 78. MediaLB 3-Pin Interface Electrical DC Specifications

| Parameter                   | Symbol          | Test Conditions           | Min | Max | Unit |

|-----------------------------|-----------------|---------------------------|-----|-----|------|

| Maximum input voltage       | —               | —                         | _   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | _                         | _   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>     | 1.8 | _   | V    |

| Low level output threshold  | V <sub>OL</sub> | I <sub>OL</sub> = 6 mA    | _   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = -6 mA   | 2.0 | —   | V    |

| Input leakage current       | ١L              | 0 < V <sub>in</sub> < VDD | _   | ±10 | μA   |

<sup>1</sup> Higher V<sub>IH</sub> thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

## Table 79 lists the MediaLB 6-pin interface electrical characteristics.

## Table 79. MediaLB 6-Pin Interface Electrical DC Specifications

| Symbol             | Test Conditions                                                              | Min                                                                                                                                                                                                                                                                                                               | Max                                                                                                                                                                     | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                  | Driver Characteristics                                                       |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>OD</sub>    | See Note <sup>1</sup>                                                        | 300                                                                                                                                                                                                                                                                                                               | 500                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ΔV <sub>OD</sub>   | _                                                                            | -50                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                      | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>OCM</sub>   | _                                                                            | 1.0                                                                                                                                                                                                                                                                                                               | 1.5                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ΔV <sub>OCM</sub>  | _                                                                            | -50                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                      | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>CMV</sub>   | See Note <sup>2</sup>                                                        | _                                                                                                                                                                                                                                                                                                                 | 150                                                                                                                                                                     | mVpp                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ll <sub>OS</sub> l | See Note <sup>3</sup>                                                        |                                                                                                                                                                                                                                                                                                                   | 43                                                                                                                                                                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ZO                 | _                                                                            | 1.6                                                                                                                                                                                                                                                                                                               | _                                                                                                                                                                       | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    | V <sub>OD</sub><br>ΔV <sub>OD</sub><br>V <sub>OCM</sub><br>ΔV <sub>OCM</sub> | Driver Characteristics           V <sub>OD</sub> See Note <sup>1</sup> ΔV <sub>OD</sub> —           ΔV <sub>OD</sub> —           V <sub>OCM</sub> —           ΔV <sub>OCM</sub> —           ΔV <sub>OCM</sub> —           V <sub>CMV</sub> See Note <sup>2</sup> II <sub>OS</sub> I         See Note <sup>3</sup> | Driver Characteristics $V_{OD}$ See Note1300 $\Delta V_{OD}$ —-50 $V_{OCM}$ —1.0 $\Delta V_{OCM}$ —-50 $\Delta V_{OCM}$ —-50 $V_{CMV}$ See Note2— $II_{OS}I$ See Note3— | Driver Characteristics         300         500 $\Delta V_{OD}$ See Note <sup>1</sup> 300         500 $\Delta V_{OD}$ -         -50         50 $\nabla_{OCM}$ -         1.0         1.5 $\Delta V_{OCM}$ -         -50         50 $\nabla_{OCM}$ -         -         50 $\nabla_{VOCM}$ -         -         50 $\nabla_{VOCM}$ -         -         50 $\nabla_{VOCM}$ See Note <sup>2</sup> -         150 $II_{OS}I$ See Note <sup>3</sup> -         43 |

| Characteristics                                                                         | Symbol  | Timing Para | meter Range         | Unit |

|-----------------------------------------------------------------------------------------|---------|-------------|---------------------|------|

| Characteristics                                                                         | Symbol  | Min         | Max                 | Onn  |

| SPDIFIN Skew: asynchronous inputs, no specs apply                                       | _       | _           | 0.7                 | ns   |

| SPDIFOUT output (Load = 50pf)<br>• Skew<br>• Transition rising<br>• Transition falling  |         |             | 1.5<br>24.2<br>31.3 | ns   |

| SPDIFOUT1 output (Load = 30pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         | <br><br>    | 1.5<br>13.6<br>18.0 | ns   |

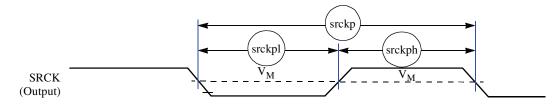

| Modulating Rx clock (SRCK) period                                                       | srckp   | 40.0        | _                   | ns   |

| SRCK high period                                                                        | srckph  | 16.0        | _                   | ns   |

| SRCK low period                                                                         | srckpl  | 16.0        |                     | ns   |

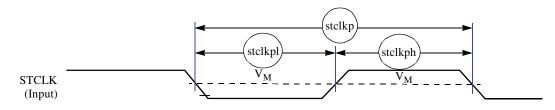

| Modulating Tx clock (STCLK) period                                                      | stclkp  | 40.0        | —                   | ns   |

| STCLK high period                                                                       | stclkph | 16.0        | _                   | ns   |

| STCLK low period                                                                        | stclkpl | 16.0        | —                   | ns   |

## **Table 85. SPDIF Timing Parameters**

Figure 93. SRCK Timing Diagram

Figure 94. STCLK Timing Diagram

NOTES:

1. ALL DIMENSIONS IN MILLIMETERS.

2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\$  MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|---------------|---------|--------------------|-------------|

| TITLE: PBGA, LOW PROF                                   | FILE,         | DOCUMEI | NT NO: 98ASA00404D | REV: O      |

| FINE PITCH, 624                                         | , .           | CASE NU | JMBER: 2240-01     | 27 SEP 2011 |

| 21 X 21 PKG, 0.8 MM F                                   | ИТСН (МАР)    | STANDAF | RD: NON-JEDEC      |             |

### Figure 105. 21 x 21 mm BGA, Case 2240 Package Top, Bottom, and Side Views

## Package Information and Contact Assignments

|           |      |              |              | Out of Reset Condition <sup>2</sup> |                  |                      |                        |  |  |  |  |  |  |

|-----------|------|--------------|--------------|-------------------------------------|------------------|----------------------|------------------------|--|--|--|--|--|--|

| Ball Name | Ball | Power Group  | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Outpu<br>t | Value                  |  |  |  |  |  |  |

| RTC_XTALI | D9   | VDD_SNVS_CAP |              |                                     |                  |                      |                        |  |  |  |  |  |  |

| RTC_XTALO | C9   | VDD_SNVS_CAP |              |                                     |                  |                      |                        |  |  |  |  |  |  |

| SD1_CLK   | D20  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[20]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD1_CMD   | B21  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[18]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD1_DAT0  | A21  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[16]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD1_DAT1  | C20  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[17]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD1_DAT2  | E19  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[19]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD1_DAT3  | F18  | NVCC_SD1     | GPIO         | ALT5                                | gpio1.GPIO[21]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD2_CLK   | C21  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[10]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD2_CMD   | F19  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[11]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD2_DAT0  | A22  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[15]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD2_DAT1  | E20  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[14]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD2_DAT2  | A23  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[13]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD2_DAT3  | B22  | NVCC_SD2     | GPIO         | ALT5                                | gpio1.GPIO[12]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD3_CLK   | D14  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[3]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_CMD   | B13  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[2]    | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD3_DAT0  | E14  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[4]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT1  | F14  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[5]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT2  | A15  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[6]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT3  | B15  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[7]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT4  | D13  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[1]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT5  | C13  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[0]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD3_DAT6  | E13  | NVCC_SD3     | GPIO         | ALT5                                | gpio6.GPIO[18]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD3_DAT7  | F13  | NVCC_SD3     | GPIO         | ALT5                                | gpio6.GPIO[17]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD3_RST   | D15  | NVCC_SD3     | GPIO         | ALT5                                | gpio7.GPIO[8]    | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD4_CLK   | E16  | NVCC_NANDF   | GPIO         | ALT5                                | gpio7.GPIO[10]   | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD4_CMD   | B17  | NVCC_NANDF   | GPIO         | ALT5                                | gpio7.GPIO[9]    | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD4_DAT0  | D18  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[8]    | Input                | 100 kΩ pull-up         |  |  |  |  |  |  |

| SD4_DAT1  | B19  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[9]    | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

| SD4_DAT2  | F17  | NVCC_NANDF   | GPIO         | ALT5                                | gpio2.GPIO[10]   | Input                | 100 k $\Omega$ pull-up |  |  |  |  |  |  |

|           | _    |              |              | 1                                   | L                | -                    |                        |  |  |  |  |  |  |

Table 101. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

## Package Information and Contact Assignments

|    | AE             | AD           |

|----|----------------|--------------|

| -  | GND            | DRAM_D5      |

| 2  | DRAM_D1        | DRAM_D0      |

| e  | DRAM_SDQS0     | DRAM_SDQS0_B |

| 4  | DRAM_D7        | GND          |

| 5  | DRAM_D9        | DRAM_D8      |

| 9  | DRAM_SDQS1_B   | DRAM_SDQS1   |

| 7  | DRAM_D11       | GND          |

| 8  | DRAM_SDQS2_B   | DRAM_SDQS2   |

| 6  | DRAM_D24       | DRAM_D29     |

| 10 | DRAM_DQM3      | GND          |

| 11 | DRAM_D26       | DRAM_D30     |

| 12 | DRAM_A9        | DRAM_A12     |

| 13 | DRAM_A5        | GND          |

| 14 | DRAM_SDCLK_1_B | DRAM_SDCLK_1 |

| 15 | DRAM_SDCLK_0_B | DRAM_SDCLK_0 |

| 16 | DRAM_CAS       | GND          |

| 17 | ZQPAD          | DRAM_CS1     |

| 18 | NC             | NC           |

| 19 | NC             | GND          |

| 20 | NC             | NC           |

| 21 | NC             | NC           |

| 22 | NC             | GND          |

| 23 | NC             | NC           |

| 24 | NC             | NC           |

| 25 | GND            | NC           |

|    | AE             | AD           |

|    |                |              |

Table 102. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

Table 103 shows the 21 x 21 mm, 0.8 mm pitch ball map for the i.MX 6DualLite.

Table 103. 21 x 21 mm, 0.8 mm Pitch Ball Map

|   | -        | 2          | e        | 4        | ß      | 9          | ~      | 8             | 6         | 10          | ÷           | 12         | 13       | 4       | 15        | 16        | 17        | 18       | 19       | 20       | 21        | 52           | 23           | 24        | 25        |          |

|---|----------|------------|----------|----------|--------|------------|--------|---------------|-----------|-------------|-------------|------------|----------|---------|-----------|-----------|-----------|----------|----------|----------|-----------|--------------|--------------|-----------|-----------|----------|

|   | -        |            |          | ~        | 47     | <b>.</b>   |        | ~             | 0,        | -           | -           | -          | -        | -       | -         | -         | -         | -        | -        | 2        | 2         | 2            | 3            | Ñ         | 3         | <u> </u> |

| ٩ | NC       | PCIE_REXT  | PCIE_TXM | GND      | FA_ANA | USB_OTG_DP | XTALI  | GND           | MLB_SN    | MLB_DP      | MLB_CN      | NC         | GND      | NC      | SD3_DAT2  | NANDF_ALE | NANDF_CS2 | NANDF_D0 | NANDF_D4 | SD4_DAT3 | SD1_DAT0  | SD2_DAT0     | SD2_DAT2     | RGMII_TD3 | GND       | A        |

| ß | PCIE_RXM | PCIE_RXP   | PCIE_TXP | GND      | VDD_FA | USB_OTG_DN | XTALO  | USB_OTG_CHD_B | MLB_SP    | MLB_DN      | MLB_CP      | NC         | SD3_CMD  | NC      | SD3_DAT3  | NANDF_RB0 | SD4_CMD   | NANDF_D5 | SD4_DAT1 | SD4_DAT6 | SD1_CMD   | SD2_DAT3     | RGMII_RD1    | RGMII_RD2 | RGMII_RXC | B        |

| U | GND      | JTAG_TRSTB | JTAG_TMS | GND      | CLK2_N | GND        | CLK1_N | GPANAIO       | RTC_XTALO | GND         | POR_B       | BOOT_MODE0 | SD3_DAT5 | NC      | NANDF_CLE | NANDF_CS1 | NANDF_D1  | NANDF_D7 | SD4_DAT5 | SD1_DAT1 | SD2_CLK   | RGMII_TD0    | RGMII_TX_CTL | RGMII_RD0 | EIM_D16   | U        |

| ٥ | CSI_D1M  | CSI_D1P    | GND      | CSI_REXT | CLK2_P | GND        | CLK1_P | GND           | RTC_XTALI | USB_H1_VBUS | PMIC_ON_REQ | ONOFF      | SD3_DAT4 | SD3_CLK | SD3_RST   | NANDF_CS3 | NANDF_D3  | SD4_DAT0 | SD4_DAT7 | SD1_CLK  | RGMII_TXC | RGMII_RX_CTL | RGMII_RD3    | EIM_D18   | EIM_D23   | D        |

### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARM Cortex<sup>™</sup>-A9 is a trademark of ARM Limited.

© 2012 Freescale Semiconductor, Inc. All rights reserved.

Document Number: IMX6SDLAEC Rev. 1 11/2012