#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Betuns                             |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s6avm08acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic                   | Block Name                    | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCOTP_CTRL                       | OTP Controller                | Security                    | The On-Chip OTP controller (OCOTP_CTRL) provides<br>an interface for reading, programming, and/or overriding<br>identification and control information stored in on-chip<br>fuse elements. The module supports<br>electrically-programmable poly fuses (eFUSEs). The<br>OCOTP_CTRL also provides a set of volatile<br>software-accessible signals that can be used for<br>software control of hardware elements, not requiring<br>non-volatility. The OCOTP_CTRL provides the primary<br>user-visible mechanism for interfacing with on-chip fuse<br>elements. Among the uses for the fuses are unique chip<br>identifiers, mask revision numbers, cryptographic keys,<br>JTAG secure mode, boot characteristics, and various<br>control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>controller  | Data Path                   | The On-Chip Memory controller (OCRAM) module is<br>designed as an interface between system's AXI bus and<br>internal (on-chip) SRAM memory module.<br>In i.MX 6Solo/6DualLite processors, the OCRAM is<br>used for controlling the 128 KB multimedia RAM through<br>a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSC32KHz                         | OSC32KHz                      | Clocking                    | Generates 32.768 KHz clock from external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PMU                              | Power-Management<br>functions | Data Path                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width Modulation        | Connectivity<br>Peripherals | The pulse-width modulator (PWM) has a 16-bit counter<br>and is optimized to generate sound from stored sample<br>audio images and it can also generate tones. It uses<br>16-bit resolution and a 4x16 data FIFO to generate<br>sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAM<br>128 KB                    | Internal RAM                  | Internal Memory             | Internal RAM, which is accessed through OCRAM memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure RAM         | Secured Internal<br>Memory  | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ROM<br>96KB                      | Boot ROM                      | Internal Memory             | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ROMCP                            | ROM Controller with<br>Patch  | Data Path                   | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2. i.MX 6Solo/6DualLite M | Modules List (continued) |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

#### **Modules List**

| Block Mnemonic | Block Name                                  | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|---------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDMA           | Smart Direct Memory<br>Access               | System Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast Context-Switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

| SJC            | System JTAG Controller                      | System Control<br>Peripherals | The SJC provides JTAG interface, which complies with<br>JTAG TAP standards, to internal logic. The i.MX<br>6Solo/6DualLite processors use JTAG port for<br>production, testing, and system debugging. In addition,<br>the SJC provides BSR (Boundary Scan Register)<br>standard support, which complies with IEEE1149.1 and<br>IEEE1149.6 standards.<br>The JTAG port must be accessible during platform initial<br>laboratory bring-up, for manufacturing tests and<br>troubleshooting, as well as for software debugging by<br>authorized entities. The i.MX 6Solo/6DualLite SJC<br>incorporates three security modes for protecting against<br>unauthorized accesses. Modes are selected through<br>eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                  |

| SPDIF          | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals     | A standard audio file transfer format, developed jointly<br>by the Sony and Phillips corporations. Has Transmitter<br>and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SNVS           | Secure Non-Volatile<br>Storage              | Security                      | Secure Non-Volatile Storage, including Secure Real<br>Time Clock, Security State Machine, Master Key<br>Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

#### **Modules List**

| Signal Name      | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRAM_VREF        | When using DDR_VREF with DDR I/O, the nominal reference voltage must be half of the NVCC_DRAM supply. The user must tie DDR_VREF to a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_DRAM. Shunt each resistor with a closely-mounted 0.1 µF capacitor.                                                                                                                                                                    |

|                  | To reduce supply current, a pair of 1.5 k $\Omega$ 0.1% resistors can be used. Using resistors with recommended tolerances ensures the ± 2% DDR_VREF tolerance (per the DDR3 specification) is maintained when four DDR3 ICs plus the i.MX 6Solo/6DualLite are drawing current on the resistor divider.                                                                                                                                                                                           |

|                  | It is recommended to use regulated power supply for "big" memory configurations (more that eight devices)                                                                                                                                                                                                                                                                                                                                                                                         |

| ZQPAD            | DRAM calibration resistor 240 $\Omega$ 1% used as reference during DRAM output buffer driver calibration should be connected between this pad and GND.                                                                                                                                                                                                                                                                                                                                            |

| NVCC_LVDS2P5     | The DDR pre-drivers share the NVCC_LVDS2P5 ball with the LVDS interface. This ball can be shorted to VDDHIGH_CAP on the circuit board.                                                                                                                                                                                                                                                                                                                                                            |

| VDD_FA<br>FA_ANA | These signals are reserved for Freescale manufacturing use only. User must tie both connections to GND.                                                                                                                                                                                                                                                                                                                                                                                           |

| GPANAIO          | This signal is reserved for Freescale manufacturing use only. User must leave this connection floating.                                                                                                                                                                                                                                                                                                                                                                                           |

| JTAG_nnnn        | The JTAG interface is summarized in Table 4. Use of external resistors is unnecessary. However, if external resistors are used, the user must ensure that the on-chip pull-up/down configuration is followed. For example, do not use an external pull down on an input that has on-chip pull-up.                                                                                                                                                                                                 |

|                  | JTAG_TDO is configured with a keeper circuit such that the floating condition is eliminated if an external pull resistor is not present. An external pull resistor on JTAG_TDO is detrimental and should be avoided.                                                                                                                                                                                                                                                                              |

|                  | JTAG_MOD is referenced as SJC_MOD in the i.MX 6Solo/6DualLite reference manual. Both names refer to the same signal. JTAG_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed. JTAG_MOD set to hi configures the JTAG interface to mode compliant with IEEE1149.1 standard. JTAG_MOD set to low configures the JTAG interface for common SW debug adding all the system TAPs to the chain. |

| NC               | These signals are No Connect (NC) and should be floated by the user.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| POR_B            | This cold reset negative logic input resets all modules and logic in the IC.<br>May be used in addition to internally generated power on reset signal (logical AND, both internal<br>and external signals are considered active low).                                                                                                                                                                                                                                                             |

| ONOFF            | In normal mode may be connected to ON/OFF button (De-bouncing provided at this input).<br>Internally this pad is pulled up. Short connection to GND in OFF mode causes internal power<br>management state machine to change state to ON. In ON mode short connection to GND<br>generates interrupt (intended to SW controllable power down). Long above ~5s connection to GND<br>causes "forced" OFF.                                                                                             |

| TEST_MODE        | TEST_MODE is for Freescale factory use. This signal is internally connected to an on-chip pull-down device. The user must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                                                                              |

| PCIE_REXT        | The impedance calibration process requires connection of reference resistor 200 $\Omega$ 1% precision resistor on PCIE_REXT pad to ground.                                                                                                                                                                                                                                                                                                                                                        |

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 11 are required for use with Freescale BSPs to ensure precise time

keeping and USB operation. For RTC\_XTAL operation, two clock sources are available.

On-chip 40 kHz ring oscillator-this clock source has the following characteristics:

Approximately 25 µA more Idd than crystal oscillator

Approximately ±50% tolerance

No external component required

Starts up quicker than 32 kHz crystal oscillator

External crystal oscillator with on-chip support circuit:

At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

Higher accuracy than ring oscillator

If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision timeout.

## 4.1.5 Maximal Supply Currents

The Power Virus numbers shown in Table 12 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The MMPF0100xxxx, Freescale's power management IC targeted for the i.MX 6x family, supports the Power Virus mode operating at 1% duty cycle. Higher duty cycles are allowed, but a robust thermal design is required for the increased system power dissipation.

See the i.MX 6Solo/6DualLite Power Consumption Measurement Application Note (AN4576) for more details on typical power consumption under various use case definitions.

| Power Line                         | Conditions                                             | Max Current      | Unit |

|------------------------------------|--------------------------------------------------------|------------------|------|

| VDDARM_IN                          | 996 MHz ARM clock<br>based on Power Virus<br>operation | 2200             | mA   |

| VDDSOC_IN                          | 996 MHz ARM clock                                      | 1260             | mA   |

| VDDHIGH_IN                         |                                                        | 125 <sup>1</sup> | mA   |

| VDD_SNVS_IN                        |                                                        | 275 <sup>2</sup> | μA   |

| USB_OTG_VBUS/USB_H1_VBUS (LDO 3P0) |                                                        | 25 <sup>3</sup>  | mA   |

| Prima                              | ary Interface (IO) Supplies                            |                  |      |

Table 12. Maximal Supply Currents

- VDDARM\_IN supply must be turned ON together with VDDSOC\_IN supply or not delayed more than 1 ms

- VDDARM\_CAP must not exceed VDDSOC\_CAP by more than 50 mV.

### NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the *i.MX 6Solo/6DualLite Reference Manual* for further details and to ensure that all necessary requirements are being met.

### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

### NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and may be powered at any time.

### 4.2.2 Power-Down Sequence

No special restrictions for i.MX 6Solo/6DualLite IC.

## 4.2.3 **Power Supplies Usage**

All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Rail" columns in pin list tables of Section 6, "Package Information and Contact Assignments."

## 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for details on the power tree scheme.

### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

# 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of

Table 27 shows the Low Voltage Differential Signaling (LVDS) I/O DC parameters.

| Parameter                   | Symbol | Test Conditions         | Min   | Тур   | Мах   | Unit |

|-----------------------------|--------|-------------------------|-------|-------|-------|------|

| Output Differential Voltage | VOD    | Rload-100 $\Omega$ Diff | 250   | 350   | 450   | mV   |

| Output High Voltage         | VOH    | IOH = 0 mA              | 1.25  | 1.375 | 1.6   | V    |

| Output Low Voltage          | VOL    | IOL = 0 mA              | 0.9   | 1.025 | 1.25  | V    |

| Offset Voltage              | VOS    |                         | 1.125 | 1.2   | 1.375 | V    |

Table 27. LVDS I/O DC Characteristics

### 4.6.4 MLB I/O DC Parameters

The MLB interface complies with Analog Interface of 6-pin differential Media Local Bus specification version 4.1. See 6-pin differential MLB specification v4.1, "MediaLB 6-pin interface Electrical Characteristics" for details.

### NOTE

The MLB 6-pin interface does not support speed mode 8192 fs.

Table 28 shows the Media Local Bus (MLB) I/O DC parameters.

Table 28. MLB I/O DC Characteristics

| Parameter                                         | Symbol | Test Conditions        | Min  | Мах  | Unit |

|---------------------------------------------------|--------|------------------------|------|------|------|

| Output Differential Voltage                       | VOD    | Rload-50Ω Diff         | 300  | 500  | mV   |

| Output High Voltage                               | VOH    | Rload-50Ω Diff         | 1.25 | 1.75 | V    |

| Output Low Voltage                                | VOL    | Rload-50Ω Diff         | 0.75 | 1.25 | V    |

| Common-mode output voltage<br>((Vpadp*+Vpadn*)/2) | Vocm   | Rload-50 $\Omega$ Diff | 1    | 1.5  | V    |

| Differential output impedance                     | Zo     |                        | 1.6  |      | kΩ   |

# 4.7 I/O AC Parameters

This section includes the AC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

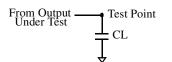

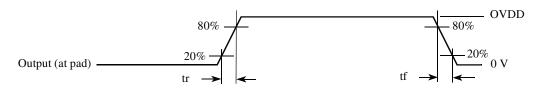

The GPIO and DDR I/O load circuit and output transition time waveforms are shown in Figure 4 and Figure 5.

CL includes package, probe and fixture capacitance

#### Figure 4. Load Circuit for Output

Figure 5. Output Transition Time Waveform

### 4.7.1 General Purpose I/O AC Parameters

The I/O AC parameters for GPIO in slow and fast modes are presented in the Table 29 and Table 30, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bits in the IOMUXC control registers.

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.20/3.36<br>1.96/2.07 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 |      |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | —                                                          | —   | —   | 25                     | ns   |

Table 29. General Purpose I/O AC Parameters 1.8 V Mode

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

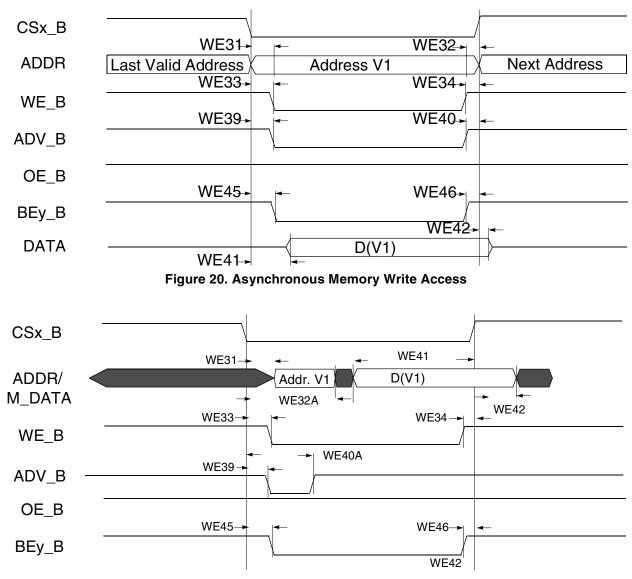

Figure 21. Asynchronous A/D Muxed Write Access

Figure 28 shows the write timing parameters. The timing parameters for this diagram appear in Table 49.

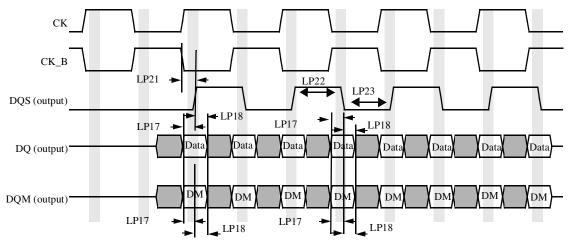

Figure 28. LPDDR2 Write Cycle

| Table 49. | LPDDR2 | Write | Cycle |

|-----------|--------|-------|-------|

|-----------|--------|-------|-------|

| ID   | Parameter                                                 | Symbol        | CK = 400 MHz |       | Unit |

|------|-----------------------------------------------------------|---------------|--------------|-------|------|

|      |                                                           |               | Min          | Max   |      |

| LP17 | DQ and DQM setup time to DQS (differential strobe)        | tDS           | 375          | —     | ps   |

| LP18 | DQ and DQM hold time to DQS (differential strobe)         | tdн           | 375          | —     | ps   |

| LP21 | DQS latching rising transitions to associated clock edges |               | -0.25        | +0.25 | tCK  |

| LP22 | DQS high level width                                      | <b>t</b> DQSH | 0.4          | -     | tCK  |

| LP23 | DQS low level width                                       | tDQSL         | 0.4          | -     | tCK  |

<sup>1</sup> To receive the reported setup and hold values, write calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

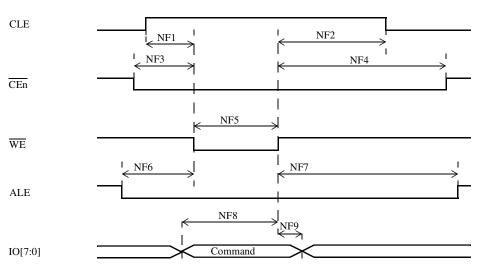

Figure 30. Command Latch Cycle Timing Diagram

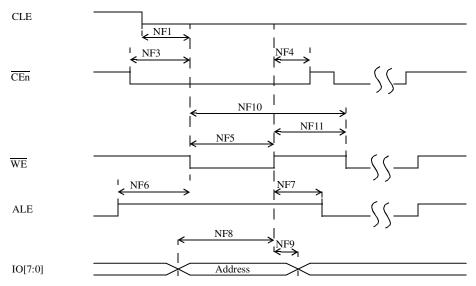

Figure 31. Address Latch Cycle Timing Diagram

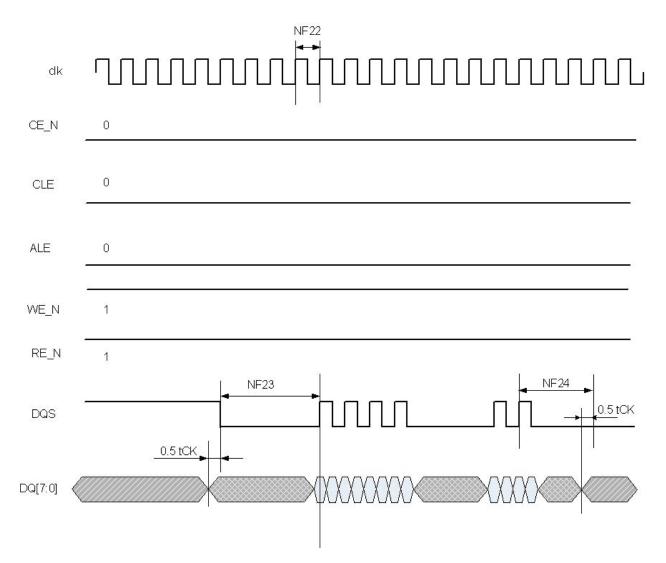

### 4.10.3.2 Read and Write Timing

Figure 38. Samsung Toggle Mode Data Write Timing

| No. | Characteristics <sup>1,2</sup>                                      | Symbol | Expression <sup>2</sup> | Min         | Max          | Condition <sup>3</sup> | Unit |

|-----|---------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 81  | SCKT rising edge to FST out (wr) low <sup>5</sup>                   |        |                         | _           | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                               | —      | —                       | _           | 19.0<br>9.0  | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                | —      | —                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance             | —      |                         | _           | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                  | —      |                         | _           | 18.0<br>13.0 | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>67</sup>           | —      |                         | _           | 21.0<br>16.0 | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>5</sup> | —      | —                       | 2.0<br>18.0 | —            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                  | —      |                         | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                         |        |                         | 4.0<br>5.0  |              | x ck<br>i ck           | ns   |

| 95  | HCKR/HCKT clock cycle                                               | —      | 2 x T <sub>C</sub>      | 15          |              | —                      | ns   |

| 96  | HCKT input rising edge to SCKT output                               | —      | —                       | —           | 18.0         | —                      | ns   |

| 97  | HCKR input rising edge to SCKR output                               | —      | —                       | _           | 18.0         | —                      | ns   |

#### Table 56. Enhanced Serial Audio Interface (ESAI) Timing (continued)

<sup>1</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that SCKT and SCKR are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that SCKT and SCKR are the same clock)

- <sup>2</sup> bl = bit length

- wl = word length

wr = word length relative

- <sup>3</sup> SCKT(SCKT pin) = transmit clock SCKR(SCKR pin) = receive clock FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync HCKT(HCKT pin) = transmit high frequency clock HCKR(HCKR pin) = receive high frequency clock

- <sup>4</sup> For the internal clock, the external clock cycle is defined by lcyc and the ESAI control register.

- <sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

- <sup>6</sup> Periodically sampled and not 100% tested.

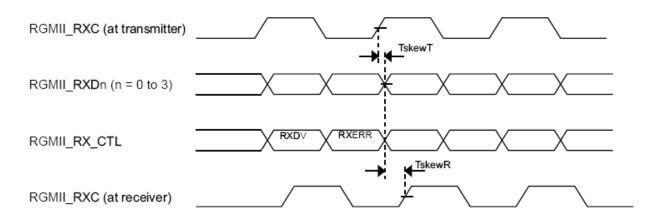

Figure 53. RGMII Receive Signal Timing Diagram Original

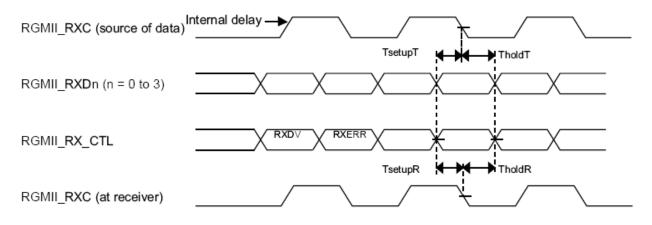

Figure 54. RGMII Receive Signal Timing Diagram with Internal Delay

## 4.11.6 Flexible Controller Area Network (FLEXCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* to see which pins expose Tx and Rx pins; these ports are named TXCAN and RXCAN, respectively.

# 4.11.7 HDMI Module Timing Parameters

## 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

| i.MX 6Solo/6DualLite  |                             | LCD           |               |               |                                                 |                                  |                        |                                              |

|-----------------------|-----------------------------|---------------|---------------|---------------|-------------------------------------------------|----------------------------------|------------------------|----------------------------------------------|

|                       | RGB,                        | R             | GB/TV S       | Signal A      | llocation                                       | (Examp                           | ole)                   | Comment <sup>1</sup>                         |

| Port Name<br>(x=0, 1) | Signal<br>Name<br>(General) | 16-bit<br>RGB | 18-bit<br>RGB | 24 Bit<br>RGB | 8-bit<br>YCrCb <sup>2</sup>                     | 16-bit<br>YCrCb                  | 20-bit<br>YCrCb        |                                              |

| DISPx_DAT22           | DAT[22]                     | —             | _             | R[6]          | _                                               | —                                | —                      | —                                            |

| DISPx_DAT23           | DAT[23]                     |               | _             | R[7]          | _                                               | —                                | —                      | —                                            |

| DIx_DISP_CLK          |                             |               |               | PixCLK        |                                                 |                                  |                        | —                                            |

| DIx_PIN1              |                             | _             |               |               |                                                 | May be required for anti-tearing |                        |                                              |

| DIx_PIN2              |                             | HSYNC         |               |               |                                                 |                                  |                        |                                              |

| DIx_PIN3              |                             | VSYNC         |               |               | VSYNC out                                       |                                  |                        |                                              |

| DIx_PIN4              |                             | —             |               |               | Additional frame/row synchronous                |                                  |                        |                                              |

| DIx_PIN5              |                             |               |               |               |                                                 | signals with programmable timin  |                        |                                              |

| DIx_PIN6              |                             | _             |               |               |                                                 |                                  |                        |                                              |

| DIx_PIN7              |                             | _             |               |               |                                                 |                                  |                        |                                              |

| DIx_PIN8              |                             |               |               |               |                                                 |                                  |                        |                                              |

| Dlx_D0_CS             |                             | _             |               |               | —                                               |                                  |                        |                                              |

| DIx_D1_CS             |                             | _             |               |               | Alternate mode of PWM contrast or brightness co |                                  |                        |                                              |

| DIx_PIN11             |                             |               |               |               |                                                 | —                                |                        |                                              |

| DIx_PIN12             |                             |               |               |               |                                                 |                                  |                        |                                              |

| DIx_PIN13             | PIN13                       |               |               |               |                                                 |                                  | Register select signal |                                              |

| DIx_PIN14             | _PIN14 —                    |               | _             |               |                                                 | Optional RS2                     |                        |                                              |

| DIx_PIN15             |                             |               | [             | DRDY/D        | V                                               |                                  |                        | Data validation/blank, data enable           |

| DIx_PIN16             |                             |               |               | _             |                                                 |                                  |                        | Additional data synchronous                  |

| DIx_PIN17             |                             |               |               | Q             |                                                 |                                  |                        | signals with programmable<br>features/timing |

#### Table 71. Video Signal Cross-Reference (continued)

<sup>1</sup> Signal mapping (both data and control/synchronization) is flexible. The table provides examples.

<sup>2</sup> This mode works in compliance with recommendation ITU-R BT.656. The timing reference signals (frame start, frame end, line start, and line end) are embedded in the 8-bit data bus. Only video data is supported, transmission of non-video related data during blanking intervals is not supported.

| V <sub>LEAK</sub>        | Input leakage current                                                            | VGNDSH(min) = VI =<br>VGNDSH(max) +<br>VOH(absmax)<br>Lane module in LP<br>Receive Mode | -10 | _   | 10   | mA |

|--------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|------|----|

| V <sub>GNDSH</sub>       | Ground Shift                                                                     |                                                                                         | -50 | —   | 50   | mV |

| V <sub>OH(absmax)</sub>  | Maximum transient output voltage level                                           |                                                                                         | _   | _   | 1.45 | V  |

| t <sub>voh(absmax)</sub> | Maximum transient time above VOH(absmax)                                         |                                                                                         | —   | —   | 20   | ns |

|                          | HS Li                                                                            | ne Drivers DC Specificatio                                                              | ns  |     |      |    |

| IV <sub>OD</sub> I       | HS Transmit Differential output voltage magnitude                                | 80 Ω<= RL< = 125 Ω                                                                      | 140 | 200 | 270  | mV |

| $\Delta  V_{OD} $        | Change in Differential<br>output voltage magnitude<br>between logic states       | 80 Ω<= RL< = 125 Ω                                                                      |     |     | 10   | mV |

| V <sub>CMTX</sub>        | Steady-state<br>common-mode output<br>voltage.                                   | 80 Ω<= RL< = 125 Ω                                                                      | 150 | 200 | 250  | mV |

| ∆V <sub>CMTX</sub> (1,0) | Changes in steady-state<br>common-mode output<br>voltage between logic<br>states | 80 Ω<= RL< = 125 Ω                                                                      |     |     | 5    | mV |

| V <sub>OHHS</sub>        | HS output high voltage                                                           | 80 Ω<= RL< = 125 Ω                                                                      |     |     | 360  | mV |

| Z <sub>OS</sub>          | Single-ended output impedance.                                                   |                                                                                         | 40  | 50  | 62.5 | Ω  |

| ΔZ <sub>OS</sub>         | Single-ended output impedance mismatch.                                          |                                                                                         |     |     | 10   | %  |

|                          | LP Li                                                                            | ne Drivers DC Specificatio                                                              | ns  |     |      |    |

| V <sub>OL</sub>          | Output low-level SE voltage                                                      |                                                                                         | -50 |     | 50   | mV |

| V <sub>OH</sub>          | Output high-level SE voltage                                                     |                                                                                         | 1.1 | 1.2 | 1.3  | V  |

| Z <sub>OLP</sub>         | Single-ended output impedance.                                                   |                                                                                         | 110 |     |      | Ω  |

| ΔZ <sub>OLP(01-10)</sub> | Single-ended output<br>impedance mismatch<br>driving opposite level              |                                                                                         |     |     | 20   | %  |

| ΔZ <sub>OLP(0-11)</sub>  | Single-ended output<br>impedance mismatch<br>driving same level                  |                                                                                         |     |     | 5    | %  |

|                          | HS Lin                                                                           | e Receiver DC Specification                                                             | ons |     |      |    |

| V <sub>IDTH</sub>        | Differential input high voltage threshold                                        |                                                                                         |     |     | 70   | mV |

| Table 75. Electrical and Timing In | nformation (continued) |

|------------------------------------|------------------------|

|------------------------------------|------------------------|

## 4.11.12.7 Forward High-Speed Data Transmission Timing

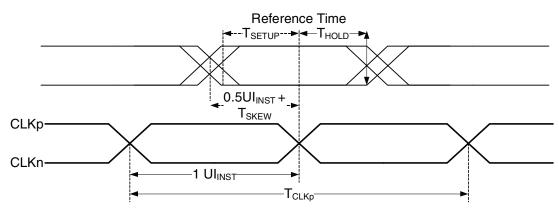

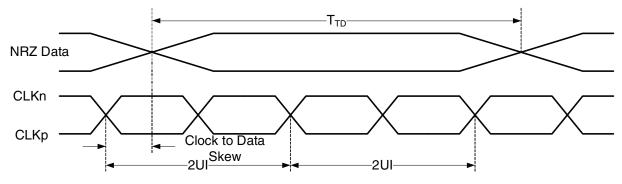

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 75:

Figure 75. Data to Clock Timing Definitions

### 4.11.12.8 Reverse High-Speed Data Transmission Timing

Figure 76. Reverse High-Speed Data Transmission Timing at Slave Side

### 4.11.12.9 Low-Power Receiver Timing

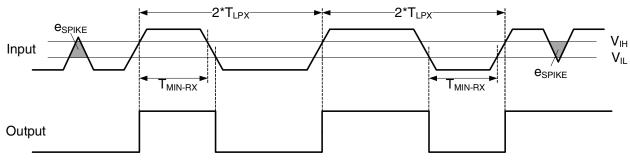

Figure 77. Input Glitch Rejection of Low-Power Receivers

# 4.11.13 HSI Host Controller Timing Parameters

This section describes the timing parameters of the HSI Host Controller which are compliant with High-speed Synchronous Serial Interface (HSI) Physical Layer specification version1.01.

## 4.11.13.1 Synchronous Data Flow

## 4.11.13.2 Pipelined Data Flow

## 4.11.13.3 Receiver Real-Time Data Flow

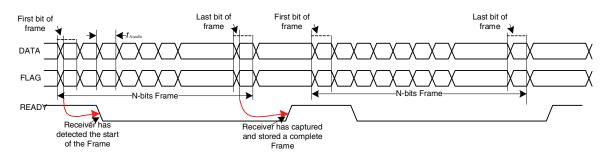

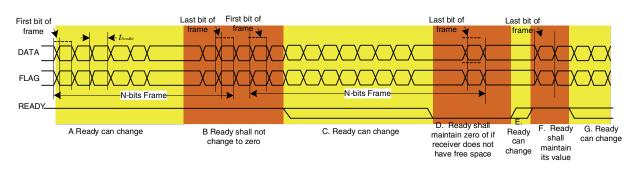

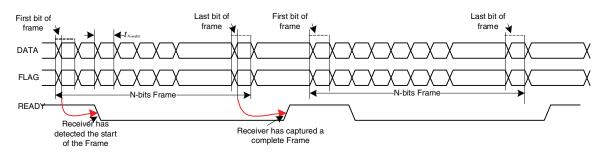

Figure 80. Receiver Real-Time Data Flow READY Signal Timing

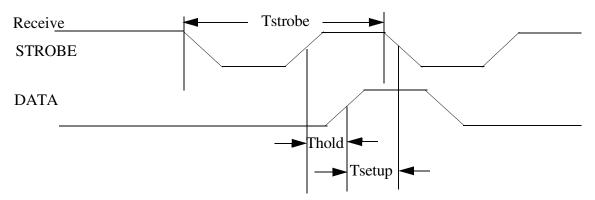

## 4.11.21.2 Receive Timing

Figure 104. USB HSIC Receive Waveform

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 4.11.22 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

#### Package Information and Contact Assignments

|              |      |             |              | Out of Reset Condition <sup>2</sup> |                  |                      |                          |  |

|--------------|------|-------------|--------------|-------------------------------------|------------------|----------------------|--------------------------|--|

| Ball Name    | Ball | Power Group | Ball<br>Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Outpu<br>t | Value                    |  |

| EIM_EB1      | K23  | NVCC_EIM    | GPIO         | ALT0                                | weim.WEIM_EB[1]  | Output               | High                     |  |

| EIM_EB2      | E22  | NVCC_EIM    | GPIO         | ALT5                                | gpio2.GPIO[30]   | Input                | 100 kΩ pull-up           |  |

| EIM_EB3      | F23  | NVCC_EIM    | GPIO         | ALT5                                | gpio2.GPIO[31]   | Input                | 100 kΩ pull-up           |  |

| EIM_LBA      | K22  | NVCC_EIM    | GPIO         | ALT0                                | weim.WEIM_LBA    | Output               | High                     |  |

| EIM_OE       | J24  | NVCC_EIM    | GPIO         | ALT0                                | weim.WEIM_OE     | Output               | High                     |  |

| EIM_RW       | K20  | NVCC_EIM    | GPIO         | ALT0                                | weim.WEIM_RW     | Output               | High                     |  |

| EIM_WAIT     | M25  | NVCC_EIM    | GPIO         | ALT0                                | weim.WEIM_WAIT   | Input                | 100 kΩ pull-up           |  |

| ENET_CRS_DV  | U21  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[25]   | Input                | 100 kΩ pull-up           |  |

| ENET_MDC     | V20  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[31]   | Input                | 100 kΩ pull-up           |  |

| ENET_MDIO    | V23  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[22]   | Input                | 100 kΩ pull-up           |  |

| ENET_REF_CLK | V22  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[23]   | Input                | 100 kΩ pull-up           |  |

| ENET_RX_ER   | W23  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[24]   | Input                | 100 kΩ pull-up           |  |

| ENET_RXD0    | W21  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[27]   | Input                | 100 kΩ pull-up           |  |

| ENET_RXD1    | W22  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[26]   | Input                | 100 kΩ pull-up           |  |

| ENET_TX_EN   | V21  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[28]   | Input                | 100 kΩ pull-up           |  |

| ENET_TXD0    | U20  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[30]   | Input                | 100 kΩ pull-up           |  |

| ENET_TXD1    | W20  | NVCC_ENET   | GPIO         | ALT5                                | gpio1.GPIO[29]   | Input                | 100 kΩ pull-up           |  |

| GPIO_0       | T5   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[0]    | Input                | 100 k $\Omega$ pull-down |  |

| GPIO_1       | T4   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[1]    | Input                | 100 kΩ pull-up           |  |

| GPIO_16      | R2   | NVCC_GPIO   | GPIO         | ALT5                                | gpio7.GPIO[11]   | Input                | 100 kΩ pull-up           |  |

| GPIO_17      | R1   | NVCC_GPIO   | GPIO         | ALT5                                | gpio7.GPIO[12]   | Input                | 100 kΩ pull-up           |  |

| GPIO_18      | P6   | NVCC_GPIO   | GPIO         | ALT5                                | gpio7.GPIO[13]   | Input                | 100 kΩ pull-up           |  |

| GPIO_19      | P5   | NVCC_GPIO   | GPIO         | ALT5                                | gpio4.GPIO[5]    | Input                | 100 kΩ pull-up           |  |

| GPIO_2       | T1   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[2]    | Input                | 100 kΩ pull-up           |  |

| GPIO_3       | R7   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[3]    | Input                | 100 kΩ pull-up           |  |

| GPIO_4       | R6   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[4]    | Input                | 100 kΩ pull-up           |  |

| GPIO_5       | R4   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[5]    | Input                | 100 kΩ pull-up           |  |

| GPIO_6       | ТЗ   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[6]    | Input                | 100 kΩ pull-up           |  |

| GPIO_7       | R3   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[7]    | Input                | 100 kΩ pull-up           |  |

| GPIO_8       | R5   | NVCC_GPIO   | GPIO         | ALT5                                | gpio1.GPIO[8]    | Input                | 100 kΩ pull-up           |  |

|              |      | I           | 1            |                                     | I                |                      | I                        |  |

Table 101. 21 x 21 mm Functional Contact Assignments<sup>1</sup> (continued)

| ~           | 8           | >            | Э           | F           | æ           | ٩            | z            |

|-------------|-------------|--------------|-------------|-------------|-------------|--------------|--------------|

| LVDS1_TX0_N | LVDS0_TX3_P | LVDS0_TX2_P  | LVDS0_TX0_P | GPIO_2      | GPI0_17     | CSI0_PIXCLK  | CSI0_DAT4    |

| LVDS1_TX0_P | LVDS0_TX3_N | LVDS0_TX2_N  | LVDS0_TX0_N | GPIO_9      | GPIO_16     | CSI0_DAT5    | CSI0_VSYNC   |

| LVDS1_CLK_N | GND         | LVDS0_CLK_P  | LVDS0_TX1_P | GPIO_6      | GPIO_7      | CSI0_DATA_EN | CSI0_DAT7    |

| LVDS1_CLK_P | KEY_ROW2    | LVDS0_CLK_N  | LVDS0_TX1_N | GPI0_1      | GPIO_5      | CSI0_MCLK    | CSI0_DAT6    |

| GND         | KEY_COL0    | KEY_ROW4     | KEY_COL3    | GPIO_0      | GPIO_8      | GPIO_19      | CSI0_DAT9    |

| DRAM_RESET  | KEY_COL2    | KEY_ROW0     | KEY_ROW1    | KEY_COL4    | GPIO_4      | GPIO_18      | CSI0_DAT8    |

| DRAM_D20    | GND         | NVCC_LVDS2P5 | KEY_COL1    | KEY_ROW3    | GPIO_3      | NVCC_GPIO    | NVCC_CSI     |

| DRAM_D21    | GND         | GND          | GND         | GND         | GND         | GND          | GND          |

| DRAM_D19    | GND         | NVCC_DRAM    | VDDARM_IN   | VDDARM_IN   | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_D25    | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDSOC_CAP  | GND          | GND          |

| DRAM_SDCKE0 | GND         | NVCC_DRAM    | GND         | GND         | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A15    | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | NC           |

| DRAM_A7     | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_CAP  | VDDARM_CAP   | VDDARM_CAP   |

| DRAM_A3     | DRAM_A4     | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  | VDDARM_IN   | VDDARM_IN    | VDDARM_IN    |

| DRAM_SDBA1  | GND         | NVCC_DRAM    | GND         | GND         | GND         | GND          | GND          |

| DRAM_CS0    | GND         | NVCC_DRAM    | VDDSOC_IN   | VDDSOC_IN   |             | VDDSOC_IN    | VDDSOC_IN    |

| DRAM_D36    | GND         | NVCC_DRAM    | GND         | GND         | GND         | VDDPU_CAP    | VDDPU_CAP    |

| DRAM_D37    | GND         | NVCC_DRAM    | NVCC_DRAM   | NVCC_DRAM   | NVCC_DRAM   | GND          | GND          |

| DRAM_D40    | GND         | GND          | GND         | GND         | NVCC_ENET   | NVCC_LCD     | DI0_DISP_CLK |

| DRAM_D44    | ENET_TXD1   | ENET_MDC     | ENET_TXD0   | DISP0_DAT21 | DISP0_DAT13 | DISP0_DAT4   | DI0_PIN3     |

| DRAM_DQM7   | ENET_RXD0   | ENET_TX_EN   | ENET_CRS_DV | DISP0_DAT16 | DISP0_DAT10 | DISP0_DAT3   | DI0_PIN15    |

| DRAM_D59    | ENET_RXD1   | ENET_REF_CLK | DISP0_DAT20 | DISP0_DAT15 | DISP0_DAT8  | DISP0_DAT1   | EIM_BCLK     |

| DRAM_D62    | ENET_RX_ER  | ENET_MDIO    | DISP0_DAT19 | DISP0_DAT11 | DISP0_DAT6  | DISP0_DAT2   | EIM_DA14     |

| GND         | DISP0_DAT23 | DISP0_DAT22  | DISP0_DAT17 | DISP0_DAT12 | DISP0_DAT7  | DISP0_DAT0   | EIM_DA15     |

| DRAM_D58    | DRAM_D63    | DISP0_DAT18  | DISP0_DAT14 | DISP0_DAT9  | DISP0_DAT5  | DI0_PIN4     | DI0_PIN2     |

| ٨           | ×           | >            | D           | F           | æ           | ٩            | z            |

### Package Information and Contact Assignments

| Table 103. 21 x 21 mm | , 0.8 mm Pitch | Ball Map | (continued) |

|-----------------------|----------------|----------|-------------|

|-----------------------|----------------|----------|-------------|