#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                     | Not For New Designs                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u1avm08abr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Integrated power management—The processors integrate linear regulators and internally generate voltage levels for different domains. This significantly simplifies system power management structure.

# **1.1 Ordering Information**

Table 1 shows the orderable part numbers covered by this datasheet. Table 1 does not include all possible orderable part numbers. The latest part numbers are available on the web page freescale.com/imx6series. If the desired part number is not listed in Table 1, or there may be any questions about available parts, see the web page freescale.com/imx6series or contact a Freescale representative.

| Part Number     | Solo/DualLite<br>CPU | Options                    | Speed<br>Grade | Temperature<br>Grade | Package                                |

|-----------------|----------------------|----------------------------|----------------|----------------------|----------------------------------------|

| MCIMX6U6AVM08AB | i.MX 6DualLite       | With VPU, GPU, no EPD      | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6U4AVM08AB | i.MX 6DualLite       | With GPU, no VPU, no EPD   | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6U1AVM08AB | i.MX 6DualLite       | no GPU, no VPU, no display | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S6AVM08AB | i.MX 6Solo           | With VPU, GPU, no EPD      | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S4AVM08AB | i.MX 6Solo           | With GPU, no VPU, no EPD   | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| MCIMX6S1AVM08AB | i.MX 6Solo           | no GPU, no VPU, no display | 800 MHz        | Automotive           | 21 mm x 21 mm, 0.8 mm<br>pitch, MAPBGA |

| Table 1 | . Orderable | Part | Numbers    |

|---------|-------------|------|------------|

|         | oraorabio   |      | 1101110010 |

Figure 1 describe the part number nomenclature so that the users can identify the characteristics of the specific part number they have (for example, cores, frequency, temperature grade, fuse options, and silicon revision). The primary characteristic which describes which datasheet applies to a specific part is the temperature grade (junction) field.

- The i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors datasheet (IMX6SDLAEC) covers parts listed with an "A (Automotive temp)"

- The i.MX 6Solo/6DualLite Applications Processors for Consumer Products datasheet (IMX6SDLCEC) covers parts listed with a "D (Consumer temp)" or "E (Extended Consumer temp)"

- The i.MX 6Solo/6DualLite Applications Processors for Industrial Products datasheet (IMX6SDLIEC) covers parts listed with "C (Industrial temp)"

Ensure to have the proper datasheet for specific part by verifying the temperature grade (junction) field and matching it to the proper datasheet. If there will be any questions, visit see the web page freescale.com/imx6series or contact a Freescale representative for details.

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (MOST25, MOST50, MOST150) with the option of DTCP cipher accelerator

The i.MX 6Solo/6DualLite processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use SW State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Solo/6DualLite processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Solo/6DualLite processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H

- GPU3Dv5—3D Graphics Processing Unit (OpenGL ES 2.0) version 5

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing cryptographic and hash engines, 16 KB secure RAM, and True and Pseudo Random Number Generator (NIST certified).

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

- A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

### NOTE

The actual feature set depends on the part numbers as described in Table 1, "Orderable Part Numbers," on page 3. Functions, such as video hardware acceleration, and 2D and 3D hardware graphics acceleration may not be enabled for specific part numbers.

#### **Modules List**

| Block Mnemonic                           | Block Name                                                                          | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-2<br>uSDHC-3<br>uSDHC-4 | SD/MMC and SDXC<br>Enhanced Multi-Media<br>Card / Secure Digital Host<br>Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6Solo/6DualLite specific SoC characteristics:<br/>All four MMC/SD/SDIO controller IPs are identical and<br/>are based on the uSDHC IP. They are:</li> <li>Fully compliant with MMC command/response sets<br/>and Physical Layer as defined in the Multimedia Card<br/>System Specification, v4.2/4.3/4.4 including<br/>high-capacity (size &gt; 2 GB) cards HC MMC.</li> <li>Fully compliant with SD command/response sets and<br/>Physical Layer as defined in the SD Memory Card<br/>Specifications, v3.0 including high-capacity SDHC<br/>cards up to 32 GB.</li> <li>Fully compliant with SDIO command/response sets<br/>and interrupt/read-wait mode as defined in the SDIO<br/>Card Specification, Part E1, v3.0</li> <li>All four ports support:</li> <li>1-bit or 4-bit transfer mode specifications for SD and<br/>SDIO cards up to UHS-I SDR104 mode (104 MB/s<br/>max)</li> <li>1-bit, 4-bit, or 8-bit transfer mode specifications for<br/>MMC cards up to 52 MHz in both SDR and DDR<br/>modes (104 MB/s max)</li> <li>However, the SoC level integration and I/O muxing logic<br/>restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve<br/>as external slots or interfaces to on-board SDIO<br/>devices. These ports are equipped with "Card<br/>detection" and "Write Protection" pads and do not<br/>support hardware reset.</li> <li>Instances #3 and #4 are primarily intended to serve<br/>interfaces to embedded MMC memory or interfaces<br/>to on-board SDIO devices. These ports do not have<br/>"Card detection" and "Write Protection" pads and do<br/>support hardware reset.</li> <li>All ports can work with 1.8 V and 3.3 V cards. There<br/>are two completely independent I/O power domains<br/>for Ports #1 and #2 in four bit configuration (SD<br/>interface). Port #3 is placed in his own independent<br/>power domain and port #4 shares power domain with<br/>some other interfaces.</li> </ul> |

| FlexCAN-1<br>FlexCAN-2                   | Flexible Controller Area<br>Network                                                 | Connectivity<br>Peripherals | The CAN protocol was primarily, but not only, designed<br>to be used as a vehicle serial data bus, meeting the<br>specific requirements of this field: real-time processing,<br>reliable operation in the Electromagnetic interference<br>(EMI) environment of a vehicle, cost-effectiveness and<br>required bandwidth. The FlexCAN module is a full<br>implementation of the CAN protocol specification,<br>Version 2.0 B, which supports both standard and<br>extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block Mnemonic                                                                     | Block Name                            | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 512x8 Fuse Box                                                                     | Electrical Fuse Array                 | Security                      | Electrical Fuse Array. Enables to setup Boot Modes,<br>Security Levels, Security Keys, and many other system<br>parameters.<br>The i.MX 6Solo/6DualLite processors consist of<br>512x8-bit fuse fox accessible through OCOTP_CTRL<br>interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7                 | General Purpose I/O<br>Modules        | System Control<br>Peripherals | Used for general purpose input/output to external ICs.<br>Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPMI                                                                               | General Media Interface               | Connectivity<br>Peripherals   | The GPMI module supports up to 8x NAND devices.<br>40-bit ECC encryption/decryption for NAND Flash<br>controller (GPMI2). The GPMI supports separate DMA<br>channels per NAND device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPT                                                                                | General Purpose Timer                 | Timer Peripherals             | Each GPT is a 32-bit "free-running" or "set and forget"<br>mode timer with programmable prescaler and compare<br>and capture register. A timer counter value can be<br>captured using an external event and can be configured<br>to trigger a capture event on either the leading or trailing<br>edges of an input pulse. When the timer is configured to<br>operate in "set and forget" mode, it is capable of<br>providing precise interrupts at regular intervals with<br>minimal processor intervention. The counter has output<br>compare logic to provide the status and interrupt at<br>comparison. This timer can be configured to run either<br>on an external clock or on an internal clock. |

| GPU3Dv5                                                                            | Graphics Processing<br>Unit, ver.5    | Multimedia<br>Peripherals     | The GPU3Dv5 provides hardware acceleration for 3D graphics algorithms with sufficient processor power to run desktop quality interactive graphics applications on displays up to HD1080 resolution. The GPU3D provides OpenGL ES 2.0, including extensions, OpenGL ES 1.1, and OpenVG 1.1                                                                                                                                                                                                                                                                                                                                                                                                              |

| GPU2Dv2                                                                            | Graphics Processing<br>Unit-2D, ver 2 | Multimedia<br>Peripherals     | The GPU2Dv2 provides hardware acceleration for 2D graphics algorithms, such as Bit BLT, stretch BLT, and many other 2D functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HDMI Tx                                                                            | HDMI Tx i/f                           | Multimedia<br>Peripherals     | The HDMI module provides HDMI standard i/f port to an HDMI 1.4 compliant display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HSI                                                                                | MIPI HSI i/f                          | Connectivity<br>Peripherals   | The MIPI HSI provides a standard MIPI interface to the applications processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <sup>2</sup> C-1<br>  <sup>2</sup> C-2<br>  <sup>2</sup> C-3<br>  <sup>2</sup> C-4 | I <sup>2</sup> C Interface            | Connectivity<br>Peripherals   | I <sup>2</sup> C provide serial interface for external devices. Data rates of up to 400 kbps are supported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Modules List**

| Block Mnemonic | Block Name                       | Subsystem                                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|----------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOMUXC         | IOMUX Control                    | System Control<br>Peripherals               | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IPUv3H         | Image Processing Unit,<br>ver.3H | Multimedia<br>Peripherals                   | <ul> <li>IPUv3H enables connectivity to displays and video sources, relevant processing and synchronization and control capabilities, allowing autonomous operation. The IPUv3H supports concurrent output to two display ports and concurrent input from two camera ports, through the following interfaces: <ul> <li>Parallel Interfaces for both display and camera</li> <li>Single/dual channel LVDS display interface</li> <li>HDMI transmitter</li> <li>MIPI/DSI transmitter</li> <li>MIPI/CSI-2 receiver</li> </ul> </li> <li>The processing includes: <ul> <li>Image conversions: resizing, rotation, inversion, and color space conversion</li> <li>A high-quality de-interlacing filter</li> <li>Video/graphics combining</li> <li>Image enhancement: color adjustment and gamut mapping, gamma correction, and contrast enhancement</li> <li>Support for display backlight reduction</li> </ul> </li> </ul> |

| КРР            | Key Pad Port                     | Connectivity<br>Peripherals                 | <ul> <li>KPP Supports 8x8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LDB            | LVDS Display Bridge              | Connectivity<br>Peripherals                 | <ul> <li>LVDS Display Bridge is used to connect the IPU (Image<br/>Processing Unit) to External LVDS Display Interface.</li> <li>LDB supports two channels; each channel has following<br/>signals: <ul> <li>One clock pair</li> <li>Four data pairs</li> <li>Each signal pair contains LVDS special differential pad<br/>(PadP, PadM).</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MLB150         | MediaLB                          | Connectivity /<br>Multimedia<br>Peripherals | The MLB interface module provides a link to a MOST <sup>®</sup> data network, using the standardized MediaLB protocol (up to 6144 fs).<br>The module is backward compatible to MLB-50.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MMDC           | Multi-Mode DDR<br>Controller     | Connectivity<br>Peripherals                 | <ul> <li>DDR Controller has the following features:</li> <li>Supports 16/32-bit DDR3-800 (LV) or LPDDR2-800 in i.MX 6Solo</li> <li>Supports 16/32/64-bit DDR3-800 (LV) or LPDDR2-800 in i.MX 6DualLite</li> <li>Supports 2x32 LPDDR2-800 in i.MX 6DualLite</li> <li>Supports up to 4 GByte DDR memory space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

# 4.1.7 USB PHY Current Consumption

## 4.1.7.1 Power Down Mode

In power down mode, everything is powered down, including the VBUS valid detectors in typical condition. Table 14 shows the USB interface current consumption in power down mode..

### Table 14. USB PHY Current Consumption in Power Down Mode

|         | VDDUSB_CAP (3.0 V) | VDDHIGH_CAP (2.5 V) | NVCC_PLL_OUT (1.1 V) |

|---------|--------------------|---------------------|----------------------|

| Current | 5.1 μΑ             | 1.7 μΑ              | <0.5 µA              |

### NOTE

The currents on the VDDHIGH\_CAP and VDDUSB\_CAP were identified to be the voltage divider circuits in the USB-specific level shifters.

## 4.1.8 PCIe 2.0 Power Consumption

Table 15 provides PCIe PHY currents under certain Tx operating modes.

| Mode                        | Test Conditions | Supply            | Max Current | Unit |

|-----------------------------|-----------------|-------------------|-------------|------|

| PO: Normal Operation        | 5G Operations   | PCIE_VP (1.1 V)   | 40          | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 21          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 27          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 20          |      |

|                             |                 | PCIE_VPH (2.5 V)  | 20          |      |

| POs: Low Recovery Time      | 5G Operations   | PCIE_VP (1.1 V)   | 30          | mA   |

| Latency, Power Saving State |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 18          |      |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 20          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 18          |      |

| P1: Longer Reocvery Time    |                 | PCIE_VP (1.1 V)   | 12          | mA   |

| Latency, Lower Power State  |                 | PCIE_VPTX (1.1 V) | 2.4         |      |

|                             |                 | PCIE_VPH (2.5 V)  | 12          |      |

| Power Down                  |                 | PCIE_VP (1.1 V)   | 1.3         | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 0.18        |      |

|                             |                 | PCIE_VPH (2.5 V)  | 0.36        |      |

Table 15. PCIe PHY Current Drain

# 4.5 On-Chip Oscillators

## 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

## 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDDHIGH\_IN such as the oscillator consumes power from VDDHIGH\_IN when that supply is available and transitions to the back up battery when VDDHIGH\_IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 K will automatically switch to a crude internal ring oscillator. The frequency range of this block is approximately 10–45 kHz. It highly depends on the process, voltage, and temperature.

The OSC32k runs from VDD\_SNVS\_CAP supply, which comes from the

VDDHIGH\_IN/VDD\_SNVS\_IN. The target battery is a ~3 V coin cell. Proper choice of coin cell type is necessary for chosen VDDHIGH\_IN range. Appropriate series resistor (Rs) must be used when connecting the coin cell. Rs depends on the charge current limit that depends on the chosen coin cell. For example, for Panasonic ML621:

- Average Discharge Voltage is 2.5 V

- Maximum Charge Current is 0.6 mA

For a charge voltage of 3.2 V, Rs = (3.2-2.5)/0.6 m = 1.17 k

|                        | Min | Тур        | Мах | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-----|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fosc                   |     | 32.768 KHz |     | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                                                                                                             |

| Current<br>consumption |     | 4 μΑ       |     | The 4 $\mu$ A is the consumption of the oscillator alone (OSC32k). Total supply consumption will depend on what the digital portion of the RTC consumes. The ring oscillator consumes 1 $\mu$ A when ring oscillator is inactive, 20 $\mu$ A when the ring oscillator is running. Another 1.5 $\mu$ A is drawn from vdd_rtc in the power_detect block. So, the total current is 6.5 $\mu$ A on vdd_rtc when the ring oscillator is not running. |

### Table 23. OSC32K Main Characteristics

- <sup>2</sup> To maintain a valid level, the transition edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, Vil or Vih. Monotonic input transition time is from 0.1 ns to 1 s.

- <sup>3</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled.

## 4.6.2 DDR I/O DC Parameters

The DDR I/O pads support LPDDR2 and DDR3/DDR3L operational modes.

### 4.6.2.1 LPDDR2 Mode I/O DC Parameters

The LPDDR2 interface mode fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009.

| Parameters                               | Symbol   | Test Conditions   | Min               | Max               | Unit |

|------------------------------------------|----------|-------------------|-------------------|-------------------|------|

| High-level output voltage                | VOH      | loh= -0.1mA       | 0.9*OVDD          |                   | V    |

| Low-level output voltage                 | VOL      | lol= 0.1mA        |                   | 0.1*OVDD          | V    |

| Input Reference Voltage                  | Vref     |                   | 0.49*OVDD         | 0.51*OVDD         | V    |

| DC High-Level input voltage              | Vih_DC   |                   | Vref+0.13         | OVDD              | V    |

| DC Low-Level input voltage               | Vil_DC   |                   | OVSS              | Vref-0.13         | V    |

| Differential Input Logic High            | Vih_diff |                   | 0.26              | Note <sup>2</sup> |      |

| Differential Input Logic Low             | Vil_diff |                   | Note <sup>3</sup> | -0.26             |      |

| Pull-up/Pull-down Impedance Mismatch     | Mmpupd   |                   | -15               | 15                | %    |

| 240 $\Omega$ unit calibration resolution | Rres     |                   |                   | 10                | Ω    |

| Keeper Circuit Resistance                | Rkeep    |                   | 110               | 175               | kΩ   |

| Input current (no pull-up/down)          | lin      | VI = 0, VI = OVDD | -2.5              | 2.5               | μA   |

|                                          |          |                   |                   |                   |      |

Table 25. LPDDR2 I/O DC Electrical Parameters<sup>1</sup>

<sup>1</sup> Note that the JEDEC LPDDR2 specification (JESD209\_2B) supersedes any specification in this document.

<sup>2</sup> The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as the limitations for overshoot and undershoot.

- 2. Calibration is done against 240  $\Omega$  external reference resistor.

- 3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

## 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

## 4.8.4 MLB I/O Differential Output Impedance

Table 38 shows MLB I/O differential output impedance of the i.MX 6Solo/6DualLite processors.

#### Table 38. MLB I/O Differential Output Impedance

| Parameter                     | Symbol | Test Conditions | Min   | Тур | Мах | Unit |

|-------------------------------|--------|-----------------|-------|-----|-----|------|

| Differential Output Impedance | Zo     |                 | 1.6 K |     | _   | Ω    |

## 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Solo/6DualLite processor.

## 4.9.1 Reset Timings Parameters

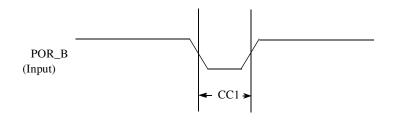

Figure 10 shows the reset timing and Table 39 lists the timing parameters.

Figure 10. Reset Timing Diagram

| Table 39. Reset | Timing | Parameters |

|-----------------|--------|------------|

|-----------------|--------|------------|

| ID  | Parameter                                                       | Min | Max | Unit               |

|-----|-----------------------------------------------------------------|-----|-----|--------------------|

| CC1 | Duration of POR_B to be qualified as valid (input slope = 5 ns) | 1   |     | RTC_XTALI<br>cycle |

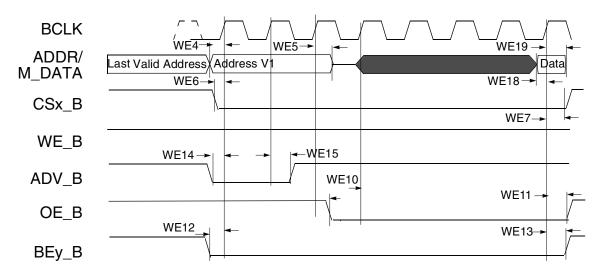

Figure 17. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

### 4.9.3.5 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22, and Table 44 help you determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for the EIM programming model.

Figure 35. Source Synchronous Mode Data Write Timing Diagram

| No. | Characteristics <sup>1,2</sup>                                      | Symbol | Expression <sup>2</sup> | Min         | Max          | Condition <sup>3</sup> | Unit |

|-----|---------------------------------------------------------------------|--------|-------------------------|-------------|--------------|------------------------|------|

| 81  | SCKT rising edge to FST out (wr) low <sup>5</sup>                   |        |                         | _           | 22.0<br>12.0 | x ck<br>i ck           | ns   |

| 82  | SCKT rising edge to FST out (wl) high                               | —      | —                       | _           | 19.0<br>9.0  | x ck<br>i ck           | ns   |

| 83  | SCKT rising edge to FST out (wl) low                                | —      | —                       | _           | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 84  | SCKT rising edge to data out enable from high impedance             | —      |                         | _           | 22.0<br>17.0 | x ck<br>i ck           | ns   |

| 86  | SCKT rising edge to data out valid                                  | —      |                         | _           | 18.0<br>13.0 | x ck<br>i ck           | ns   |

| 87  | SCKT rising edge to data out high impedance <sup>67</sup>           | —      |                         | _           | 21.0<br>16.0 | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT falling edge <sup>5</sup> | —      | —                       | 2.0<br>18.0 | —            | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT falling edge                  | —      |                         | 2.0<br>18.0 | _            | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT falling edge                         |        |                         | 4.0<br>5.0  |              | x ck<br>i ck           | ns   |

| 95  | HCKR/HCKT clock cycle                                               | —      | 2 x T <sub>C</sub>      | 15          |              | —                      | ns   |

| 96  | HCKT input rising edge to SCKT output                               | —      | —                       | —           | 18.0         | —                      | ns   |

| 97  | HCKR input rising edge to SCKR output                               | —      | —                       | _           | 18.0         | —                      | ns   |

#### Table 56. Enhanced Serial Audio Interface (ESAI) Timing (continued)

<sup>1</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that SCKT and SCKR are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that SCKT and SCKR are the same clock)

- <sup>2</sup> bl = bit length

- wl = word length

wr = word length relative

- <sup>3</sup> SCKT(SCKT pin) = transmit clock SCKR(SCKR pin) = receive clock FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync HCKT(HCKT pin) = transmit high frequency clock HCKR(HCKR pin) = receive high frequency clock

- <sup>4</sup> For the internal clock, the external clock cycle is defined by lcyc and the ESAI control register.

- <sup>5</sup> The word-relative frame sync signal waveform relative to the clock operates in the same manner as the bit-length frame sync signal waveform, but it spreads from one serial clock before the first bit clock (like the bit length frame sync signal), until the second-to-last bit clock of the first word in the frame.

- <sup>6</sup> Periodically sampled and not 100% tested.

| ID                                                   | Parameter                          | Symbols          | Min | Max | Unit |  |  |

|------------------------------------------------------|------------------------------------|------------------|-----|-----|------|--|--|

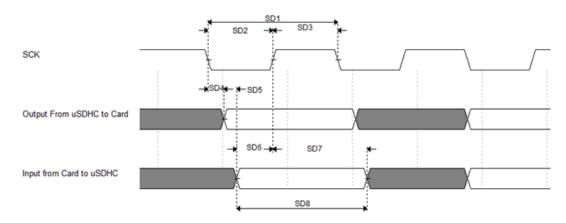

| uSDHC Input/Card Outputs CMD, DAT (Reference to CLK) |                                    |                  |     |     |      |  |  |

| SD7                                                  | uSDHC Input Setup Time             | t <sub>ISU</sub> | 2.5 | —   | ns   |  |  |

| SD8                                                  | uSDHC Input Hold Time <sup>4</sup> | t <sub>IH</sub>  | 5.6 | —   | ns   |  |  |

#### Table 57. SD/eMMC4.3 Interface Timing Specification (continued)

<sup>1</sup> In low speed mode, card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

<sup>2</sup> In normal (full) speed mode for SD/SDIO card, clock frequency can be any value between 0–25 MHz. In high-speed mode, clock frequency can be any value between 0–50 MHz.

<sup>3</sup> In normal (full) speed mode for MMC card, clock frequency can be any value between 0-20 MHz. In high-speed mode, clock frequency can be any value between 0-52 MHz.

<sup>4</sup>To satisfy hold timing, the delay difference between clock input and cmd/data input must not exceed 2 ns.

## 4.11.4.2 eMMC4.4 (Dual Data Rate) AC Timing

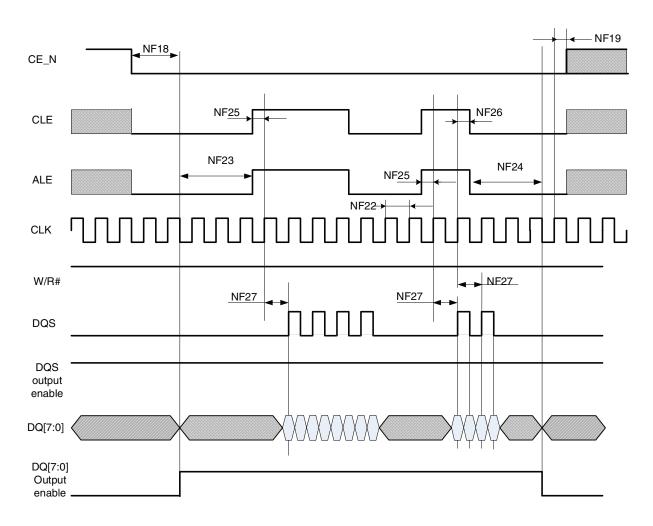

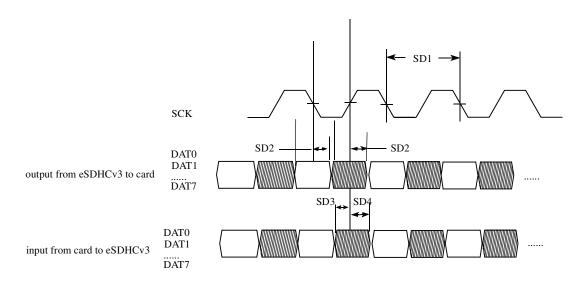

Figure 45 depicts the timing of eMMC4.4. Table 58 lists the eMMC4.4 timing characteristics. Be aware that only DATA is sampled on both edges of the clock (not applicable to CMD).

#### Figure 45. eMMC4.4 Timing

Table 58. eMMC4.4 Interface Timing Specification

| ID               | Parameter                                              | Symbols         | Min | Max | Unit |  |  |

|------------------|--------------------------------------------------------|-----------------|-----|-----|------|--|--|

| Card Input Clock |                                                        |                 |     |     |      |  |  |

| SD1              | Clock Frequency (EMMC4.4 DDR)                          | f <sub>PP</sub> | 0   | 52  | MHz  |  |  |

| SD1              | Clock Frequency (SD3.0 DDR)                            | f <sub>PP</sub> | 0   | 50  | MHz  |  |  |

|                  | uSDHC Output / Card Inputs CMD, DAT (Reference to CLK) |                 |     |     |      |  |  |

| SD2              | uSDHC Output Delay                                     | t <sub>OD</sub> | 2.5 | 7.1 | ns   |  |  |

| ID                                                     | Parameter Symbol       |                  | Min | Max | Unit |  |  |

|--------------------------------------------------------|------------------------|------------------|-----|-----|------|--|--|

| uSDHC Input / Card Outputs CMD, DAT (Reference to CLK) |                        |                  |     |     |      |  |  |

| SD3                                                    | uSDHC Input Setup Time | t <sub>ISU</sub> | 2.6 | _   | ns   |  |  |

| SD4                                                    | uSDHC Input Hold Time  | t <sub>IH</sub>  | 1.5 | _   | ns   |  |  |

#### Table 58. eMMC4.4 Interface Timing Specification (continued)

## 4.11.4.3 SDR50/SDR104 AC Timing

Figure 46 depicts the timing of SDR50/SDR104, and Table 59 lists the SDR50/SDR104 timing characteristics.

### Figure 46. SDR50/SDR104 Timing

### Table 59. SDR50/SDR104 Interface Timing Specification

| ID               | Parameter                                                     | Symbols          | Min                  | Мах                  | Unit |  |  |

|------------------|---------------------------------------------------------------|------------------|----------------------|----------------------|------|--|--|

| Card Input Clock |                                                               |                  |                      |                      |      |  |  |

| SD1              | Clock Frequency Period                                        | t <sub>CLK</sub> | 4.8                  | _                    | ns   |  |  |

| SD2              | Clock Low Time                                                | t <sub>CL</sub>  | 0.3*t <sub>CLK</sub> | 0.7*t <sub>CLK</sub> | ns   |  |  |

| SD2              | Clock High Time                                               | t <sub>CH</sub>  | 0.3*t <sub>CLK</sub> | 0.7*t <sub>CLK</sub> | ns   |  |  |

|                  | uSDHC Output/Card Inputs C                                    | CMD, DAT in SDF  | 850 (Reference       | e to CLK)            | ·    |  |  |

| SD4              | uSDHC Output Delay                                            | t <sub>OD</sub>  | -3                   | 1                    | ns   |  |  |

|                  | uSDHC Output/Card Inputs C                                    | MD, DAT in SDR   | 104 (Referenc        | e to CLK)            |      |  |  |

| SD5              | uSDHC Output Delay                                            | t <sub>OD</sub>  | -1.6                 | 1                    | ns   |  |  |

|                  | uSDHC Input/Card Outputs CMD, DAT in SDR50 (Reference to CLK) |                  |                      |                      |      |  |  |

| SD6              | uSDHC Input Setup Time                                        | t <sub>ISU</sub> | 2.5                  | —                    | ns   |  |  |

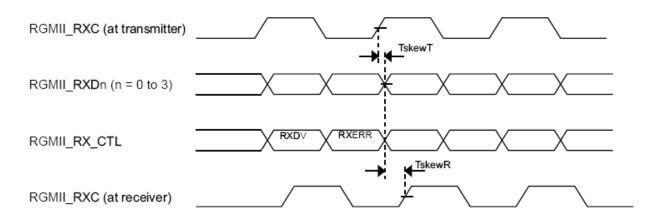

Figure 53. RGMII Receive Signal Timing Diagram Original

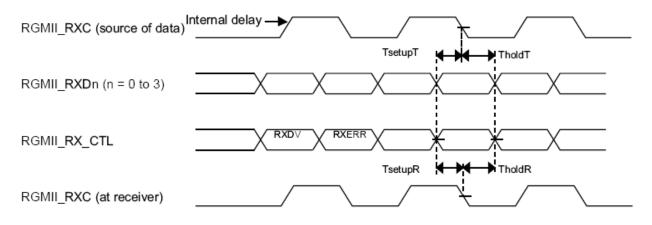

Figure 54. RGMII Receive Signal Timing Diagram with Internal Delay

## 4.11.6 Flexible Controller Area Network (FLEXCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* to see which pins expose Tx and Rx pins; these ports are named TXCAN and RXCAN, respectively.

# 4.11.7 HDMI Module Timing Parameters

## 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

| Symbol                                                            | Parameter                                                                                                                                                                                                                                                                                                                                                                 | Condition                                                                                                                                                                              | Min.                 | Тур.                | Max.                 | Unit |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|----------------------|------|

|                                                                   | I                                                                                                                                                                                                                                                                                                                                                                         | Operating conditions for HD                                                                                                                                                            | MI                   |                     | L L                  |      |

| avddtmds                                                          | Termination supply voltage                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | 3.15                 | 3.3                 | 3.45                 | V    |

| R <sub>T</sub>                                                    | Termination resistance                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                      | 45                   | 50                  | 55                   | Ω    |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                           | TMDS drivers DC specification                                                                                                                                                          | ons                  |                     |                      |      |

| $V_{OFF}$ Single-ended standby voltage RT = 50 Ω avddtmds ± 10 mV |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                        |                      |                     | mV                   |      |

| V <sub>SWING</sub>                                                | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                                                         | For measurement conditions<br>and definitions, see the first<br>two figures above.<br>Compliance point TP1 as<br>defined in the HDMI<br>specification, version 1.3a,<br>section 4.2.4. | 400                  | -                   | 600                  | mV   |

| V <sub>H</sub>                                                    | Single-ended output high<br>voltage                                                                                                                                                                                                                                                                                                                                       | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                                    | avo                  | ldtmds ± 10         | mV                   | mV   |

| For definition, see the second figure above                       | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                                                                                                                                                                                                                            | avddtmds<br>- 200 mV                                                                                                                                                                   | -                    | avddtmds<br>+ 10 mV | mV                   |      |

| VL                                                                | voltage                                                                                                                                                                                                                                                                                                                                                                   | If attached sink supports<br>TMDSCLK < or = 165 MHz                                                                                                                                    | avddtmds<br>- 600 mV | -                   | avddtmds<br>- 400mV  | mV   |

|                                                                   | For definition, see the second figure above                                                                                                                                                                                                                                                                                                                               | If attached sink supports<br>TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>- 700 mV | -                   | avddtmds<br>- 400 mV | mV   |

| R <sub>term</sub>                                                 | Differential source termination<br>load (inside HDMI 3D Tx PHY)<br>Although the HDMI 3D Tx<br>PHY includes differential<br>source termination, the<br>user-defined value is set for<br>each single line (for<br>illustration, see the third figure<br>above).<br><b>Note:</b> R <sub>TERM</sub> can also be<br>configured to be open and not<br>present on TMDS channels. | -                                                                                                                                                                                      | 50                   | -                   | 200                  | Ω    |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                           | Hot plug detect specificatio                                                                                                                                                           | ns                   |                     | . I                  |      |

| HPD <sup>VH</sup>                                                 | Hot plug detect high range                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | 2.0                  | -                   | 5.3                  | V    |

| VHPD<br>VL                                                        | Hot plug detect low range                                                                                                                                                                                                                                                                                                                                                 | -                                                                                                                                                                                      | 0                    | -                   | 0.8                  | V    |

| HPD                                                               | Hot plug detect input<br>impedance                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                      | 10                   | -                   | -                    | kΩ   |

| HPD                                                               | Hot plug detect time delay                                                                                                                                                                                                                                                                                                                                                | -                                                                                                                                                                                      | -                    | -                   | 100                  | μs   |

# 4.11.8 Switching Characteristics

Table 67 describes switching characteristics for the HDMI 3D Tx PHY. Figure 58 to Figure 62 illustrate various parameters specified in table.

## 4.11.19.4 SSI Receiver Timing with External Clock

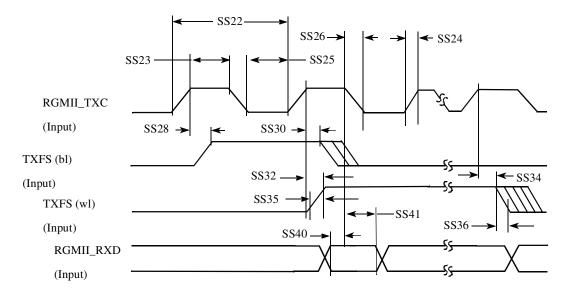

Figure 98 depicts the SSI receiver external clock timing and Table 90 lists the timing parameters for the receiver timing with the external clock.

#### Figure 98. SSI Receiver External Clock Timing Diagram

| ID   | Parameter                          | Min  | Max  | Unit |  |  |  |  |

|------|------------------------------------|------|------|------|--|--|--|--|

|      | External Clock Operation           |      |      |      |  |  |  |  |

| SS22 | (Tx/Rx) CK clock period            | 81.4 | —    | ns   |  |  |  |  |

| SS23 | (Tx/Rx) CK clock high period       | 36   | —    | ns   |  |  |  |  |

| SS24 | (Tx/Rx) CK clock rise time         | —    | 6.0  | ns   |  |  |  |  |

| SS25 | (Tx/Rx) CK clock low period        | 36   | —    | ns   |  |  |  |  |

| SS26 | (Tx/Rx) CK clock fall time         | —    | 6.0  | ns   |  |  |  |  |

| SS28 | (Rx) CK high to FS (bl) high       | -10  | 15.0 | ns   |  |  |  |  |

| SS30 | (Rx) CK high to FS (bl) low        | 10   | —    | ns   |  |  |  |  |

| SS32 | (Rx) CK high to FS (wl) high       | -10  | 15.0 | ns   |  |  |  |  |

| SS34 | (Rx) CK high to FS (wl) low        | 10   | —    | ns   |  |  |  |  |

| SS35 | (Tx/Rx) External FS rise time      | —    | 6.0  | ns   |  |  |  |  |

| SS36 | (Tx/Rx) External FS fall time      | —    | 6.0  | ns   |  |  |  |  |

| SS40 | SRXD setup time before (Rx) CK low | 10   | —    | ns   |  |  |  |  |

| SS41 | SRXD hold time after (Rx) CK low   | 2    | —    | ns   |  |  |  |  |

#### Table 90. SSI Receiver Timing with External Clock

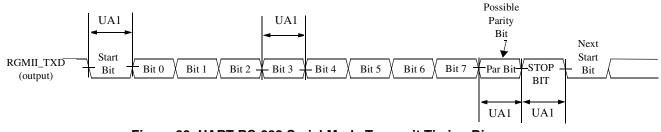

### 4.11.20.2.1 UART Transmitter

Figure 99 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 92 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 99. UART RS-232 Serial Mode Transmit Timing Diagram

| ID  | Parameter         | Symbol            | Min                                                    | Мах                                                | Unit |

|-----|-------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> +<br>T <sub>ref_clk</sub> | _    |

Table 92. RS-232 Serial Mode Transmit Timing Parameters

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

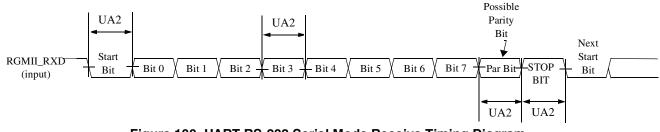

### 4.11.20.2.2 UART Receiver

Figure 100 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 93 lists serial mode receive timing characteristics.

Figure 100. UART RS-232 Serial Mode Receive Timing Diagram

#### Table 93. RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | —    |

<sup>1</sup> The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

#### Package Information and Contact Assignments

| AC          | AB           | AA          | 7           | 8           | >            | 5           | F           |

|-------------|--------------|-------------|-------------|-------------|--------------|-------------|-------------|

| DRAM_D4     | LVDS1_TX2_N  | LVDS1_TX1_P | LVDS1_TX0_N | LVDS0_TX3_P | LVDS0_TX2_P  | LVDS0_TX0_P | GPIO_2      |

| DRAM_VREF   | LVDS1_TX2_P  | LVDS1_TX1_N | LVDS1_TX0_P | LVDS0_TX3_N | LVDS0_TX2_N  | LVDS0_TX0_N | GPIO_9      |

| DRAM_DQM0   | GND          | LVDS1_TX3_N | LVDS1_CLK_N | GND         | LVDS0_CLK_P  | LVDS0_TX1_P | GPIO_6      |

| DRAM_D2     | DRAM_D6      | LVDS1_TX3_P | LVDS1_CLK_P | KEY_ROW2    | LVDS0_CLK_N  | LVDS0_TX1_N | GPIO_1      |

| DRAM_D13    | DRAM_D12     | DRAM_D3     | GND         | KEY_COL0    | KEY_ROW4     | KEY_COL3    | GPIO_0      |

| DRAM_DQM1   | DRAM_D14     | DRAM_D10    | DRAM_RESET  | KEY_COL2    | KEY_ROW0     | KEY_ROW1    | KEY_COL4    |

| DRAM_D15    | DRAM_D16     | GND         | DRAM_D20    | GND         | NVCC_LVDS2P5 | KEY_COL1    | KEY_ROW3    |

| DRAM_D22    | DRAM_DQM2    | DRAM_D17    | DRAM_D21    | GND         | GND          | GND         | GND         |

| DRAM_D28    | DRAM_D18     | DRAM_D23    | DRAM_D19    | GND         | NVCC_DRAM    | VDDARM_IN   | VDDARM_IN   |

| DRAM_SDQS3  | DRAM_SDQS3_B | GND         | DRAM_D25    | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  |

| DRAM_D31    | DRAM_D27     | DRAM_SDCKE1 | DRAM_SDCKE0 | GND         | NVCC_DRAM    | GND         | GND         |

| DRAM_A11    | DRAM_SDBA2   | DRAM_A14    | DRAM_A15    | GND         | NVCC_DRAM    | GND         | GND         |

| DRAM_A6     | DRAM_A8      | GND         | DRAM_A7     | GND         | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  |

| DRAM_A0     | DRAM_A1      | DRAM_A2     | DRAM_A3     | DRAM_A4     | NVCC_DRAM    | VDDSOC_CAP  | VDDSOC_CAP  |

| DRAM_SDBA0  | DRAM_RAS     | DRAM_A10    | DRAM_SDBA1  | GND         | NVCC_DRAM    | GND         | GND         |

| DRAM_SDODT0 | DRAM_SDWE    | GND         | DRAM_CS0    | GND         | NVCC_DRAM    | VDDSOC_IN   | VDDSOC_IN   |

| DRAM_A13    | DRAM_SDODT1  | NC          | NC          | GND         | NVCC_DRAM    | GND         | GND         |

| Ŋ           | NC           | NC          | NC          | GND         | NVCC_DRAM    | NVCC_DRAM   | NVCC_DRAM   |

| N           | NC           | GND         | NC          | GND         | GND          | GND         | GND         |

| N           | NC           | NC          | Ŋ           | ENET_TXD1   | ENET_MDC     | ENET_TXD0   | DISP0_DAT21 |

| N           | NC           | NC          | NC          | ENET_RXD0   | ENET_TX_EN   | ENET_CRS_DV | DISP0_DAT16 |

| N           | NC           | GND         | NC          | ENET_RXD1   | ENET_REF_CLK | DISP0_DAT20 | DISP0_DAT15 |

| NC          | NC           | NC          | Q           | ENET_RX_ER  | ENET_MDIO    | DISP0_DAT19 | DISP0_DAT11 |

| S           | GND          | NC          | GND         | DISP0_DAT23 | DISP0_DAT22  | DISP0_DAT17 | DISP0_DAT12 |

| NC          | NC           | NC          | NC          | NC          | DISP0_DAT18  | DISP0_DAT14 | DISP0_DAT9  |

| AC          | AB           | AA          | ٨           | Ν           | >            | D           | F           |

#### Table 102. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

#### Package Information and Contact Assignments

|    | AE             | AD           |

|----|----------------|--------------|

| -  | GND            | DRAM_D5      |

| 2  | DRAM_D1        | DRAM_D0      |

| e  | DRAM_SDQS0     | DRAM_SDQS0_B |

| 4  | DRAM_D7        | GND          |

| 5  | DRAM_D9        | DRAM_D8      |

| 9  | DRAM_SDQS1_B   | DRAM_SDQS1   |

| 7  | DRAM_D11       | GND          |

| 8  | DRAM_SDQS2_B   | DRAM_SDQS2   |

| 6  | DRAM_D24       | DRAM_D29     |

| 10 | DRAM_DQM3      | GND          |

| 11 | DRAM_D26       | DRAM_D30     |

| 12 | DRAM_A9        | DRAM_A12     |

| 13 | DRAM_A5        | GND          |

| 14 | DRAM_SDCLK_1_B | DRAM_SDCLK_1 |

| 15 | DRAM_SDCLK_0_B | DRAM_SDCLK_0 |

| 16 | DRAM_CAS       | GND          |

| 17 | ZQPAD          | DRAM_CS1     |

| 18 | NC             | NC           |

| 19 | NC             | GND          |

| 20 | NC             | NC           |

| 21 | NC             | NC           |

| 22 | NC             | GND          |

| 23 | NC             | NC           |

| 24 | NC             | NC           |

| 25 | GND            | NC           |

|    | AE             | AD           |

|    |                |              |

Table 102. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

Table 103 shows the 21 x 21 mm, 0.8 mm pitch ball map for the i.MX 6DualLite.

Table 103. 21 x 21 mm, 0.8 mm Pitch Ball Map