#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

E·XF

| Details                            |                                                                                                                                     |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Obsolete                                                                                                                            |

| Core Processor                     | ARM® Cortex®-A9                                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                                      |

| Speed                              | 800MHz                                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ MPE                                                                                                               |

| RAM Controllers                    | DDR3, DDR3L, LPDDR2                                                                                                                 |

| Graphics Acceleration              | Yes                                                                                                                                 |

| Display & Interface<br>Controllers | HDMI, Keypad, LCD, LVDS, MIPI                                                                                                       |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                                 |

| SATA                               | -                                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                                              |

| Operating<br>Temperature           | -40°C ~ 125°C (TJ)                                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                                           |

| Supplier Device<br>Package         | 624-MAPBGA (21x21)                                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u4avm08ac                                                             |

|                                    |                                                                                                                                     |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Two Controller Area Network (FlexCAN), 1 Mbps each

- Two Watchdog timers (WDOG)

- Audio MUX (AUDMUX)

- MLB (MediaLB) provides interface to MOST Networks (MOST25, MOST50, MOST150) with the option of DTCP cipher accelerator

The i.MX 6Solo/6DualLite processors integrate advanced power management unit and controllers:

- Provide PMU, including LDO supplies, for on-chip resources

- Use Temperature Sensor for monitoring the die temperature

- Support DVFS techniques for low power modes

- Use SW State Retention and Power Gating for ARM and MPE

- Support various levels of system power modes

- Use flexible clock gating control scheme

The i.MX 6Solo/6DualLite processors use dedicated hardware accelerators to meet the targeted multimedia performance. The use of hardware accelerators is a key factor in obtaining high performance at low power consumption numbers, while having the CPU core relatively free for performing other tasks.

The i.MX 6Solo/6DualLite processors incorporate the following hardware accelerators:

- VPU—Video Processing Unit

- IPUv3H—Image Processing Unit version 3H

- GPU3Dv5—3D Graphics Processing Unit (OpenGL ES 2.0) version 5

- GPU2Dv2—2D Graphics Processing Unit (BitBlt)

- ASRC—Asynchronous Sample Rate Converter

Security functions are enabled and accelerated by the following hardware:

- ARM TrustZone including the TZ architecture (separation of interrupts, memory mapping, etc.)

- SJC—System JTAG Controller. Protecting JTAG from debug port attacks by regulating or blocking the access to the system debug features.

- CAAM—Cryptographic Acceleration and Assurance Module, containing cryptographic and hash engines, 16 KB secure RAM, and True and Pseudo Random Number Generator (NIST certified).

- SNVS—Secure Non-Volatile Storage, including Secure Real Time Clock

- CSU—Central Security Unit. Enhancement for the IC Identification Module (IIM). Will be configured during boot and by eFUSEs and will determine the security level operation mode as well as the TZ policy.

- A-HAB—Advanced High Assurance Boot—HABv4 with the new embedded enhancements: SHA-256, 2048-bit RSA key, version control mechanism, warm boot, CSU, and TZ initialization.

### NOTE

The actual feature set depends on the part numbers as described in Table 1, "Orderable Part Numbers," on page 3. Functions, such as video hardware acceleration, and 2D and 3D hardware graphics acceleration may not be enabled for specific part numbers.

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 11 are required for use with Freescale BSPs to ensure precise time

keeping and USB operation. For RTC\_XTAL operation, two clock sources are available.

On-chip 40 kHz ring oscillator-this clock source has the following characteristics:

Approximately 25 µA more Idd than crystal oscillator

Approximately ±50% tolerance

No external component required

Starts up quicker than 32 kHz crystal oscillator

External crystal oscillator with on-chip support circuit:

At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

Higher accuracy than ring oscillator

If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision timeout.

### 4.1.5 Maximal Supply Currents

The Power Virus numbers shown in Table 12 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The MMPF0100xxxx, Freescale's power management IC targeted for the i.MX 6x family, supports the Power Virus mode operating at 1% duty cycle. Higher duty cycles are allowed, but a robust thermal design is required for the increased system power dissipation.

See the i.MX 6Solo/6DualLite Power Consumption Measurement Application Note (AN4576) for more details on typical power consumption under various use case definitions.

| Power Line                         | Conditions                                             | Max Current      | Unit |  |  |

|------------------------------------|--------------------------------------------------------|------------------|------|--|--|

| VDDARM_IN                          | 996 MHz ARM clock<br>based on Power Virus<br>operation | 2200             | mA   |  |  |

| VDDSOC_IN                          | 996 MHz ARM clock                                      | 1260             | mA   |  |  |

| VDDHIGH_IN                         |                                                        | 125 <sup>1</sup> | mA   |  |  |

| VDD_SNVS_IN                        |                                                        | 275 <sup>2</sup> | μA   |  |  |

| USB_OTG_VBUS/USB_H1_VBUS (LDO 3P0) |                                                        | 25 <sup>3</sup>  | mA   |  |  |

| Primary Interface (IO) Supplies    |                                                        |                  |      |  |  |

Table 12. Maximal Supply Currents

| Power Line | Conditions | Max Current                          | Unit |

|------------|------------|--------------------------------------|------|

| NVCC_DRAM  | —          | 4                                    |      |

| NVCC_ENET  | N=10       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_LCD   | N=29       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_GPIO  | N=24       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_CSI   | N=20       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_EIM   | N=53       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_JTAG  | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_RGMII | N=12       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD1   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD2   | N=6        | Use maximal IO equation <sup>5</sup> |      |

| NVCC_SD3   | N=11       | Use maximal IO equation <sup>5</sup> |      |

| NVCC_NANDF | N=26       | Use maximal IO equation <sup>5</sup> |      |

|            | MISC       |                                      |      |

| DDR_VREF   | —          | 1                                    | mA   |

#### Table 12. Maximal Supply Currents (continued)

<sup>1</sup> The actual maximum current drawn from VDDHIGH\_IN will be as shown plus any additional current drawn from the VDDHIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS2P5, NVCC\_MIPI, or HDMI and PCIe VPH supplies).

<sup>2</sup> The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA, if available. VDD\_SNVS\_CAP charge time will increase if less than 1 mA is available.

<sup>3</sup> This is the maximum current per active USB physical interface.

<sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the i.MX 6Solo/DualLite Power Consumption Measurement Application Note (AN4576) for examples of DRAM power consumption during specific use case scenarios.

<sup>5</sup> General equation for estimated, maximal power consumption of an IO power supply:

$Imax = N \times C \times V \times (0.5 \times F)$

Where:

N—Number of IO pins supplied by the power line

C—Equivalent external capacitive load

V—IO voltage

(0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

- VDDARM\_IN supply must be turned ON together with VDDSOC\_IN supply or not delayed more than 1 ms

- VDDARM\_CAP must not exceed VDDSOC\_CAP by more than 50 mV.

### NOTE

The POR\_B input (if used) must be immediately asserted at power-up and remain asserted until after the last power rail reaches its working voltage. In the absence of an external reset feeding the POR\_B input, the internal POR module takes control. See the *i.MX 6Solo/6DualLite Reference Manual* for further details and to ensure that all necessary requirements are being met.

### NOTE

Need to ensure that there is no back voltage (leakage) from any supply on the board towards the 3.3 V supply (for example, from the external components that use both the 1.8 V and 3.3 V supplies).

### NOTE

USB\_OTG\_VBUS and USB\_H1\_VBUS are not part of the power supply sequence and may be powered at any time.

### 4.2.2 Power-Down Sequence

No special restrictions for i.MX 6Solo/6DualLite IC.

### 4.2.3 **Power Supplies Usage**

All I/O pins should not be externally driven while the I/O power supply for the pin (NVCC\_xxx) is OFF. This can cause internal latch-up and malfunctions due to reverse current flows. For information about I/O power supply of each pin, see "Power Rail" columns in pin list tables of Section 6, "Package Information and Contact Assignments."

### 4.3 Integrated LDO Voltage Regulator Parameters

Various internal supplies can be powered ON from internal LDO voltage regulators. All the supply pins named \*\_CAP must be connected to external capacitors. The onboard LDOs are intended for internal use only and should not be used to power any external circuitry. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for details on the power tree scheme.

### NOTE

The \*\_CAP signals should not be powered externally. These signals are intended for internal LDO or LDO bypass operation only.

### 4.3.1 Digital Regulators (LDO\_ARM, LDO\_PU, LDO\_SOC)

There are three digital LDO regulators ("Digital", because of the logic loads that they drive, not because of their construction). The advantages of the regulators are to reduce the input supply variation because of

### 4.4.3 Ethernet PLL

| Parameter          | Value                   |  |

|--------------------|-------------------------|--|

| Clock output range | 500 MHz                 |  |

| Reference clock    | 24 MHz                  |  |

| Lock time          | <11250 reference cycles |  |

#### Table 19. Ethernet PLL's Electrical Parameters

### 4.4.4 480 MHz PLL

#### Table 20. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                 |  |

|--------------------|-----------------------|--|

| Clock output range | 480 MHz PLL output    |  |

| Reference clock    | 24 MHz                |  |

| Lock time          | <383 reference cycles |  |

### 4.4.5 MLB PLL

The MediaLB PLL is necessary in the MediaLB 6-Pin implementation to phase align the internal and external clock edges, effectively tuning out the delay of the differential clock receiver and is also responsible for generating the higher speed internal clock, when the internal-to-external clock ratio is not 1:1.

#### Table 21. MLB PLL's Electrical Parameters

| Parameter | Value |

|-----------|-------|

| Lock time | <1 ms |

### 4.4.6 ARM PLL

#### Table 22. ARM PLL's Electrical Parameters

| Parameter          | Value                  |  |

|--------------------|------------------------|--|

| Clock output range | 650 MHz ~ 1.3 GHz      |  |

| Reference clock    | 24 MHz                 |  |

| Lock time          | <2250 reference cycles |  |

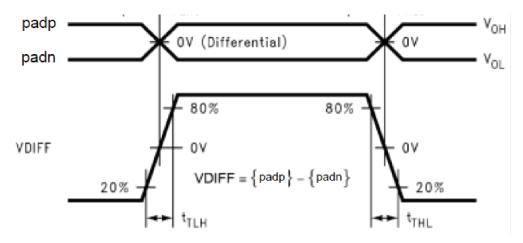

Table 33 shows the AC parameters for LVDS I/O.

| Parameter                                | Symbol           | Test Condition                 | Min | Тур | Мах  | Unit |

|------------------------------------------|------------------|--------------------------------|-----|-----|------|------|

| Differential pulse skew <sup>1</sup>     | t <sub>SKD</sub> |                                | _   | _   | 0.25 |      |

| Transition Low to High Time <sup>2</sup> | t <sub>TLH</sub> | Rload = 100 Ω,<br>Cload = 2 pF | —   | —   | 0.5  | ns   |

| Transition High to Low Time <sup>2</sup> | t <sub>THL</sub> |                                | —   | —   | 0.5  |      |

| Operating Frequency                      | f                | —                              | —   | 600 | 800  | MHz  |

| Offset voltage imbalance                 | Vos              | —                              | _   | —   | 150  | mV   |

t<sub>SKD</sub> = | t<sub>PHLD</sub> - t<sub>PLHD</sub> |, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

<sup>2</sup> Measurement levels are 20-80% from output voltage.

### 4.7.4 MLB I/O AC Parameters

The differential output transition time waveform is shown in Figure 7.

Figure 7. Differential MLB Driver Transition Time Waveform

A 4-stage pipeline is utilized in the MLB 6-pin implementation in order to facilitate design, maximize throughput, and allow for reasonable PCB trace lengths. Each cycle is one ipp\_clk\_in\* (internal clock from MLB PLL) clock period. Cycles 2, 3, and 4 are MLB PHY related. Cycle 2 includes clock-to-output delay of Signal/Data sampling flip-flop and Transmitter, Cycle 3 includes clock-to-output delay of Signal/Data clocked receiver, Cycle 4 includes clock-to-output delay of Signal/Data sampling flip-flop.

MLB 6-pin pipeline diagram is shown in Figure 8.

### 4.8.1 GPIO Output Buffer Impedance

Table 35 shows the GPIO output buffer impedance (OVDD 1.8 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 260       |      |

|               |        | 010                  | 130       |      |

| Output Driver | Rdrv   | 011                  | 90        |      |

| Impedance     |        | 100                  | 60        | Ω    |

|               |        | 101                  | 50        |      |

|               |        | 110                  | 40        |      |

|               |        | 111                  | 33        |      |

#### Table 35. GPIO Output Buffer Average Impedance (OVDD 1.8 V)

Table 36 shows the GPIO output buffer impedance (OVDD 3.3 V).

| Parameter     | Symbol | Drive Strength (DSE) | Typ Value | Unit |

|---------------|--------|----------------------|-----------|------|

|               |        | 001                  | 150       |      |

|               |        | 010                  | 75        |      |

| Output Driver | Rdrv   | 011                  | 50        |      |

| Impedance     |        | 100                  | 37        | Ω    |

|               |        | 101                  | 30        |      |

|               |        | 110                  | 25        |      |

|               |        | 111                  | 20        |      |

### 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 37 shows DDR I/O output buffer impedance of i.MX 6Solo/6DualLite processors.

| Table 37. DDR I/O Output | t Buffer Impedance |

|--------------------------|--------------------|

|                          |                    |

|                            |        |                                                      | Тур                                              |                                                  |      |

|----------------------------|--------|------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

| Parameter                  | Symbol | Test Conditions DSE(Drive<br>Strength)               | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv   | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

#### Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

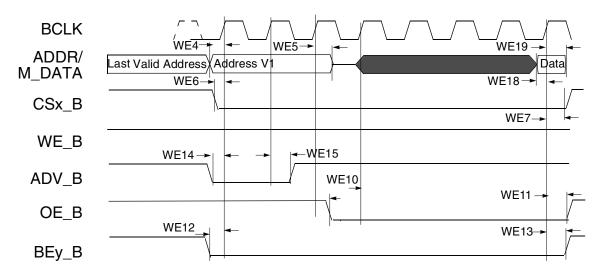

Figure 17. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

### 4.9.3.5 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22, and Table 44 help you determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for the EIM programming model.

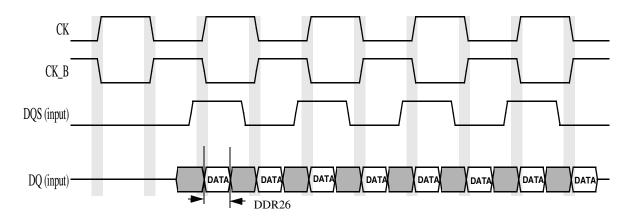

Figure 26 shows the read DDR3/DDR3L timing parameters. The timing parameters for this diagram appear in Table 47.

#### Figure 26. DDR3/DDR3L Read Cycle

#### Table 47. DDR3/DDR3L Read Cycle

| ID Parameter |                                        | Symbol | CK = 4 | Unit |      |

|--------------|----------------------------------------|--------|--------|------|------|

|              | i arameter                             |        | Min    | Max  | onne |

| DDR26        | Minimum required DQ valid window width |        | 450    | —    | ps   |

<sup>1</sup> To receive the reported setup and hold values, read calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

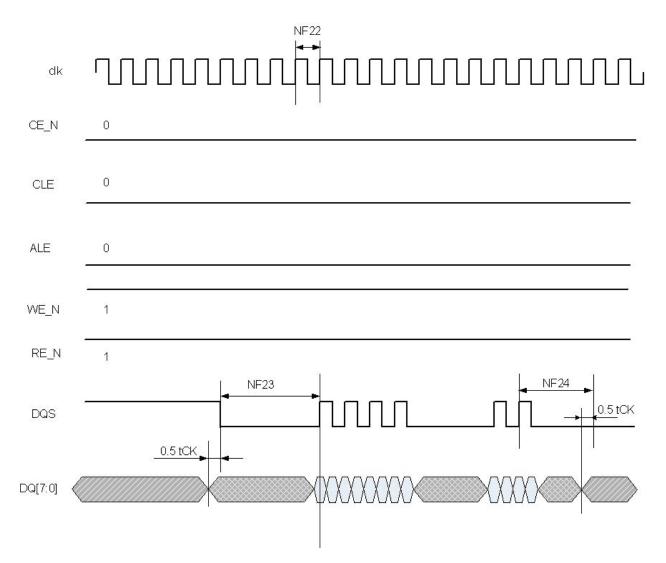

### 4.10.3.2 Read and Write Timing

Figure 38. Samsung Toggle Mode Data Write Timing

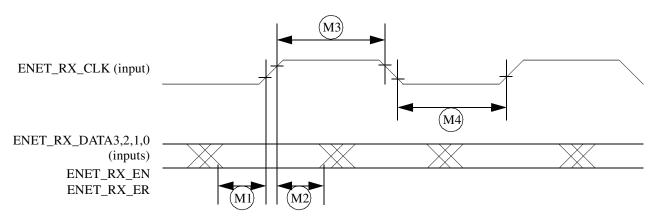

Figure 47 shows MII receive signal timings. Table 60 describes the timing parameters (M1–M4) shown in the figure.

Figure 47. MII Receive Signal Timing Diagram

Table 60. MII Receive Signal Timing

| ID | Characteristic <sup>1</sup>                                        | Min. | Max. | Unit               |

|----|--------------------------------------------------------------------|------|------|--------------------|

| M1 | ENET_RX_DATA3,2,1,0, ENET_RX_EN, ENET_RX_ER to ENET_RX_CLK setup   | 5    | _    | ns                 |

| M2 | ENET_RX_CLK to ENET_RX_DATA3,2,1,0, ENET_RX_EN,<br>ENET_RX_ER hold | 5    | _    | ns                 |

| М3 | ENET_RX_CLK pulse width high                                       | 35%  | 65%  | ENET_RX_CLK period |

| M4 | ENET_RX_CLK pulse width low                                        | 35%  | 65%  | ENET_RX_CLK period |

<sup>1</sup> ENET\_RX\_EN, ENET\_RX\_CLK, and ENET0\_RXD0 have the same timing in 10 Mbps 7-wire interface mode.

## 4.11.5.1.2 MII Transmit Signal Timing (ENET\_TX\_DATA3,2,1,0, ENET\_TX\_EN, ENET\_TX\_ER, and ENET\_TX\_CLK)

The transmitter functions correctly up to an ENET\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_TX\_CLK frequency.

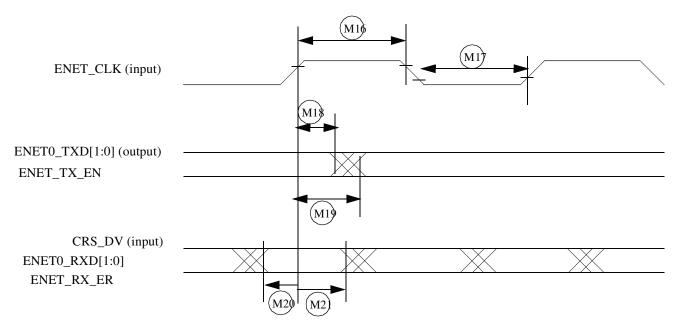

Figure 51 shows RMII mode timings. Table 64 describes the timing parameters (M16–M21) shown in the figure.

#### Figure 51. RMII Mode Signal Timing Diagram

#### Table 64. RMII Signal Timing

| ID  | Characteristic                                                   | Min. | Max. | Unit            |

|-----|------------------------------------------------------------------|------|------|-----------------|

| M16 | ENET_CLK pulse width high                                        | 35%  | 65%  | ENET_CLK period |

| M17 | ENET_CLK pulse width low                                         | 35%  | 65%  | ENET_CLK period |

| M18 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN invalid                   | 4    | _    | ns              |

| M19 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN valid                     | _    | 15   | ns              |

| M20 | ENET0_RXD[1:0], CRS_DV(ENET_RX_EN), ENET_RX_ER to ENET_CLK setup | 4    | _    | ns              |

| M21 | ENET_CLK to ENET0_RXD[1:0], ENET_RX_EN, ENET_RX_ER hold          | 2    | _    | ns              |

### 4.11.5.3 RGMII Signal Switching Specifications

The following timing specifications meet the requirements for RGMII interfaces for a range of transceiver devices.

| Table 65. RGMII Signa | I Switching Specifications <sup>1</sup> |

|-----------------------|-----------------------------------------|

|-----------------------|-----------------------------------------|

| Symbol                          | Description                              |      | Max. | Unit |

|---------------------------------|------------------------------------------|------|------|------|

| T <sub>cyc</sub> <sup>2</sup>   | Clock cycle duration                     | 7.2  | 8.8  | ns   |

| T <sub>skewT</sub> <sup>3</sup> | Data to clock output skew at transmitter | -100 | 900  | ps   |

### Table 72 shows timing characteristics of signals presented in Figure 68 and Figure 69.

| ID   | Parameter                      | Symbol | Value                                 | Description                                                                                                                                                                                                                                                                                                      | Unit |

|------|--------------------------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5  | Display interface clock period | Tdicp  | (1)                                   | Display interface clock. IPP_DISP_CLK                                                                                                                                                                                                                                                                            | ns   |

| IP6  | Display pixel clock period     | Tdpcp  | DISP_CLK_PER_PIXEL<br>× Tdicp         | Time of translation of one pixel to display,<br>DISP_CLK_PER_PIXEL—number of pixel<br>components in one pixel (1.n). The<br>DISP_CLK_PER_PIXEL is virtual<br>parameter to define Display pixel clock<br>period.<br>The DISP_CLK_PER_PIXEL is received by<br>DC/DI one access division to <b>n</b><br>components. | ns   |

| IP7  | Screen width time              | Tsw    | (SCREEN_WIDTH)<br>× Tdicp             | SCREEN_WIDTH—screen width in,<br>interface clocks. horizontal blanking<br>included.<br>The SCREEN_WIDTH should be built by<br>suitable DI's counter <sup>2</sup> .                                                                                                                                               | ns   |

| IP8  | HSYNC width time               | Thsw   | (HSYNC_WIDTH)                         | HSYNC_WIDTH—Hsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                     | ns   |

| IP9  | Horizontal blank interval 1    | Thbi1  | BGXP × Tdicp                          | BGXP—width of a horizontal blanking<br>before a first active data in a line (in<br>interface clocks). The BGXP should be built<br>by suitable DI's counter.                                                                                                                                                      | ns   |

| IP10 | Horizontal blank interval 2    | Thbi2  | (SCREEN_WIDTH -<br>BGXP - FW) × Tdicp | Width a horizontal blanking after a last<br>active data in a line (in interface clocks)<br>FW—with of active line in interface clocks.<br>The FW should be built by suitable DI's<br>counter.                                                                                                                    | ns   |

| IP12 | Screen height                  | Tsh    | (SCREEN_HEIGHT)<br>X Tsw              | SCREEN_HEIGHT— screen height in lines<br>with blanking.<br>The SCREEN_HEIGHT is a distance<br>between 2 VSYNCs.<br>The SCREEN_HEIGHT should be built by<br>suitable DI's counter.                                                                                                                                | ns   |

| IP13 | VSYNC width                    | Tvsw   | VSYNC_WIDTH                           | VSYNC_WIDTH—Vsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter                                                                                                                                                                                                                      | ns   |

| IP14 | Vertical blank interval 1      | Tvbi1  | BGYP × Tsw                            | BGYP—width of first Vertical<br>blanking interval in line. The BGYP should<br>be built by suitable DI's counter.                                                                                                                                                                                                 | ns   |

| IP15 | Vertical blank interval 2      | Tvbi2  | (SCREEN_HEIGHT -<br>BGYP - FH) × Tsw  | Width of second Vertical<br>blanking interval in line. The FH should be<br>built by suitable DI's counter.                                                                                                                                                                                                       | ns   |

#### Table 72. Synchronous Display Interface Timing Characteristics (Pixel Level)

| V <sub>IDTL</sub>                          | Differential input low voltage threshold | -70                       |     | mV |  |  |  |

|--------------------------------------------|------------------------------------------|---------------------------|-----|----|--|--|--|

| V <sub>IHHS</sub>                          | Single ended input high voltage          |                           | 460 | mV |  |  |  |

| V <sub>ILHS</sub>                          | Single ended input low voltage           | -40                       |     | mV |  |  |  |

| V <sub>CMRXDC</sub>                        | Input common mode voltage                | 70                        | 330 | mV |  |  |  |

| Z <sub>ID</sub>                            | Differential input<br>impedance          | 80                        | 125 | Ω  |  |  |  |

|                                            | LP Lin                                   | eceiver DC Specifications |     |    |  |  |  |

| V <sub>IL</sub>                            | Input low voltage                        |                           | 550 | mV |  |  |  |

| V <sub>IH</sub>                            | Input high voltage                       | 920                       |     | mV |  |  |  |

| V <sub>HYST</sub>                          | Input hysteresis                         | 25                        |     | mV |  |  |  |

| Contention Line Receiver DC Specifications |                                          |                           |     |    |  |  |  |

| V <sub>ILF</sub>                           | Input low fault threshold                | 200                       | 450 | mV |  |  |  |

Table 75. Electrical and Timing Information (continued)

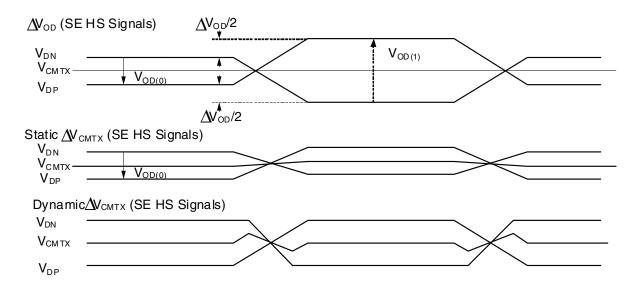

### 4.11.12.4 Possible $\triangle VCMTX$ and $\triangle VOD$ Distortions of the Single-ended HS Signals

Figure 73. Possible  $\triangle$ VCMTX and  $\triangle$ VOD Distortions of the Single-ended HS Signals

### 4.11.12.5 MIPI D-PHY Switching Characteristics

| Symbol                 | Parameters                                   | Test Conditions                                          | MIN   | ТҮР   | MAX   | Unit              |

|------------------------|----------------------------------------------|----------------------------------------------------------|-------|-------|-------|-------------------|

|                        | HS Line D                                    | rivers AC Specifications                                 | I     | 1     |       |                   |

| _                      | Maximum serial data rate (forward direction) | On DATAP/N outputs.<br>80 $\Omega$ <= RL <= 125 $\Omega$ | 80    | _     | 1000  | Mbps              |

| F <sub>DDRCLK</sub>    | DDR CLK frequency                            | On DATAP/N outputs.                                      | 40    | —     | 500   | MHz               |

| P <sub>DDRCLK</sub>    | DDR CLK period                               | 80 Ω<= RL< = 125 Ω                                       | 2     | —     | 25    | ns                |

| t <sub>CDC</sub>       | DDR CLK duty cycle                           | $t_{CDC} = t_{CPH} / P_{DDRCLK}$                         | —     | 50    | —     | %                 |

| t <sub>CPH</sub>       | DDR CLK high time                            |                                                          | —     | 1     | —     | UI                |

| t <sub>CPL</sub>       | DDR CLK low time                             |                                                          | —     | 1     | —     | UI                |

| _                      | DDR CLK / DATA Jitter                        |                                                          | —     | 75    | —     | ps pk–pk          |

| t <sub>SKEW[PN]</sub>  | Intra-Pair (Pulse) skew                      |                                                          |       | 0.075 |       | UI                |

| t <sub>SKEW[TX]</sub>  | Data to Clock Skew                           |                                                          | 0.350 |       | 0.650 | UI                |

| t <sub>SETUP[RX]</sub> | Data to Clock Receiver Setup time            |                                                          | 0.15  |       |       | UI                |

| t <sub>HOLD[RX]</sub>  | Clock to Data Receiver Hold time             |                                                          | 0.15  |       |       | UI                |

| t <sub>r</sub>         | Differential output signal rise time         | 20% to 80%, RL = 50 $\Omega$                             | 150   |       | 0.3UI | ps                |

| t <sub>f</sub>         | Differential output signal fall time         | 20% to 80%, RL = 50 $\Omega$                             | 150   |       | 0.3UI | ps                |

| ΔV <sub>CMTX(HF)</sub> | Common level variation above 450 MHz         | 80 Ω<= RL< = 125 Ω                                       |       |       | 15    | mV <sub>rms</sub> |

#### Table 76. Electrical and Timing Information

| Parameter                                                                | Symbol             | Min | Мах               | Unit | Comment |

|--------------------------------------------------------------------------|--------------------|-----|-------------------|------|---------|

| MLBSIG/MLBDAT output high<br>impedance from MLBCLK low                   | t <sub>mcfdz</sub> | 0   | t <sub>mckl</sub> | ns   | 3       |

| Bus Hold from MLBCLK low                                                 | t <sub>mdzh</sub>  | 2   | —                 | ns   | _       |

| MLBSIG/MLBDAT output valid<br>from transition of MLBCLK (low<br>to high) | t <sub>delay</sub> | _   | 7                 | ns   | _       |

Table 81. MLB 1024 Fs Timing Parameters (continued)

The controller can shut off MLBCLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLBCLK.

<sup>2</sup> MLBCLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLBDAT/MLBSIG line as soon as MLBCLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Table 82 lists the MediaLB 6-pin interface timing characteristics, and Figure 87 shows the MLB 6-pin delay, setup, and hold times.

| Parameter                                                                                              | Symbol              | Min  | Max | Unit | Comment |

|--------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|---------|

| Cycle-to-cycle system jitter                                                                           | t <sub>jitter</sub> | —    | 600 | ps   | —       |

| Transmitter MLBSP/N (MLBDP/N) output<br>valid from transition of MLBCP/N<br>(low-to-high) <sup>1</sup> | t <sub>delay</sub>  | 0.6  | 1.3 | ns   |         |

| Disable turnaround time from transition of MLBCP/N (low-to-high)                                       | t <sub>phz</sub>    | 0.6  | 3.5 | ns   |         |

| Enable turnaround time from transition of MLBCP/N (low-to-high)                                        | t <sub>plz</sub>    | 0.6  | 5.6 | ns   |         |

| MLBSP/N (MLBDP/N) valid to transition of MLBCP/N (low-to-high)                                         | t <sub>su</sub>     | 0.05 | —   | ns   |         |

| MLBSP/N (MLBDP/N) hold from transition of MLBCP/N (low-to-high) <sup>2</sup>                           | t <sub>hd</sub>     | 0.6  |     |      |         |

Table 82. MLB 6-Pin Interface Timing Parameters

t<sub>delay</sub>, t<sub>phz</sub>, t<sub>plz</sub>, t<sub>su</sub>, and t<sub>hd</sub> may also be referenced from a low-to-high transition of the recovered clock for 2:1 and 4:1 recovered-to-external clock ratios.

<sup>2</sup> The transmitting device must ensure valid data on MLBSP/N (MLBDP/N) for at least t<sub>hd(min)</sub> following the rising edge of ML-BCP/N; receivers must latch MLBSP/N (MLBDP/N) data within t<sub>hd(min)</sub> of the rising edge of MLBCP/N.

| ID                                   | Parameter                               | Min  | Мах  | Unit |

|--------------------------------------|-----------------------------------------|------|------|------|

| SS39                                 | S39 (Tx) CK high to STXD high impedance |      | 15.0 | ns   |

| Synchronous External Clock Operation |                                         |      |      |      |

| SS44                                 | SRXD setup before (Tx) CK falling       | 10.0 | _    | ns   |

| SS45                                 | SRXD hold after (Tx) CK falling         | 2.0  | —    | ns   |

| SS46                                 | SRXD rise/fall time                     | —    | 6.0  | ns   |

#### Table 89. SSI Transmitter Timing with External Clock (continued)

#### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

### 4.11.20.2.1 UART Transmitter

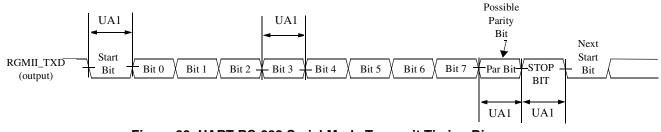

Figure 99 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 92 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 99. UART RS-232 Serial Mode Transmit Timing Diagram

| ID  | Parameter         | Symbol            | Min                                                    | Мах                                                | Unit |

|-----|-------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> +<br>T <sub>ref_clk</sub> | —    |

Table 92. RS-232 Serial Mode Transmit Timing Parameters

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

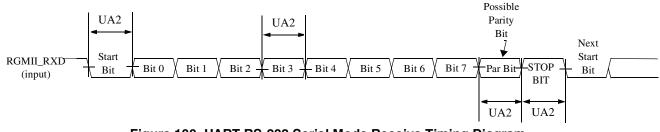

### 4.11.20.2.2 UART Receiver

Figure 100 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 93 lists serial mode receive timing characteristics.

Figure 100. UART RS-232 Serial Mode Receive Timing Diagram

#### Table 93. RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | —    |

<sup>1</sup> The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

## 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

### 6.1 21x21 mm Package Information

### 6.1.1 Case 2240, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

Figure 105 shows the top, bottom, and side views of the 21×21 mm BGA package.

Package Information and Contact Assignments

# 6.1.2 21 x 21 mm Supplies Contact Assignments and Functional Contact Assignments

Table 100 shows supplies contact assignments for the 21 x 21 mm package.

| Table 100. 21 x 21 | mm Supplies Contact | Assignments |

|--------------------|---------------------|-------------|

|--------------------|---------------------|-------------|

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remark                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| CSI_REXT         | D4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| DRAM_VREF        | AC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                          |

| DSI_REXT         | G4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| GND              | A4, A8, A13, A25, B4, C1, C4, C6, C10, D3, D6, D8, E5, E6, E7, F5, F6, F7, F8, G3, G10, G19, H8, H12, H15, H18, J2, J8, J12, J15, J18, K8, K10, K12, K15, K18, L2, L5, L8, L10, L12, L15, L18, M8, M10, M12, M15, M18, N8, N10, N15, N18, P8, P10, P12, P15, P18, R8, R12, R15, R17, T8, T11, T12, T15, T17, T19, U8, U11, U12, U15, U17, U19, V8, V19, W3, W7, W8, W9, W10, W11, W12, W13, W15, W16, W17, W18, W19, Y5, Y24, AA7, AA10, AA13, AA16, AA19, AA22, AB3, AB24, AD4, AD7, AD10, AD13, AD16, AD19, AD22, AE1, AE25 |                                                          |

| HDMI_REF         | J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| HDMI_VP          | L7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| HDMI_VPH         | M7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| NVCC_CSI         | N7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the camera sensor interface                    |

| NVCC_DRAM        | R18, T18, U18, V9, V10, V11, V12, V13, V14, V15, V16, V17, V18                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supply of the DDR interface                              |

| NVCC_EIM         | K19, L19, M19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Supply of the EIM interface                              |

| NVCC_ENET        | R19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |

| NVCC_GPIO        | P7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the GPIO interface                             |

| NVCC_JTAG        | J7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the JTAG tap controller interface              |

| NVCC_LCD         | P19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the LCD interface                              |

| NVCC_LVDS2P5     | V7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the LVDS display interface and DDR pre-drivers |

| NVCC_MIPI        | К7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Supply of the MIPI interface                             |

| NVCC_NANDF       | G15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the raw NAND Flash memories interface          |

| NVCC_PLL_OUT     | E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |

| NVCC_RGMII       | G18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the ENET interface                             |

| NVCC_SD1         | G16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |

| NVCC_SD2         | G17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |

| NVCC_SD3         | G14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supply of the SD card interface                          |