#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx6u6avm08ab                                                        |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

such as WLAN, Bluetooth<sup>TM</sup>, GPS, hard drive, displays, and camera sensors.

The i.MX 6Solo/6DualLite processors are specifically useful for applications such as:

- Automotive navigation and entertainment

- Graphics rendering for Human Machine Interfaces (HMI)

- High-performance speech processing with large databases

- Audio playback

- Video processing and display

The i.MX 6Solo/6DualLite processors have some very exciting features, for example:

- Multilevel memory system—The multilevel memory system of each processor is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The processors support many types of external memory devices, including DDR3, low voltage DDR3, LPDDR2, NOR Flash, PSRAM, cellular RAM, NAND Flash (MLC and SLC), OneNAND<sup>TM</sup>, and managed NAND, including eMMC up to rev 4.4.

- Smart speed technology—The processors have power management throughout the IC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart speed technology enables the designer to deliver a feature-rich product, requiring levels of power far lower than industry expectations.

- Dynamic voltage and frequency scaling—The processors improve the power efficiency of devices by scaling the voltage and frequency to optimize performance.

- Multimedia powerhouse—The multimedia performance of each processor is enhanced by a multilevel cache system, Neon MPE (Media Processor Engine) co-processor, a multi-standard hardware video codec, an image processing unit (IPU), and a programmable smart DMA (SDMA) controller.

- Powerful graphics acceleration—Each processor provides two independent, integrated graphics processing units: an OpenGL<sup>®</sup> ES 2.0 3D graphics accelerator with a shader and a 2D graphics accelerator.

- Interface flexibility—Each processor supports connections to a variety of interfaces: LCD controller for up to two displays (including parallel display, HDMI1.4, MIPI display, and LVDS display), dual CMOS sensor interface (parallel or through MIPI), high-speed USB on-the-go with PHY, high-speed USB host with PHY, multiple expansion card ports (high-speed MMC/SDIO host and other), 10/100/1000 Mbps Gigabit Ethernet controller, and a variety of other popular interfaces (such as UART, I<sup>2</sup>C, and I<sup>2</sup>S serial audio, and PCIe-II).

- Automotive environment support—Each processor includes interfaces, such as two CAN ports, an MLB150/50 port, an ESAI audio interface, and an asynchronous sample rate converter for multichannel/multisource audio.

- Advanced security—The processors deliver hardware-enabled security features that enable secure e-commerce, digital rights management (DRM), information encryption, secure boot, and secure software downloads. The security features will be discussed in detail in the *i.MX 6Solo/6DualLite Security Reference Manual* (to be released soon).

#### Introduction

- MIPI/DSI, two lanes at 1 Gbps

- Camera sensors:

- Two parallel Camera ports (up to 20 bit and up to 240 MHz peak)

- MIPI CSI-2 Serial port, supporting from 80 Mbps to 1 Gbps speed per data lane. The CSI-2 Receiver core can manage one clock lane and up to two data lanes. Each i.MX 6Solo/6DualLite processor has two lanes.

- Expansion cards:

- Four MMC/SD/SDIO card ports all supporting:

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One high speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB Phy

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed Phy

- Two HS hosts with integrated HS-IC USB (High Speed Inter-Chip USB) Phy

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- Three I2S/SSI/AC97, up to 1.4 Mbps each

- Enhanced Serial Audio Interface (ESAI), up to 1.4 Mbps per channel

- Five UARTs, up to 4.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while others four supports 4-wire. This is due to the SoC IOMUX limitation, since all UART IPs are identical.

- Four eCSPI (Enhanced CSPI)

- Four  $I^2C$ , supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

- System JTAG Controller (SJC)

- GPIO with interrupt capabilities

- 8x8 Key Pad Port (KPP)

- Sony Philips Digital Interconnect Format (SPDIF), Rx and Tx

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Solo/6DualLite errata document (IMX6SDLCE).

| Block Mnemonic                   | Block Name                    | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|-------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCOTP_CTRL                       | OTP Controller                | Security                    | The On-Chip OTP controller (OCOTP_CTRL) provides<br>an interface for reading, programming, and/or overriding<br>identification and control information stored in on-chip<br>fuse elements. The module supports<br>electrically-programmable poly fuses (eFUSEs). The<br>OCOTP_CTRL also provides a set of volatile<br>software-accessible signals that can be used for<br>software control of hardware elements, not requiring<br>non-volatility. The OCOTP_CTRL provides the primary<br>user-visible mechanism for interfacing with on-chip fuse<br>elements. Among the uses for the fuses are unique chip<br>identifiers, mask revision numbers, cryptographic keys,<br>JTAG secure mode, boot characteristics, and various<br>control signals, requiring permanent non-volatility. |

| OCRAM                            | On-Chip Memory<br>controller  | Data Path                   | The On-Chip Memory controller (OCRAM) module is<br>designed as an interface between system's AXI bus and<br>internal (on-chip) SRAM memory module.<br>In i.MX 6Solo/6DualLite processors, the OCRAM is<br>used for controlling the 128 KB multimedia RAM through<br>a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSC32KHz                         | OSC32KHz                      | Clocking                    | Generates 32.768 KHz clock from external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCle                             | PCI Express 2.0               | Connectivity<br>Peripherals | The PCIe IP provides PCI Express Gen 2.0 functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PMU                              | Power-Management<br>functions | Data Path                   | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width Modulation        | Connectivity<br>Peripherals | The pulse-width modulator (PWM) has a 16-bit counter<br>and is optimized to generate sound from stored sample<br>audio images and it can also generate tones. It uses<br>16-bit resolution and a 4x16 data FIFO to generate<br>sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAM<br>128 KB                    | Internal RAM                  | Internal Memory             | Internal RAM, which is accessed through OCRAM memory controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RAM<br>16 KB                     | Secure/non-secure RAM         | Secured Internal<br>Memory  | Secure/non-secure Internal RAM, interfaced through the CAAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ROM<br>96KB                      | Boot ROM                      | Internal Memory             | Supports secure and regular Boot Modes. Includes read protection on 4K region for content protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ROMCP                            | ROM Controller with<br>Patch  | Data Path                   | ROM Controller with ROM Patch support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2. i.MX 6Solo/6DualLite M | Modules List (continued) |

|---------------------------------|--------------------------|

|---------------------------------|--------------------------|

#### **Modules List**

| Block Mnemonic | Block Name                    | Subsystem                            | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPU            | Video Processing Unit         | Multimedia<br>Peripherals            | A high-performing video processing unit (VPU), which<br>covers many SD-level and HD-level video decoders and<br>SD-level encoders as a multi-standard video codec<br>engine as well as several important video processing,<br>such as rotation and mirroring.<br>See the i. <i>MX 6Solo/6DualLite Reference Manual</i><br>( <i>IMX6SDLRM</i> ) for complete list of VPU's<br>decoding/encoding capabilities.                                                                                                                                                                                                                                                                                                                                                                                            |

| WDOG-1         | Watch Dog                     | Timer Peripherals                    | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-2<br>(TZ) | Watch Dog (TrustZone)         | Timer Peripherals                    | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW. |

| WEIM           | NOR-Flash /PSRAM<br>interface | Connectivity<br>Peripherals          | <ul> <li>The WEIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALOSC        | Crystal Oscillator I/F        | Clocks, Resets, and<br>Power Control | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator to provide USB required frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- 2. Calibration is done against 240  $\Omega$  external reference resistor.

- 3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

## 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

## 4.8.4 MLB I/O Differential Output Impedance

Table 38 shows MLB I/O differential output impedance of the i.MX 6Solo/6DualLite processors.

#### Table 38. MLB I/O Differential Output Impedance

| Parameter                     | Symbol | Test Conditions | Min   | Тур | Мах | Unit |

|-------------------------------|--------|-----------------|-------|-----|-----|------|

| Differential Output Impedance | Zo     |                 | 1.6 K |     | _   | Ω    |

## 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Solo/6DualLite processor.

### 4.9.1 Reset Timings Parameters

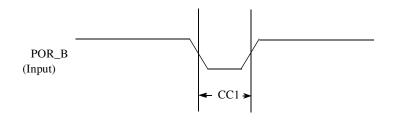

Figure 10 shows the reset timing and Table 39 lists the timing parameters.

Figure 10. Reset Timing Diagram

| Table 39. Reset | Timing | Parameters |

|-----------------|--------|------------|

|-----------------|--------|------------|

| ID  | Parameter                                                       | Min | Max | Unit               |

|-----|-----------------------------------------------------------------|-----|-----|--------------------|

| CC1 | Duration of POR_B to be qualified as valid (input slope = 5 ns) | 1   |     | RTC_XTALI<br>cycle |

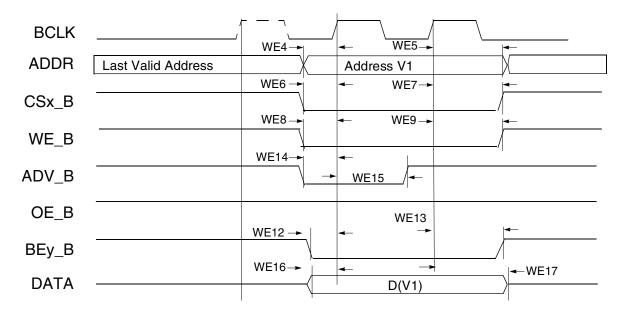

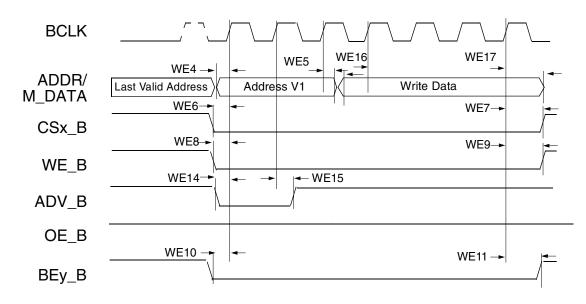

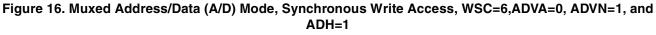

## 4.9.3.4 Examples of EIM Synchronous Accesses

|      | Parameter                                   | BCD = 0            |                    | BCD = 1   |            | BCD = 2            |                   | BCD = 3          |                  |

|------|---------------------------------------------|--------------------|--------------------|-----------|------------|--------------------|-------------------|------------------|------------------|

| ID   |                                             | Min                | Мах                | Min       | Max        | Min                | Max               | Min              | Max              |

| WE1  | BCLK Cycle time <sup>2</sup>                | t                  | —                  | 2 x t     |            | 3 x t              |                   | 4 x t            | —                |

| WE2  | BCLK Low Level<br>Width                     | 0.4 x t            | —                  | 0.8 x t   |            | 1.2 x t            | _                 | 1.6 x t          | -                |

| WE3  | BCLK High Level<br>Width                    | 0.4 x t            | —                  | 0.8 x t   |            | 1.2 x t            | —                 | 1.6 x t          | —                |

| WE4  | Clock rise to<br>address valid <sup>3</sup> | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | -t + 1.75  | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE5  | Clock rise to address invalid               | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE6  | Clock rise to<br>CSx_B valid                | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE7  | Clock rise to<br>CSx_B invalid              | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE8  | Clock rise to<br>WE_B Valid                 | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE9  | Clock rise to<br>WE_B Invalid               | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE10 | Clock rise to OE_B<br>Valid                 | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE11 | Clock rise to OE_B<br>Invalid               | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE12 | Clock rise to<br>BEy_B Valid                | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE13 | Clock rise to<br>BEy_B Invalid              | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE14 | Clock rise to<br>ADV_B Valid                | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE15 | Clock rise to<br>ADV_B Invalid              | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE16 | Clock rise to<br>Output Data Valid          | -0.5 x t -<br>1.25 | -0.5 x t +<br>1.75 | -t - 1.25 | - t + 1.75 | -1.5 x t -<br>1.25 | -1.5 x t<br>+1.75 | -2 x t -<br>1.25 | -2 x t +<br>1.75 |

| WE17 | Clock rise to<br>Output Data<br>Invalid     | 0.5 x t -<br>1.25  | 0.5 x t + 1.75     | t - 1.25  | t + 1.75   | 1.5 x t -<br>1.25  | 1.5 x t<br>+1.75  | 2 x t -<br>1.25  | 2 x t + 1.75     |

| WE18 | Input Data setup<br>time to Clock rise      | 2                  | —                  | 4         | —          | —                  |                   | —                | -                |

NOTE

In 32-bit muxed address/data (A/D) mode the 16 MSBs are driven on the data bus.

Figure 17. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=0

### 4.9.3.5 General EIM Timing-Asynchronous Mode

Figure 18 through Figure 22, and Table 44 help you determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Asynchronous read & write access length in cycles may vary from what is shown in Figure 18 through Figure 21 as RWSC, OEN & CSN is configured differently. See the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* for the EIM programming model.

- <sup>1</sup> All measurements are in reference to Vref level.

- $^2\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

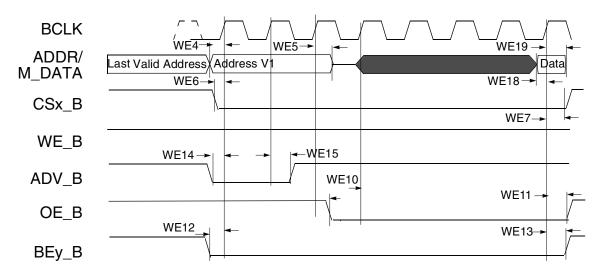

Figure 25shows the DDR3/DDR3L write timing parameters. The timing parameters for this diagram appear in Table 46.

Figure 25. DDR3/DDR3L Write Cycle

| ID    | Parameter                                                 | Symbol | CK = 40 | Unit  |      |

|-------|-----------------------------------------------------------|--------|---------|-------|------|

|       | Falametei                                                 | Symbol | Min     | Max   | Unit |

| DDR17 | DQ and DQM setup time to DQS (differential strobe)        | tDS    | 420     | —     | ps   |

| DDR18 | DQ and DQM hold time to DQS (differential strobe)         | tdн    | 345     | _     | ps   |

| DDR21 | DQS latching rising transitions to associated clock edges | tDQSS  | -0.25   | +0.25 | tCK  |

| DDR22 | DQS high level width                                      | tDQSH  | 0.45    | 0.55  | tCK  |

| DDR23 | DQS low level width                                       | tDQSL  | 0.45    | 0.55  | tCK  |

#### Table 46. DDR3/DDR3L Write Cycle

<sup>1</sup> To receive the reported setup and hold values, write calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

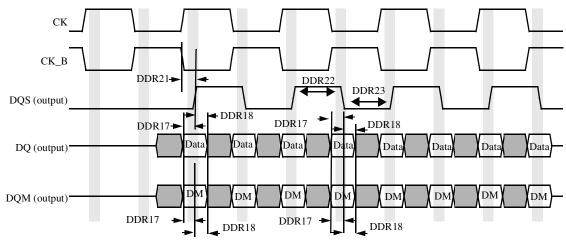

Figure 32. Write Data Latch Cycle Timing Diagram

| ID  | Parameter      | Symbol | Tim<br>T = GPMI C | -    | Example T<br>GPMI Clock<br>T = 1 | Unit |    |

|-----|----------------|--------|-------------------|------|----------------------------------|------|----|

|     |                |        | Min.              | Max. | Min.                             | Max. |    |

| NF1 | CLE setup time | tCLS   | (AS+1) x T        | _    | 10                               | _    | ns |

| NF2 | CLE hold time  | tCLH   | (DH+1) x T        | _    | 20                               | _    | ns |

| NF3 | CEn setup time | tCS    | (AS+1) x T        | _    | 10                               | _    | ns |

| NF4 | CE hold time   | tCH    | (DH+1) x T        | _    | 20                               |      | ns |

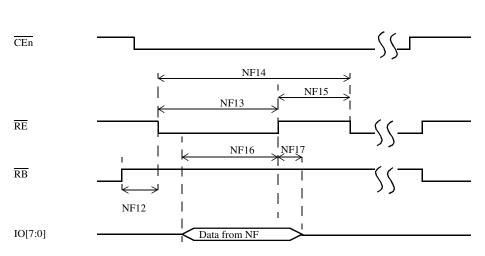

Table 51. Asynchronous Mode Timing Parameters<sup>1</sup>

#### i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

CLE

## 4.11.3 Enhanced Serial Audio Interface (ESAI) Timing Parameters

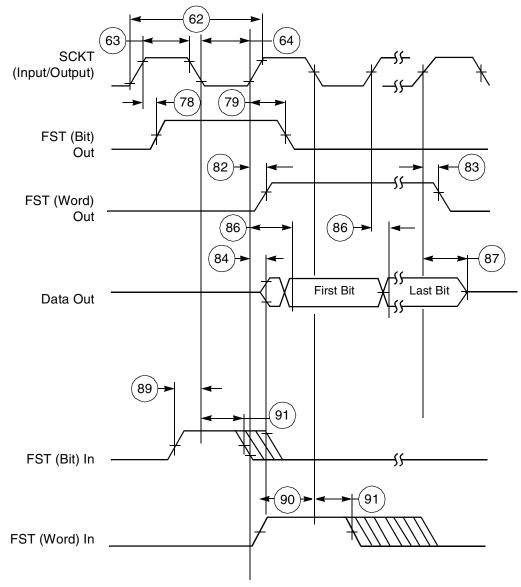

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 56 shows the interface timing values. The number field in the table refers to timing signals found in Figure 42 and Figure 43.

| No. | Characteristics <sup>1,2</sup>                                        | Symbol | Expression <sup>2</sup>                                       | Min          | Max          | Condition <sup>3</sup> | Unit |

|-----|-----------------------------------------------------------------------|--------|---------------------------------------------------------------|--------------|--------------|------------------------|------|

| 62  | Clock cycle <sup>4</sup>                                              | tssicc | $\begin{array}{c} 4\times T_{C} \\ 4\times T_{C} \end{array}$ | 30.0<br>30.0 | _            | i ck<br>i ck           | ns   |

| 63  | Clock high period:<br>• For internal clock<br>• For external clock    |        | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                       | 6<br>15      |              |                        | ns   |

| 64  | Clock low period:<br>• For internal clock<br>• For external clock     |        | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                       | 6<br>15      | _            |                        | ns   |

| 65  | SCKR rising edge to FSR out (bl) high                                 |        | _                                                             |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66  | SCKR rising edge to FSR out (bl) low                                  |        |                                                               |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67  | SCKR rising edge to FSR out (wr) high <sup>5</sup>                    |        | —                                                             |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68  | SCKR rising edge to FSR out (wr) low <sup>5</sup>                     |        |                                                               |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69  | SCKR rising edge to FSR out (wl) high                                 |        |                                                               |              | 16.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70  | SCKR rising edge to FSR out (wl) low                                  |        |                                                               |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge |        |                                                               | 12.0<br>19.0 |              | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                             |        |                                                               | 3.5<br>9.0   |              | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>5</sup>         |        |                                                               | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                          |        |                                                               | 2.0<br>12.0  |              | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                           |        |                                                               | 2.5<br>8.5   | —            | x ck<br>i ck a         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                 | <br>   | —                                                             |              | 18.0<br>8.0  | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                  |        | —                                                             |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80  | SCKT rising edge to FST out (wr) high <sup>5</sup>                    | _      |                                                               |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

#### Table 56. Enhanced Serial Audio Interface (ESAI) Timing

Figure 42. ESAI Transmitter Timing

## 4.11.13 HSI Host Controller Timing Parameters

This section describes the timing parameters of the HSI Host Controller which are compliant with High-speed Synchronous Serial Interface (HSI) Physical Layer specification version1.01.

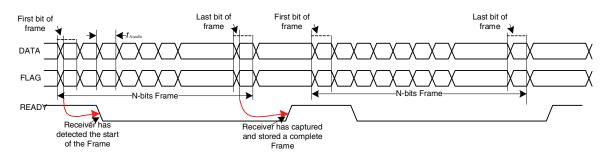

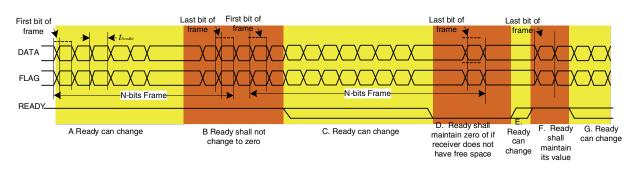

## 4.11.13.1 Synchronous Data Flow

### 4.11.13.2 Pipelined Data Flow

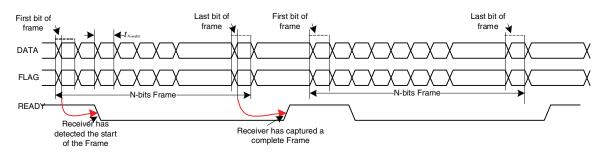

### 4.11.13.3 Receiver Real-Time Data Flow

Figure 80. Receiver Real-Time Data Flow READY Signal Timing

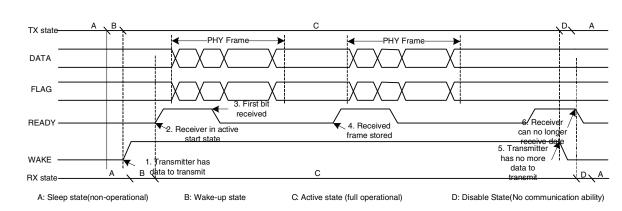

### 4.11.13.4 Synchronized Data Flow Transmission with Wake

Figure 81. Synchronized Data Flow Transmission with WAKE

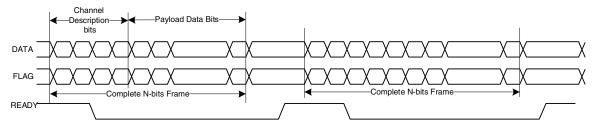

### 4.11.13.5 Stream Transmission Mode Frame Transfer

Figure 82. Stream Transmission Mode Frame Transfer (Synchronized Data Flow)

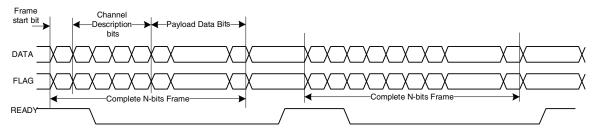

### 4.11.13.6 Frame Transmission Mode (Synchronized Data Flow)

Figure 83. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

## 4.11.14 MediaLB (MLB) Characteristics

### 4.11.14.1 MediaLB (MLB) DC Characteristics

Table 78 lists the MediaLB 3-pin interface electrical characteristics.

#### Table 78. MediaLB 3-Pin Interface Electrical DC Specifications

| Parameter                   | Symbol          | Test Conditions           | Min | Max | Unit |

|-----------------------------|-----------------|---------------------------|-----|-----|------|

| Maximum input voltage       | —               | —                         | _   | 3.6 | V    |

| Low level input threshold   | V <sub>IL</sub> | _                         | _   | 0.7 | V    |

| High level input threshold  | V <sub>IH</sub> | See Note <sup>1</sup>     | 1.8 | _   | V    |

| Low level output threshold  | V <sub>OL</sub> | I <sub>OL</sub> = 6 mA    | _   | 0.4 | V    |

| High level output threshold | V <sub>OH</sub> | I <sub>OH</sub> = -6 mA   | 2.0 | —   | V    |

| Input leakage current       | ١L              | 0 < V <sub>in</sub> < VDD | _   | ±10 | μΑ   |

<sup>1</sup> Higher V<sub>IH</sub> thresholds can be used; however, the risks associated with less noise margin in the system must be evaluated and assumed by the customer.

#### Table 79 lists the MediaLB 6-pin interface electrical characteristics.

#### Table 79. MediaLB 6-Pin Interface Electrical DC Specifications

| Symbol             | Test Conditions                                                              | Min                                                                                                                                                                                                                                                                                                               | Max                                                                                                                                                                     | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                  | Driver Characteristics                                                       |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>OD</sub>    | See Note <sup>1</sup>                                                        | 300                                                                                                                                                                                                                                                                                                               | 500                                                                                                                                                                     | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ΔV <sub>OD</sub>   | _                                                                            | -50                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                      | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>OCM</sub>   | _                                                                            | 1.0                                                                                                                                                                                                                                                                                                               | 1.5                                                                                                                                                                     | V                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ΔV <sub>OCM</sub>  | _                                                                            | -50                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                      | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>CMV</sub>   | See Note <sup>2</sup>                                                        | _                                                                                                                                                                                                                                                                                                                 | 150                                                                                                                                                                     | mVpp                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ll <sub>OS</sub> l | See Note <sup>3</sup>                                                        |                                                                                                                                                                                                                                                                                                                   | 43                                                                                                                                                                      | mA                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ZO                 | —                                                                            | 1.6                                                                                                                                                                                                                                                                                                               | _                                                                                                                                                                       | kΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| -                  | V <sub>OD</sub><br>ΔV <sub>OD</sub><br>V <sub>OCM</sub><br>ΔV <sub>OCM</sub> | Driver Characteristics           V <sub>OD</sub> See Note <sup>1</sup> ΔV <sub>OD</sub> —           ΔV <sub>OD</sub> —           V <sub>OCM</sub> —           ΔV <sub>OCM</sub> —           ΔV <sub>OCM</sub> —           V <sub>CMV</sub> See Note <sup>2</sup> II <sub>OS</sub> I         See Note <sup>3</sup> | Driver Characteristics $V_{OD}$ See Note1300 $\Delta V_{OD}$ —-50 $V_{OCM}$ —1.0 $\Delta V_{OCM}$ —-50 $\Delta V_{OCM}$ —-50 $V_{CMV}$ See Note2— $II_{OS}I$ See Note3— | Driver Characteristics         300         500 $\Delta V_{OD}$ See Note <sup>1</sup> 300         500 $\Delta V_{OD}$ -         -50         50 $\nabla_{OCM}$ -         1.0         1.5 $\Delta V_{OCM}$ -         -50         50 $\nabla_{OCM}$ -         -         50 $\nabla_{VOCM}$ -         -         50 $\nabla_{VOCM}$ -         -         50 $\nabla_{VOCM}$ See Note <sup>2</sup> -         150 $I_{OSI}$ See Note <sup>3</sup> -         43 |

| Parameter                                                                | Symbol             | Min               | Мах               | Unit | Comment                                  |

|--------------------------------------------------------------------------|--------------------|-------------------|-------------------|------|------------------------------------------|

| MLBCLK operating frequency <sup>1</sup>                                  | f <sub>mck</sub>   | 11.264            | 25.6              | MHz  | 256xFs at 44.0 kHz<br>512xFs at 50.0 kHz |

| MLBCLK rise time                                                         | t <sub>mckr</sub>  | _                 | 3                 | ns   | V <sub>IL</sub> TO V <sub>IH</sub>       |

| MLBCLK fall time                                                         | t <sub>mckf</sub>  |                   | 3                 | ns   | V <sub>IH</sub> TO V <sub>IL</sub>       |

| MLBCLK low time <sup>2</sup>                                             | t <sub>mckl</sub>  | 30<br>14          | —                 | ns   | 256xFs<br>512xFs                         |

| MLBCLK high time                                                         | t <sub>mckh</sub>  | 30<br>14          | —                 | ns   | 256xFs<br>512xFs                         |

| MLBSIG/MLBDAT receiver<br>input valid to MLBCLK falling                  | t <sub>dsmcf</sub> | 1                 | —                 | ns   | _                                        |

| MLBSIG/MLBDAT receiver<br>input hold from MLBCLK low                     | t <sub>dhmcf</sub> | t <sub>mdzh</sub> | —                 | ns   | _                                        |

| MLBSIG/MLBDAT output high<br>impedance from MLBCLK low                   | t <sub>mcfdz</sub> | 0                 | t <sub>mckl</sub> | ns   | 3                                        |

| Bus Hold from MLBCLK low                                                 | t <sub>mdzh</sub>  | 4                 | —                 | ns   | _                                        |

| MLBSIG/MLBDAT output valid<br>from transition of MLBCLK (low<br>to high) | t <sub>delay</sub> |                   | 10                | ns   | _                                        |

#### Table 80. MLB 256/512 Fs Timing Parameters

<sup>1</sup> The controller can shut off MLBCLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLBCLK.

<sup>2</sup> MLBCLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLBDAT/MLBSIG line as soon as MLBCLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Ground = 0.0 V; load capacitance = 40 pF; MediaLB speed = 1024 Fs; Fs = 48 kHz; all timing parameters specified from the valid voltage threshold as listed in Table 81; unless otherwise noted.

| Parameter                                               | Symbol             | Min               | Max  | Unit | Comment                                    |

|---------------------------------------------------------|--------------------|-------------------|------|------|--------------------------------------------|

| MLBCLK Operating<br>Frequency <sup>1</sup>              | f <sub>mck</sub>   | 45.056            | 51.2 | MHz  | 1024xfs at 44.0 kHz<br>1024xfs at 50.0 kHz |

| MLBCLK rise time                                        | t <sub>mckr</sub>  | _                 | 1    | ns   | V <sub>IL</sub> TO V <sub>IH</sub>         |

| MLBCLK fall time                                        | t <sub>mckf</sub>  | _                 | 1    | ns   | V <sub>IH</sub> TO V <sub>IL</sub>         |

| MLBCLK low time                                         | t <sub>mckl</sub>  | 6.1               | —    | ns   | 2                                          |

| MLBCLK high time                                        | t <sub>mckh</sub>  | 9.3               | —    | ns   | _                                          |

| MLBSIG/MLBDAT receiver<br>input valid to MLBCLK falling | t <sub>dsmcf</sub> | 1                 | —    | ns   | _                                          |

| MLBSIG/MLBDAT receiver<br>input hold from MLBCLK low    | t <sub>dhmcf</sub> | t <sub>mdzh</sub> | _    | ns   | _                                          |

Table 81. MLB 1024 Fs Timing Parameters

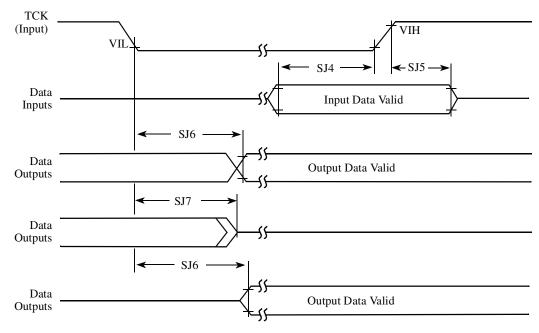

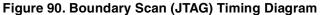

Figure 91. Test Access Port Timing Diagram

| Characteristics                                                                         | Symbol  | Timing Para | meter Range         | Unit |  |

|-----------------------------------------------------------------------------------------|---------|-------------|---------------------|------|--|

| Characteristics                                                                         | Symbol  | Min         | Max                 | Onn  |  |

| SPDIFIN Skew: asynchronous inputs, no specs apply                                       | _       | _           | 0.7                 | ns   |  |

| SPDIFOUT output (Load = 50pf)<br>• Skew<br>• Transition rising<br>• Transition falling  |         | <br>        | 1.5<br>24.2<br>31.3 | ns   |  |

| SPDIFOUT1 output (Load = 30pf)<br>• Skew<br>• Transition rising<br>• Transition falling |         | <br><br>    | 1.5<br>13.6<br>18.0 | ns   |  |

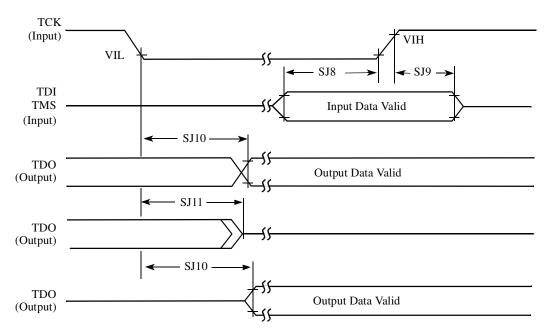

| Modulating Rx clock (SRCK) period                                                       | srckp   | 40.0        | _                   | ns   |  |

| SRCK high period                                                                        | srckph  | 16.0        | _                   | ns   |  |

| SRCK low period                                                                         | srckpl  | 16.0        |                     | ns   |  |

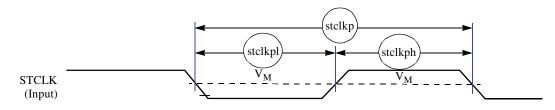

| Modulating Tx clock (STCLK) period                                                      | stclkp  | 40.0        | —                   | ns   |  |

| STCLK high period                                                                       | stclkph | 16.0        | _                   | ns   |  |

| STCLK low period                                                                        | stclkpl | 16.0        | —                   | ns   |  |

#### **Table 85. SPDIF Timing Parameters**

Figure 93. SRCK Timing Diagram

Figure 94. STCLK Timing Diagram

### 4.11.20.2.1 UART Transmitter

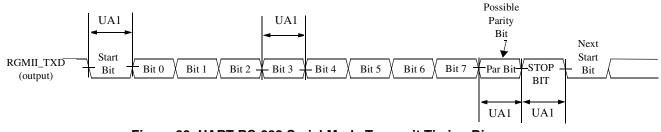

Figure 99 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 92 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 99. UART RS-232 Serial Mode Transmit Timing Diagram

| ID  | Parameter         | Symbol            | Min                                                    | Мах                                                | Unit |

|-----|-------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | 1/F <sub>baud_rate</sub> 1 -<br>T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> +<br>T <sub>ref_clk</sub> | —    |

Table 92. RS-232 Serial Mode Transmit Timing Parameters

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

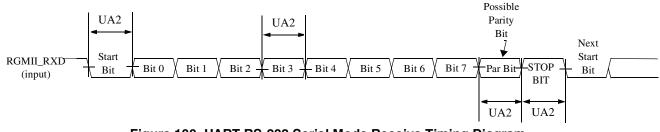

### 4.11.20.2.2 UART Receiver

Figure 100 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 93 lists serial mode receive timing characteristics.

Figure 100. UART RS-232 Serial Mode Receive Timing Diagram

#### Table 93. RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16<br>x F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 x F <sub>baud_rate</sub> ) | —    |

<sup>1</sup> The UART receiver can tolerate 1/(16 x F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16 x F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

# 6 Package Information and Contact Assignments

This section includes the contact assignment information and mechanical package drawing.

## 6.1 21x21 mm Package Information

## 6.1.1 Case 2240, 21 x 21 mm, 0.8 mm Pitch, 25 x 25 Ball Matrix

Figure 105 shows the top, bottom, and side views of the 21×21 mm BGA package.