#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u6avm08acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic                                 | Block Name                                | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------|-------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97 Interface                    | Connectivity<br>Peripherals   | The SSI is a full-duplex synchronous interface, which is<br>used on the AP to provide connectivity with off-chip<br>audio peripherals. The SSI supports a wide variety of<br>protocols (SSI normal, SSI network, I2S, and AC-97), bit<br>depths (up to 24 bits per word), and clock / frame sync<br>options.<br>The SSI has two pairs of 8x24 FIFOs and hardware<br>support for an external DMA controller in order to<br>minimize its impact on system performance. The<br>second pair of FIFOs provides hardware interleaving of<br>a second audio stream that reduces CPU overhead in<br>use cases where two time slots are being used<br>simultaneously. |

| TEMPMON                                        | Temperature Monitor                       | System Control<br>Peripherals | The Temperature sensor IP is used for detecting die<br>temperature. The temperature read out does not reflect<br>case or ambient temperature. It reflects the temperature<br>in proximity of the sensor location on the die.<br>Temperature distribution may not be uniformly<br>distributed, therefore the read out value may not be the<br>reflection of the temperature value of the entire die.                                                                                                                                                                                                                                                          |

| TZASC                                          | Trust-Zone Address<br>Space Controller    | Security                      | The TZASC (TZC-380 by ARM) provides security<br>address region control functions required for intended<br>application. It is used on the path to the DRAM<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                            | Connectivity<br>Peripherals   | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and the i.MX31 UART modules.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>                                             |

| USBOH3                                         | USB 2.0 High Speed<br>OTG and 3x HS Hosts | Connectivity<br>Peripherals   | <ul> <li>USBOH3 contains:</li> <li>One high-speed OTG module with integrated HS<br/>USB PHY</li> <li>One high-speed Host module with integrated HS<br/>USB PHY</li> <li>Two identical high-speed Host modules connected to<br/>HSIC USB ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDOA                                           | VDOA                                      | Multimedia<br>Peripherals     | Video Data Order Adapter (VDOA): used to re-order video data from the "tiled" order used by the VPU to the conventional raster-scan order needed by the IPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

# 3.1 Special Signal Considerations

Table 3 lists special signal considerations for the i.MX 6Solo/6DualLite processors. The signal names are listed in alphabetical order.

The package contact assignments can be found in Section 6, "Package Information and Contact Assignments." Signal descriptions are provided in the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)*.

| Signal Name                    | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK1_P/CLK1_N<br>CLK2_P/CLK2_N | <ul> <li>Two general purpose differential high speed clock Input/outputs are provided.</li> <li>Any or both of them could be used:</li> <li>To feed external reference clock to the PLLs and further to the modules inside SoC, for example as alternate reference clock for PCIe, Video/Audio interfaces, etc.</li> <li>To output internal SoC clock to be used outside the SoC as either reference clock or as a functional clock for peripherals, for example it could be used as an output of the PCIe master clock (root complex use)</li> <li>See the i.MX 6Solo/6DualLite reference manual for details on the respective clock trees.</li> <li>The clock inputs/outputs are LVDS differential pairs compatible with TIA/EIA-644 standard, the maximal frequency range supported is 0600 MHz.</li> <li>Alternatively one may use single ended signal to drive CLKx_P input. In this case corresponding CLKx_N input should be tied to the constant voltage level equal 1/2 of the input signal swing.</li> <li>Termination should be provided in case of high frequency signals.</li> <li>See LVDS pad electrical specification for further details.</li> <li>After initialization, the CLKx inputs/outputs could be disabled (if not used). If unused any or both of the CLKx_N/P pairs may be left floating.</li> </ul> |

| RTC_XTALI/RTC_XTALO            | If the user wishes to configure RTC_XTALI and RTC_XTALO as an RTC oscillator, a 32.768 kHz crystal, ( $\leq$ 100 k $\Omega$ ESR, 10 pF load) should be connected between RTC_XTALI and RTC_XTALO. Keep in mind the capacitors implemented on either side of the crystal are about twice the crystal load capacitor. To hit the exact oscillation frequency, the board capacitors need to be reduced to account for board and chip parasitics. The integrated oscillation amplifier is self biasing, but relatively weak. Care must be taken to limit parasitic leakage from RTC_XTALI and RTC_XTALO to either power or ground (>100 M $\Omega$ ). This will debias the amplifier and cause a reduction of startup margin. Typically RTC_XTALI and RTC_XTALO should bias to approximately 0.5 V. If it is desired to feed an external low frequency clock into RTC_XTALI the RTC_XTALO pin should be left floating or driven with a complimentary signal. The logic level of this forcing clock should not exceed VDD_SNVS_CAP level and the frequency should be <100 kHz under typical conditions. In case when high accuracy real time clock are not required system may use internal low frequency ring oscillator. It is recommended to connect RTC_XTALI to GND and keep RTC_XTALO floating.                                |

| XTALI/XTALO                    | A 24.0 MHz crystal should be connected between XTALI and XTALO. level and the frequency should be <32 MHz under typical conditions.<br>The crystal must be rated for a maximum drive level of 250 $\mu$ W. An ESR (equivalent series resistance) of typical 80 $\Omega$ is recommended. Freescale BSP (board support package) software requires 24 MHz on XTALI/XTALO.<br>The crystal can be eliminated if an external 24 MHz oscillator is available in the system. In this case, XTALI must be directly driven by the external oscillator and XTALO is floated. The XTALI signal level must swing from ~0.8 x NVCC_PLL_OUT to ~0.2 V.<br>If this clock is used as a reference for USB and PCIe, then there are strict frequency tolerance and jitter requirements. See OSC24M chapter and relevant interface specifications chapters for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Table 3. Special Signal Considerations

# 4.1.3 **Operating Ranges**

Table 9 provides the operating ranges of the i.MX 6Solo/6DualLite processors. For details on the chip's power structure, see the "Power Management Unit (PMU)" chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)*.

| Parameter<br>Description                         | Symbol                   | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment                                                                                                                                                  |

|--------------------------------------------------|--------------------------|----------------------|------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode: LDO<br>enabled                         | VDDARM_IN                | 1.275 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.150 V minimum for operation up to 792 MHz.                                                                         |

|                                                  |                          | 1.175 <sup>2</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDDARM_CAP) = 1.05<br>V minimum for operation up to 396 MHz.                                                                       |

|                                                  | VDDSOC_IN <sup>3</sup>   | 1.275 <sup>2,4</sup> | _    | 1.5              | V    | VPU = 328 MHz, VDDSOC and VDDPU LDO<br outputs (VDDSOC_CAP and VDDPU_CAP) =<br>1.225 V maximum and 1.15 V minimum.                                       |

| Run mode: LDO<br>bypassed                        | VDDARM_IN                | 1.150                | —    | 1.3              | V    | LDO bypassed for operation up to 792 MHz                                                                                                                 |

|                                                  |                          | 1.05                 | _    | 1.3              | V    | LDO bypassed for operation up to 396 MHz                                                                                                                 |

|                                                  | VDDSOC_IN <sup>3</sup>   | 1.15 <sup>4</sup>    | —    | 1.225            | V    | LDO bypassed for operation VPU = 328 MHz</td                                                                                                             |

| Standby/DSM mode                                 | VDDARM_IN                | 0.9                  | —    | 1.3              | V    | Refer to Table 13, "Stop Mode Current and Power Consumption," on page 29.                                                                                |

|                                                  | VDDSOC_IN                | 0.9                  | —    | 1.225            | V    |                                                                                                                                                          |

| VDDHIGH internal<br>regulator                    | VDDHIGH_IN               | 2.8                  | —    | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                                           |

| Backup battery supply range                      | VDD_SNVS_IN <sup>5</sup> | 2.9                  | _    | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state.                      |

| USB supply voltages                              | USB_OTG_VBUS             | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

|                                                  | USB_H1_VBUS              | 4.4                  | —    | 5.25             | V    |                                                                                                                                                          |

| DDR I/O supply voltage                           | NVCC_DRAM                | 1.14                 | 1.2  | 1.3              | V    | LPDDR2, DDR3-U                                                                                                                                           |

|                                                  |                          | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                     |

|                                                  |                          | 1.283                | 1.35 | 1.45             | V    | DDR3_L                                                                                                                                                   |

| Supply for RGMII I/O<br>power group <sup>6</sup> | NVCC_RGMII               | 1.15                 |      | 2.625            | V    | 1.15 V – 1.30 V in HSIC 1.2 V mode<br>1.43 V – 1.58 V in RMGII 1.5 V mode<br>1.70 V – 1.90 V in RMGII 1.8 V mode<br>2.25 V – 2.625 V in RMGII 2.5 V mode |

| Parameter<br>Description          | Symbol                                                                                                                             | Min   | Тур                 | Max <sup>1</sup> | Unit | Comment                                               |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|------------------|------|-------------------------------------------------------|

| GPIO supply voltages <sup>6</sup> | NVCC_CSI,<br>NVCC_EIM,<br>NVCC_ENET,<br>NVCC_GPIO,<br>NVCC_LCD,<br>NVCC_NANDF,<br>NVCC_SD1,<br>NVCC_SD2,<br>NVCC_SD3,<br>NVCC_JTAG | 1.65  | 1.8,<br>2.8,<br>3.3 | 3.6              | V    |                                                       |

|                                   | NVCC_LVDS2P5 <sup>7</sup><br>NVCC_MIPI                                                                                             | 2.25  | 2.5                 | 2.75             | V    |                                                       |

| HDMI supply voltages              | HDMI_VP                                                                                                                            | 0.99  | 1.1                 | 1.3              | V    |                                                       |

|                                   | HDMI_VPH                                                                                                                           | 2.25  | 2.5                 | 2.75             | V    |                                                       |

| PCIe supply voltages              | PCIE_VP                                                                                                                            | 1.023 | 1.1                 | 1.225            | V    |                                                       |

|                                   | PCIE_VPH                                                                                                                           | 2.325 | 2.5                 | 2.75             | V    |                                                       |

|                                   | PCIE_VPTX                                                                                                                          | 1.023 | 1.1                 | 1.225            | V    |                                                       |

| Junction temperature              | T<br>J                                                                                                                             | -40   | —                   | 125              | °C   | Refer to Automotive qualification report for details. |

### Table 9. Operating Ranges (continued)

<sup>1</sup> Applying the maximum voltage results in maximum power consumption and heat generation. Freescale recommends a voltage set point = (Vmin + the supply tolerance). This results in an optimized power/speed ratio.

<sup>2</sup> VDDARM\_IN and VDDSOC\_IN must be 125 mV higher than the LDO Output Set Point for correct regulator supply voltage.

<sup>3</sup> VDDSOC\_CAP and VDDPU\_CAP must be equal.

<sup>4</sup> VDDSOC and VDDPU output voltage must be set to this rule: VDDARM - VDDSOC/PU < 100 mV.

<sup>5</sup> While setting VDD\_SNVS\_IN voltage with respect to Charging Currents and RTC, refer to Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>6</sup> All digital I/O supplies (NVCC\_xxxx) must be powered under normal conditions whether the associated I/O pins are in use or not and associated IO pins need to have a Pullup or Pulldown resistor applied to limit any floating gate current.

<sup>7</sup> This supply also powers the pre-drivers of the DDR IO pins, hence, it must be always provided, even when LVDS is not used

Table 10 shows on-chip LDO regulators that can supply on-chip loads.

Table 10. On-Chip LDOs<sup>1</sup> and their On-Chip Loads

| Voltage Source | Load         | Comment                               |

|----------------|--------------|---------------------------------------|

| VDDHIGH_CAP    | NVCC_LVDS2P5 | Board-level connection to VDDHIGH_CAP |

|                | NVCC_MIPI    |                                       |

|                | HDMI_VPH     |                                       |

|                | PCIE_VPH     |                                       |

| Voltage Source | Load      | Comment                                             |

|----------------|-----------|-----------------------------------------------------|

| VDDSOC_CAP     | HDMI_VP   | Board-level connection to VDDSOC_CAP <sup>2 3</sup> |

|                | PCIE_VP   |                                                     |

|                | PCIE_VPTX |                                                     |

Table 10. On-Chip LDOs<sup>1</sup> and their On-Chip Loads (continued)

<sup>1</sup> On-chip LDOs are designed to supply i.MX6 loads and must not be used to supply external loads.

<sup>2</sup> VDDARM\_CAP should not exceed VDDSOC\_CAP by more than 50 mV.

<sup>3</sup> There is no requirement for VDDSOC\_CAP to track within 50 mV as long as it is greater than VDDARM\_CAP.

# 4.1.4 External Clock Sources

Each i.MX 6Solo/6DualLite processor has two external input system clocks: a low frequency (CKIL) and a high frequency (XTAL).

The CKIL is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watch-dog counters. The clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier. Additionally, there is an internal ring oscillator, which can substitute the CKIL, in case accuracy is not important.

The system clock input XTAL is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either external oscillator or a crystal using internal oscillator amplifier.

Table 11 shows the interface frequency requirements.

| Parameter Description          | Symbol            | Min | Тур                       | Max | Unit |

|--------------------------------|-------------------|-----|---------------------------|-----|------|

| CKIL Oscillator <sup>1,2</sup> | f <sub>ckil</sub> | —   | 32.768 <sup>3</sup> /32.0 | —   | kHz  |

| XTAL Oscillator <sup>2,4</sup> | f <sub>xtal</sub> |     | 24                        |     | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

# 4.5 On-Chip Oscillators

# 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDDHIGH\_IN such as the oscillator consumes power from VDDHIGH\_IN when that supply is available and transitions to the back up battery when VDDHIGH\_IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 K will automatically switch to a crude internal ring oscillator. The frequency range of this block is approximately 10–45 kHz. It highly depends on the process, voltage, and temperature.

The OSC32k runs from VDD\_SNVS\_CAP supply, which comes from the

VDDHIGH\_IN/VDD\_SNVS\_IN. The target battery is a ~3 V coin cell. Proper choice of coin cell type is necessary for chosen VDDHIGH\_IN range. Appropriate series resistor (Rs) must be used when connecting the coin cell. Rs depends on the charge current limit that depends on the chosen coin cell. For example, for Panasonic ML621:

- Average Discharge Voltage is 2.5 V

- Maximum Charge Current is 0.6 mA

For a charge voltage of 3.2 V, Rs = (3.2-2.5)/0.6 m = 1.17 k

|                        | Min | Тур        | Мах | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-----|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fosc                   |     | 32.768 KHz |     | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                                                                                                             |

| Current<br>consumption |     | 4 μΑ       |     | The 4 $\mu$ A is the consumption of the oscillator alone (OSC32k). Total supply consumption will depend on what the digital portion of the RTC consumes. The ring oscillator consumes 1 $\mu$ A when ring oscillator is inactive, 20 $\mu$ A when the ring oscillator is running. Another 1.5 $\mu$ A is drawn from vdd_rtc in the power_detect block. So, the total current is 6.5 $\mu$ A on vdd_rtc when the ring oscillator is not running. |

### Table 23. OSC32K Main Characteristics

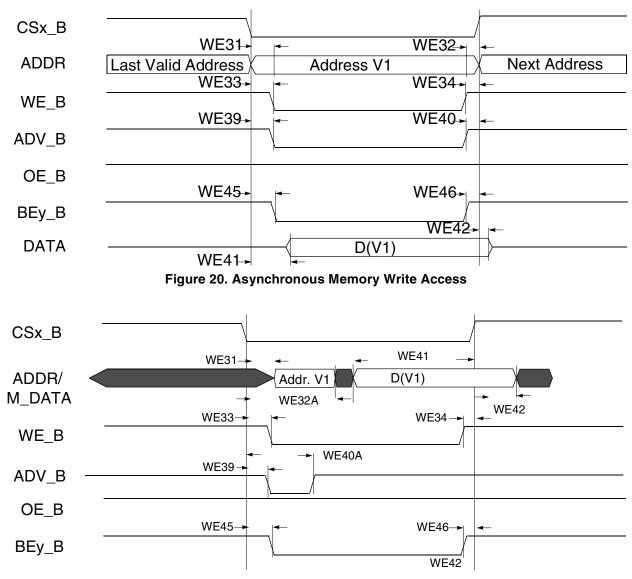

| Reference Manual EIM Chapter<br>Nomenclature | Data Sheet Nomenclature, Reference Manual External Signals and Pin<br>Multiplexing Chapter, and IOMUXC Controller Chapter Nomenclature |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADV_B                                        | EIM_LBA                                                                                                                                |  |  |  |

| ADDR                                         | EIM_A[25:16], EIM_DA[15:0]                                                                                                             |  |  |  |

| ADDR/M_DATA                                  | EIM_DAx (Addr/Data muxed mode)                                                                                                         |  |  |  |

| DATA                                         | EIM_NFC_D (Data bus shared with NAND Flash)<br>EIM_Dx (dedicated data bus)                                                             |  |  |  |

| WAIT_B                                       | EIM_WAIT                                                                                                                               |  |  |  |

#### Table 41. EIM Signal Cross Reference (continued)

### 4.9.3.2 EIM Interface Pads Allocation

EIM supports 32-bit, 16-bit and 8-bit devices operating in address/data separate or multiplexed modes. Table 42 provides EIM interface pads allocation in different modes.

|           | Non Multiplexed Address/Data Mode |           |           |           |               |           | Multiplexed Address/Data mode |           |              |

|-----------|-----------------------------------|-----------|-----------|-----------|---------------|-----------|-------------------------------|-----------|--------------|

| Setup     |                                   | 8 E       | Bit       |           | 16 Bit 32 Bit |           | 32 Bit                        | 16 Bit    | 32 Bit       |

|           | MUM = 0,                          | MUM = 0,  | MUM = 0,  | MUM = 0,  | MUM = 0,      | MUM = 0,  | MUM = 0,                      | MUM = 1,  | MUM = 1,     |

|           | DSZ = 100                         | DSZ = 101 | DSZ = 110 | DSZ = 111 | DSZ = 001     | DSZ = 010 | DSZ = 011                     | DSZ = 001 | DSZ = 011    |

| A[15:0]   | WEIM_DA_A                         | WEIM_DA_A | WEIM_DA_A | WEIM_DA_A | WEIM_DA_A     | WEIM_DA_A | WEIM_DA_A                     | WEIM_DA_A | WEIM_DA_A    |

|           | [15:0]                            | [15:0]    | [15:0]    | [15:0]    | [15:0]        | [15:0]    | [15:0]                        | [15:0]    | [15:0]       |

| A[25:16]  | WEIM_A                            | WEIM_A    | WEIM_A    | WEIM_A    | WEIM_A        | WEIM_A    | WEIM_A                        | WEIM_A    | WEIM_D       |

|           | [25:16]                           | [25:16]   | [25:16]   | [25:16]   | [25:16]       | [25:16]   | [25:16]                       | [25:16]   | [9:0]        |

| D[7:0],   | WEIM_D                            | _         |           | —         | WEIM_D        | _         | WEIM_D                        | WEIM_DA_A | WEIM_DA_A    |

| EIM_EB0   | [7:0]                             |           |           |           | [7:0]         |           | [7:0]                         | [7:0]     | [7:0]        |

| D[15:8],  | —                                 | WEIM_D    |           | —         | WEIM_D        | _         | WEIM_D                        | WEIM_DA_A | WEIM_DA_A    |

| EIM_EB1   |                                   | [15:8]    |           |           | [15:8]        |           | [15:8]                        | [15:8]    | [15:8]       |

| D[23:16], | —                                 | _         | WEIM_D    | —         |               | WEIM_D    | EIM_D                         | _         | WEIM_D [7:0] |

| EIM_EB2   |                                   |           | [24:16]   |           |               | [23:16]   | [23:16]                       |           |              |

| D[31:24], | —                                 | —         |           | WEIM_D    |               | WEIM_D    | EIM_D                         | —         | WEIM_D       |

| EIM_EB3   |                                   |           |           | [31:24]   |               | [31:24]   | [31:24]                       |           | [15:8]       |

Table 42. EIM Internal Module Multiplexing<sup>1</sup>

<sup>1</sup> For more information on configuration ports mentioned in this table, see the i.MX 6Solo/6DualLite reference manual.

Figure 21. Asynchronous A/D Muxed Write Access

**Electrical Characteristics**

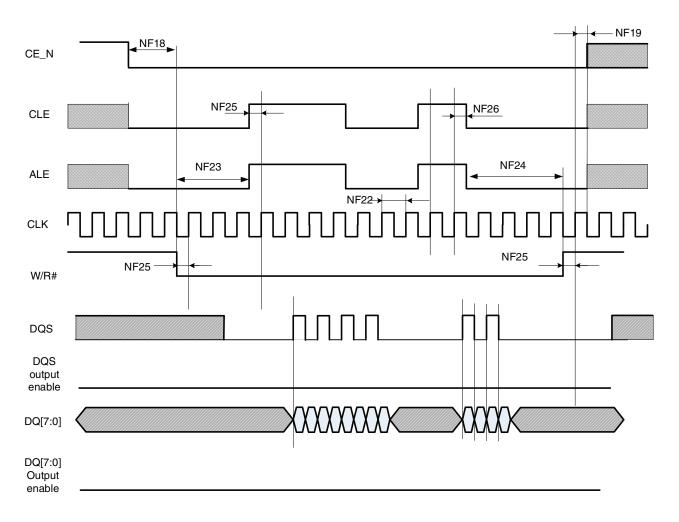

Figure 36. Source Synchronous Mode Data Read Timing Diagram

| ID   | Parameter                                      | Symbol | Tim<br>T = GPMI C | -    | Unit |

|------|------------------------------------------------|--------|-------------------|------|------|

|      |                                                |        | Min.              | Max. |      |

| NF18 | CE# access time                                | tCE    | CE_DELAY x tCK    | —    | ns   |

| NF19 | CE# hold time                                  | tCH    | 0.5 x tCK         | —    | ns   |

| NF20 | Command/address DQ setup time                  | tCAS   | 0.5 x tCK         | —    | ns   |

| NF21 | Command/address DQ<br>hold time                | tCAH   | 0.5 x tCK         | _    | ns   |

| NF22 | clock period                                   | tCK    | 5                 |      | ns   |

| NF23 | preamble delay                                 | tPRE   | PRE_DELAY x tCK   | —    | ns   |

| NF24 | postamble delay                                | tPOST  | POST_DELAY x tCK  | —    | ns   |

| NF25 | CLE and ALE setup time                         | tCALS  | 0.5 x tCK         | —    | ns   |

| NF26 | CLE and ALE hold time                          | tCALH  | 0.5 x tCK         | —    | ns   |

| NF27 | Data input to first DQS<br>latching transition | tDQSS  | tCK               |      | ns   |

Table 52. Source Synchronous Mode Timing Parameters<sup>1</sup>

<sup>1</sup> GPMI's Sync Mode output timing could be controlled by module's internal registers, say

${\sf HW\_GPMI\_TIMING2\_CE\_DELAY,\, HW\_GPMI\_TIMING\_PREAMBLE\_DELAY,\, and}$

HW\_GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers' settings. In the above table, we use CE\_DELAY/PRE\_DELAY/POST\_DELAY to represent each of these settings.

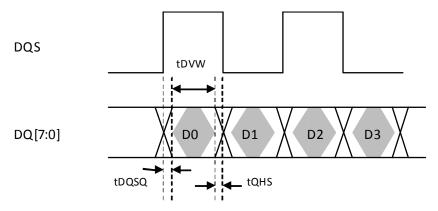

For DDR Source sync mode, Figure 37 shows the timing diagram of DQS/DQ read valid window. The typical value of tDQSQ is 0.85ns (max) and 1ns (max) for tQHS at 200MB/s. GPMI will sample DQ[7:0] at both rising and falling edge of an delayed DQS signal, which can be provided by an internal DPLL. The delay value can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET(see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value of this register is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

# 4.10.3 Samsung Toggle Mode AC Timing

### 4.10.3.1 Command and Address Timing

NOTE

Samsung Toggle Mode command and address timing is the same as ONFI 1.0 compatible Async mode AC timing. See Section 4.10.1, "Asynchronous Mode AC Timing (ONFI 1.0 Compatible)," for details.

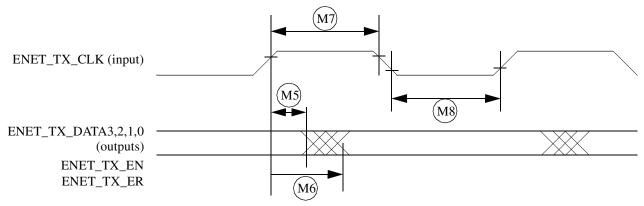

Figure 48 shows MII transmit signal timings. Table 61 describes the timing parameters (M5–M8) shown in the figure.

Figure 48. MII Transmit Signal Timing Diagram

Table 61. MII Transmit Signal Timing

| ID | Characteristic <sup>1</sup>                                           | Min. | Max. | Unit               |

|----|-----------------------------------------------------------------------|------|------|--------------------|

| M5 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER invalid | 5    | _    | ns                 |

| M6 | ENET_TX_CLK to ENET_TX_DATA3,2,1,0, ENET_TX_EN,<br>ENET_TX_ER valid   | —    | 20   | ns                 |

| M7 | ENET_TX_CLK pulse width high                                          | 35%  | 65%  | ENET_TX_CLK period |

| M8 | ENET_TX_CLK pulse width low                                           | 35%  | 65%  | ENET_TX_CLK period |

<sup>1</sup> ENET\_TX\_EN, ENET\_TX\_CLK, and ENET0\_TXD0 have the same timing in 10-Mbps 7-wire interface mode.

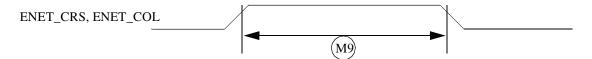

### 4.11.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 49 shows MII asynchronous input timings. Table 62 describes the timing parameter (M9) shown in the figure.

Figure 49. MII Async Inputs Timing Diagram

| Table 62 | MII | Asynchronous | Inputs | Signal Ti | ming |

|----------|-----|--------------|--------|-----------|------|

|----------|-----|--------------|--------|-----------|------|

| ID              | Characteristic                           | Min. | Max. | Unit               |

|-----------------|------------------------------------------|------|------|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5  | _    | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

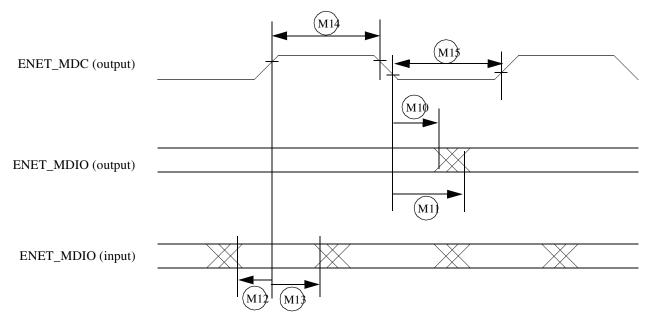

### 4.11.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 50 shows MII asynchronous input timings. Table 63 describes the timing parameters (M10–M15) shown in the figure.

Figure 50. MII Serial Management Channel Timing Diagram

| Table 63. MII Serial Management Ch | hannel Timing |

|------------------------------------|---------------|

|------------------------------------|---------------|

| ID  | Characteristic                                                             | Min. | Max. | Unit            |

|-----|----------------------------------------------------------------------------|------|------|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (min. propagation delay) | 0    | —    | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (max. propagation delay)   | _    | 5    | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                            | 18   | —    | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                             | 0    | —    | ns              |

| M14 | ENET_MDC pulse width high                                                  | 40%  | 60%  | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                   | 40%  | 60%  | ENET_MDC period |

### 4.11.5.2 RMII Mode Timing

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz ± 50 ppm continuous reference clock. ENET\_RX\_EN is used as the CRS\_DV in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET0\_RXD[1:0] and ENET\_RX\_ER.

| ID   | Parameter                                           | Standa | ard Mode | Fast Mode          |     | Unit |

|------|-----------------------------------------------------|--------|----------|--------------------|-----|------|

|      |                                                     | Min    | Мах      | Min                | Max |      |

| IC8  | Data set-up time                                    | 250    | _        | 100 <sup>3</sup>   | —   | ns   |

| IC9  | Bus free time between a STOP and START condition    | 4.7    | _        | 1.3                | —   | μs   |

| IC10 | Rise time of both I2DAT and I2CLK signals           | _      | 1000     | $20 + 0.1 C_b^{4}$ | 300 | ns   |

| IC11 | Fall time of both I2DAT and I2CLK signals           | _      | 300      | $20 + 0.1 C_b^{4}$ | 300 | ns   |

| IC12 | Capacitive load for each bus line (C <sub>b</sub> ) | —      | 400      | —                  | 400 | pF   |

### Table 68. I<sup>2</sup>C Module Timing Parameters (continued)

<sup>1</sup> A device must internally provide a hold time of at least 300 ns for I2DAT signal in order to bridge the undefined region of the falling edge of I2CLK.

<sup>2</sup> The maximum hold time has only to be met if the device does not stretch the LOW period (ID no IC5) of the I2CLK signal.

<sup>3</sup> A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement of Set-up time (ID No IC7) of 250 ns must be met. This automatically is the case if the device does not stretch the LOW period of the I2CLK signal. If such a device does stretch the LOW period of the I2CLK signal, it must output the next data bit to the I2DAT line max\_rise\_time (IC9) + data\_setup\_time (IC7) = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the I2CLK line is released.

<sup>4</sup>  $C_{b}$  = total capacitance of one bus line in pF.

# 4.11.10 Image Processing Unit (IPU) Module Parameters

The purpose of the IPU is to provide comprehensive support for the flow of data from an image sensor and/or to a display device. This support covers all aspects of these activities:

- Connectivity to relevant devices—cameras, displays, graphics accelerators, and TV encoders.

- Related image processing and manipulation: sensor image signal processing, display processing, image conversions, and other related functions.

- Synchronization and control capabilities, such as avoidance of tearing artifacts.

## 4.11.10.3 Electrical Characteristics

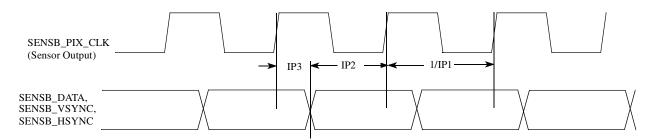

Figure 66 depicts the sensor interface timing. SENSB\_MCLK signal described here is not generated by the IPU. Table 70 lists the sensor interface timing characteristics.

Figure 66. Sensor Interface Timing Diagram

### Table 70. Sensor Interface Timing Characteristics

| ID  | Parameter                             | Symbol | Min  | Мах | Unit |

|-----|---------------------------------------|--------|------|-----|------|

| IP1 | Sensor output (pixel) clock frequency | Fpck   | 0.01 | 180 | MHz  |

| IP2 | Data and control setup time           | Tsu    | 2    | —   | ns   |

| IP3 | Data and control holdup time          | Thd    | 1    | —   | ns   |

### 4.11.10.4 IPU Display Interface Signal Mapping

The IPU supports a number of display output video formats. Table 71 defines the mapping of the Display Interface Pins used during various supported video interface formats.

# NOTE

Table 71 provides information for both the Disp0 and Disp1 ports. However, Disp1 port has reduced pinout depending on IOMUXC configuration and therefore may not support all the above configurations. See the IOMUXC table for details.

# 4.11.10.5 IPU Display Interface Timing

The IPU Display Interface supports two kinds of display accesses: synchronous and asynchronous. There are two groups of external interface pins to provide synchronous and asynchronous controls accordantly.

## 4.11.10.5.1 Synchronous Controls

The synchronous control changes its value as a function of a system or of an external clock. This control has a permanent period and a permanent wave form.

There are special physical outputs to provide synchronous controls:

- The ipp\_disp\_clk is a dedicated base synchronous signal that is used to generate a base display (component, pixel) clock for a display.

- The ipp\_pin\_1- ipp\_pin\_7 are general purpose synchronous pins, that can be used to provide HSYNC, VSYNC, DRDY or any else independent signal to a display.

The IPU has a system of internal binding counters for internal events (such as, HSYNC/VSYCN) calculation. The internal event (local start point) is synchronized with internal DI\_CLK. A suitable control starts from the local start point with predefined UP and DOWN values to calculate control's changing points with half DI\_CLK resolution. A full description of the counters system can be found in the IPU chapter of the *i.MX* 6Solo/6DualLite Reference Manual (IMX6SDLRM).

### 4.11.10.5.2 Asynchronous Controls

The asynchronous control is a data-oriented signal that changes its value with an output data according to additional internal flags coming with the data.

There are special physical outputs to provide asynchronous controls, as follows:

- The ipp\_d0\_cs and ipp\_d1\_cs pins are dedicated to provide chip select signals to two displays.

- The ipp\_pin\_11- ipp\_pin\_17 are general purpose asynchronous pins, that can be used to provide WR. RD, RS or any other data oriented signal to display.

### NOTE

The IPU has independent signal generators for asynchronous signals toggling. When a DI decides to put a new asynchronous data in the bus, a new internal start (local start point) is generated. The signals generators calculate predefined UP and DOWN values to change pins states with half DI\_CLK resolution.

| ID    | Parameter              | Symbol | Value                       | Description                                                                                                                                                                                                                             | Unit |

|-------|------------------------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5o  | Offset of IPP_DISP_CLK | Todicp | DISP_CLK_OFFSET<br>× Tdiclk | DISP_CLK_OFFSET—offset of<br>IPP_DISP_CLK edges from local start<br>point, in DI_CLK×2<br>(0.5 DI_CLK Resolution).<br>Defined by DISP_CLK counter                                                                                       | ns   |

| IP13o | Offset of VSYNC        | Tovs   | VSYNC_OFFSET<br>X Tdiclk    | VSYNC_OFFSET—offset of Vsync edges<br>from a local start point, when a Vsync<br>should be active, in DI_CLK×2<br>(0.5 DI_CLK Resolution). The<br>VSYNC_OFFSET should be built by<br>suitable DI's counter.                              | ns   |

| IP8o  | Offset of HSYNC        | Tohs   | HSYNC_OFFSET<br>X Tdiclk    | HSYNC_OFFSET—offset of Hsync edges<br>from a local start point, when a Hsync<br>should be active, in DI_CLK×2<br>(0.5 DI_CLK Resolution). The<br>HSYNC_OFFSET should be built by<br>suitable DI's counter.                              | ns   |

| IP9o  | Offset of DRDY         | Todrdy | DRDY_OFFSET<br>X Tdiclk     | DRDY_OFFSET—offset of DRDY edges<br>from a suitable local start point, when a<br>corresponding data has been set on the<br>bus, in DI_CLK×2<br>(0.5 DI_CLK Resolution).<br>The DRDY_OFFSET should be built by<br>suitable DI's counter. | ns   |

### Table 72. Synchronous Display Interface Timing Characteristics (Pixel Level) (continued)

Display interface clock period immediate value.

$$Tdicp = \begin{cases} T_{diclk} \times \frac{DISP\_CLK\_PERIOD}{DI\_CLK\_PERIOD}, & for integer \frac{DISP\_CLK\_PERIOD}{DI\_CLK\_PERIOD} \\ T_{diclk} (floor[\frac{DISP\_CLK\_PERIOD}{DI\_CLK\_PERIOD}] + 0.5 \pm 0.5), & for fractional \frac{DISP\_CLK\_PERIOD}{DI\_CLK\_PERIOD} \end{cases}$$

DISP\_CLK\_PERIOD—number of DI\_CLK per one Tdicp. Resolution 1/16 of DI\_CLK. DI\_CLK\_PERIOD—relation of between programing clock frequency and current system clock frequency Display interface clock period average value.

$$\overline{T}dicp = T_{diclk} \times \frac{DISP_CLK_PERIOD}{DI_CLK_PERIOD}$$

<sup>2</sup> DI's counter can define offset, period and UP/DOWN characteristic of output signal according to programed parameters of the counter. Same of parameters in the table are not defined by DI's registers directly (by name), but can be generated by corresponding DI's counter. The SCREEN\_WIDTH is an input value for DI's HSYNC generation counter. The distance between HSYNCs is a SCREEN\_WIDTH.

The maximal accuracy of UP/DOWN edge of controls is:

Accuracy =  $(0.5 \times T_{diclk}) \pm 0.62$  ns

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 1

1

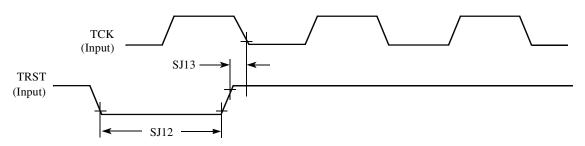

### Figure 92. TRST Timing Diagram

| Table | 84. | JTAG | Timing |

|-------|-----|------|--------|

|-------|-----|------|--------|

| ID   | Parameter <sup>1,2</sup>                                       | All Freq | uencies | Unit |

|------|----------------------------------------------------------------|----------|---------|------|

|      | Farameter                                                      | Min      | Мах     | Onit |

| SJ0  | TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22      | MHz  |

| SJ1  | TCK cycle time in crystal mode                                 | 45       | —       | ns   |

| SJ2  | TCK clock pulse width measured at $V_M^2$                      | 22.5     | _       | ns   |

| SJ3  | TCK rise and fall times                                        | —        | 3       | ns   |

| SJ4  | Boundary scan input data set-up time                           | 5        | —       | ns   |

| SJ5  | Boundary scan input data hold time                             | 24       | —       | ns   |

| SJ6  | TCK low to output data valid                                   | —        | 40      | ns   |

| SJ7  | TCK low to output high impedance                               | —        | 40      | ns   |

| SJ8  | TMS, TDI data set-up time                                      | 5        | —       | ns   |

| SJ9  | TMS, TDI data hold time                                        | 25       | —       | ns   |

| SJ10 | TCK low to TDO data valid                                      | —        | 44      | ns   |

| SJ11 | TCK low to TDO high impedance                                  | —        | 44      | ns   |

| SJ12 | TRST assert time                                               | 100      | —       | ns   |

| SJ13 | TRST set-up time to TCK low                                    | 40       | —       | ns   |

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{M}$  = mid-point voltage

# 4.11.18 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 85 and Figure 93 and Figure 94 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SRCK) for SPDIF in Rx mode and the timing of the modulating Tx clock (STCLK) for SPDIF in Tx mode.

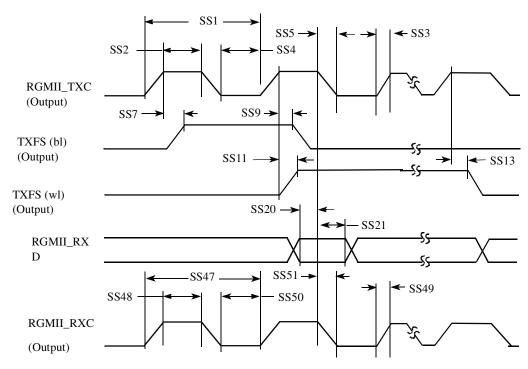

## 4.11.19.2 SSI Receiver Timing with Internal Clock

Figure 96 depicts the SSI receiver internal clock timing and Table 88 lists the timing parameters for the receiver timing with the internal clock.

Figure 96. SSI Receiver Internal Clock Timing Diagram

| Table 88. SSI Receiver Ti | ming with Internal Clock |

|---------------------------|--------------------------|

|---------------------------|--------------------------|

| ID                           | Parameter                          | Min  | Мах  | Unit |  |  |

|------------------------------|------------------------------------|------|------|------|--|--|

|                              | Internal Clock Operation           |      |      |      |  |  |

| SS1                          | (Tx/Rx) CK clock period            | 81.4 | _    | ns   |  |  |

| SS2                          | (Tx/Rx) CK clock high period       | 36.0 | _    | ns   |  |  |

| SS3                          | (Tx/Rx) CK clock rise time         | —    | 6.0  | ns   |  |  |

| SS4                          | (Tx/Rx) CK clock low period        | 36.0 | _    | ns   |  |  |

| SS5                          | (Tx/Rx) CK clock fall time         | —    | 6.0  | ns   |  |  |

| SS7                          | (Rx) CK high to FS (bl) high       | —    | 15.0 | ns   |  |  |

| SS9                          | (Rx) CK high to FS (bl) low        | —    | 15.0 | ns   |  |  |

| SS11                         | (Rx) CK high to FS (wl) high       | —    | 15.0 | ns   |  |  |

| SS13                         | (Rx) CK high to FS (wl) low        | —    | 15.0 | ns   |  |  |

| SS20                         | SRXD setup time before (Rx) CK low | 10.0 | _    | ns   |  |  |

| SS21                         | SRXD hold time after (Rx) CK low   | 0.0  | _    | ns   |  |  |

| Oversampling Clock Operation |                                    |      |      |      |  |  |

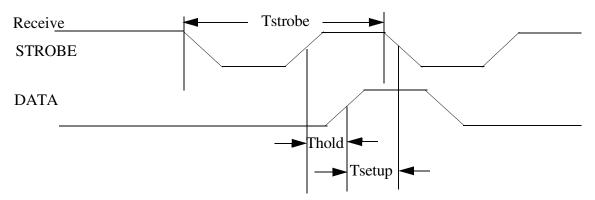

# 4.11.21.2 Receive Timing

Figure 104. USB HSIC Receive Waveform

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |

|---------|---------------------------------|-------|-------|------|--------------------------------|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |

<sup>1</sup> The timings in the table are guaranteed when:

-AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

# 4.11.22 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host with the amendments below (On-The-Go and Embedded Host Supplement to the USB Revision 2.0 Specification is not applicable to Host port).

- USB ENGINEERING CHANGE NOTICE

- Title: 5V Short Circuit Withstand Requirement Change

- Applies to: Universal Serial Bus Specification, Revision 2.0

- Errata for USB Revision 2.0 April 27, 2000 as of 12/7/2000

- USB ENGINEERING CHANGE NOTICE

- Title: Pull-up/Pull-down resistors

- Applies to: Universal Serial Bus Specification, Revision 2.0

- USB ENGINEERING CHANGE NOTICE

- Title: Suspend Current Limit Changes

- Applies to: Universal Serial Bus Specification, Revision 2.0

| Supply Rail Name | Ball(s) Position(s)                                                               | Remark                                                                                                                        |

|------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PCIE_REXT        | A2                                                                                |                                                                                                                               |

| PCIE_VP          | Н7                                                                                |                                                                                                                               |

| PCIE_VPH         | G7                                                                                | PCI PHY supply                                                                                                                |

| PCIE_VPTX        | G8                                                                                | PCI PHY supply                                                                                                                |

| VDD_SNVS_CAP     | G9                                                                                | Secondary supply for the SNVS (internal regulator output—requires capacitor if internal regulator is used)                    |

| VDD_SNVS_IN      | G11                                                                               | Primary supply for the SNVS regulator                                                                                         |

| VDDARM_CAP       | H11, H13, J11, J13, K11, K13, L11, L13, M11, M13,<br>N11, N13, P11, P13, R11, R13 | Secondary supply for core (internal regulator output—requires capacitor if internal regulator is used)                        |

| VDDARM_IN        | H14, J14, K9, K14, L9, L14, M9, M14, N9, N14, P9, P14, R9, R14, T9, U9            | Primary supply for the ARM core's regulator                                                                                   |

| VDDHIGH_CAP      | H10, J10                                                                          | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires capacitor<br>if internal regulator is used)      |

| VDDHIGH_IN       | H9, J9                                                                            | Primary supply for the 2.5 V regulator                                                                                        |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                                                 | Secondary supply for VPU and GPUs<br>(internal regulator output—requires capacitor<br>if internal regulator is used)          |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                                                 | Secondary supply for SoC and PU regulators<br>(internal regulator output—requires capacitor<br>if internal regulator is used) |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16                                  | Primary supply for SoC and PU regulators                                                                                      |

| VDDUSB_CAP       | F9                                                                                | Secondary supply for the 3 V Domain (internal regulator output—requires capacitor if internal regulator is used)              |

| USB_H1_VBUS      | D10                                                                               | Primary supply for the 3 V regulator                                                                                          |

| USB_OTG_VBUS     | E9                                                                                | Primary supply for the 3 V regulator                                                                                          |

| HDMI_DDCCEC      | K2                                                                                | Analog Ground(Ground reference for the Hot Plug Detect signal)                                                                |

| FA_ANA           | A5                                                                                |                                                                                                                               |

| GPANAIO          | C8                                                                                |                                                                                                                               |

| VDD_FA           | B5                                                                                |                                                                                                                               |

| ZQPAD            | AE17                                                                              |                                                                                                                               |

| NC               | C14                                                                               |                                                                                                                               |

| NC               | G12                                                                               |                                                                                                                               |

| Table 100. 21 x 21 mm | <b>Supplies Contact</b> | Assignments | (continued) |

|-----------------------|-------------------------|-------------|-------------|

|-----------------------|-------------------------|-------------|-------------|