Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M3Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, Cap Sense, DMA, I²S, POR, PWM, WDTNumber of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12bOscillator TypeInternal |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, Cap Sense, DMA, I²S, POR, PWM, WDTNumber of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                         |

| Speed32MHzConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, Cap Sense, DMA, I²S, POR, PWM, WDTNumber of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                    |

| ConnectivityI²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, Cap Sense, DMA, I²S, POR, PWM, WDTNumber of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                              |

| PeripheralsBrown-out Detect/Reset, Cap Sense, DMA, I2S, POR, PWM, WDTNumber of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                 |

| Number of I/O37Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                      |

| Program Memory Size32KB (32K x 8)Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                     |

| Program Memory TypeFLASHEEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                                                      |

| EEPROM Size4K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                              |

| RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                               |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                                              |

| Data ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Oscillator Type Internal                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                                                                                                                                                                                                                                                |

| Mounting Type Surface Mount                                                                                                                                                                                                                                                                                                                                                                                            |

| Package / Case 48-LQFP                                                                                                                                                                                                                                                                                                                                                                                                 |

| Supplier Device Package48-LQFP (7x7)                                                                                                                                                                                                                                                                                                                                                                                   |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151c6t6atr                                                                                                                                                                                                                                                                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 48. | I <sup>2</sup> C characteristics                                               | 89 |

|-----------|--------------------------------------------------------------------------------|----|

| Table 49. | SCL frequency (f <sub>PCLK1</sub> = 32 MHz, V <sub>DD</sub> = VDD_I2C = 3.3 V) | 90 |

| Table 50. | SPI characteristics                                                            |    |

| Table 51. | USB startup time                                                               |    |

| Table 52. | USB DC electrical characteristics                                              |    |

| Table 53. | USB: full speed electrical characteristics                                     |    |

| Table 54. | ADC clock frequency                                                            |    |

| Table 55. | ADC characteristics                                                            |    |

| Table 56. | ADC accuracy.                                                                  | 97 |

| Table 57. | Maximum source impedance R <sub>AIN</sub> max                                  | 99 |

| Table 58. | DAC characteristics                                                            |    |

| Table 59. | Temperature sensor calibration values                                          | 02 |

| Table 60. | Temperature sensor characteristics                                             | 02 |

| Table 61. | Comparator 1 characteristics                                                   | 03 |

| Table 62. | Comparator 2 characteristics                                                   | 04 |

| Table 63. | LCD controller characteristics                                                 | 05 |

| Table 64. | LQPF100 14 x 14 mm, 100-pin low-profile quad flat package                      |    |

|           | mechanical data                                                                | 07 |

| Table 65. | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical data10      | 09 |

| Table 66. | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package mechanical data 1        | 13 |

| Table 67. | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package mechanical data1                      | 16 |

| Table 68. | UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array         |    |

|           | package mechanical data                                                        | 18 |

| Table 69. | UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules                  | 19 |

| Table 70. | TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array                |    |

|           | package mechanical data                                                        | 21 |

| Table 71. | TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules                   | 22 |

| Table 72. | Thermal characteristics                                                        | 24 |

| Table 73. | Ordering information scheme                                                    | 26 |

| Table 74. | Document revision history                                                      | 27 |

# 2.1 Device overview

#### Table 2. Ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A device features and peripheral counts

| Periph                                 | STM32L15xCxxxA                                                                                         |       | xxxA    | STM32L15xRxxxA                     |                                                      |    | STM32L15xVxxxA   |                   |     |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|-------|---------|------------------------------------|------------------------------------------------------|----|------------------|-------------------|-----|--|

| Flash (Kbytes)                         |                                                                                                        | 32    | 64      | 128                                | 32                                                   | 64 | 128              | 64                | 128 |  |

| Data EEPROM (Kb                        | oytes)                                                                                                 |       | 4       |                                    |                                                      |    |                  |                   |     |  |

| RAM (Kbytes)                           |                                                                                                        | 16    | 32      | 32                                 | 16                                                   | 32 | 32               | 32                | 32  |  |

| General-<br>purpose                    |                                                                                                        |       |         |                                    |                                                      | 6  |                  |                   |     |  |

|                                        | Basic                                                                                                  |       |         |                                    |                                                      | 2  |                  |                   |     |  |

| SPI                                    |                                                                                                        |       |         |                                    |                                                      | 2  |                  |                   |     |  |

| Communication                          | l <sup>2</sup> C                                                                                       |       |         |                                    |                                                      | 2  |                  |                   |     |  |

| interfaces                             | USART                                                                                                  | 3     |         |                                    |                                                      |    |                  |                   |     |  |

|                                        | USB                                                                                                    | 1     |         |                                    |                                                      |    |                  |                   |     |  |

| GPIOs                                  | 37                                                                                                     |       |         | 51/50 <sup>(1)</sup>               |                                                      |    | 83               |                   |     |  |

| 12-bit synchronize<br>Number of channe | 1<br>14 channels                                                                                       |       |         | 1<br>20/19 channels <sup>(1)</sup> |                                                      |    | 1<br>24 channels |                   |     |  |

| 12-bit DAC<br>Number of channe         | els                                                                                                    | 2 2   |         |                                    |                                                      |    |                  |                   |     |  |

| LCD (STM32L152)<br>COM x SEG           | xxxA Only)                                                                                             | 4x16  |         |                                    | 4x32/4x31 <sup>(1)</sup><br>8x28/8x27 <sup>(1)</sup> |    |                  | 4x44<br>8x40      |     |  |

| Comparator                             |                                                                                                        | 2     |         |                                    |                                                      |    |                  |                   |     |  |

| Capacitive sensing                     | g channels                                                                                             | 13 20 |         |                                    |                                                      |    |                  |                   |     |  |

| Max. CPU frequen                       | 32 MHz                                                                                                 |       |         |                                    |                                                      |    |                  |                   |     |  |

| Operating voltage                      | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option    |       |         |                                    |                                                      |    |                  |                   |     |  |

| Operating tempera                      | Ambient operating temperatures: –40 to +85 °C / –40 to + 105 °C<br>Junction temperature: -40 to +110°C |       |         |                                    |                                                      |    |                  |                   |     |  |

| Packages                               |                                                                                                        | LQFP  | 48, UFQ | FPN48                              | LQFP64, TFBGA64                                      |    |                  | LQFP100, UFBGA100 |     |  |

1. For TFBGA64 package (instead of PC3 pin there is  $V_{\mathsf{REF}^+}$  pin).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

## 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See the application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

## 3.10.1 Temperature sensor

The temperature sensor  $T_{\text{SENSE}}$  generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode, see *Table 59: Temperature sensor calibration values*.

## 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode see *Table 17: Embedded internal reference voltage*.

## 3.11 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

| Figure 5. STM32L15xRxxxA TFBGA64 ballout |                        |                      |         |                      |                      |                      |                |        |  |

|------------------------------------------|------------------------|----------------------|---------|----------------------|----------------------|----------------------|----------------|--------|--|

|                                          | 1                      | 2                    | 3       | 4                    | 5                    | 6                    | 7              | 8      |  |

| A                                        | , PC14-,<br>0\\$C32_lN | , PC13-,<br>WKUP2    | ( PB9 ) | , PB4 )              | ( PB3 )              | (PA15)               | (PA14)         | (PA13) |  |

| В                                        | /PC15-\<br>O\$C32_OUT  | - (VLCD)             | ( PB8 ) | BOOTO                | (PD2)                | (PC11)               | (PC10)         | (PA12) |  |

| С                                        | , ∕₽́ĤÒ`,<br>OSC_IN;   | Vss_4                | ( PB7 ) | ( PB5 )              | (PC12)               | (PA10)               | (PA9)          | (PA11) |  |

| D                                        | OSC_OUT                | 'V <sub>DD_4</sub> ' | (PB6)   | VSS_3                | VSS_2                | ,V <sub>SS_1</sub> , | (PA8)          | (PC9)  |  |

| E                                        | (NRST)                 | (PC1)                | ( PC0 ) | 'V <sub>DD_3</sub> ' | 'V <sub>DD_2</sub> ' | ,V <sub>DD_1</sub> , | (PC7)          | (PC8)  |  |

| F                                        | VSSA                   | (PC2)                | ( PA2 ) | ( PA5 )              | ( PB0 )              | (PC6)                | (PB15)         | (PB14) |  |

| G                                        | VREF+                  | PAO-WKUP1            | ( PA3 ) | ( PA6 )              | // PB1 )             | ( PB2 )              | (PB10)         | (PB13) |  |

| н                                        | VDDA;                  | ( PA1 )              | ( PA4 ) | ( PA7 )              | ( PC4 )              | (PC5)                | // (<br>(PB11) | (PB12) |  |

|                                          |                        |                      |         |                      |                      |                      |                | Al1609 |  |

Figure 5. STM32L15xRxxxA TFBGA64 ballout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |          |                         |               |                                                  | Pins functions                                 |                         |  |

|---------|--------|---------|----------|--------------------|----------|-------------------------|---------------|--------------------------------------------------|------------------------------------------------|-------------------------|--|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                            | Additional<br>functions |  |

| 82      | -      | -       | B9       | -                  | PD1      | I/O                     | FT            | PD1                                              | SPI2_SCK                                       | -                       |  |

| 83      | 54     | В5      | C8       | -                  | PD2      | I/O                     | FT            | PD2                                              | TIM3_ETR/LCD_SEG31<br>/LCD_SEG43/<br>LCD_COM7  | -                       |  |

| 84      | -      | -       | B8       | -                  | PD3      | I/O                     | FT            | PD3                                              | USART2_CTS/<br>SPI2_MISO                       | -                       |  |

| 85      | -      | -       | B7       | -                  | PD4      | I/O                     | FT            | PD4                                              | USART2_RTS/<br>SPI2_MOSI                       | -                       |  |

| 86      | -      | -       | A6       | -                  | PD5      | I/O                     | FT            | PD5                                              | USART2_TX                                      | -                       |  |

| 87      | -      | -       | B6       | -                  | PD6      | I/O                     | FT            | PD6                                              | USART2_RX                                      | -                       |  |

| 88      | -      | -       | A5       | -                  | PD7      | I/O                     | FT            | PD7                                              | USART2_CK/<br>TIM9_CH2                         | -                       |  |

| 89      | 55     | A5      | A8       | 39                 | PB3      | I/O                     | FT            | JTDO                                             | TIM2_CH2/PB3/<br>SPI1_SCK/<br>LCD_SEG7/JTDO    | COMP2_INM               |  |

| 90      | 56     | A4      | A7       | 40                 | PB4      | I/O                     | FT            | NJTRST                                           | TIM3_CH1/PB4/<br>SPI1_MISO/LCD_SEG8<br>/NJTRST | COMP2_INP               |  |

| 91      | 57     | C4      | C5       | 41                 | PB5      | I/O                     | FT            | PB5                                              | I2C1_SMBA/TIM3_CH2/<br>SPI1_MOSI/LCD_SEG9      | COMP2_INP               |  |

| 92      | 58     | D3      | B5       | 42                 | PB6      | I/O                     | FT            | PB6                                              | I2C1_SCL/TIM4_CH1/<br>USART1_TX                | _                       |  |

| 93      | 59     | C3      | B4       | 43                 | PB7      | I/O                     | FT            | PB7                                              | I2C1_SDA/TIM4_CH2/<br>USART1_RX                | PVD_IN                  |  |

| 94      | 60     | B4      | A4       | 44                 | BOOT0    | Ι                       | В             | BOOT0                                            | -                                              | -                       |  |

| 95      | 61     | В3      | A3       | 45                 | PB8      | I/O                     | FT            | PB8                                              | TIM4_CH3/I2C1_SCL/<br>LCD_SEG16/<br>TIM10_CH1  | -                       |  |

| 96      | 62     | A3      | В3       | 46                 | PB9      | I/O                     | FT            | PB9                                              | TIM4_CH4/I2C1_SDA/<br>LCD_COM3/<br>TIM11_CH1   | -                       |  |

| 97      | -      | -       | C3       | -                  | PE0      | I/O                     | FT            | PE0                                              | TIM4_ETR/LCD_SEG36<br>/ TIM10_CH1              | -                       |  |

| Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued) |  |

|------------------------------------------------------------------------------|--|

|                                                                              |  |

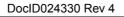

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- Caution: To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL ≤ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

## 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                         | Conditions                                                                        | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                         | V <sub>DD</sub> = 3.0 V                                                           | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                  | Trimming code is not a multiple of 16                                             | -                 | ±0.4 | 0.7              | %    |

| TRIM                                | resolution                                        | Trimming code is a multiple of 16                                                 | -                 | -    | ±1.5             | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                                  | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the factory-calibrated HSI oscillator | $V_{DDA}$ = 3.0 V, T <sub>A</sub> = 0 to 55 °C                                    |                   | -    | 1.5              | %    |

|                                     |                                                   | he $V_{DDA} = 3.0 \text{ V}, \text{ T}_{A} = -10 \text{ to } 70 ^{\circ}\text{C}$ |                   | -    | 2                | %    |

|                                     |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C                           | -2.5              | -    | 2                | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                                          | -4                | -    | 2                | %    |

|                                     |                                                   | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C              | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                    | -                                                                                 | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption               | -                                                                                 | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

## Low-speed internal (LSI) RC oscillator

| Table 32. LSI oscillator | r characteristics |

|--------------------------|-------------------|

|--------------------------|-------------------|

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | _   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

## 6.3.9 Memory characteristics

The characteristics are given at  $T_{\text{A}}$  = -40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

#### **RAM** memory

| Table | 35. | RAM | and | hardware | reaisters |

|-------|-----|-----|-----|----------|-----------|

| 10010 | ••• |     | ana | naranaro | regiotore |

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

| Symbol            | Parameter                                                                                     | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                                     | -                                               | 1.65 | -    | 3.6                | V    |

|                   | t <sub>prog</sub> Programming / erasing time for<br>byte / word / double word / half-<br>page | Erasing                                         | -    | 3.28 | 3.94               |      |

| t <sub>prog</sub> |                                                                                               | Programming                                     | -    | 3.28 | 3.94               | ms   |

|                   | Average current during whole program/erase operation                                          | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 300  | -                  | μA   |

| I <sub>DD</sub>   | Maximum current (peak) during program/erase operation                                         | Γ <sub>A</sub> = 25° C, V <sub>DD</sub> = 3.0 V | -    | 1.5  | 2.5                | mA   |

#### Table 36. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

#### Table 37. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                      | Conditions              | Value              |     |     | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------|--------------------|-----|-----|---------|

| Symbol                          | Falameter                                                                      | Conditions              | Min <sup>(1)</sup> | Тур | Мах | onit    |

| NCYC <sup>(2)</sup>             | Cycling (erase / write)<br>Program memory                                      | $T_A = -40^{\circ}C$ to | 10                 | -   | -   | kovolos |

| NOTO: 7                         | Cycling (erase / write)<br>EEPROM data memory                                  | 105 °C                  | 300                | -   | -   | kcycles |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | TRET = +85 °C           | 30                 | -   | -   |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C         | TRET - +05 C            | 30                 | -   | -   | voare   |

| Dat                             | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | TRET = +105 °C          | 10                 | -   | -   | years   |

|                                 | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 105 °C        | III.ET = 1103 C         | 10                 | _   | -   |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

DocID024330 Rev 4

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                             | Conditions                                  | Min | Max <sup>(2)</sup> | Unit  |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------------|---------------------------------------------|-----|--------------------|-------|

|                                               | f                       | Maximum frequency <sup>(3)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 400                | kHz   |

| 00                                            | f <sub>max(IO)out</sub> |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 400                | KIIZ  |

| 00                                            | t <sub>f(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 625                | ns    |

|                                               | t <sub>r(IO)out</sub>   |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 625                | 115   |

|                                               | f                       | Maximum frequency <sup>(3)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 2                  | MHz   |

| 01                                            | f <sub>max(IO)out</sub> |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 1                  |       |

| 01                                            | t <sub>f(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 125                | ns    |

|                                               | t <sub>r(IO)out</sub>   |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 250                |       |

|                                               | F <sub>max(IO)out</sub> | F <sub>max(IO)out</sub> Maximum frequency <sup>(3)</sup>              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 10                 | - MHz |

| 10                                            |                         |                                                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 2                  |       |

| 10                                            | t <sub>f(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 25                 |       |

|                                               | t <sub>r(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 125                | ns    |

|                                               | E                       | Maximum fraguanay <sup>(3)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 50                 | MHz   |

| 11                                            | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                      | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 8                  |       |

|                                               | t <sub>f(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V  | -   | 5                  |       |

|                                               | t <sub>r(IO)out</sub>   | Output rise and fall time                                             | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V | -   | 30                 |       |

| -                                             | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller | -                                           | 8   | -                  | ns    |

| Table 45. I/O AC characteristi |

|--------------------------------|

|--------------------------------|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 19*.

## 6.3.16 Communication interfaces

## I<sup>2</sup>C interface characteristics

The STM32L151x6/8/B-A and STM32L152x6/8/B-A product line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            | Standaı<br>I <sup>2</sup> C <sup>(</sup> | d mode<br>1)(2)     | Fast mod | Unit               |    |  |

|--------------------------------------------|----------------------------------------------------------------------|------------------------------------------|---------------------|----------|--------------------|----|--|

|                                            |                                                                      | Min                                      | Max                 | Min      | Max                |    |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7                                      | -                   | 1.3      | -                  |    |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0                                      | -                   | 0.6      | -                  | μs |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250                                      | -                   | 100      | -                  |    |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -                                        | 3450 <sup>(3)</sup> | -        | 900 <sup>(3)</sup> |    |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -                                        | 1000                | -        | 300                | ns |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -                                        | 300                 | -        | 300                |    |  |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0                                      | -                   | 0.6      | -                  |    |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7                                      | -                   | 0.6      | -                  | μs |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0                                      | -                   | 0.6      | -                  | μs |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7                                      | -                   | 1.3      | -                  | μs |  |

| Cb                                         | Capacitive load for each bus line                                    | -                                        | 400                 | -        | 400                | pF |  |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0                                        | 50 <sup>(4)</sup>   | 0        | 50 <sup>(4)</sup>  | ns |  |

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

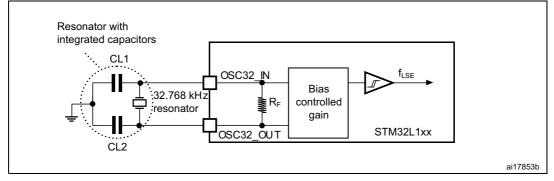

Figure 24. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

#### **USB** characteristics

The USB interface is USB-IF certified (full speed).

#### Table 51. USB startup time

| Symbol                              | Parameter                    | Мах | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

| Symbol                         | Parameter                            | Conditions                                                          | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |

|--------------------------------|--------------------------------------|---------------------------------------------------------------------|---------------------|---------------------|------|--|

| Input leve                     | ls                                   |                                                                     |                     |                     |      |  |

| $V_{DD}$                       | USB operating voltage <sup>(2)</sup> | -                                                                   | 3.0                 | 3.6                 | V    |  |

| $V_{DI}^{(3)}$                 | Differential input sensitivity       | I(USB_DP, USB_DM)                                                   | 0.2                 | -                   |      |  |

| V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range       | Includes V <sub>DI</sub> range                                      | 0.8                 | 2.5                 | V    |  |

| $V_{SE}^{(3)}$                 | Single ended receiver threshold      | -                                                                   | 1.3                 | 2.0                 |      |  |

| Output le                      | vels                                 |                                                                     |                     |                     |      |  |

| $V_{OL}^{(4)}$                 | Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(5)}$          | -                   | 0.3                 | v    |  |

| V <sub>OH</sub> <sup>(4)</sup> | Static output level high             | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}^{(5)}$ | 2.8                 | 3.6                 |      |  |

Table 52. USB DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. Guaranteed by characterization results.

4. Guaranteed by test in production.

5.  $\ensuremath{\,R_L}$  is the load connected on the USB drivers.

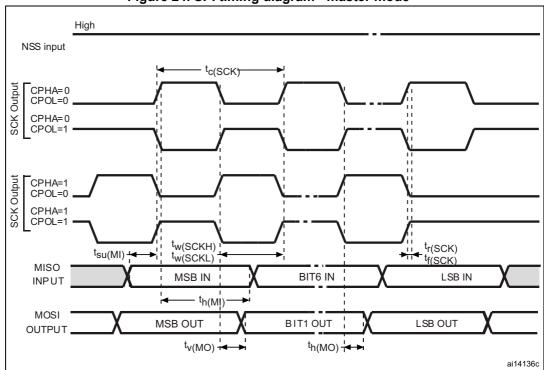

#### Figure 25. USB timings: definition of data signal rise and fall time

#### Table 53. USB: full speed electrical characteristics

|                  | Driver characteristics <sup>(1)</sup> |                                |     |     |      |  |  |

|------------------|---------------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol           | Parameter                             | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>   | Fall Time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching              | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage       | -                              | 1.3 | 2.0 | V    |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification section 7 (version 2.0).

| Symbol            | Parameter                                          | Conditions                                             | Min                                                            | ,<br>Тур | Мах     | Unit               |  |

|-------------------|----------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|----------|---------|--------------------|--|

|                   |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                                                           | -        | -       |                    |  |

|                   |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56                                                           | -        | -       |                    |  |

| t <sub>S</sub>    | Sampling time <sup>(5)</sup>                       | Direct channels<br>1.8 V ≤V <sub>DDA</sub> ⊴2.4 V      | 0.56                                                           | -        | -       | μs                 |  |

|                   |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1                                                              | -        | -       |                    |  |

|                   |                                                    | -                                                      | 4                                                              | -        | 384     | 1/f <sub>ADC</sub> |  |

|                   |                                                    | f <sub>ADC</sub> = 16 MHz                              | 1                                                              | -        | 24.75   | μs                 |  |

| t <sub>CONV</sub> | Total conversion time<br>(including sampling time) | -                                                      | 4 to 384 (sampling<br>phase) +12 (successive<br>approximation) |          |         | 1/f <sub>ADC</sub> |  |

| C                 | Internal sample and hold                           | Direct channels                                        | -                                                              | 16       | -       | pF                 |  |

| C <sub>ADC</sub>  | capacitor                                          | Multiplexed channels                                   | -                                                              | 10       | -       | μ                  |  |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                              | -        | Tconv+1 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Regular sequencer                                  | 6/8/10-bit conversions                                 | -                                                              | -        | Tconv   | 1/f <sub>ADC</sub> |  |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                              | -        | Tconv+2 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Injected sequencer                                 | 6/8/10-bit conversions                                 | -                                                              | -        | Tconv+1 | 1/f <sub>ADC</sub> |  |

| R <sub>AIN</sub>  | Signal source impedance <sup>(5)</sup>             | -                                                      | -                                                              | -        | 50      | кΩ                 |  |

| t <sub>lat</sub>  | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219                                                            | -        | 281     | ns                 |  |

|                   | latency                                            | -                                                      | 3.5                                                            | -        | 4.5     | 1/f <sub>ADC</sub> |  |

| 4                 | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                                                            | -        | 219     | ns                 |  |

| t <sub>latr</sub> | latency                                            | -                                                      | 2.5                                                            | -        | 3.5     | 1/f <sub>ADC</sub> |  |

| t <sub>STAB</sub> | Power-up time                                      | -                                                      | -                                                              | -        | 3.5     | μs                 |  |

Table 55. ADC characteristics (continued)

1. The V<sub>REF+</sub> input can be grounded if neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

2. The current consumption through  $\mathsf{V}_{\mathsf{REF}}$  is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu$ A), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

3. V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pin descriptions for further details.

4.  $V_{SSA}$  or  $V_{REF-}$  must be tied to ground.

5. See Table 57: Maximum source impedance RAIN max for  $\mathsf{R}_{\mathsf{AIN}}$  limitations

## 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | Conditions                                                                  |                               | Min | Тур       | Max                       | Unit |

|---------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|-----|-----------|---------------------------|------|

| V <sub>DDA</sub>                | Analog supply voltage                                 | -                                                                           |                               | 1.8 | -         | 3.6                       | V    |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must<br>V <sub>DDA</sub>                                  | always be below               | 1.8 | -         | 3.6                       | V    |

| V <sub>REF-</sub>               | Lower reference voltage                               | -                                                                           |                               |     | $V_{SSA}$ |                           | V    |

| (4)                             | Current consumption on                                | No load, mid                                                                | dle code (0x800)              | -   | 130       | 220                       | μA   |

| I <sub>DDVREF+</sub> (1)        | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                                                                | st code (0x000)               | -   | 220       | 350                       | μA   |

| (1)                             | Current consumption on                                | No load, mid                                                                | ldle code (0x800)             | -   | 210       | 320                       | μA   |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wor                                                                | st code (0xF1C)               | -   | 320       | 520                       | μA   |

| D                               | Resistive load                                        | DAC output                                                                  | Connected to $V_{SSA}$        | 5   | -         | -                         | kΩ   |

| R <sub>L</sub>                  | Resistive load                                        | buffer ON                                                                   | Connected to V <sub>DDA</sub> | 25  | -         | -                         | K52  |

| CL                              | Capacitive load                                       | DAC output                                                                  | buffer ON                     | -   | -         | 50                        | pF   |

| R <sub>O</sub>                  | Output impedance                                      | DAC output buffer OFF                                                       |                               | 12  | 16        | 20                        | kΩ   |

| V                               | Voltage on DAC_OUT                                    | DAC output buffer ON                                                        |                               | 0.2 | -         | V <sub>DDA</sub> –<br>0.2 | V    |

| V <sub>DAC_OUT</sub>            | output                                                | DAC output                                                                  | buffer OFF                    | 0.5 | -         | V <sub>REF+</sub><br>1LSB | mV   |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>             | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | 1.5       | 3                         |      |

| Ditt                            |                                                       | No $R_L$ , $C_L \le DAC$ output                                             |                               | -   | 1.5       | 3                         |      |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF, F}$<br>DAC output                                    | -                             | -   | 2         | 4                         |      |

|                                 | Integral nor linearity ·                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                 |                               | -   | 2         | 4                         | LSB  |

| · · (1)                         | Offset error at code 0x800 <sup>(4)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON  |                               | -   | ±10       | ±25                       |      |

| Offset <sup>(1)</sup>           |                                                       | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF          |                               | -   | ±5        | ±8                        |      |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>             | No R <sub>L</sub> , C <sub>L</sub> $\leq$ DAC output                        |                               | -   | ±1.5      | ±5                        |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

# 6.3.20 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |  |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|--|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |  |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |  |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  |           |  |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                                     | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |  |  |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 | μs        |  |  |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 |           |  |  |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |  |  |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |  |  |

Table 61. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

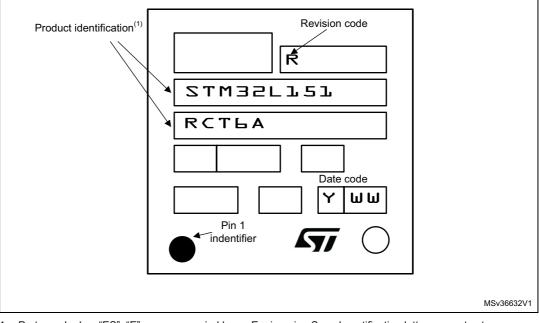

#### LQFP64 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

### Figure 35. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

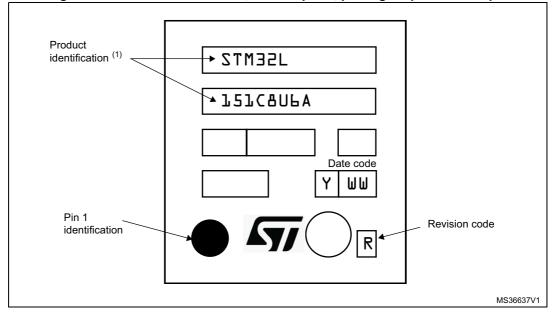

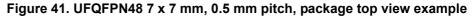

#### **UFQFPN48** device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

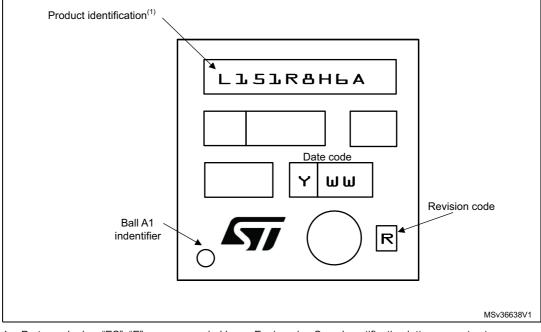

#### **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 47. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date | Revision | ChangesUpdated Section 7: Package information structure: Paragraph titlesand paragraph heading level.Updated Section 7: Package information for all package devicemarkings, adding text for device orientation versus pin 1/ ball A1identifier.Updated Section 7: Package information for all package devicemarkings, adding text for device orientation versus pin 1/ ball A1identifier.Updated Figure 32: LQFP100 14 x 14 mm, 100-pin package topview example removing gate mark.Updated Table 65: LQFP64 10 x 10 mm, 64-pin low-profile quad flatpackage mechanical data.Updated Section 7.5: UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thinfine-pitch ball grid array package information adding Table 69:UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thinfine-pitch ball grid array package recommended PCB designrules and Figure 43: UFBGA100 7 x 7 mm, 0.5 mm pitch, thin fine-pitch ball grid array package recommended footprint.Updated Section 7.6: TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package recommended footprint.Updated Table 17: Embedded internal reference voltagetemperature coefficient at 100ppm/°C and table note 3: "guaranteedby design" changed by "guaranteed by characterization results".Updated Table 62: Comparator 2 characteristics new maximumthreshold volt |  |  |

|      |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |