Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151cbu6a  |

## 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151x6/8/B-A and STM32L152x6/8/B-A ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontrollers product line.

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A microcontroller family includes devices in 3 different package types: from 48 to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- · PC peripherals, gaming, GPS and sport equipment

- Alarm systems, Wired and wireless sensors, Video intercom

- Utility metering

This STM32L151x6/8/B-A and STM32L152x6/8/B-A datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The document "Getting started with STM32L1xxxx hardware development" AN3216 gives a hardware implementation overview.

Both documents are available from the STMicroelectronics website www.st.com.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the ARM website.

Figure 1 shows the general block diagram of the device family.

#### Caution:

This datasheet does not apply to:

STM32L15xx6/8/B

covered by a separate datasheet.

# 2.1 Device overview

Table 2. Ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A device features and peripheral counts

| Periph                              | STM                                                                                                   | 32L15xC | xxxA          | STM | 32L15xR              | xxxA                 | STM32L1            | 5xVxxxA  |                  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|---------|---------------|-----|----------------------|----------------------|--------------------|----------|------------------|--|

| Flash (Kbytes)                      |                                                                                                       | 32      | 64            | 128 | 32                   | 64                   | 128                | 64       | 128              |  |

| Data EEPROM (Kb                     | oytes)                                                                                                |         | •             |     |                      | 4                    |                    |          |                  |  |

| RAM (Kbytes)                        |                                                                                                       | 16      | 32            | 32  | 16                   | 32                   | 32                 | 32       | 32               |  |

| General-<br>purpose                 |                                                                                                       | 6       |               |     |                      |                      |                    |          |                  |  |

|                                     | Basic                                                                                                 |         |               |     |                      | 2                    |                    |          |                  |  |

|                                     | SPI                                                                                                   |         |               |     |                      | 2                    |                    |          |                  |  |

| Communication                       | I <sup>2</sup> C                                                                                      |         |               |     |                      | 2                    |                    |          |                  |  |

| interfaces                          | USART                                                                                                 |         | 3             |     |                      |                      |                    |          |                  |  |

|                                     | USB                                                                                                   | 1       |               |     |                      |                      |                    |          |                  |  |

| GPIOs                               | •                                                                                                     | 37      |               |     | 51/50 <sup>(1)</sup> |                      |                    | 83       |                  |  |

| 12-bit synchronize Number of channe |                                                                                                       | 1.      | 1<br>4 channe | els | 20/1                 | 1<br>9 channe        | els <sup>(1)</sup> |          | 1<br>24 channels |  |

| 12-bit DAC<br>Number of channe      | els                                                                                                   | 2 2     |               |     |                      |                      |                    |          |                  |  |

| LCD (STM32L152x<br>COM x SEG        | xxxxA Only)                                                                                           |         | 4x16          |     |                      | x32/4x31<br>x28/8x27 |                    | 4x<br>8x |                  |  |

| Comparator                          |                                                                                                       |         |               |     |                      | 2                    |                    |          |                  |  |

| Capacitive sensing                  | g channels                                                                                            | 13 20   |               |     |                      |                      |                    |          |                  |  |

| Max. CPU frequen                    | су                                                                                                    | 32 MHz  |               |     |                      |                      |                    |          |                  |  |

| Operating voltage                   | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option 1.65 V to 3.6 V without BOR option      |         |               |     |                      |                      |                    | ption    |                  |  |

| Operating tempera                   | Ambient operating temperatures: -40 to +85 °C / -40 to + 105 °C  Junction temperature: -40 to +110 °C |         |               |     |                      |                      | 05 °C              |          |                  |  |

| Packages                            |                                                                                                       | LQFP    | 48, UFQI      |     |                      |                      | UFBGA100           |          |                  |  |

<sup>1.</sup> For TFBGA64 package (instead of PC3 pin there is  $V_{\text{REF+}}$  pin).

## 3.1 Low-power modes

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply:

- In Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), the CPU runs at up to 32 MHz (refer to *Table 18* for consumption).

- In Range 2 (full V<sub>DD</sub> range), the CPU runs at up to 16 MHz (refer to Table 18 for consumption)

- In Range 3 (full V<sub>DD</sub> range), the CPU runs at up to 4 MHz (generated only with the multispeed internal RC oscillator clock source). Refer to *Table 18* for consumption.

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### • Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Sleep mode power consumption: refer to *Table 20*.

#### • Low-power Run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (less than 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In the low-power Run mode, the clock frequency and the number of enabled peripherals are both limited.

Low-power Run mode consumption: refer to Table 21.

#### • Low-power Sleep mode

This mode is achieved by entering the Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In the low-power Sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

Low-power Sleep mode consumption: refer to Table 22.

#### • Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

#### Stop mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI

Table 3. Functionalities depending on the operating power supply range (continued)

|                                | Functionalities depending on the operating power supply range |                           |                                   |                      |  |  |  |  |

|--------------------------------|---------------------------------------------------------------|---------------------------|-----------------------------------|----------------------|--|--|--|--|

| Operating power supply range   | DAC and ADC operation                                         | USB                       | Dynamic voltage scaling range     | I/O operation        |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V | Conversion time up to 500 Ksps                                | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V | Conversion time up to 1 Msps                                  | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

<sup>1.</sup> CPU frequency changes from initial to final must respect " $F_{CPU}$  initial <  $4*F_{CPU}$  final" to limit  $V_{CORE}$  drop due to current consumption peak when frequency increases. It must also respect 5  $\mu$ s delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5  $\mu$ s, then switch from 16 MHz to 32 MHz.

Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                 | Dynamic voltage scaling range |

|-----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)    | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)      | Range 2                       |

| 2.1 MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

<sup>2.</sup> Should be USB-compliant from I/O voltage standpoint, the minimum  $V_{DD}$  is 3.0 V.

## 3.17 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.18 Development support

#### Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG JTMS and JTCK pins are shared with SWDAT and SWCLK, respectively, and a specific sequence on the JTMS pin is used to switch between JTAG-DP and SW-DP.

The JTAG port can be permanently disabled with a JTAG fuse.

#### **Embedded Trace Macrocell™**

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L151x6/8/B-A and STM32L152x6/8/B-A device through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

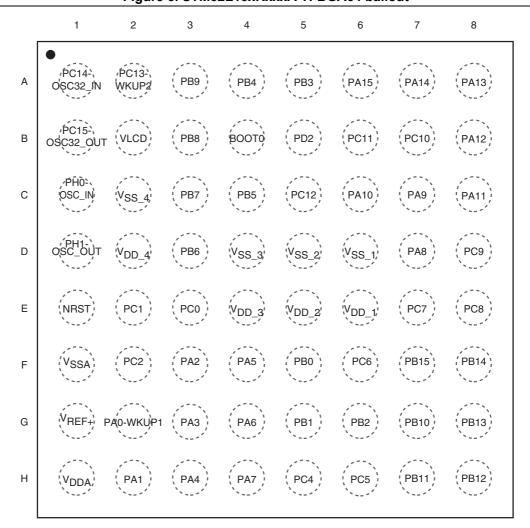

Figure 5. STM32L15xRxxxA TFBGA64 ballout

1. This figure shows the package top view.

AI16090c

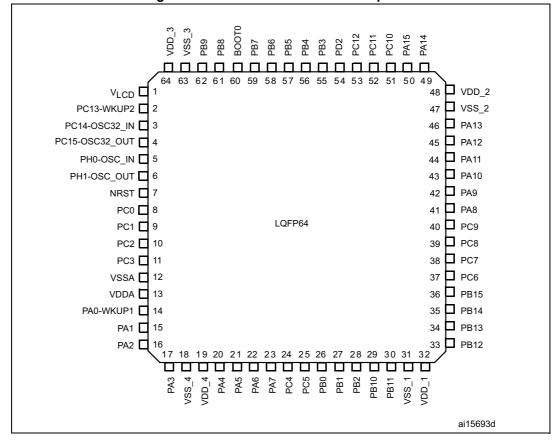

Figure 6. STM32L15xRxxxA LQFP64 pinout

1. This figure shows the package top view.

|           |                    |              |          |            |        | Digital alterna | te function | number         |           |           |        |            |            |          |          |

|-----------|--------------------|--------------|----------|------------|--------|-----------------|-------------|----------------|-----------|-----------|--------|------------|------------|----------|----------|

|           | AFIO0              | AFIO1        | AFIO2    | AFIO3      | AFIO4  | AFIO5           | AFOI6       | AFIO7          | AFI<br>O8 | AFI<br>O9 | AFIO11 | AFIO<br>12 | AFIO<br>13 | AFIO14   | AFIO15   |

| Port name | Alternate function |              |          |            |        |                 |             |                |           |           |        |            |            |          |          |

|           | SYSTEM             | TIM2         | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2          | N/A         | USART<br>1/2/3 | N/A       | N/A       | LCD    | N/A        | N/A        | RI       | SYSTEM   |

| воото     | воото              | -            | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| NRST      | NRST               | -            | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| PA0-WKUP1 | =                  | TIM2_CH1_ETR | -        | -          | -      | -               | -           | USART2_CTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA1       | -                  | TIM2_CH2     | -        | -          | -      | -               | -           | USART2_RTS     | -         | -         | [SEG0] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA2       | -                  | TIM2_CH3     | -        | TIM9_CH1   | -      | -               | -           | USART2_TX      | -         | -         | [SEG1] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA3       | -                  | TIM2_CH4     | -        | TIM9_CH2   | -      | -               | -           | USART2_RX      | -         | -         | [SEG2] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA4       | -                  | -            | -        | -          | -      | SPI1_NSS        | -           | USART2_CK      | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA5       | -                  | TIM2_CH1_ETR | -        | -          | -      | SPI1_SCK        | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA6       | -                  | -            | TIM3_CH1 | TIM10_CH1  | -      | SPI1_MISO       | -           | -              | -         | -         | [SEG3] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA7       | -                  | -            | TIM3_CH2 | TIM11_CH1  | -      | SPI1_MOSI       | -           | -              | -         | -         | [SEG4] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA8       | МСО                | -            | -        | -          | -      | -               | -           | USART1_CK      | -         | -         | [COM0] | -          | -          | TIMx_IC1 | EVENTOUT |

| PA9       | -                  | -            | -        | -          | -      | -               | -           | USART1_TX      | -         | -         | [COM1] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA10      | -                  | -            | -        | -          | -      | -               | -           | USART1_RX      | -         | -         | [COM2] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA11      | -                  | -            | -        | -          | -      | SPI1_MISO       | -           | USART1_CTS     | -         | -         | -      | -          | -          | TIMx_IC4 | EVENTOUT |

| PA12      | -                  | -            | -        | -          | -      | SPI1_MOSI       | -           | USART1_RTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA13      | JTMS-<br>SWDIO     | -            | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA14      | JTCK-<br>SWCLK     | -            | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | TIMx_IC3 | EVENTOUT |

| PA15      | JTDI               | TIM2_CH1_ETR | -        | -          | -      | SPI1_NSS        | -           | -              | -         | -         | SEG17  | -          | -          | TIMx_IC4 | EVENTOUT |

| PB0       | -                  | -            | TIM3_CH3 | -          | -      | -               | -           | -              | -         | -         | [SEG5] | -          | -          | -        | EVENTOUT |

| PB1       | -                  | -            | TIM3_CH4 | -          | -      | -               | -           | -              | -         | -         | [SEG6] | -          | -          | -        | EVENTOUT |

| PB2       | BOOT1              | -            | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | EVENTOUT |

| PB3       | JTDO               | TIM2_CH2     | -        | -          | -      | SPI1_SCK        | -           | -              | -         | -         | [SEG7] | -          | -          | -        | EVENTOUT |

- 3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.17.

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11* for maximum allowed input voltage values.

- 5. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11: Voltage characteristics* for the maximum allowed input voltage values.

- When several inputs are submitted to a current injection, the maximum ΣI<sub>INJ(PIN)</sub> is the absolute sum of the

positive and negative injected currents (instantaneous values).

**Table 13. Thermal characteristics**

| Symbol            | Ratings                                   | Value        | Unit |

|-------------------|-------------------------------------------|--------------|------|

| T <sub>STG</sub>  | Storage temperature range                 | -65 to +150  | °C   |

| T <sub>J</sub>    | Maximum junction temperature              | 150          | °C   |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering | see note (1) | °C   |

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup>

7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS

directive 2011/65/EU, July 2011).

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 14. General operating conditions

| Symbol                          | Parameter                                       | Conditions                            | Min  | Max                  | Unit |

|---------------------------------|-------------------------------------------------|---------------------------------------|------|----------------------|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                    | -                                     | 0    | 32                   |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                   | -                                     | 0    | 32                   | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                   | -                                     | 0    | 32                   |      |

|                                 |                                                 | BOR detector disabled                 | 1.65 | 3.6                  |      |

| V <sub>DD</sub>                 | Standard operating voltage                      | BOR detector enabled, at power on     | 1.8  | 3.6                  | V    |

|                                 |                                                 | BOR detector disabled, after power on | 1.65 | 3.6                  |      |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage (ADC and DAC not used) | Must be the same voltage as           | 1.65 | 3.6                  | V    |

| V DDA`                          | Analog operating voltage (ADC or DAC used)      | $V_{DD}^{(2)}$                        | 1.8  | 3.6                  | V    |

|                                 |                                                 | FT pins: 2.0 V ≤V <sub>DD</sub>       | -0.3 | 5.5 <sup>(3)</sup>   |      |

| V                               | I/O input voltage                               | FT pins: V <sub>DD</sub> < 2.0 V      | -0.3 | 5.25 <sup>(3)</sup>  | V    |

| V <sub>IN</sub>                 | input voltage                                   | воото                                 | 0    | 5.5                  | V    |

|                                 |                                                 | Any other pin                         | -0.3 | V <sub>DD</sub> +0.3 |      |

Table 20. Current consumption in Sleep mode

| Symbol            | Parameter          | Cond                                                           | litions                                               | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|--------------------|----------------------------------------------------------------|-------------------------------------------------------|-------------------|------|--------------------|------|

|                   |                    |                                                                | Range 3,                                              | 1 MHz             | 50   | 155                |      |

|                   |                    |                                                                | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 78.5 | 235                |      |

|                   |                    |                                                                | VOS[1:0] = 11                                         | 4 MHz             | 140  | 370 <sup>(3)</sup> |      |

|                   |                    | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                              | 4 MHz             | 165  | 375                |      |

|                   |                    | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 310  | 530                |      |

|                   |                    | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 590  | 1000               |      |

|                   | Cupply             | OIV)                                                           | Range 1,                                              | 8 MHz             | 350  | 615                |      |

|                   | Supply current in  |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 680  | 1200               |      |

|                   | Sleep              |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2350               | μΑ   |

|                   | mode,<br>Flash OFF | HSI clock source                                               | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 640  | 970                |      |

|                   |                    | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2350               |      |

|                   |                    | MSI clock, 65 kHz                                              | Range 3,                                              | 65 kHz<br>524 kHz | 19   | 60                 |      |

|                   |                    | MSI clock, 524 kHz                                             | V <sub>CORE</sub> =1.2 V                              |                   | 33   | 90                 |      |

| I <sub>DD</sub>   |                    | MSI clock, 4.2 MHz                                             | VOS[1:0] = 11                                         | 4.2 MHz           | 145  | 210                |      |

| (Sleep)           |                    |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 60.5 | 145                |      |

|                   |                    |                                                                |                                                       | 2 MHz             | 89.5 | 225                |      |

|                   |                    |                                                                |                                                       | 4 MHz             | 150  | 360                |      |

|                   |                    | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, |                                                       | 4 MHz             | 180  | 370                |      |

|                   |                    | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 320  | 490                |      |

|                   |                    | above 16 MHz (PLL ON) <sup>(2)</sup>                           | VOS[1:0] = 10                                         | 16 MHz            | 605  | 895                |      |

|                   | Supply             |                                                                | Range 1,                                              | 8 MHz             | 380  | 565                |      |

|                   | current in         |                                                                | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 695  | 1070               |      |

|                   | Sleep              |                                                                | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2200               | μΑ   |

| mode,<br>Flash ON | Flash ON           | HSI clock source                                               | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 650  | 970                |      |

|                   |                    | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2320               |      |

|                   |                    | MSI clock, 65 kHz                                              | Range 3,                                              | 65 kHz            | 29.5 | 65                 |      |

|                   |                    | MSI clock, 524 kHz                                             | V <sub>CORE</sub> =1.2V                               | 524 kHz           | 44   | 80                 |      |

|                   |                    | MSI clock, 4.2 MHz                                             | VOS[1:0] = 11                                         | 4.2 MHz           | 155  | 220                |      |

<sup>1.</sup> Guaranteed by characterization results, unless otherwise specified.

<sup>3.</sup> Guaranteed by test in production.

<sup>2.</sup> Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

### 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

## High-speed internal (HSI) RC oscillator

Table 31. HSI oscillator characteristics

|                                     | Table 31. Hor oscillator characteristics          |                                                                        |                   |      |                  |      |  |  |  |

|-------------------------------------|---------------------------------------------------|------------------------------------------------------------------------|-------------------|------|------------------|------|--|--|--|

| Symbol                              | Parameter                                         | Conditions                                                             | Min               | Тур  | Max              | Unit |  |  |  |

| f <sub>HSI</sub>                    | Frequency                                         | V <sub>DD</sub> = 3.0 V                                                | -                 | 16   | -                | MHz  |  |  |  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                  | Trimming code is not a multiple of 16                                  | -                 | ±0.4 | 0.7              | %    |  |  |  |

| TRIM                                | resolution                                        | Trimming code is a multiple of 16                                      | -                 | -    | ±1.5             | %    |  |  |  |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = 25 °C                                       | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |  |  |  |

|                                     | Accuracy of the factory-calibrated HSI oscillator | $V_{DDA} = 3.0 \text{ V}, T_A = 0 \text{ to } 55 ^{\circ}\text{C}$     | -1.5              | -    | 1.5              | %    |  |  |  |

|                                     |                                                   | $V_{DDA} = 3.0 \text{ V}, T_{A} = -10 \text{ to } 70 ^{\circ}\text{C}$ | -2                | -    | 2                | %    |  |  |  |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C                | -2.5              | -    | 2                | %    |  |  |  |

|                                     |                                                   | $V_{DDA} = 3.0 \text{ V}, T_A = -10 \text{ to } 105 ^{\circ}\text{C}$  | -4                | -    | 2                | %    |  |  |  |

|                                     |                                                   | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C   | -4                | -    | 3                | %    |  |  |  |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time                       | -                                                                      | -                 | 3.7  | 6                | μs   |  |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption                  | -                                                                      | -                 | 100  | 140              | μΑ   |  |  |  |

<sup>1.</sup> The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

### Low-speed internal (LSI) RC oscillator

Table 32. LSI oscillator characteristics

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | -   | 400 | 510 | nA   |

<sup>1.</sup> Guaranteed by test in production.

<sup>2.</sup> Guaranteed by characterization results.

<sup>3.</sup> Guaranteed by test in production.

<sup>2.</sup> This is a deviation for an individual part, once the initial frequency has been measured.

<sup>3.</sup> Guaranteed by design.

## 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105  $^{\circ}$ C unless otherwise specified.

## **RAM** memory

Table 35. RAM and hardware registers

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

## Flash memory and data EEPROM

Table 36. Flash memory and data EEPROM characteristics

| Symbol            | Parameter                                             | Conditions                                       | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|-------------------------------------------------------|--------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase             | -                                                | 1.65 | -    | 3.6                | V    |

| t <sub>prog</sub> | Programming / erasing time for                        | Erasing                                          | -    | 3.28 | 3.94               | ms   |

|                   | byte / word / double word / half-<br>page             | Programming                                      | -    | 3.28 | 3.94               |      |

| I <sub>DD</sub>   | Average current during whole program/erase operation  | -T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 300  | -                  | μΑ   |

|                   | Maximum current (peak) during program/erase operation |                                                  | -    | 1.5  | 2.5                | mA   |

<sup>1.</sup> Guaranteed by design.

Table 37. Flash memory, data EEPROM endurance and data retention

| Cumbal                          | Parameter Conditions                                                             |                         | Value              |     |     | Unit    |

|---------------------------------|----------------------------------------------------------------------------------|-------------------------|--------------------|-----|-----|---------|

| Symbol                          | Parameter                                                                        | Conditions              | Min <sup>(1)</sup> | Тур | Max | Onit    |

| NCYC <sup>(2)</sup>             | Cycling (erase / write)<br>Program memory                                        | $T_A = -40^{\circ}C$ to | 10                 | -   | -   | kcycles |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                    | 105 °C                  | 300                | -   | -   |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after 10 kcycles at T <sub>A</sub> = 85 °C       | TRET = +85 °C           | 30                 | -   | -   | - years |

|                                 | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C           | TRET = 100 C            | 30                 | -   | -   |         |

|                                 | Data retention (program memory) after 10 kcycles at T <sub>A</sub> = 105 °C      | TRET = +105 °C          | 10                 | -   | -   |         |

|                                 | Data retention (EEPROM data memory) after 300 kcycles at T <sub>A</sub> = 105 °C | 11121 - 1103 0          | 10                 | -   | -   |         |

<sup>1.</sup> Guaranteed by characterization results.

577

<sup>2.</sup> Characterization is done according to JEDEC JESD22-A117.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Table 45. I/O AC characteristics<sup>(1)</sup>

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                        | Conditions                                                       | Min                                                      | Max <sup>(2)</sup> | Unit    |     |  |

|-----------------------------------------------|-------------------------|------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|--------------------|---------|-----|--|

| 00                                            | f                       | Maximum frequency <sup>(3)</sup>                                 | $C_L = 50 \text{ pF}, V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}$  | -                                                        | 400                | kHz     |     |  |

|                                               | f <sub>max(IO)out</sub> | Maximum frequency                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -                                                        | 400                | KIIZ    |     |  |

| 00                                            | t <sub>f(IO)out</sub>   | Output rise and fall time                                        | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -                                                        | 625                | ns      |     |  |

|                                               | $t_{r(IO)out}$          | Output rise and fail time                                        | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -                                                        | 625                | 115     |     |  |

|                                               | f                       | Maximum frequency <sup>(3)</sup>                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -                                                        | 2                  | MHz     |     |  |

| 01                                            | f <sub>max(IO)out</sub> | Maximum frequency                                                | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -                                                        | 1                  | IVIITZ  |     |  |

| 01                                            | t <sub>f(IO)out</sub>   | t <sub>f(IO)out</sub>                                            | t <sub>f(IO)out</sub> Output rise and fall time                  | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -                  | 125     | ns  |  |

|                                               |                         | Output rise and fail time                                        | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -                                                        | 250                | 113     |     |  |

|                                               | F <sub>max(IO)out</sub> | E Maximu                                                         | Maximum frequency <sup>(3)</sup>                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -                  | 10      | MHz |  |

| 10                                            |                         | iviaximum nequency                                               | $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$ | -                                                        | 2                  | 1011 12 |     |  |

| 10                                            | t <sub>f(IO)out</sub>   | Output rise and fall time                                        | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -                                                        | 25                 | ns      |     |  |

|                                               | $t_{r(IO)out}$          | Output rise and fail time                                        | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -                                                        | 125                | 115     |     |  |

|                                               | F                       | (3)                                                              | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -                                                        | 50                 | MHz     |     |  |

| 44                                            | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> $C_{L} = 50 \text{ pF}, V_{DD}$ | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -                                                        | 8                  | IVIITZ  |     |  |

| 11                                            | t <sub>f(IO)out</sub>   | Output rice and fall time                                        | C <sub>L</sub> = 30 pF, V <sub>DD</sub> = 2.7 V to 3.6 V         | -                                                        | 5                  |         |     |  |

|                                               | t <sub>r(IO)out</sub>   | Output rise and fall time                                        | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 2.7 V        | -                                                        | 30                 |         |     |  |

| -                                             | t <sub>EXTIpw</sub>     | Pulse width of external signals detected by the EXTI controller  | -                                                                | 8                                                        | -                  | ns      |     |  |

The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the reference manual for a description of GPIO Port configuration register.

47/

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> The maximum frequency is defined in Figure 19.

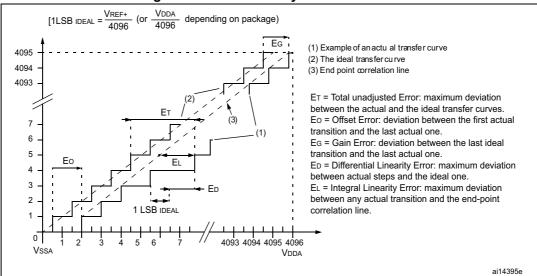

Table 56. ADC accuracy<sup>(1)(2)</sup>

| Symbol | Parameter                            | Test conditions                                                                                                                                                  | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                                                                                                 | -                  | 2.5 | 4                  |      |

| EO     | Offset error                         |                                                                                                                                                                  | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤ $V_{REF+}$ ≤ 3.6 V<br>$f_{ADC}$ = 8 MHz, $R_{AIN}$ = 50 Ω                                                                                                | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$                                                                                                                     | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                  | -                  | 2   | 3                  |      |

| ENOB   | Effective number of bits             | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                                                                                                 | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+}$ $f_{ADC} = 16 \text{ MHz}, R_{AIN} = 50 \Omega$                                                                                             | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | T <sub>A</sub> = -40 to 105 ° C                                                                                                                                  | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                                                                                                       | -                  | -72 | -69                |      |

| ENOB   | Effective number of bits             | $1.8 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.4 \text{ V}$ $\text{V}_{\text{DDA}} = \text{V}_{\text{REF+}}$ $\text{f}_{\text{ADC}} = 8 \text{ MHz or 4 MHz},$ | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio |                                                                                                                                                                  | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | $R_{AIN}$ = 50 Ω<br>$T_{A}$ = -40 to 105 ° C                                                                                                                     | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                                                                                                       | -                  | -72 | -69                |      |

| ET     | Total unadjusted error               |                                                                                                                                                                  | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                                                                                                      | -                  | 1.5 | 3.5                |      |

| EG     | Gain error                           | 1.8 V ≤ $V_{REF+}$ ≤ 2.4 V<br>$f_{ADC}$ = 4 MHz, $R_{AIN}$ = 50 Ω                                                                                                | -                  | 3.5 | 6                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$                                                                                                                     | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                  | -                  | 2.5 | 3.5                |      |

| ET     | Total unadjusted error               |                                                                                                                                                                  | -                  | 2   | 3                  |      |

| EO     | Offset error                         | 1.8 V ≤ V <sub>DDA</sub> ≤ 2.4 V<br>1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>$f_{ADC}$ = 4 MHz, $R_{AIN}$ = 50 Ω                                                     | -                  | 1   | 1.5                |      |

| EG     | Gain error                           |                                                                                                                                                                  | -                  | 1.5 | 2.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$                                                                                                                     | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                                                                                                  | -                  | 2   | 3                  |      |

<sup>1.</sup> ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this

significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a

Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC

accuracy.

<sup>3.</sup> Guaranteed by characterization results.

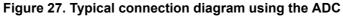

Figure 26. ADC accuracy characteristics

- Refer to Table 57: Maximum source impedance RAIN max for the value of R<sub>AIN</sub> and Table 55: ADC characteristics for the value of CADC

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

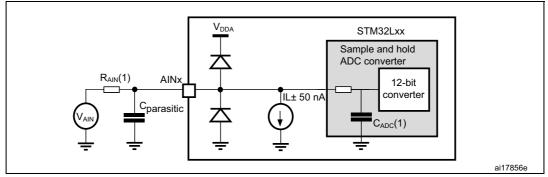

## **UFQFPN48** device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 41. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package top view example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package mechanical data (continued)

| Cumb al | millimeters |      |      | inches <sup>(1)</sup> |        |        |

|---------|-------------|------|------|-----------------------|--------|--------|

| Symbol  | Min         | Тур  | Max  | Min                   | Тур    | Max    |

| F       | 0.7         | 0.75 | 0.8  | 0.0276                | 0.0295 | 0.0315 |

| ddd     | -           | -    | 0.1  | -                     | -      | 0.0039 |

| eee     | -           | -    | 0.15 | -                     | -      | 0.0059 |

| fff     | -           | -    | 0.05 | -                     | -      | 0.002  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

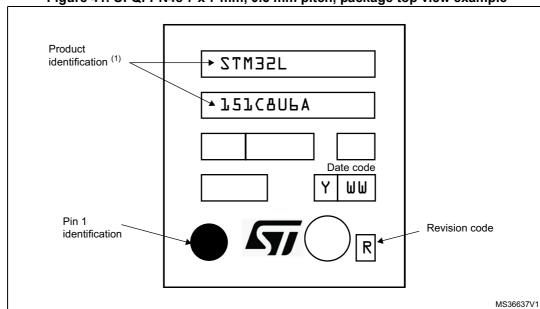

Figure 43. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package recommended footprint

Table 69. UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

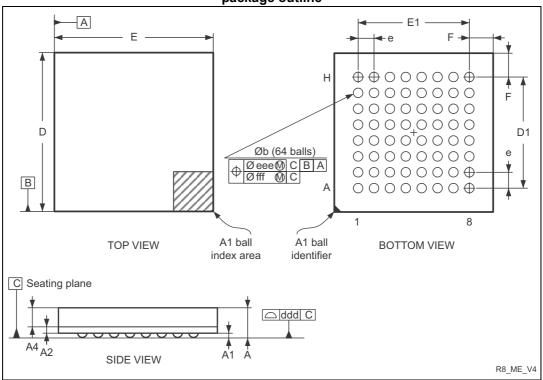

# 7.6 TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package information

Figure 45. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| Α      | -     | -           | 1.200 | -      | -                     | 0.0472 |

| A1     | 0.150 | -           | -     | 0.0059 | -                     | -      |

| A2     | -     | 0.200       | -     | -      | 0.0079                | -      |

| A4     | -     | -           | 0.600 | -      | -                     | 0.0236 |

| b      | 0.250 | 0.300       | 0.350 | 0.0098 | 0.0118                | 0.0138 |

| D      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| D1     | -     | 3.500       | -     | -      | 0.1378                | -      |

| Е      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| E1     | -     | 3.500       | -     | -      | 0.1378                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| F      | -     | 0.750       | -     | -      | 0.0295                | -      |

## 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O} \max = \sum (V_{OL} \times I_{OL}) + \sum ((V_{DD} - V_{OH}) \times I_{OH}),$$

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                               | Value | Unit   |

|---------------|-------------------------------------------------------------------------|-------|--------|

|               | Thermal resistance junction-ambient UFBGA100 - 7 x 7 mm                 | 59    |        |

|               | Thermal resistance junction-ambient LQFP100 - 14 x 14 mm / 0.5 mm pitch | 46    |        |

| $\Theta_{JA}$ | Thermal resistance junction-ambient TFBGA64 - 5 x 5 mm                  | 65    | - °C/W |

|               | Thermal resistance junction-ambient LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 45    |        |

|               | Thermal resistance junction-ambient LQFP48 - 7 x 7 mm / 0.5 mm pitch    | 55    |        |

|               | Thermal resistance junction-ambient UFQFPN48 - 7 x 7 mm / 0.5 mm pitch  | 33    |        |

Table 72. Thermal characteristics

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved