Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151r6t6a  |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |       | 3.15.1   | General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11)  | . 29       |

|---|-------|----------|-------------------------------------------------------------------|------------|

|   |       | 3.15.2   | Basic timers (TIM6 and TIM7)                                      | . 29       |

|   |       | 3.15.3   | SysTick timer                                                     | . 29       |

|   |       | 3.15.4   | Independent watchdog (IWDG)                                       | . 29       |

|   |       | 3.15.5   | Window watchdog (WWDG)                                            | . 30       |

|   | 3.16  | Commu    | unication interfaces                                              | 30         |

|   |       | 3.16.1   | I <sup>2</sup> C bus                                              | . 30       |

|   |       | 3.16.2   | Universal synchronous/asynchronous receiver transmitter (USART) . | . 30       |

|   |       | 3.16.3   | Serial peripheral interface (SPI)                                 | . 30       |

|   |       | 3.16.4   | Universal serial bus (USB)                                        | . 30       |

|   | 3.17  | CRC (c   | cyclic redundancy check) calculation unit                         | 31         |

|   | 3.18  | Develo   | pment support                                                     | 31         |

|   |       |          |                                                                   |            |

| 4 | Pin d | escripti | ions                                                              | 32         |

| 5 | Mom   | oru mar  | oping                                                             | <b>6</b> 1 |

| 5 | MEIII | ուծ արգ  | Jping                                                             | 51         |

| 6 | Elect | rical ch | aracteristics                                                     | 52         |

|   | 6.1   | Parame   | eter conditions                                                   | 52         |

|   |       | 6.1.1    | Minimum and maximum values                                        | . 52       |

|   |       | 6.1.2    | Typical values                                                    | . 52       |

|   |       | 6.1.3    | Typical curves                                                    | . 52       |

|   |       | 6.1.4    | Loading capacitor                                                 | . 52       |

|   |       | 6.1.5    | Pin input voltage                                                 | . 52       |

|   |       | 6.1.6    | Power supply scheme                                               | . 53       |

|   |       | 6.1.7    | Optional LCD power supply scheme                                  | . 54       |

|   |       | 6.1.8    | Current consumption measurement                                   | . 54       |

|   | 6.2   | Absolut  | te maximum ratings                                                | 55         |

|   | 6.3   | Operati  | ing conditions                                                    | 56         |

|   |       | 6.3.1    | General operating conditions                                      | . 56       |

|   |       | 6.3.2    | Embedded reset and power control block characteristics            | . 57       |

|   |       | 6.3.3    | Embedded internal reference voltage                               | . 59       |

|   |       | 6.3.4    | Supply current characteristics                                    | . 60       |

|   |       | 6.3.5    | Wakeup time from Low-power mode                                   | . 70       |

|   |       | 6.3.6    | External clock source characteristics                             | . 72       |

|   |       | 6.3.7    | Internal clock source characteristics                             | . 77       |

|   |       | 6.3.8    | PLL characteristics                                               | . 79       |

|   |       |          |                                                                   |            |

line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

Stop mode consumption: refer to *Table 23*.

• Standby mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

• **Standby** mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI, RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Standby mode consumption: refer to *Table 24*.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped by entering the Stop or Standby mode.

|                                                                      | Functionalities depending on the operating power supply range |                |                                   |                            |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|--|--|

| Operating power<br>supply range                                      | DAC and ADC<br>operation USB                                  |                | Dynamic voltage<br>scaling range  | I/O operation              |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V                                     | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup>                       | Not functional                                                | Not functional | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup> Conversion ti<br>up to 500 Ks |                                                               | Not functional | Range 1,<br>Range 2 or<br>Range 3 | Degraded speed performance |  |  |

#### Table 3. Functionalities depending on the operating power supply range

# 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

# 3.13 Routing interface

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.14 Touch sensing

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.13: Routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

# 3.15 Timers and watchdogs

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices include six general-purpose timers, two basic timers and two watchdog timers.

Table 7 compares the features of the general-purpose and basic timers.

DocID024330 Rev 4

|                        | Table 7. Timer feature comparison |                         |                                       |                        |                             |                          |  |  |

|------------------------|-----------------------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|--|--|

| Timer                  | Counter resolution                | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |

| TIM2,<br>TIM3,<br>TIM4 | 16-bit                            | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |  |  |

| TIM9                   | 16-bit                            | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | No                     | 2                           | No                       |  |  |

| TIM10,<br>TIM11        | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 1                           | No                       |  |  |

| TIM6,<br>TIM7          | 16-bit                            | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |  |  |

Table 7. Timer feature comparison

# 3.15.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit down-counter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.16 Communication interfaces

### 3.16.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

### 3.16.2 Universal synchronous/asynchronous receiver transmitter (USART)

All USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They provide hardware management of the CTS and RTS signals and are ISO 7816 compliant. They support IrDA SIR ENDEC and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

### 3.16.3 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

# 3.16.4 Universal serial bus (USB)

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices embed a USB device peripheral compatible with the USB full speed 12 Mbit/s. The USB interface implements a full speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

|         | Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued) |         |          |                    |          |                         | •             |                                                  |                                                              |                                      |

|---------|------------------------------------------------------------------------------|---------|----------|--------------------|----------|-------------------------|---------------|--------------------------------------------------|--------------------------------------------------------------|--------------------------------------|

|         | 1                                                                            | Pins    | ;        | 1                  |          |                         |               |                                                  | Pins functio                                                 | ns                                   |

| LQFP100 | LQFP64                                                                       | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                          | Additional<br>functions              |

| 51      | 33                                                                           | H8      | L12      | 25                 | PB12     | I/O                     | FT            | PB12                                             | SPI2_NSS/I2C2_SMBA/<br>USART3_CK/<br>LCD_SEG12/<br>TIM10_CH1 | ADC_IN18/<br>COMP1_INP<br>/VLCDRAIL2 |

| 52      | 34                                                                           | G8      | K12      | 26                 | PB13     | I/O                     | FT            | PB13                                             | SPI2_SCK/<br>USART3_CTS/<br>LCD_SEG13/TIM9_CH1               | ADC_IN19/<br>COMP1_INP               |

| 53      | 35                                                                           | F8      | K11      | 27                 | PB14     | I/O                     | FT            | PB14                                             | SPI2_MISO/<br>USART3_RTS/<br>LCD_SEG14/TIM9_CH2              | ADC_IN20/<br>COMP1_INP               |

| 54      | 36                                                                           | F7      | K10      | 28                 | PB15     | I/O                     | FT            | PB15                                             | SPI2_MOSI/<br>LCD_SEG15/<br>TIM11_CH1                        | ADC_IN21/<br>COMP1_INP/<br>RTC_REFIN |

| 55      | -                                                                            | -       | K9       | -                  | PD8      | I/O                     | FT            | PD8                                              | USART3_TX/<br>LCD_SEG28                                      | -                                    |

| 56      | -                                                                            | -       | K8       | -                  | PD9      | I/O                     | FT            | PD9                                              | USART3_RX/<br>LCD_SEG29                                      | -                                    |

| 57      | -                                                                            | -       | J12      | -                  | PD10     | I/O                     | FT            | PD10                                             | USART3_CK/<br>LCD_SEG30                                      | -                                    |

| 58      | -                                                                            | -       | J11      | -                  | PD11     | I/O                     | FT            | PD11                                             | USART3_CTS/<br>LCD_SEG31                                     | -                                    |

| 59      | -                                                                            | -       | J10      | -                  | PD12     | I/O                     | FT            | PD12                                             | TIM4_CH1/<br>USART3_RTS/<br>LCD_SEG32                        | -                                    |

| 60      | -                                                                            | -       | H12      | -                  | PD13     | I/O                     | FT            | PD13                                             | TIM4_CH2/LCD_SEG33                                           | -                                    |

| 61      | -                                                                            | -       | H11      | -                  | PD14     | I/O                     | FT            | PD14                                             | TIM4_CH3/LCD_SEG34                                           | -                                    |

| 62      | -                                                                            | -       | H10      | -                  | PD15     | I/O                     | FT            | PD15                                             | TIM4_CH4/LCD_SEG35                                           | -                                    |

| 63      | 37                                                                           | F6      | E12      | -                  | PC6      | I/O                     | FT            | PC6                                              | TIM3_CH1/LCD_SEG24                                           | -                                    |

| 64      | 38                                                                           | E7      | E11      | -                  | PC7      | I/O                     | FT            | PC7                                              | TIM3_CH2/LCD_SEG25                                           | -                                    |

| 65      | 39                                                                           | E8      | E10      | -                  | PC8      | I/O                     | FT            | PC8                                              | TIM3_CH3/LCD_SEG26                                           | -                                    |

| 66      | 40                                                                           | D8      | D12      | -                  | PC9      | I/O                     | FT            | PC9                                              | TIM3_CH4/LCD_SEG27                                           | -                                    |

# Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

DocID024330 Rev 4

# 6.3.3 Embedded internal reference voltage

The parameters given in the following table are based on characterization results, unless otherwise specified.

| Calibration value name | Description                                                                          | Memory address          |

|------------------------|--------------------------------------------------------------------------------------|-------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 30 °C ±5 °C,<br>V <sub>DDA</sub> = 3 V ±10 mV | 0x1FF8 0078-0x1FF8 0079 |

| Symbol                                  | Symbol Parameter                                                                             |                                    | Min   | Тур   | Max   | Unit                  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------|-------|-------|-------|-----------------------|--|

| V <sub>REFINT out</sub> (1)             | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +110 °C | 1.202 | 1.224 | 1.242 | V                     |  |

| I <sub>REFINT</sub>                     | Internal reference current consumption                                                       | -                                  | -     | 1.4   | 2.3   | μA                    |  |

| T <sub>VREFINT</sub>                    | Internal reference startup time                                                              | -                                  | -     | 2     | 3     | ms                    |  |

| V <sub>VREF_MEAS</sub>                  | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                  | 2.99  | 3     | 3.01  | V                     |  |

| A <sub>VREF_MEAS</sub>                  | Accuracy of factory-measured Vpr                                                             |                                    | -     | -     | ±5    | mV                    |  |

| T <sub>Coeff</sub> <sup>(3)</sup>       | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +110 °C  | -     | 25    | 100   | ppm/°C                |  |

| A <sub>Coeff</sub> <sup>(3)</sup>       | Long-term stability                                                                          | 1000 hours, T= 25 °C               | -     | -     | 1000  | ppm                   |  |

| V <sub>DDCoeff</sub> <sup>(3)(4)</sup>  | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V   | -     | -     | 2000  | ppm/V                 |  |

| T <sub>S_vrefint</sub> <sup>(3)</sup>   | ADC sampling time when reading the internal reference voltage                                | -                                  | 4     | -     | -     | μs                    |  |

| T <sub>ADC_BUF</sub> <sup>(3)</sup>     | Startup time of reference voltage buffer for ADC                                             | -                                  | -     | -     | 10    | μs                    |  |

| I <sub>BUF_ADC</sub> <sup>(3)</sup>     | Consumption of reference voltage buffer for ADC                                              | -                                  | -     | 13.5  | 25    | μA                    |  |

| I <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output current <sup>(5)</sup>                                                       | -                                  | -     | -     | 1     | μA                    |  |

| C <sub>VREF_OUT</sub> <sup>(3)</sup>    | VREF_OUT output load                                                                         | -                                  | -     | -     | 50    | pF                    |  |

| I <sub>LPBUF</sub> <sup>(3)</sup>       | Consumption of reference voltage buffer for VREF_OUT and COMP                                | -                                  | _     | 730   | 1200  | nA                    |  |

| V <sub>REFINT_DIV1</sub> <sup>(3)</sup> | 1/4 reference voltage                                                                        | -                                  | 24    | 25    | 26    |                       |  |

| V <sub>REFINT_DIV2</sub> <sup>(3)</sup> | 1/2 reference voltage                                                                        | -                                  | 49    | 50    | 51    | % V <sub>REFINT</sub> |  |

| V <sub>REFINT_DIV3</sub> <sup>(3)</sup> | 3/4 reference voltage                                                                        | -                                  | 74    | 75    | 76    | 1                     |  |

#### Table 17. Embedded internal reference voltage

1. Guaranteed by test in production.

2. The internal  $V_{\text{REF}}$  value is individually measured in production and stored in dedicated EEPROM bytes.

3. Guaranteed by characterization results.

4. Shortest sampling time can be determined in the application by multiple interactions.

5. To guarantee less than 1% VREF\_OUT deviation.

| Symbol                                         | Parameter                                          |                                              | Conditions                                      |                                         | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------------------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------|-----------------------------------------|------|--------------------|------|

|                                                |                                                    |                                              |                                                 | $T_A$ = -40 °C to 25 °C                 | 10.9 | 12                 |      |

|                                                |                                                    |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                  | 16.5 | 23                 |      |

|                                                |                                                    |                                              | HOLK V- WH                                      | T <sub>A</sub> = 105 °C                 | 26   | 47                 |      |

|                                                |                                                    | All peripherals<br>OFF, code                 |                                                 | $T_A$ = -40 °C to 25 °C                 | 15   | 16                 |      |

|                                                |                                                    | executed from<br>RAM, Flash                  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                  | 22   | 29                 |      |

|                                                |                                                    | switched OFF,                                | HOLK COMME                                      | T <sub>A</sub> = 105 °C                 | 32   | 51                 |      |

|                                                |                                                    | V <sub>DD</sub> from<br>1.65 V to 3.6 V      |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 29   | 37                 |      |

|                                                |                                                    | 1.00 V 10 0.0 V                              | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 32.5 | 40                 |      |

|                                                | Supply current in                                  |                                              | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 35.5 | 54                 | -    |

| I <sub>DD</sub>                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 45   | 65                 |      |

| (LP Run)                                       | Low-power<br>run mode                              | All peripherals<br>OFF, code                 | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A$ = -40 °C to 25 °C                 | 23   | 24                 |      |

|                                                | Tun mode                                           |                                              |                                                 | T <sub>A</sub> = 85 °C                  | 31   | 34                 | μA   |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 42.5 | 56                 |      |

|                                                |                                                    |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A$ = -40 °C to 25 °C                 | 29   | 31                 |      |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 85 °C                  | 38   | 41                 |      |

|                                                |                                                    | executed from<br>Flash, V <sub>DD</sub> from |                                                 | T <sub>A</sub> = 105 °C                 | 49   | 63                 | 1    |

|                                                |                                                    | 1.65 V to 3.6 V                              |                                                 | $T_A$ = -40 °C to 25 °C                 | 46   | 55                 |      |

|                                                |                                                    |                                              | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 48   | 59                 |      |

|                                                |                                                    |                                              | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 53.5 | 72                 |      |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 64.8 | 84                 |      |

| I <sub>DD</sub> Max<br>(LP Run) <sup>(2)</sup> | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to 3.6 V      | -                                               | -                                       | -    | 200                |      |

Table 21. Current consumption in Low-power run mode

1. Guaranteed by characterization results, unless otherwise specified.

2. This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

| Symbol                | Parameter                                          | C                                                                                                                              | onditions                                 |                                                                          | Typ <sup>(1)</sup> | Max<br>(1)(2) | Unit |

|-----------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------|--------------------|---------------|------|

|                       |                                                    |                                                                                                                                |                                           | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8 \text{ V}$ | 1.13               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.38               | 4             |      |

|                       |                                                    |                                                                                                                                | LCD OFF                                   | T <sub>A</sub> = 55°C                                                    | 1.70               | 6             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.30               | 10            |      |

|                       |                                                    | RTC clocked by LSI,                                                                                                            |                                           | T <sub>A</sub> = 105°C                                                   | 7.80               | 23            |      |

|                       |                                                    | regulator in LP mode, HSI                                                                                                      |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.50               | 6             |      |

|                       |                                                    | and HSE OFF<br>(no independent                                                                                                 | LCD ON<br>(static                         | T <sub>A</sub> = 55°C                                                    | 1.80               | 7             |      |

|                       |                                                    | watchdog)                                                                                                                      | duty) <sup>(3)</sup>                      | T <sub>A</sub> = 85°C                                                    | 3.45               | 12            |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 8.02               | 27            |      |

|                       |                                                    |                                                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.80               | 10            |      |

|                       |                                                    |                                                                                                                                | LCD ON<br>(1/8<br>duty) <sup>(4)</sup>    | T <sub>A</sub> = 55°C                                                    | 4.30               | 11            | - μΑ |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 6.10               | 16            |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 10.8               | 44            |      |

|                       | Supply ourront in                                  | RTC clocked by LSE<br>external clock (32.768<br>kHz), regulator in LP<br>mode, HSI and HSE OFF<br>(no independent<br>watchdog) | LCD OFF                                   | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.50               | -             |      |

| I <sub>DD (Stop</sub> | Supply current in<br>Stop mode with<br>RTC enabled |                                                                                                                                |                                           | T <sub>A</sub> = 55°C                                                    | 1.90               | -             |      |

| with RTC)             |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.65               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 8.25               | -             |      |

|                       |                                                    |                                                                                                                                | LCD ON<br>(static<br>duty) <sup>(3)</sup> | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.60               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 55°C                                                    | 2.05               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.75               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 8.40               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.90               | -             |      |

|                       |                                                    |                                                                                                                                | LCD ON<br>(1/8                            | T <sub>A</sub> = 55°C                                                    | 4.55               | -             |      |

|                       |                                                    |                                                                                                                                | duty) <sup>(4)</sup>                      | T <sub>A</sub> = 85°C                                                    | 6.35               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 11.10              | -             |      |

|                       |                                                    |                                                                                                                                |                                           | T <sub>A</sub> = -40°C to 25°C<br>V <sub>DD</sub> = 1.8 V                | 1.23               | -             |      |

|                       |                                                    | RTC clocked by LSE (no independent watchdog) <sup>(5)</sup>                                                                    | LCD OFF                                   | T <sub>A</sub> = -40°C to 25°C<br>V <sub>DD</sub> = 3.0 V                | 1.50               | -             |      |

|                       |                                                    |                                                                                                                                |                                           | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.6 \text{ V}$ | 1.75               | -             |      |

# Table 23. Typical and maximum current consumptions in Stop mode

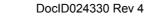

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

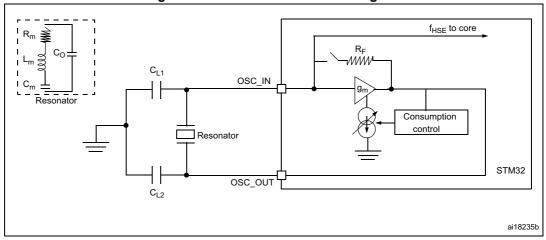

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 14*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>               | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>                      | Oscillator transconductance -                                                                 |                                       | 3   | -      | -   | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | $V_{DD}$ is stabilized                | -   | 1      | -   | S    |

| Table 30. LSE oscillator characteristics | ; (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small  $R_S$  value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- Caution: To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL ≤ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

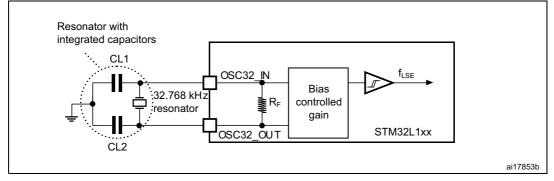

Figure 21. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistors

- 2.  $R_P$  = pull-up resistors

- 3.  $V_{DD_{12C}} = 12C$  bus supply

- 4. Measurement points are done at CMOS levels: 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

| £ (1.11-)              | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801B                  |

| 300                    | 0x8024                  |

| 200                    | 0x8035                  |

| 100                    | 0x00A0                  |

| 50                     | 0x0140                  |

| 20                     | 0x0320                  |

# Table 49. SCL frequency $(f_{PCLK1} = 32 \text{ MHz}, V_{DD} = V_{DD_12C} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol            | Parameter                                          | Conditions                                             | Min                                                       | ,<br>Тур | Мах     | Unit               |  |

|-------------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|----------|---------|--------------------|--|

|                   |                                                    | Direct channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V      | 0.25                                                      | -        | -       |                    |  |

|                   |                                                    | Multiplexed channels<br>2.4 V ≤V <sub>DDA</sub> ≤3.6 V | 0.56                                                      | -        | -       | μs                 |  |

| t <sub>S</sub>    | Sampling time <sup>(5)</sup>                       | Direct channels<br>1.8 V ≤V <sub>DDA</sub> ⊴2.4 V      | 0.56                                                      | -        |         |                    |  |

|                   |                                                    | Multiplexed channels<br>1.8 V ≤V <sub>DDA</sub> ≤2.4 V | 1                                                         | -        | -       |                    |  |

|                   |                                                    | -                                                      | 4                                                         | -        | 384     | 1/f <sub>ADC</sub> |  |

|                   |                                                    | f <sub>ADC</sub> = 16 MHz                              | 1                                                         | -        | 24.75   | μs                 |  |

| t <sub>CONV</sub> | Total conversion time<br>(including sampling time) | -                                                      | 4 to 384 (sampling<br>phase) +12 (succe<br>approximation) |          |         | 1/f <sub>ADC</sub> |  |

| Inte              | Internal sample and hold                           | Direct channels                                        | -                                                         | 16       | -       | ъĘ                 |  |

| C <sub>ADC</sub>  | capacitor                                          | Multiplexed channels                                   | -                                                         | 10       | -       | pF                 |  |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                         | -        | Tconv+1 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Regular sequencer                                  | 6/8/10-bit conversions                                 | -                                                         | -        | Tconv   | 1/f <sub>ADC</sub> |  |

| f                 | External trigger frequency                         | 12-bit conversions                                     | -                                                         | -        | Tconv+2 | 1/f <sub>ADC</sub> |  |

| f <sub>TRIG</sub> | Injected sequencer                                 | 6/8/10-bit conversions                                 | -                                                         | -        | Tconv+1 | 1/f <sub>ADC</sub> |  |

| R <sub>AIN</sub>  | Signal source impedance <sup>(5)</sup>             | -                                                      | -                                                         | -        | 50      | кΩ                 |  |

| +                 | Injection trigger conversion                       | f <sub>ADC</sub> = 16 MHz                              | 219                                                       | -        | 281     | ns                 |  |

| t <sub>lat</sub>  | latency                                            | -                                                      | 3.5                                                       | -        | 4.5     | 1/f <sub>ADC</sub> |  |

| t                 | Regular trigger conversion                         | f <sub>ADC</sub> = 16 MHz                              | 156                                                       | -        | 219     | ns                 |  |

| t <sub>latr</sub> | latency                                            | -                                                      | 2.5                                                       | -        | 3.5     | 1/f <sub>ADC</sub> |  |

| t <sub>STAB</sub> | Power-up time                                      | -                                                      | -                                                         | -        | 3.5     | μs                 |  |

Table 55. ADC characteristics (continued)

1. The V<sub>REF+</sub> input can be grounded if neither the ADC nor the DAC are used (this allows to shut down an external voltage reference).

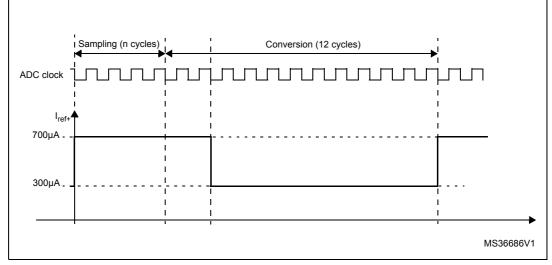

2. The current consumption through  $\mathsf{V}_{\mathsf{REF}}$  is composed of two parameters:

- one constant (max 300 µA)

- one variable (max 400  $\mu$ A), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700  $\mu A$  and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450  $\mu A$  at 1Msps

3. V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pin descriptions for further details.

4.  $V_{SSA}$  or  $V_{REF-}$  must be tied to ground.

5. See Table 57: Maximum source impedance RAIN max for  $\mathsf{R}_{\mathsf{AIN}}$  limitations

# Table 57. Maximum source impedance $R_{AIN} max^{(1)}$

|            | R <sub>AIN</sub> max (kOhm)      |                                  |                                  |                                                                                      |     |  |

|------------|----------------------------------|----------------------------------|----------------------------------|--------------------------------------------------------------------------------------|-----|--|

| Ts<br>(µs) | Multiplexe                       | d channels                       | Direct o                         | Direct channels<br>2.4 V < V <sub>DDA</sub> < 3.3 V 1.8 V < V <sub>DDA</sub> < 2.4 V |     |  |

|            | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.3 V |                                                                                      |     |  |

| 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                                                                          | 4   |  |

| 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                                                                                  | 9   |  |

| 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                                                                                  | 16  |  |

| 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                                                                                  | 24  |  |

| 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                                                                                 | 48  |  |

| 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                                                                                 | 96  |  |

| 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                                                                                 | 192 |  |

| 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                                                                                 | 384 |  |

1. Guaranteed by design.

2. Number of samples calculated for  $f_{ADC}$  = 16 MHz. For  $f_{ADC}$  = 8 and 4 MHz the number of sampling cycles can be reduced with respect to the minimum sampling time Ts (us).

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 12*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 100 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

| Symbol              | Parameter                                                                                                                                                    | Conditions                                                                           | Min | Тур             | Max              | Unit    |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------|------------------|---------|--|

|                     | Offset error temperature                                                                                                                                     | $V_{DDA} = 3.3V, V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF    | -20 | -10             | 0                | - µV/°C |  |

|                     | coefficient (code 0x800)                                                                                                                                     | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | 0   | 20              | 50               |         |  |

| Gain <sup>(1)</sup> | Gain error <sup>(6)</sup>                                                                                                                                    | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON           | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% |         |  |

| Gainty              | Gainenor                                                                                                                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | +0 / -<br>0.2%  | +0 / -<br>0.4%   | . %     |  |

| $\alpha_{\alpha}$   | Gain error temperature                                                                                                                                       | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF | -10 | -2              | 0                |         |  |

|                     | coefficient                                                                                                                                                  | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | -40 | -8              | 0                | µV/°C   |  |

| TUE <sup>(1)</sup>  | Total unadjusted error                                                                                                                                       | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON          | -   | 12              | 30               | – LSB   |  |

| TUE                 |                                                                                                                                                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | 8               | 12               |         |  |

| tSETTLING           | Settling time (full scale: for a<br>12-bit code transition<br>between the lowest and the<br>highest input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 7               | 12               | μs      |  |

| Update rate         | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -               | 1                | Msps    |  |

| t <sub>WAKEUP</sub> | Wakeup time from off state<br>(setting the ENx bit in the<br>DAC Control register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 9               | 15               | μs      |  |

| PSRR+               | V <sub>DDA</sub> supply rejection ratio (static DC measurement)                                                                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -60             | -35              | dB      |  |

Table 58. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 5. Difference between the value measured at Code (0x001) and the ideal value.

- 6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

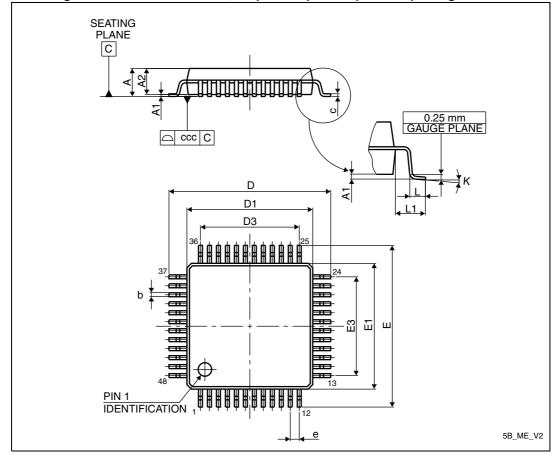

# 7.3 LQFP48 7 x 7 mm, 48-pin low-profile quad flat package information

Figure 36. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline

1. Drawing is not to scale.

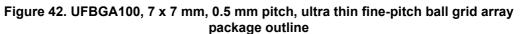

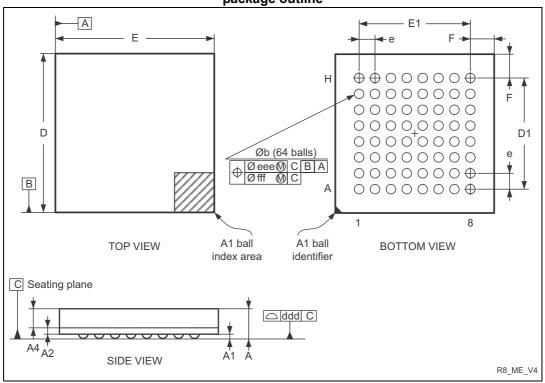

# 7.5 UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package information

1. Drawing is not to scale.

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |

|----------------------------------------------------------------------------------|

| package mechanical data                                                          |

|        | millimeters |      |      | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|------|------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур  | Max  | Min                   | Тур    | Max    |  |

| А      | -           | -    | 0.6  | -                     | -      | 0.0236 |  |

| A1     | 0.05        | 0.08 | 0.11 | 0.002                 | 0.0031 | 0.0043 |  |

| A2     | 0.4         | 0.45 | 0.5  | 0.0157                | 0.0177 | 0.0197 |  |

| A3     | 0.08        | 0.13 | 0.18 | 0.0031                | 0.0051 | 0.0071 |  |

| A4     | 0.27        | 0.32 | 0.37 | 0.0106                | 0.0126 | 0.0146 |  |

| b      | 0.2         | 0.25 | 0.3  | 0.0079                | 0.0098 | 0.0118 |  |

| D      | 6.95        | 7    | 7.05 | 0.2736                | 0.2756 | 0.2776 |  |

| D1     | 5.45        | 5.5  | 5.55 | 0.2146                | 0.2165 | 0.2185 |  |

| Е      | 6.95        | 7    | 7.05 | 0.2736                | 0.2756 | 0.2776 |  |

| E1     | 5.45        | 5.5  | 5.55 | 0.2146                | 0.2165 | 0.2185 |  |

| е      | -           | 0.5  | -    | -                     | 0.0197 | -      |  |

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |  |

|----------------------------------------------------------------------------------|--|

| package mechanical data (continued)                                              |  |

| Symbol | millimeters |      |      | inches <sup>(1)</sup> |        |        |

|--------|-------------|------|------|-----------------------|--------|--------|

| Symbol | Min         | Тур  | Max  | Min                   | Тур    | Max    |

| F      | 0.7         | 0.75 | 0.8  | 0.0276                | 0.0295 | 0.0315 |

| ddd    | -           | -    | 0.1  | -                     | -      | 0.0039 |

| eee    | -           | -    | 0.15 | -                     | -      | 0.0059 |

| fff    | -           | -    | 0.05 | -                     | -      | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

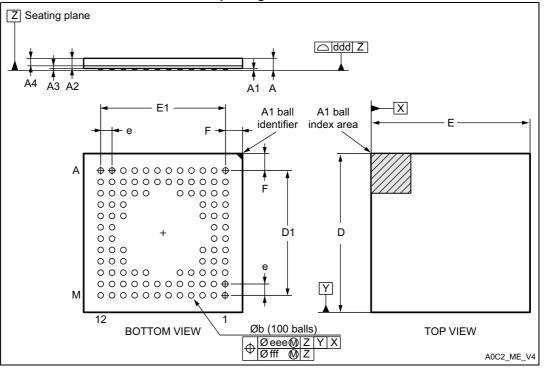

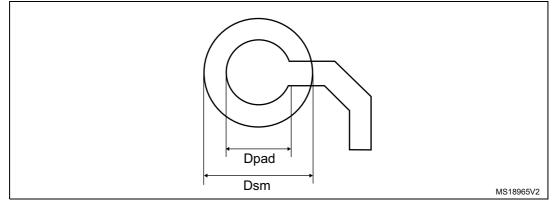

# Figure 43. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package recommended footprint

#### Table 69. UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

#### **Package information**

# 7.6 TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package information

Figure 45. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |

|---------------------------------------------------------------------------|

| package mechanical data                                                   |

| Ourseland I |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|-------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol      | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |

| А           | -     | -           | 1.200 | -                     | -      | 0.0472 |  |

| A1          | 0.150 | -           | -     | 0.0059                | -      | -      |  |

| A2          | -     | 0.200       | -     | -                     | 0.0079 | -      |  |

| A4          | -     | -           | 0.600 | -                     | -      | 0.0236 |  |

| b           | 0.250 | 0.300       | 0.350 | 0.0098                | 0.0118 | 0.0138 |  |

| D           | 4.850 | 5.000       | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| D1          | -     | 3.500       | -     | -                     | 0.1378 | -      |  |

| E           | 4.850 | 5.000       | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| E1          | -     | 3.500       | -     | -                     | 0.1378 | -      |  |

| е           | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| F           | -     | 0.750       | -     | -                     | 0.0295 | -      |  |

DocID024330 Rev 4

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |  |

|---------------------------------------------------------------------------|--|

| package mechanical data (continued)                                       |  |

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

|        | Min         | Тур | Мах   | Min                   | Тур | Мах    |

| ddd    | -           | -   | 0.080 | -                     | -   | 0.0031 |

| eee    | -           | -   | 0.15  | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.05  | -                     | -   | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

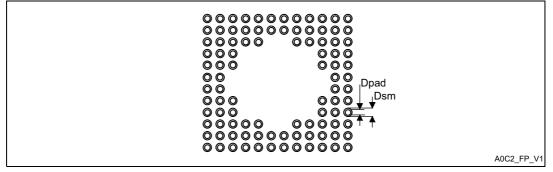

# Figure 46. TFBGA64, 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package recommended footprint

#### Table 71. TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |