Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT  |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP                                                                  |

| Supplier Device Package    | 64-LQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151r8t6atr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From a proprietary 8bit core up to the Cortex-M3, including the Cortex-M0+, the STM8Lx and STM32Lx series offer the best range of choices to meet your requirements in terms of ultra-low-power features. The STM32 Ultra-low-power series is an ideal fit for applications like gas/water meters, keyboard/mouse, or wearable devices for fitness and healthcare. Numerous built-in features like LCD drivers, dual-bank memory, low-power Run mode, op-amp, AES-128bit, DAC, crystal-less USB and many others, allow to build highly cost-optimized applications by reducing the BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lx and STM32Lx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, your existing applications can be upgraded to respond to the latest market features and efficiency demand.

## 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-Low-power performance to range from 5 up to 33.3 DMIPs.

## 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

### 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xxx and STM32L1xxxx families use a common architecture:

- Common power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xxx devices)

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultra-safe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 512 Kbytes

DocID024330 Rev 4

# 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rail decoupling capability

|                       |                      | Bias                 | Р                    | <b>1</b> 4 |      |  |

|-----------------------|----------------------|----------------------|----------------------|------------|------|--|

|                       | 1/2                  | 1/3                  | 1/4                  | Pin        |      |  |

| V <sub>LCDrail1</sub> | 1/2 V <sub>LCD</sub> | 2/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | PB2        |      |  |

| V <sub>LCDrail2</sub> | NA                   | 1/3 V <sub>LCD</sub> | 1/4 V <sub>LCD</sub> | PB12       | PE11 |  |

| V <sub>LCDrail3</sub> | NA                   | NA                   | 3/4 V <sub>LCD</sub> | PB0        | PE12 |  |

#### Table 6. V<sub>LCD</sub> rail decoupling

# 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151x6/8/B-A and STM32L152x6/8/B-A devices with up to 24 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

#### 3.10.1 Temperature sensor

The temperature sensor  $T_{\text{SENSE}}$  generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode, see *Table 59: Temperature sensor calibration values*.

## 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode see *Table 17: Embedded internal reference voltage*.

# 3.11 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 4 Pin descriptions

|   | 1                  | 2              | 3     | 4      | 5     | 6     | 7        | 8      | 9             | 10            | 11     | 12           |          |

|---|--------------------|----------------|-------|--------|-------|-------|----------|--------|---------------|---------------|--------|--------------|----------|

|   |                    |                |       |        |       |       |          |        |               |               |        |              |          |

| A | (PE3)              | (PE1)          | (PB8) | iBOOTO | (PD7) | (PD5) | (PB4)    | (PB3)  | (PA15)        | (PA14)        | (PA13) | (PA12)       |          |

| в | (PE4)              | (PE2)          | (PB9) | (PB7)  | (PB6) | (PD6) | (PD4)    | (PD3)  | /-\<br>(PD1)  | PC12)         | (PC10) | (PA11)       |          |

| С | PC13<br>WKUP2      | (PE5)          | (PEO) | VDD_B  | (PB5) |       | '<br>    | (PD2)  | (PD0)         | PC11)         | (PH2)  | (PA10)       |          |

| D | PC14)<br>0\$C32_IN | PE6)<br>WUKP3  | ŃSS_B |        |       |       |          |        |               | (PA9)         | (PA8)  | (PC9)        |          |

| E | PC15)<br>OSC32_C   | VLCD           | NSS_H |        |       |       |          |        |               | (PC8)         | (PC7)  | (PC6)        |          |

| F | PHO<br>QSCZIN      | a zzvi         |       |        |       |       | 1        |        |               |               | NSS_P  | vss_1        |          |

| G | PH1)               |                |       |        |       |       | ⊢ −<br>' |        |               |               |        | אַרַם אַ     |          |

| н | (PC0)              | INRST          |       |        |       |       |          |        |               | PD15)         | PD14)  | (PD13)       |          |

| J | VSSA)              | (PC1)          | (PC2) |        |       |       |          |        |               | PD12)         | (PD11) | (PD10)       |          |

| к | VREF               | (PC3)          | (PA2) | (PA5)  | (PC4) |       |          | (PD9)  | (PD8)         | (PB15)        | (PB14) | (PB13)       |          |

| L | (VRE俳+             | (PA0)<br>WKUP1 | (PA3) | (PA6)  | (PC5) | (PB2) | (PE8)    | (PE10) | /=\<br>IPE12  | (PB10)        | (PB11) | (PB12)       |          |

| м | NDDA               | (PA1)          | (PA4) | (PA7)  | (PB0) | (PB1) | (PE7)    | (PE9)  | /=\<br>(PE11) | /-\<br>(PE13) | PE14   | /~\<br>(PE19 |          |

|   |                    |                |       |        |       |       |          |        |               |               |        |              |          |

|   |                    |                |       |        |       |       |          |        |               |               |        |              | ai17096f |

#### Figure 3. STM32L15xVxxxA UFBGA100 ballout

1. This figure shows the package top view.

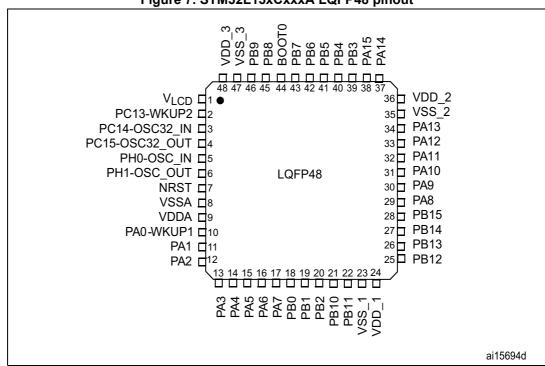

Figure 7. STM32L15xCxxxA LQFP48 pinout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functio                                  | ,                                                |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                           | Additional<br>functions                          |

| 35      | 26     | F5      | M5       | 18                 | PB0               | I/O                     | TC            | PB0                                              | TIM3_CH3/<br>LCD_SEG5                         | ADC_IN8/<br>COMP1_INP/<br>VREF_OUT<br>/VLCDRAIL3 |

| 36      | 27     | G5      | M6       | 19                 | PB1               | I/O                     | FT            | PB1                                              | TIM3_CH4/<br>LCD_SEG6                         | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT               |

| 37      | 28     | G6      | L6       | 20                 | PB2               | I/O                     | FT            | PB2/<br>BOOT1                                    | BOOT1                                         | VLCDRAIL1                                        |

| 38      | -      | -       | M7       | -                  | PE7               | I/O                     | тс            | PE7                                              | -                                             | ADC_IN22/<br>COMP1_INP                           |

| 39      | -      | -       | L7       | -                  | PE8               | I/O                     | тС            | PE8                                              | -                                             | ADC_IN23/<br>COMP1_INP                           |

| 40      | -      | -       | M8       | -                  | PE9               | I/O                     | тС            | PE9                                              | TIM2_CH1_ETR                                  | ADC_IN24/<br>COMP1_INP                           |

| 41      | -      | -       | L8       | -                  | PE10              | I/O                     | тС            | PE10                                             | TIM2_CH2                                      | ADC_IN25/<br>COMP1_INP                           |

| 42      | -      | -       | M9       | -                  | PE11              | I/O                     | FT            | PE11                                             | TIM2_CH3                                      | VLCDRAIL2                                        |

| 43      | -      | -       | L9       | -                  | PE12              | I/O                     | FT            | PE12                                             | TIM2_CH4/<br>SPI1_NSS                         | VLCDRAIL3                                        |

| 44      | -      | -       | M10      | -                  | PE13              | I/O                     | FT            | PE13                                             | SPI1_SCK                                      | -                                                |

| 45      | -      | -       | M11      | -                  | PE14              | I/O                     | FT            | PE14                                             | SPI1_MISO                                     | -                                                |

| 46      | -      | -       | M12      | -                  | PE15              | I/O                     | FT            | PE15                                             | SPI1_MOSI                                     | -                                                |

| 47      | 29     | G7      | L10      | 21                 | PB10              | I/O                     | FT            | PB10                                             | I2C2_SCL/USART3_TX<br>/TIM2_CH3/<br>LCD_SEG10 | -                                                |

| 48      | 30     | H7      | L11      | 22                 | PB11              | I/O                     | FT            | PB11                                             | I2C2_SDA/USART3_RX<br>/TIM2_CH4/<br>LCD_SEG11 | -                                                |

| 49      | 31     | D6      | F12      | 23                 | V <sub>SS_1</sub> | S                       | -             | V <sub>SS_1</sub>                                | -                                             | -                                                |

| 50      | 32     | E6      | G12      | 24                 | V <sub>DD_1</sub> | S                       | -             | $V_{DD_1}$                                       | -                                             | -                                                |

# Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functio            | ns                      |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|-------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions     | Additional<br>functions |

| 98      | -      | -       | A2       | -                  | PE1               | I/O                     | FT            | PE1                                              | LCD_SEG37/<br>TIM11_CH1 | -                       |

| 99      | 63     | D4      | D3       | 47                 | V <sub>SS_3</sub> | S                       | -             | V <sub>SS_3</sub>                                | -                       | -                       |

| 100     | 64     | E4      | C4       | 48                 | V <sub>DD_3</sub> | S                       | -             | V <sub>DD_3</sub>                                | -                       | -                       |

#### Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

3. Applicable to STM32L152xxxxA devices only. In STM32L151xxxxA devices, this pin should be connected to V<sub>DD</sub>.

4. The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

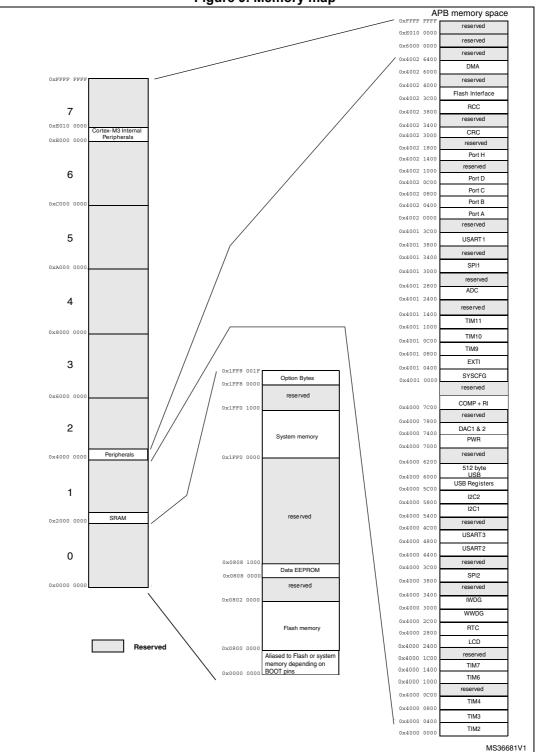

# 5 Memory mapping

The memory map is shown in the following figure.

DocID024330 Rev 4

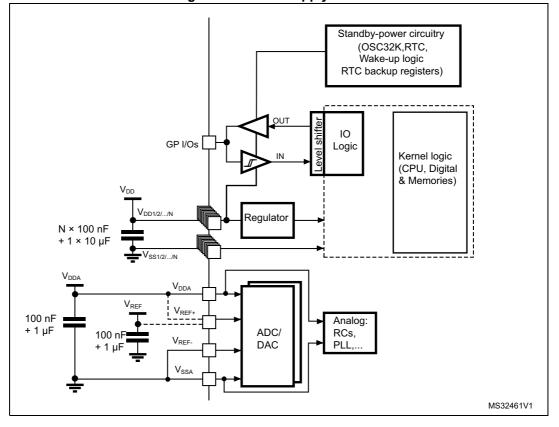

## 6.1.6 Power supply scheme

#### Figure 12. Power supply scheme

| Symbol                            | Parameter                                                  | Conditions                                 |                                                              |                                         | Тур  | Max<br>(1) | Unit |

|-----------------------------------|------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|-----------------------------------------|------|------------|------|

|                                   |                                                            |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash OFF | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 5.5  | -          |      |

|                                   |                                                            |                                            | MSI clock, 65 kHz                                            | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 32 kHz                                   | T <sub>A</sub> = 85 °C                  | 20   | 23         |      |

|                                   | Supply<br>current in<br>Low-power<br>sleep<br>mode         | All                                        | Flash ON                                                     | T <sub>A</sub> = 105 °C                 | 24   | 26         |      |

|                                   |                                                            | peripherals<br>OFF, V <sub>DD</sub>        | $f_{HCLK} = 65 \text{ kHz},$                                 | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            | from 1.65 V<br>to 3.6 V                    |                                                              | T <sub>A</sub> = 85 °C                  | 20.5 | 23         |      |

|                                   |                                                            | 10 3.0 V                                   |                                                              | T <sub>A</sub> = 105 °C                 | 25.4 | 27         |      |

|                                   |                                                            |                                            | MSI clock, 131 kHz                                           | $T_A$ = -40 °C to 25 °C                 | 18   | 20         |      |

| I <sub>DD</sub> (LP<br>Sleep)     |                                                            |                                            |                                                              | T <sub>A</sub> = 55 °C                  | 21   | 22         | μΑ   |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 131 kHz,<br>Flash ON                     | T <sub>A</sub> = 85 °C                  | 23   | 27         |      |

|                                   |                                                            |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 28   | 31         |      |

|                                   |                                                            |                                            |                                                              | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz              | T <sub>A</sub> = 85 °C                  | 20   | 22         |      |

|                                   |                                                            |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 24   | 26         |      |

|                                   |                                                            | TIM9 and USART1                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz              | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            | enabled,                                   |                                                              | T <sub>A</sub> = 85 °C                  | 20.5 | 23         | 1    |

|                                   |                                                            | Flash ON,<br>V <sub>DD</sub> from          | HCLK - 00 KHZ                                                | T <sub>A</sub> = 105 °C                 | 25.4 | 27         |      |

|                                   |                                                            | 1.65 V to<br>3.6 V                         |                                                              | $T_A$ = -40 °C to 25 °C                 | 18   | 20         |      |

|                                   |                                                            | 5.0 V                                      | MSI clock, 131 kHz                                           | T <sub>A</sub> = 55 °C                  | 21   | 22         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 131 kHz                                  | T <sub>A</sub> = 85 °C                  | 23   | 27         |      |

|                                   |                                                            |                                            |                                                              | T <sub>A</sub> = 105 °C                 | 28   | 30         |      |

| I <sub>DD</sub> Max<br>(LP Sleep) | Max<br>allowed<br>current in<br>Low-power<br>Sleep<br>mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                                            | -                                       | -    | 200        |      |

Table 22. Current consumption in Low-power sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

|                  |            |                                                                                         |                             | Max vs                      |                              |                              |      |  |

|------------------|------------|-----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------|--|

| Symbol           | Parameter  | Conditions                                                                              | Monitored<br>frequency band | 4 MHz<br>voltage<br>Range 3 | 16 MHz<br>voltage<br>Range 2 | 32 MHz<br>voltage<br>Range 1 | Unit |  |

|                  |            | $V_{DD}$ = 3.3 V,<br>$T_A$ = 25 °C,<br>LQFP100 package<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz               | -16                         | -7                           | -3                           |      |  |

| 6                | Peak level |                                                                                         | 30 to 130 MHz               | -12                         | 2                            | 12                           | dBµV |  |

| S <sub>EMI</sub> | reakievei  |                                                                                         | 130 MHz to 1GHz             | -11                         | 0                            | 8                            |      |  |

|                  |            |                                                                                         | SAE EMI Level               | 1                           | 1.5                          | 2                            | -    |  |

#### Table 39. EMI characteristics

### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the JESD22-A114, ANSI/ESD STM5.3.1 standard.

| Symbol                | Ratings                                               | Conditions                                         | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------|----------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25$ °C, conforming to JESD22-A114          | All      | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25$ °C, conforming to<br>ANSI/ESD STM5.3.1 | All      | C4    | 500                             | V    |

#### Table 40. ESD absolute maximum ratings

1. Guaranteed by characterization results.

# 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                          | Conditions                                                                                | Min                                       | Тур                                | Max                                   | Unit |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------|------|

| .,               |                                                    | TC and FT I/O                                                                             | -                                         | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |      |

| $V_{IL}$         | Input low level voltage                            | BOOT0                                                                                     | -                                         |                                    | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |      |

|                  |                                                    | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup> | -                                  | -                                     |      |

| $V_{\text{IH}}$  | Input high level voltage                           | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup> | -                                  | -                                     | V    |

|                  |                                                    | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup> | -                                  | -                                     |      |

| V                | I/O Schmitt trigger voltage                        | TC and FT I/O                                                                             | -                                         | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |      |

| V <sub>hys</sub> | hysteresis <sup>(2)</sup>                          | BOOT0                                                                                     | -                                         | 0.01                               | -                                     |      |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                        | -                                         | -                                  | ±50                                   |      |

|                  | Input leakage current <sup>(4)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches         | -                                         | -                                  | ±50                                   |      |

| l <sub>ikg</sub> |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                         | -                                  | ±50                                   | nA   |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                         | -                                  | ±250                                  |      |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/O                        | -                                         | -                                  | ±50                                   |      |

|                  |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                            | -                                         | -                                  | ±10                                   | uA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)(1)</sup> | $V_{IN} = V_{SS}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                         | -                                         | 5                                  | -                                     | pF   |

| Table 43. I/C | static) | characteristics |

|---------------|---------|-----------------|

|---------------|---------|-----------------|

1. Guaranteed by test in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

#### 6.3.16 Communication interfaces

## I<sup>2</sup>C interface characteristics

The STM32L151x6/8/B-A and STM32L152x6/8/B-A product line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            |     | rd mode<br>1)(2)    | Fast mode | e l <sup>2</sup> C <sup>(1)(2)</sup> | Unit |  |

|--------------------------------------------|----------------------------------------------------------------------|-----|---------------------|-----------|--------------------------------------|------|--|

|                                            |                                                                      | Min | Мах                 | Min       | Мах                                  |      |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7 | -                   | 1.3       | -                                    |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0 | -                   | 0.6       | -                                    | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250 | -                   | 100       | -                                    |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -   | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup>                   |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -   | 1000                | -         | 300                                  | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -   | 300                 | -         | 300                                  |      |  |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0 | -                   | 0.6       | -                                    |      |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7 | -                   | 0.6       | -                                    | μs   |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0 | -                   | 0.6       | -                                    | μs   |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7 | -                   | 1.3       | -                                    | μs   |  |

| Cb                                         | Capacitive load for each bus line                                    | -   | 400                 | -         | 400                                  | pF   |  |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0   | 50 <sup>(4)</sup>   | 0         | 50 <sup>(4)</sup>                    | ns   |  |

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

## 6.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 55* are guaranteed by design.

| Symbol           | Parameter              | Conditions     |                                |                                                                   | Min | Max | Unit |

|------------------|------------------------|----------------|--------------------------------|-------------------------------------------------------------------|-----|-----|------|

|                  |                        |                |                                | $V_{REF+} = V_{DDA}$                                              |     | 16  |      |

| f <sub>ADC</sub> |                        | Voltage        | 2.4 V ≤V <sub>DDA</sub> ≤3.6 V | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> > 2.4 V |     | 8   |      |

|                  | ADC clock<br>frequency | Range 1 &<br>2 |                                | V <sub>REF+</sub> < V <sub>DDA</sub><br>V <sub>REF+</sub> ≤2.4 V  |     | 4   | MHz  |

|                  | -                      | 1.             | 1.8 V ⊴V <sub>DDA</sub> ⊴2.4 V | V <sub>REF+ =</sub> V <sub>DDA</sub>                              | 8   |     |      |

|                  |                        |                |                                | $V_{REF+} < V_{DDA}$                                              |     | 4   |      |

|                  |                        |                | Voltage Range 3                |                                                                   |     | 4   |      |

Table 54. ADC clock frequency

#### Table 55. ADC characteristics

|                                  |                                           |                                                                                                   |                    |           |                  | r      |  |

|----------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|-----------|------------------|--------|--|

| Symbol                           | Parameter                                 | Conditions                                                                                        | Min                | Тур       | Max              | Unit   |  |

| $V_{DDA}$                        | Power supply                              | -                                                                                                 | 1.8                | -         | 3.6              | V      |  |

| V <sub>REF+</sub>                | Positive reference voltage                | 2.4 V ⊴V <sub>DDA</sub> ≤3.6 V<br>V <sub>REF+</sub> must be below<br>or equal to V <sub>DDA</sub> | 1.8 <sup>(1)</sup> | -         | V <sub>DDA</sub> | v      |  |

| $V_{REF-}$                       | Negative reference voltage                | -                                                                                                 | -                  | $V_{SSA}$ | -                | V      |  |

| I <sub>VDDA</sub>                | Current on the V <sub>DDA</sub> input pin | -                                                                                                 | -                  | 1000      | 1450             | μA     |  |

| ı (2)                            | Current on the V <sub>REF</sub> input     | Peak                                                                                              | -                  | 400       | 700              | μA     |  |

| I <sub>VREF</sub> <sup>(2)</sup> | pin                                       | Average                                                                                           | -                  | 400       | 450              | μA     |  |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                                                                                                 | 0 <sup>(4)</sup>   | -         | $V_{REF}$ +      | V      |  |

|                                  | 12-bit sampling rate                      | Direct channels                                                                                   | -                  | - 1       |                  | Mene   |  |

|                                  |                                           | Multiplexed channels                                                                              | -                  | -         | 0.76             | - Msps |  |

|                                  | 10 hit compling rate                      | Direct channels                                                                                   | -                  | -         | 1.07             | Mana   |  |

| f                                | 10-bit sampling rate                      | Multiplexed channels                                                                              | -                  | -         | 0.8              | - Msps |  |

| f <sub>S</sub>                   | 9 hit compling rate                       | Direct channels                                                                                   | -                  | -         | 1.23             | Mana   |  |

|                                  | 8-bit sampling rate                       | Multiplexed channels                                                                              | -                  | -         | 0.89             | Msps   |  |

|                                  | 6-bit sampling rate                       | Direct channels                                                                                   | -                  | -         | 1.45             | Msps   |  |

|                                  |                                           | Multiplexed channels                                                                              | -                  | -         | 1                | wisha  |  |

| Symbol | Parameter                            | Test conditions                                                                        | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|----------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                        | -                  | 2.5 | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                            | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤ V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                        | -                  | 2   | 3                  |      |

| ENOB   | Effective number of bits             | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                       | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+}$<br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω             | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | $T_A = -40$ to 105 ° C                                                                 | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                             | -                  | -72 | -69                |      |

| ENOB   | Effective number of bits             | $1.8 \text{ V} \le \text{V}_{\text{DDA}} \le 2.4 \text{ V}$                            | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+}$<br>$f_{ADC} = 8 MHz \text{ or } 4 MHz,$                           | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | — R <sub>AIN</sub> = 50 Ω<br>_ T <sub>A</sub> = -40 to 105 ° C                         | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                             | -                  | -72 | -69                |      |

| ET     | Total unadjusted error               |                                                                                        | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                            | -                  | 1.5 | 3.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 3.5 | 6                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                        | -                  | 2.5 | 3.5                |      |

| ET     | Total unadjusted error               |                                                                                        | -                  | 2   | 3                  |      |

| EO     | Offset error                         | $1.8 \text{ V} \le \text{V}_{\text{DDA}} \le 2.4 \text{ V}$                            | -                  | 1   | 1.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 1.5 | 2.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  | 1    |

| EL     | Integral linearity error             |                                                                                        | -                  | 2   | 3                  |      |

Table 56. ADC accuracy<sup>(1)(2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

#### Figure 26. ADC accuracy characteristics

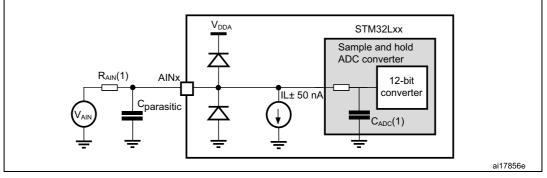

#### Figure 27. Typical connection diagram using the ADC

- 1. Refer to Table 57: Maximum source impedance RAIN max for the value of RAIN and Table 55: ADC characteristics for the value of CADC

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

| Symbol              | Parameter                                     | Conditions                                                                                                                                             | Min  | Тур | Max <sup>(1)</sup> | Unit       |  |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|--|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                                      | 1.65 | -   | 3.6                | V          |  |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                      | 0    | -   | V <sub>DDA</sub>   | V          |  |

| t                   | Comparator startup time                       | Fast mode                                                                                                                                              | -    | 15  | 20                 |            |  |

| t <sub>start</sub>  |                                               | Slow mode                                                                                                                                              | -    | 20  | 25                 |            |  |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                        | -    | 1.8 | 3.5                | μs         |  |

| t <sub>d slow</sub> | Fropagation delay 7 in slow mode              | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                         | -    | 2.5 | 6                  |            |  |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V                                                                                                                        | -    | 0.8 | 2                  |            |  |

| t <sub>d fast</sub> | Fropagation delay 7 in last mode              | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                         | -    | 1.2 | 4                  |            |  |

| V <sub>offset</sub> | Comparator offset error                       | -                                                                                                                                                      | -    | ±4  | ±20                | mV         |  |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$<br>$T_{A} = 0 \text{ to } 50 ^{\circ}\text{C}$<br>$V_{-} = V_{REFINT},$<br>$3/4 V_{REFINT},$<br>$1/2 V_{REFINT},$<br>$1/4 V_{REFINT}$ | -    | 15  | 100                | ppm<br>/°C |  |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                              | -    | 3.5 | 5                  |            |  |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                              | -    | 0.5 | 2                  | μA         |  |

| Table 62. Comparator 2 characteristics |

|----------------------------------------|

|----------------------------------------|

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min         | Тур    | Мах    | Min                   | Тур    | Мах    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 64. LQPF100 14 x 14 mm, 100-pin low-profile quad flat package |  |  |  |  |  |

|---------------------------------------------------------------------|--|--|--|--|--|

| mechanical data                                                     |  |  |  |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

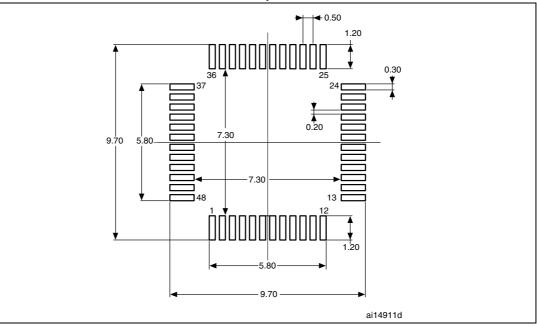

Figure 37. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

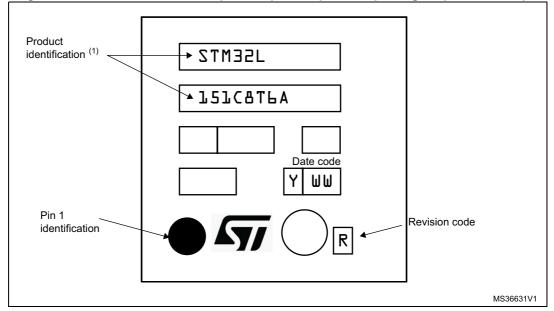

#### LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID024330 Rev 4

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |  |

|---------------------------------------------------------------------------|--|

| package mechanical data (continued)                                       |  |

| Symbol | millimeters |     |       |     |     |        |

|--------|-------------|-----|-------|-----|-----|--------|

| Symbol | Min         | Тур | Мах   | Min | Тур | Мах    |

| ddd    | -           | -   | 0.080 | -   | -   | 0.0031 |

| eee    | -           | -   | 0.15  | -   | -   | 0.0059 |

| fff    | -           | -   | 0.05  | -   | -   | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

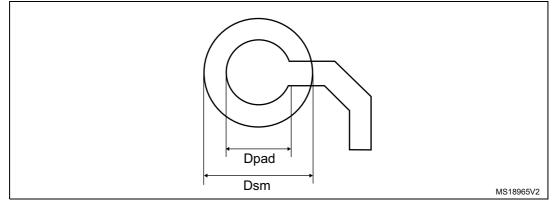

# Figure 46. TFBGA64, 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package recommended footprint

#### Table 71. TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |