Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-TFBGA                                                                |

| Supplier Device Package    | 64-TFBGA (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rbh6a  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9 | Revi | sion his            | tory                                                                                                   |  |  |  |  |  |

|---|------|---------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 8 | Orde | ering inf           | ormation                                                                                               |  |  |  |  |  |

|   |      | 7.7.1               | Reference document                                                                                     |  |  |  |  |  |

|   | 7.7  | Therma              | al characteristics                                                                                     |  |  |  |  |  |

|   | 7.6  |                     | A64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid ackage information 121                           |  |  |  |  |  |

|   | 7.5  |                     | A100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball and package information                        |  |  |  |  |  |

|   | 7.4  | UFQFF               | PN48 7 x 7 mm, 0.5 mm pitch, package information                                                       |  |  |  |  |  |

|   | 7.3  | LQFP4               | 8 7 x 7 mm, 48-pin low-profile quad flat package information112                                        |  |  |  |  |  |

|   | 7.2  | LQFP6               | 4 10 x 10 mm, 64-pin low-profile quad flat package information . 109                                   |  |  |  |  |  |

|   | 7.1  |                     | 00 14 x 14 mm, 100-pin low-profile quad flat package ation                                             |  |  |  |  |  |

| 7 | Pack | Package information |                                                                                                        |  |  |  |  |  |

|   |      | 6.3.21              | LCD controller (STM32L152x6/8/B-A devices only) 105                                                    |  |  |  |  |  |

|   |      | 6.3.20              | Comparator                                                                                             |  |  |  |  |  |

|   |      | 6.3.19              | Temperature sensor characteristics                                                                     |  |  |  |  |  |

|   |      | 6.3.18              | DAC electrical specifications                                                                          |  |  |  |  |  |

|   |      | 6.3.17              | 12-bit ADC characteristics                                                                             |  |  |  |  |  |

|   |      | 6.3.16              | Communication interfaces                                                                               |  |  |  |  |  |

|   |      | 6.3.15              | TIM timer characteristics                                                                              |  |  |  |  |  |

|   |      | 6.3.13              | NRST pin characteristics                                                                               |  |  |  |  |  |

|   |      | 6.3.12              | I/O port characteristics                                                                               |  |  |  |  |  |

|   |      | 6.3.11<br>6.3.12    | Electrical sensitivity characteristics       82         I/O current injection characteristics       83 |  |  |  |  |  |

|   |      | 6.3.10<br>6.3.11    | EMC characteristics                                                                                    |  |  |  |  |  |

|   |      |                     | Memory characteristics                                                                                 |  |  |  |  |  |

|   |      | 6.3.9               | Mamany abaractoristica 90                                                                              |  |  |  |  |  |

## 2 Description

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a frequency of 32 MHz (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 128 Kbytes and RAM up to 32 Kbytes) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

All the devices offer a 12-bit ADC, 2 DACs and 2 ultra-low-power comparators, six generalpurpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices contain standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs and a USB. The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices offer up to 20 capacitive sensing channels to simply add touch sensing functionality to any application.

They also include a real-time clock with sub-second counting and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller (except STM32L151x6/8/B-A devices) has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with contrast independent of the supply voltage.

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +85 °C and -40 to +105°C temperature ranges. A comprehensive set of power-saving modes allows the design of low-power applications.

## 2.1 Device overview

#### Table 2. Ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A device features and peripheral counts

| Peripheral                             |                                                                                                        | STM32L15xCxxxA         |         | xxxA  | STM                                                  | STM32L15xRxxxA |                    |              | STM32L15xVxxxA |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------|---------|-------|------------------------------------------------------|----------------|--------------------|--------------|----------------|--|

| Flash (Kbytes)                         |                                                                                                        | 32                     | 64      | 128   | 32                                                   | 64             | 128                | 64           | 128            |  |

| Data EEPROM (Kb                        |                                                                                                        |                        |         |       | 4                                                    |                |                    |              |                |  |

| RAM (Kbytes)                           | 16                                                                                                     | 32                     | 32      | 16    | 32                                                   | 32             | 32                 | 32           |                |  |

| Timers                                 | General-<br>purpose                                                                                    | 6                      |         |       |                                                      |                |                    |              |                |  |

|                                        | Basic                                                                                                  |                        |         |       |                                                      | 2              |                    |              |                |  |

|                                        | SPI                                                                                                    |                        |         |       |                                                      | 2              |                    |              |                |  |

| Communication                          | l <sup>2</sup> C                                                                                       |                        |         |       |                                                      | 2              |                    |              |                |  |

| interfaces                             | USART                                                                                                  | 3                      |         |       |                                                      |                |                    |              |                |  |

|                                        | USB                                                                                                    | 1                      |         |       |                                                      |                |                    |              |                |  |

| GPIOs                                  |                                                                                                        | 37                     |         |       | 51/50 <sup>(1)</sup>                                 |                |                    | 83           |                |  |

| 12-bit synchronize<br>Number of channe |                                                                                                        | 1<br>14 channels 20/19 |         |       |                                                      | 1<br>9 channe  | els <sup>(1)</sup> |              | l<br>annels    |  |

| 12-bit DAC<br>Number of channe         | els                                                                                                    | 2 2                    |         |       |                                                      |                |                    |              |                |  |

| LCD (STM32L152)<br>COM x SEG           | xxxA Only)                                                                                             | 4x16                   |         |       | 4x32/4x31 <sup>(1)</sup><br>8x28/8x27 <sup>(1)</sup> |                |                    | 4x44<br>8x40 |                |  |

| Comparator                             |                                                                                                        | 2                      |         |       |                                                      |                |                    |              |                |  |

| Capacitive sensing                     | g channels                                                                                             | 13 20                  |         |       |                                                      |                |                    |              |                |  |

| Max. CPU frequen                       | су                                                                                                     | 32 MHz                 |         |       |                                                      |                |                    |              |                |  |

| Operating voltage                      | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option    |                        |         |       |                                                      |                |                    |              |                |  |

| Operating tempera                      | Ambient operating temperatures: –40 to +85 °C / –40 to + 105 °C<br>Junction temperature: -40 to +110°C |                        |         |       |                                                      |                | 05 °C              |              |                |  |

| Packages                               |                                                                                                        | LQFP                   | 48, UFQ | FPN48 | LQFF                                                 | P64, TFB       | GA64               | LQFP100,     | UFBGA100       |  |

1. For TFBGA64 package (instead of PC3 pin there is  $V_{\mathsf{REF}^+}$  pin).

|                                           |            |   | Low- | Low-           |   | Stop                 |   | Standby              |  |

|-------------------------------------------|------------|---|------|----------------|---|----------------------|---|----------------------|--|

| lps                                       | Run/Active |   |      | power<br>Sleep |   | Wakeup<br>capability |   | Wakeup<br>capability |  |

| CPU                                       | Y          | - | Y    | -              | - | -                    | - | -                    |  |

| Flash                                     | Y          | Y | Y    | Y              | - | -                    | - | -                    |  |

| RAM                                       | Y          | Y | Y    | Y              | Y | -                    | - | -                    |  |

| Backup Registers                          | Y          | Y | Y    | Y              | Y | -                    | Y | -                    |  |

| EEPROM                                    | Y          | Y | Y    | Y              | Y | -                    | - | -                    |  |

| Brown-out reset<br>(BOR)                  | Y          | Y | Y    | Y              | Y | Y                    | Y | -                    |  |

| DMA                                       | Y          | Y | Y    | Y              | - | -                    | - | -                    |  |

| Programmable<br>Voltage Detector<br>(PVD) | Y          | Y | Y    | Y              | Y | Y                    | Y | -                    |  |

| Power On Reset<br>(POR)                   | Y          | Y | Y    | Y              | Y | Y                    | Y | -                    |  |

| Power Down Rest<br>(PDR)                  | Y          | Y | Y    | Y              | Y | -                    | Y | -                    |  |

| High Speed<br>Internal (HSI)              | Y          | Y | -    | -              | - | -                    | - | -                    |  |

| High Speed<br>External (HSE)              | Y          | Y | -    | -              | - | -                    | - | -                    |  |

| Low Speed Internal<br>(LSI)               | Y          | Y | Y    | Y              | Y | -                    | Y | -                    |  |

| Low Speed<br>External (LSE)               | Y          | Y | Y    | Y              | Y | -                    | Y | -                    |  |

| Multi-Speed<br>Internal (MSI)             | Y          | Y | Y    | Y              | - | -                    | - | -                    |  |

| Inter-Connect<br>Controller               | Y          | Y | Y    | Y              | - | -                    | - | -                    |  |

| RTC                                       | Y          | Y | Y    | Y              | Y | Y                    | Y | -                    |  |

| RTC Tamper                                | Y          | Y | Y    | Y              | Y | Y                    | Y | Y                    |  |

| Auto Wakeup<br>(AWU)                      | Y          | Y | Y    | Y              | Y | Y                    | Y | Y                    |  |

| LCD                                       | Y          | Y | Y    | Y              | Y | -                    | - | -                    |  |

| USB                                       | Y          | Y | -    | -              | - | Y                    | - | -                    |  |

| USART                                     | Y          | Y | Y    | Y              | Y | (1)                  | - | -                    |  |

| SPI                                       | Y          | Y | Y    | Y              | - | -                    | - | -                    |  |

| I2C                                       | Y          | Y | Y    | Y              | - | (1)                  | - | -                    |  |

| ADC                                       | Y          | Y | -    | -              | - | -                    | - | -                    |  |

#### 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

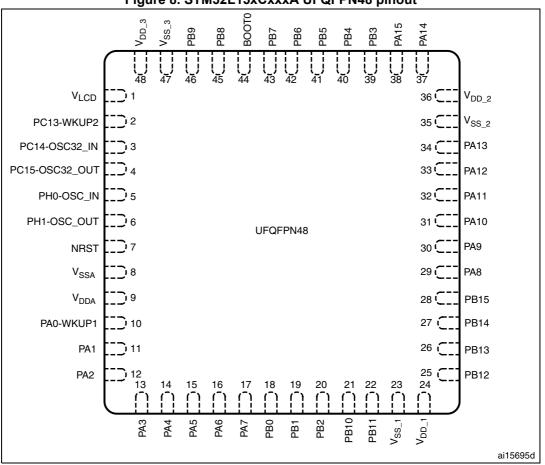

Figure 8. STM32L15xCxxxA UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |                                  |                         |               |                                                  | Pins functio                    | ons                                        |

|---------|--------|---------|----------|--------------------|----------------------------------|-------------------------|---------------|--------------------------------------------------|---------------------------------|--------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions                    |

| 1       | -      | -       | B2       | -                  | PE2                              | I/O                     | FT            | PE2                                              | TRACECLK/<br>LCD_SEG38/TIM3_ETR | -                                          |

| 2       | -      | -       | A1       | -                  | PE3                              | I/O                     | FT            | PE3                                              | TRACED0/<br>LCD_SEG39/TIM3_CH1  | -                                          |

| 3       | -      | -       | B1       | -                  | PE4                              | I/O                     | FT            | PE4                                              | TRACED1/TIM3_CH2                | -                                          |

| 4       | -      | -       | C2       | -                  | PE5                              | I/O                     | FT            | PE5                                              | TRACED2/TIM9_CH1                | -                                          |

| 5       | -      | -       | D2       | -                  | PE6-WKUP3                        | I/O                     | FT            | PE6                                              | TRACED3/TIM9_CH2                | WKUP3<br>/RTC_TAMP3                        |

| 6       | 1      | B2      | E2       | 1                  | V <sub>LCD</sub> <sup>(3)</sup>  | S                       |               | V <sub>LCD</sub>                                 | -                               | -                                          |

| 7       | 2      | A2      | C1       | 2                  | PC13-WKUP2                       | I/O                     | FT            | PC13                                             | -                               | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |

| 8       | 3      | A1      | D1       | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс            | PC14                                             | -                               | OSC32_IN                                   |

| 9       | 4      | B1      | E1       | 4                  | PC15-<br>OSC32_OUT<br>(4)        | I/O                     | тс            | PC15                                             | -                               | OSC32_OUT                                  |

| 10      | -      | -       | F2       | -                  | V <sub>SS_5</sub>                | S                       | -             | V <sub>SS_5</sub>                                | -                               | -                                          |

| 11      | -      | -       | G2       | -                  | V <sub>DD_5</sub>                | S                       | -             | $V_{DD_5}$                                       | -                               | -                                          |

| 12      | 5      | C1      | F1       | 5                  | PH0-OSC_IN <sup>(5)</sup>        | I/O                     | TC            | PH0                                              | -                               | OSC_IN                                     |

| 13      | 6      | D1      | G1       | 6                  | PH1-OSC_OUT                      | I/O                     | тс            | PH1                                              | -                               | OSC_OUT                                    |

| 14      | 7      | E1      | H2       | 7                  | NRST                             | I/O                     | RST           | NRST                                             | -                               | -                                          |

| 15      | 8      | E3      | H1       | -                  | PC0                              | I/O                     | FT            | PC0                                              | LCD_SEG18                       | ADC_IN10/<br>COMP1_INP                     |

| 16      | 9      | E2      | J2       | -                  | PC1                              | I/O                     | FT            | PC1                                              | LCD_SEG19                       | ADC_IN11/<br>COMP1_INP                     |

| 17      | 10     | F2      | J3       | -                  | PC2                              | I/O                     | FT            | PC2                                              | LCD_SEG20                       | ADC_IN12/<br>COMP1_INP                     |

| 18      | 11     | _(6)    | K2       | -                  | PC3                              | I/O                     | тс            | PC3                                              | LCD_SEG21                       | ADC_IN13/<br>COMP1_INP                     |

| 19      | 12     | F1      | J1       | 8                  | V <sub>SSA</sub>                 | S                       | -             | V <sub>SSA</sub>                                 | -                               | -                                          |

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                              | Ratings                                                                         | Min                  | Мах                  | Unit |

|-------------------------------------|---------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>    | External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>      | Input voltage on five-volt tolerant pin                                         | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN V                               | Input voltage on any other pin                                                  | V <sub>SS</sub> -0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                   | Variations between different V <sub>DD</sub> power pins                         | -                    | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub>   | Variations between all different ground pins <sup>(3)</sup>                     | -                    | 50                   |      |

| V <sub>REF+</sub> -V <sub>DDA</sub> | Allowed voltage difference for $V_{REF+} > V_{DDA}$                             | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>               | Electrostatic discharge voltage<br>(human body model)                           | See Section 6.3.11   |                      | -    |

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 12* for maximum allowed injected current values.

3. Include VREF- pin.

#### Table 12. Current characteristics

| Symbol                               | Ratings                                                                       | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------------|-------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>  | 100   |      |

| $\Sigma I_{VSS}^{(2)}$               | Total current out of sum of all $V_{SS_x}$ ground lines (sink) <sup>(1)</sup> | 100   |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD_x</sub> power pin (source) <sup>(1)</sup> | 70    |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each $V_{SS_x}$ ground pin (sink) <sup>(1)</sup>       | -70   | mA   |

| 1                                    | Output current sunk by any I/O and control pin                                | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current sourced by any I/O and control pin                             | - 25  |      |

| 21                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup>   | 60    |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control $pins^{(2)}$       | -60   |      |

| (3)                                  | Injected current on five-volt tolerant I/O <sup>(4)</sup> RST and B pins      | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on any other pin <sup>(5)</sup>                              | ± 5   |      |

| ΣI <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>       | ± 25  |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

|                                      |           | Туріса                                                    | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                           |  |  |  |  |  |

|--------------------------------------|-----------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Per                                  | ipheral   | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] = 01 | V <sub>CORE</sub> =V <sub>CORE</sub> =V <sub>CORE</sub> =Low-power1.8 V1.5 V1.2 Vsleep and run |  |  |  |  |  |

| I <sub>DD (RTC)</sub>                |           |                                                           | 0.4                                                                                            |  |  |  |  |  |

| I <sub>DD (LCD)</sub>                |           |                                                           | μΑ                                                                                             |  |  |  |  |  |

| I <sub>DD (ADC)</sub> <sup>(4)</sup> |           |                                                           |                                                                                                |  |  |  |  |  |

| I <sub>DD (DAC)</sub> <sup>(5)</sup> |           |                                                           |                                                                                                |  |  |  |  |  |

| IDD (COMP1)                          |           |                                                           |                                                                                                |  |  |  |  |  |

| 1                                    | Slow mode |                                                           | 2                                                                                              |  |  |  |  |  |

| IDD (COMP2)                          | Fast mode |                                                           |                                                                                                |  |  |  |  |  |

| I <sub>DD (PVD / BOR)</sub>          | (6)       |                                                           |                                                                                                |  |  |  |  |  |

| I <sub>DD (IWDG)</sub>               |           |                                                           | 0.25                                                                                           |  |  |  |  |  |

| Table 25. Peripheral | current consumption <sup>(1)</sup> | (continued) |

|----------------------|------------------------------------|-------------|

|----------------------|------------------------------------|-------------|

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Lowpower run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

- 3. In low-power sleep and run mode, the Flash memory must always be in power-down mode.

- 4. Data based on a differential Ibb measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

- Data based on a differential IDD measurement between DAC in reset configuration and continuous DAC conversion of VDD/2. DAC is in buffered mode, output is left floating.

- 6. Including supply current of internal reference voltage.

#### 6.3.5 Wakeup time from Low-power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

#### 6.3.6 **External clock source characteristics**

#### High-speed external user clock generated from an external source

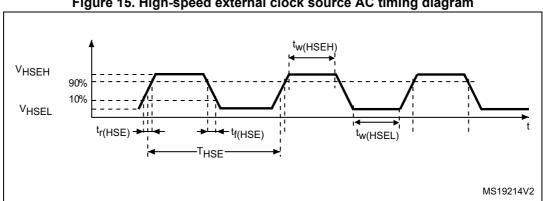

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in Section 6.3.13. However, the recommended clock input waveform is shown in Figure 15.

| Symbol                                       | Parameter                           | Conditions                  | Min             | Тур | Max             | Unit |

|----------------------------------------------|-------------------------------------|-----------------------------|-----------------|-----|-----------------|------|

| fure                                         | User external clock source          | CSS is on or<br>PLL is used | 1               | 8   | 32              | MHz  |

| f <sub>HSE_ext</sub>                         | frequency                           | CSS is off, PLL<br>not used | 0               | 0   | 52              |      |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                             | $0.7V_{DD}$     | -   | V <sub>DD</sub> |      |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |                             | V <sub>SS</sub> |     | $0.3V_{DD}$     |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 12              | -   | -               | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                             | -               | -   | 20              | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            | -                           | -               | 2.6 | -               | pF   |

1. Guaranteed by design.

Figure 15. High-speed external clock source AC timing diagram

#### 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                               | Conditions                                                           | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                               | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| -                                   | HSI user-trimmed                                        | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

|                                     | resolution                                              | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                     |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the<br>factory-calibrated<br>HSI oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                | -1.5              | -    | 1.5              | %    |

|                                     |                                                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              |                   | -    | 2                | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                         | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C              | -2.5              | -    | 2                | %    |

|                                     |                                                         | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             | -4                | -    | 2                | %    |

|                                     |                                                         | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                          | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption                     | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

#### Low-speed internal (LSI) RC oscillator

| Table 32. LSI oscillator | r characteristics |

|--------------------------|-------------------|

|--------------------------|-------------------|

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | _   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

#### 6.3.9 Memory characteristics

The characteristics are given at  $T_{\text{A}}$  = -40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

#### **RAM** memory

| Table | 35. | RAM | and | hardware | reaisters |

|-------|-----|-----|-----|----------|-----------|

| 10010 | ••• |     | ana | naranaro | regiotore |

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol            | Parameter                                             | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|-------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase             | -                                               | 1.65 | -    | 3.6                | V    |

|                   | Programming / erasing time for                        | Erasing                                         | -    | 3.28 | 3.94               |      |

| t <sub>prog</sub> | byte / word / double word / half-<br>page             | Programming                                     | -    | 3.28 | 3.94               | ms   |

|                   | Average current during whole program/erase operation  | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 300  | -                  | μA   |

| I <sub>DD</sub>   | Maximum current (peak) during program/erase operation | Γ <sub>A</sub> = 25° C, V <sub>DD</sub> = 3.0 V | -    | 1.5  | 2.5                | mA   |

#### Table 36. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

#### Table 37. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                      | Conditions              | \<br>\             | /alue |   | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------|--------------------|-------|---|---------|

| Symbol                          | Falameter                                                                      | Conditions              | Min <sup>(1)</sup> | Тур   |   | Onit    |

| NCYC <sup>(2)</sup>             | Cycling (erase / write)<br>Program memory                                      | $T_A = -40^{\circ}C$ to | 10                 | -     | - | kcycles |

| NOTO: 7                         | Cycling (erase / write)<br>EEPROM data memory                                  | 105 °C                  | 300                | -     | - | RUYCIUS |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | TRET = +85 °C           | 30                 | -     | - |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C         | TRET - +05 C            | 30                 | -     | - | voare   |

| 'RET`                           | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | TRET = +105 °C          | 10                 | -     | - | years   |

|                                 | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 105 °C        | III.ET = 1103 C         | 10                 | _     | - |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

DocID024330 Rev 4

#### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during the device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                     | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 38. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

### 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                          | Conditions                                                                                | Min                                       | Тур                                | Max                                   | Unit |

|------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------|------|

| .,               |                                                    | TC and FT I/O                                                                             | -                                         | -                                  | 0.3 V <sub>DD</sub> <sup>(1)(2)</sup> |      |

| $V_{IL}$         | Input low level voltage                            | BOOT0                                                                                     | -                                         |                                    | 0.14 V <sub>DD</sub> <sup>(2)</sup>   |      |

|                  |                                                    | TC I/O                                                                                    | 0.45 V <sub>DD</sub> +0.38 <sup>(2)</sup> | -                                  | -                                     |      |

| $V_{\text{IH}}$  | Input high level voltage                           | FT I/O                                                                                    | 0.39 V <sub>DD</sub> +0.59 <sup>(2)</sup> | -                                  | -                                     | V    |

|                  |                                                    | BOOT0                                                                                     | 0.15 V <sub>DD</sub> +0.56 <sup>(2)</sup> | -                                  | -                                     |      |

| V                | I/O Schmitt trigger voltage                        | TC and FT I/O                                                                             | -                                         | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                     |      |

| V <sub>hys</sub> | hysteresis <sup>(2)</sup>                          | BOOT0                                                                                     | -                                         | 0.01                               | -                                     |      |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                        | -                                         | -                                  | ±50                                   |      |

|                  | Input leakage current <sup>(4)</sup>               | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches         | -                                         | -                                  | ±50                                   | nA   |

| l <sub>lkg</sub> |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                                         | -                                  | ±50                                   |      |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                        | -                                         | -                                  | ±250                                  |      |

|                  |                                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>TC and FT I/O                        | -                                         | -                                  | ±50                                   |      |

|                  |                                                    | FT I/O<br>V <sub>DD</sub> ≤V <sub>IN</sub> ≤5V                                            | -                                         | -                                  | ±10                                   | uA   |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)(1)</sup> | $V_{IN} = V_{SS}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>  | $V_{IN} = V_{DD}$                                                                         | 30                                        | 45                                 | 60                                    | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                | -                                                                                         | -                                         | 5                                  | -                                     | pF   |

| Table 43. I/C | static | characteristics |

|---------------|--------|-----------------|

|---------------|--------|-----------------|

1. Guaranteed by test in production.

2. Guaranteed by design.

3. With a minimum of 200 mV.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

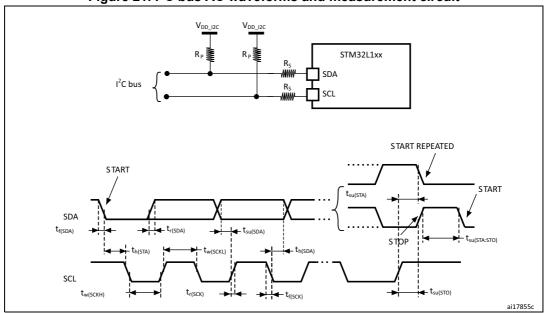

Figure 21. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistors

- 2.  $R_P$  = pull-up resistors

- 3.  $V_{DD_{12C}} = 12C$  bus supply

- 4. Measurement points are done at CMOS levels: 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

| £ (1.11-)              | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801B                  |

| 300                    | 0x8024                  |

| 200                    | 0x8035                  |

| 100                    | 0x00A0                  |

| 50                     | 0x0140                  |

| 20                     | 0x0320                  |

## Table 49. SCL frequency $(f_{PCLK1} = 32 \text{ MHz}, V_{DD} = V_{DD_12C} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

### 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                                         | Parameter                                             | Conditions                                                                 |                                                                    | Min | Тур       | Max                       | Unit |

|------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----------|---------------------------|------|

| V <sub>DDA</sub>                               | Analog supply voltage                                 | -                                                                          |                                                                    | 1.8 | -         | 3.6                       | V    |

| V <sub>REF+</sub>                              | Reference supply voltage                              | V <sub>REF+</sub> must<br>V <sub>DDA</sub>                                 | always be below                                                    | 1.8 | -         | 3.6                       | V    |

| V <sub>REF-</sub>                              | Lower reference voltage                               | -                                                                          |                                                                    |     | $V_{SSA}$ |                           | V    |

| (4)                                            | Current consumption on                                | No load, mid                                                               | dle code (0x800)                                                   | -   | 130       | 220                       | μA   |

| I <sub>DDVREF+</sub> (1)                       | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                                                               | st code (0x000)                                                    | -   | 220       | 350                       | μA   |

| (1)                                            | Current consumption on                                | No load, mid                                                               | ldle code (0x800)                                                  | -   | 210       | 320                       | μA   |

| I <sub>DDA</sub> <sup>(1)</sup>                | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wor                                                               | st code (0xF1C)                                                    | -   | 320       | 520                       | μA   |

| D                                              | Resistive load                                        | DAC output                                                                 | Connected to $V_{SSA}$                                             | 5   | -         | -                         | kΩ   |

| R <sub>L</sub>                                 | Resistive load                                        | buffer ON                                                                  | Connected to V <sub>DDA</sub>                                      | 25  | -         | -                         | K52  |

| CL                                             | Capacitive load                                       | DAC output                                                                 | buffer ON                                                          | -   | -         | 50                        | pF   |

| R <sub>O</sub>                                 | Output impedance                                      | DAC output                                                                 | buffer OFF                                                         | 12  | 16        | 20                        | kΩ   |

| Vol                                            | Voltage on DAC_OUT                                    | DAC output buffer ON                                                       |                                                                    | 0.2 | -         | V <sub>DDA</sub> –<br>0.2 | V    |

| V <sub>DAC_OUT</sub>                           | output                                                | DAC output buffer OFF                                                      |                                                                    | 0.5 | -         | V <sub>REF+</sub><br>1LSB | mV   |

| DNL <sup>(1)</sup>                             | Differential non linearity <sup>(2)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                    | -   | 1.5       | 3                         |      |

| Ditt                                           |                                                       | No $R_L$ , $C_L \le DAC$ output                                            |                                                                    | -   | 1.5       | 3                         |      |

| INL <sup>(1)</sup>                             | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                    | -   | 2         | 4                         |      |

|                                                |                                                       |                                                                            | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF |     | 2         | 4                         | LSB  |

| o m (1)                                        | Offset error at code 0x800 <sup>(4)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                    | -   | ±10       | ±25                       |      |

| Offset <sup>(1)</sup> Offset error at code 0x8 |                                                       | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                                                                    | -   | ±5        | ±8                        |      |

| Offset1 <sup>(1)</sup>                         | Offset error at code 0x001 <sup>(5)</sup>             | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF   |                                                                    | -   | ±1.5      | ±5                        |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

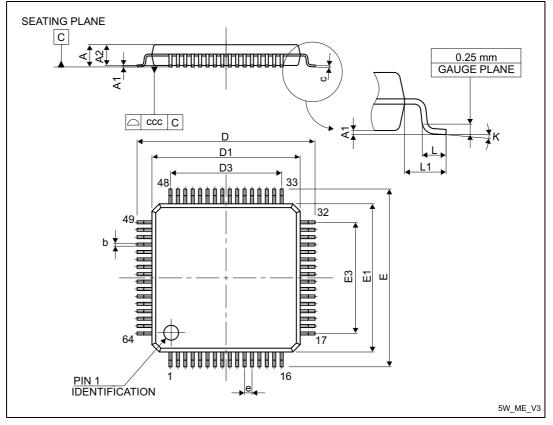

# 7.2 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 33. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 65. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data                                                                         |

|        |       |             | uata  |        |                       |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Cumhal |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

| Symbol | Min   | Тур         | Мах   | Тур    | Min                   | Мах    |  |

| А      | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| Е      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

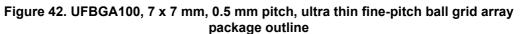

## 7.5 UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package information

1. Drawing is not to scale.

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |

|----------------------------------------------------------------------------------|

| package mechanical data                                                          |

|        |             | <b>1</b> • • • • • • • | go moonamo |                       |        |        |

|--------|-------------|------------------------|------------|-----------------------|--------|--------|

| Cumhal | millimeters |                        |            | inches <sup>(1)</sup> |        |        |

| Symbol | Min         | Тур                    | Мах        | Min                   | Тур    | Max    |

| А      | -           | -                      | 0.6        | -                     | -      | 0.0236 |

| A1     | 0.05        | 0.08                   | 0.11       | 0.002                 | 0.0031 | 0.0043 |

| A2     | 0.4         | 0.45                   | 0.5        | 0.0157                | 0.0177 | 0.0197 |

| A3     | 0.08        | 0.13                   | 0.18       | 0.0031                | 0.0051 | 0.0071 |

| A4     | 0.27        | 0.32                   | 0.37       | 0.0106                | 0.0126 | 0.0146 |

| b      | 0.2         | 0.25                   | 0.3        | 0.0079                | 0.0098 | 0.0118 |

| D      | 6.95        | 7                      | 7.05       | 0.2736                | 0.2756 | 0.2776 |

| D1     | 5.45        | 5.5                    | 5.55       | 0.2146                | 0.2165 | 0.2185 |

| Е      | 6.95        | 7                      | 7.05       | 0.2736                | 0.2756 | 0.2776 |

| E1     | 5.45        | 5.5                    | 5.55       | 0.2146                | 0.2165 | 0.2185 |

| е      | -           | 0.5                    | -          | -                     | 0.0197 | -      |

#### **Package information**

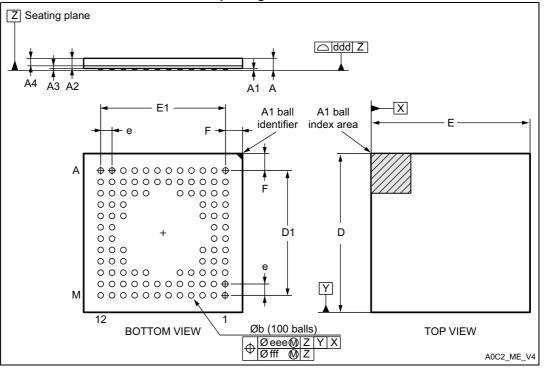

## 7.6 TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package information

Figure 45. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |

|---------------------------------------------------------------------------|

| package mechanical data                                                   |

| Cumhal | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1     | 0.150       | -     | -     | 0.0059                | -      | -      |

| A2     | -           | 0.200 | -     | -                     | 0.0079 | -      |

| A4     | -           | -     | 0.600 | -                     | -      | 0.0236 |

| b      | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |

| D      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

| E      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | -           | 0.750 | -     | -                     | 0.0295 | -      |

DocID024330 Rev 4

## 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04-Feb-2014 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12-Mar-2014 | 2        | <ul> <li>Updated Section 3.5: Low-power real-time clock and backup registers, Section 6.1.2: Typical values and Section 6.3.4: Supply current characteristics.</li> <li>Updated General PCB design guidelines.</li> <li>Updated Table 5: Working mode-dependent functionalities (from Run/active down to standby), Table 14: General operating conditions, Table 21: Current consumption in Low-power run mode, Table 22: Current consumption in Low-power sleep mode, Table 22: Current consumptions in Stop mode, Table 24: Typical and maximum current consumptions in Stop mode, Table 24: Typical and maximum current consumption, Table 42: I/O current injection susceptibility, Table 66: I/O static characteristics and Table 46: NRST pin characteristics.</li> <li>Updated Figure 14: Current consumption measurement scheme.</li> </ul> |

| 04-Feb-2015 | 3        | <ul> <li>Updated DMIPS features in cover page and Section 2: Description.</li> <li>Updated max temperature at 105°C instead of 85°C in the whole datasheet.</li> <li>Updated current consumption in Table 20: Current consumption in Sleep mode.</li> <li>Updated Table 25: Peripheral current consumption with new measured values.</li> <li>Updated Table 57: Maximum source impedance RAIN max adding note 2.</li> <li>Updated Section 7: Package information with new package device marking.</li> <li>Updated Figure 9: Memory map.</li> </ul>                                                                                                                                                                                                                                                                                                 |

#### Table 74. Document revision history