Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT  |

| Number of I/O              | 51                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 4K x 8                                                                   |

| RAM Size                   | 16K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                              |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TFBGA                                                                 |

| Supplier Device Package    | 64-TFBGA (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151rbh6ttr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151x6/8/B-A and STM32L152x6/8/B-A ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontrollers product line.

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A microcontroller family includes devices in 3 different package types: from 48 to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, Wired and wireless sensors, Video intercom

- Utility metering

This STM32L151x6/8/B-A and STM32L152x6/8/B-A datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The document "Getting started with STM32L1xxxx hardware development" AN3216 gives a hardware implementation overview.

Both documents are available from the STMicroelectronics website www.st.com.

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the ARM website.

Figure 1 shows the general block diagram of the device family.

Caution: This datasheet does not apply to:

STM32L15xx6/8/B

covered by a separate datasheet.

|                      |                     | Functionalities depending on the operating power supply range |                           |                                   |                      |  |  |  |  |

|----------------------|---------------------|---------------------------------------------------------------|---------------------------|-----------------------------------|----------------------|--|--|--|--|

| •                    | ng power<br>y range | DAC and ADC operation                                         | USB                       | Dynamic voltage<br>scaling range  | I/O operation        |  |  |  |  |

| V <sub>DD</sub> = 2. | .0 to 2.4 V         | Conversion time<br>up to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

| V <sub>DD</sub> = 2. | .4 to 3.6 V         | Conversion time<br>up to 1 Msps                               | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.

2. Should be USB-compliant from I/O voltage standpoint, the minimum V<sub>DD</sub> is 3.0 V.

### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                 | Dynamic voltage scaling range |

|-----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)    | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)      | Range 2                       |

| 2.1 MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

## 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

## 3.5 Low-power real-time clock and backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Dedicated registers contain the sub-second, second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day of the month are made automatically. The RTC provides two programmable alarms and programmable periodic interrupts with wakeup from Stop and Standby modes.

The programmable wakeup time ranges from 120 µs to 36 hours.

The RTC can be calibrated with an external 512 Hz output, and a digital compensation circuit helps reduce drift due to crystal deviation. The RTC can also be automatically corrected with a 50/60Hz stable power line.

The RTC calendar can be updated on the fly down to sub second precision, which enables network system synchronization. A time stamp can record an external event occurrence, and generates an interrupt.

There are twenty 32-bit backup registers provided to store 80 bytes of user application data. They are cleared in case of tamper detection. Three pins can be used to detect tamper events. A change on one of these pins can reset backup register and generate an interrupt. To prevent false tamper event, like ESD event, these three tamper inputs can be digitally filtered.

# **3.6 GPIOs (general-purpose inputs/outputs)**

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated AFIO registers. All GPIOs are high current capable. The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to the AHB with a toggling speed of up to 16 MHz.

## External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 83 GPIOs can be connected to the 16 external interrupt lines. The 7 other lines are connected to RTC, PVD, USB or Comparator events.

| Timer                  | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |  |

|------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|--|--|--|--|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |  |  |  |  |

| TIM9                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | No                     | 2                           | No                       |  |  |  |  |

| TIM10,<br>TIM11        | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 1                           | No                       |  |  |  |  |

| TIM6,<br>TIM7          | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |  |  |  |  |

Table 7. Timer feature comparison

## 3.17 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.18 Development support

## Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG JTMS and JTCK pins are shared with SWDAT and SWCLK, respectively, and a specific sequence on the JTMS pin is used to switch between JTAG-DP and SW-DP.

The JTAG port can be permanently disabled with a JTAG fuse.

## Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32L151x6/8/B-A and STM32L152x6/8/B-A device through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functions                                |                                                  |  |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------|--|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                           | Additional<br>functions                          |  |

| 35      | 26     | F5      | M5       | 18                 | PB0               | I/O                     | TC            | PB0                                              | TIM3_CH3/<br>LCD_SEG5                         | ADC_IN8/<br>COMP1_INP/<br>VREF_OUT<br>/VLCDRAIL3 |  |

| 36      | 27     | G5      | M6       | 19                 | PB1               | I/O                     | FT            | PB1                                              | TIM3_CH4/<br>LCD_SEG6                         | ADC_IN9/<br>COMP1_INP/<br>VREF_OUT               |  |

| 37      | 28     | G6      | L6       | 20                 | PB2               | I/O                     | FT            | PB2/<br>BOOT1                                    | BOOT1                                         | VLCDRAIL1                                        |  |

| 38      | -      | -       | M7       | -                  | PE7               | I/O                     | тс            | PE7                                              | -                                             | ADC_IN22/<br>COMP1_INP                           |  |

| 39      | -      | -       | L7       | -                  | PE8               | I/O                     | тС            | PE8                                              | -                                             | ADC_IN23/<br>COMP1_INP                           |  |

| 40      | -      | -       | M8       | -                  | PE9               | I/O                     | тС            | PE9                                              | TIM2_CH1_ETR                                  | ADC_IN24/<br>COMP1_INP                           |  |

| 41      | -      | -       | L8       | -                  | PE10              | I/O                     | тС            | PE10                                             | TIM2_CH2                                      | ADC_IN25/<br>COMP1_INP                           |  |

| 42      | -      | -       | M9       | -                  | PE11              | I/O                     | FT            | PE11                                             | TIM2_CH3                                      | VLCDRAIL2                                        |  |

| 43      | -      | -       | L9       | -                  | PE12              | I/O                     | FT            | PE12                                             | TIM2_CH4/<br>SPI1_NSS                         | VLCDRAIL3                                        |  |

| 44      | -      | -       | M10      | -                  | PE13              | I/O                     | FT            | PE13                                             | SPI1_SCK                                      | -                                                |  |

| 45      | -      | -       | M11      | -                  | PE14              | I/O                     | FT            | PE14                                             | SPI1_MISO                                     | -                                                |  |

| 46      | -      | -       | M12      | -                  | PE15              | I/O                     | FT            | PE15                                             | SPI1_MOSI                                     | -                                                |  |

| 47      | 29     | G7      | L10      | 21                 | PB10              | I/O                     | FT            | PB10                                             | I2C2_SCL/USART3_TX<br>/TIM2_CH3/<br>LCD_SEG10 | -                                                |  |

| 48      | 30     | H7      | L11      | 22                 | PB11              | I/O                     | FT            | PB11                                             | I2C2_SDA/USART3_RX<br>/TIM2_CH4/<br>LCD_SEG11 | -                                                |  |

| 49      | 31     | D6      | F12      | 23                 | V <sub>SS_1</sub> | S                       | -             | V <sub>SS_1</sub>                                | -                                             | -                                                |  |

| 50      | 32     | E6      | G12      | 24                 | V <sub>DD_1</sub> | S                       | -             | $V_{DD_1}$                                       | -                                             | -                                                |  |

# Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

46/129

DocID024330 Rev 4

|           |                | Digital alternate function number |          |            |        |           |             |                |           |           |        |            |            |          |          |

|-----------|----------------|-----------------------------------|----------|------------|--------|-----------|-------------|----------------|-----------|-----------|--------|------------|------------|----------|----------|

| Dentmann  | AFIO0          | AFIO1                             | AFIO2    | AFIO3      | AFIO4  | AFIO5     | AFOI6       | AFIO7          | AFI<br>O8 | AFI<br>O9 | AFIO11 | AFIO<br>12 | AFIO<br>13 | AFIO14   | AFIO15   |

| Port name |                |                                   |          |            |        | Altern    | ate functio | n              | •         | •         |        | •          | •          |          |          |

|           | SYSTEM         | TIM2                              | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2    | N/A         | USART<br>1/2/3 | N/A       | N/A       | LCD    | N/A        | N/A        | RI       | SYSTEM   |

| BOOT0     | BOOT0          | -                                 | -        | -          | -      | -         | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| NRST      | NRST           | -                                 | -        | -          | -      | -         | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| PA0-WKUP1 | -              | TIM2_CH1_ETR                      | -        | -          | -      | -         | -           | USART2_CTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA1       | -              | TIM2_CH2                          | -        | -          | -      | -         | -           | USART2_RTS     | -         | -         | [SEG0] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA2       | -              | TIM2_CH3                          | -        | TIM9_CH1   | -      | -         | -           | USART2_TX      | -         | -         | [SEG1] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA3       | -              | TIM2_CH4                          | -        | TIM9_CH2   | -      | -         | -           | USART2_RX      | -         | -         | [SEG2] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA4       | -              | -                                 | -        | -          | -      | SPI1_NSS  | -           | USART2_CK      | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA5       | -              | TIM2_CH1_ETR                      | -        | -          | -      | SPI1_SCK  | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA6       | -              | -                                 | TIM3_CH1 | TIM10_CH1  | -      | SPI1_MISO | -           | -              | -         | -         | [SEG3] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA7       | -              | -                                 | TIM3_CH2 | TIM11_CH1  | -      | SPI1_MOSI | -           | -              | -         | -         | [SEG4] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA8       | МСО            | -                                 | -        | -          | -      | -         | -           | USART1_CK      | -         | -         | [COM0] | -          | -          | TIMx_IC1 | EVENTOUT |

| PA9       | -              | -                                 | -        | -          | -      | -         | -           | USART1_TX      | -         | -         | [COM1] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA10      | -              | -                                 | -        | -          | -      | -         | -           | USART1_RX      | -         | -         | [COM2] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA11      | -              | -                                 | -        | -          | -      | SPI1_MISO | -           | USART1_CTS     | -         | -         | -      | -          | -          | TIMx_IC4 | EVENTOUT |

| PA12      | -              | -                                 | -        | -          | -      | SPI1_MOSI | -           | USART1_RTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA13      | JTMS-<br>SWDIO | -                                 | -        | -          | -      | -         | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA14      | JTCK-<br>SWCLK | -                                 | -        | -          | -      | -         | -           | -              | -         | -         | -      | -          | -          | TIMx_IC3 | EVENTOUT |

| PA15      | JTDI           | TIM2_CH1_ETR                      | -        | -          | -      | SPI1_NSS  | -           | -              | -         | -         | SEG17  | -          | -          | TIMx_IC4 | EVENTOUT |

| PB0       | -              | -                                 | TIM3_CH3 | -          | -      | -         | -           | -              | -         | -         | [SEG5] | -          | -          | -        | EVENTOUT |

| PB1       | -              | -                                 | TIM3_CH4 | -          | -      | -         | -           | -              | -         | -         | [SEG6] | -          | -          | -        | EVENTOUT |

| PB2       | BOOT1          | -                                 | -        | -          | -      | -         | -           | -              | -         | -         | -      | -          | -          | -        | EVENTOUT |

| PB3       | JTDO           | TIM2_CH2                          | -        | -          | -      | SPI1_SCK  | -           | -              | -         | -         | [SEG7] | -          | -          | -        | EVENTOUT |

Table 10. Alternate function input/output

Pin descriptions

| 5 |

|---|

|---|

### Digital alternate function number AFI O9 AFI AFIO AFIO AFIO2 AFIO4 AFIO5 AFOI6 AFIO11 AFIO0 AFIO1 AFIO3 AFIO7 AFIO14 AFIO15 08 13 12 Port name Alternate function USART SYSTEM TIM2 TIM3/4 TIM9/10/11 I2C1/2 SPI1/2 N/A N/A N/A LCD N/A N/A RI SYSTEM 1/2/3 PD10 USART3\_CK TIMx\_IC3 EVENTOUT ------------TIMx\_IC4 PD11 USART3\_CTS -EVENTOUT -----------PD12 TIM4 CH1 USART3\_RTS TIMx IC1 EVENTOUT -\_ ---------TIM4\_CH2 PD13 TIMx\_IC2 EVENTOUT ------------PD14 TIM4\_CH3 TIMx\_IC3 EVENTOUT ------------TIM4\_CH4 \_ -TIMx\_IC4 EVENTOUT PD15 \_ \_ -\_ -----\_ TIM4 ETR TIM10 CH1 TIMx\_IC1 EVENTOUT PE0 -----------TIM11\_CH1 TIMx\_IC2 EVENTOUT PE1 -----------TIMx\_IC3 PE2 TRACECK TIM3 ETR EVENTOUT -----------TIMx\_IC4 PE3 TRACED0 TIM3\_CH1 EVENTOUT -----------TIMx\_IC1 PE4 -EVENTOUT TRACED1 -TIM3 CH2 ---------PE5 TRACED2 TIM9 CH1\* -TIMx\_IC2 EVENTOUT ----------PE6 TRACED3 TIM9\_CH2\* TIMx\_IC3 EVENTOUT -----------TIMx\_IC4 EVENTOUT PE7 ------------TIMx\_IC1 EVENTOUT PE8 ------------TIMx\_IC2 EVENTOUT PE9 TIM2 CH1 ETR ------------EVENTOUT **PE10** TIM2\_CH2 -TIMx\_IC3 -----------EVENTOUT PE11 TIM2\_CH3 TIMx\_IC4 ------------PE12 TIMx\_IC1 EVENTOUT TIM2\_CH4 SPI1\_NSS -----------TIMx\_IC2 EVENTOUT PE13 -SPI1\_SCK -----------PE14 SPI1\_MISO TIMx\_IC3 EVENTOUT ------------PE15 SPI1\_MOSI TIMx\_IC4 EVENTOUT ------------PH0-----------. --\_ -OSC\_IN

Table 10. Alternate function input/output (continued)

49/129

Pin descriptions

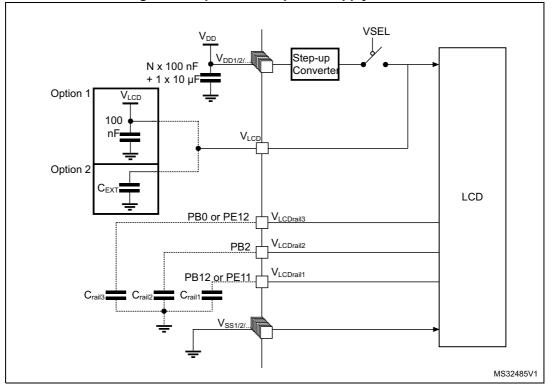

## 6.1.7 Optional LCD power supply scheme

Figure 13. Optional LCD power supply scheme

1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

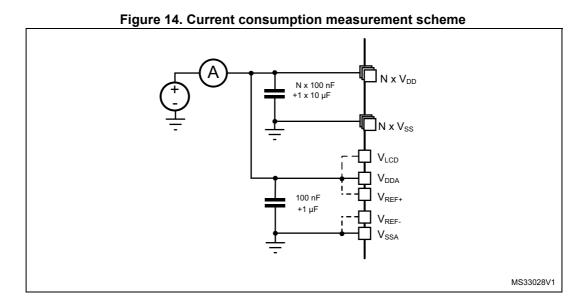

## 6.1.8 Current consumption measurement

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Мах  | Unit |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|

| V                 | Drown out react threshold 0   | Falling edge                              | 1.67 | 1.7  | 1.74 |      |

| V <sub>BOR0</sub> | Brown-out reset threshold 0   | Rising edge                               | 1.69 | 1.76 | 1.8  |      |

| M                 | Drown out react threshold 4   | Falling edge                              | 1.87 | 1.93 | 1.97 |      |

| V <sub>BOR1</sub> | Brown-out reset threshold 1   | Rising edge                               | 1.96 | 2.03 | 2.07 |      |

| V                 | Brown-out reset threshold 2   | Falling edge                              | 2.22 | 2.30 | 2.35 | v    |

| V <sub>BOR2</sub> | BIOWII-OULTESEL III ESHOIU Z  | Rising edge                               | 2.31 | 2.41 | 2.44 | v    |

| M                 | Drown out react threshold 2   | Falling edge                              | 2.45 | 2.55 | 2.60 |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 3   | Rising edge                               | 2.54 | 2.66 | 2.7  |      |

| M                 | Drown out react threshold 4   | Falling edge                              | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | Brown-out reset threshold 4   | Rising edge                               | 2.78 | 2.9  | 2.95 |      |

| M                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |

| M                 | DVD threehold 0               | Falling edge                              | 2.20 | 2.24 | 2.28 |      |

| V <sub>PVD2</sub> | PVD threshold 2               | Rising edge                               | 2.28 | 2.34 | 2.38 |      |

|                   | DVD threads all a             | Falling edge                              | 2.39 | 2.44 | 2.48 |      |

| V <sub>PVD3</sub> | PVD threshold 3               | Rising edge                               | 2.47 | 2.54 | 2.58 | V    |

| M                 | DVD threehold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> | PVD threshold 4               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |

|                   | DVD threads ald 5             | Falling edge                              | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> | PVD threshold 5               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |

|                   | DVD threads all 0             | Falling edge                              | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> | PVD threshold 6               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

| Table 15. Embedded reset and | power control block characteristics (c | continued) |

|------------------------------|----------------------------------------|------------|

1. Guaranteed by characterization.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol          | Parameter            | Cond                                                                                                      | litions                                               | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------|--------------------|------|

|                 |                      |                                                                                                           | Range 3,                                              | 1 MHz             | 50   | 155                |      |

|                 |                      |                                                                                                           | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 78.5 | 235                |      |

|                 |                      |                                                                                                           | VOS[1:0] = 11                                         | 4 MHz             | 140  | 370 <sup>(3)</sup> |      |

|                 |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                                            | Range 2,                                              | 4 MHz             | 165  | 375                |      |

|                 |                      | $f_{HSE} = f_{HCLK}/2$                                                                                    | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 310  | 530                |      |

|                 |                      | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                      | VOS[1:0] = 10                                         | 16 MHz            | 590  | 1000               |      |

|                 | Quanta               |                                                                                                           | Range 1,                                              | 8 MHz             | 350  | 615                |      |

|                 | Supply<br>current in |                                                                                                           | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 680  | 1200               |      |

|                 | Sleep                |                                                                                                           | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2350               | μA   |

|                 | mode,<br>Flash OFF   | HSI clock source                                                                                          | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 640  | 970                |      |

|                 |                      | (16 MHz)                                                                                                  | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2350               |      |

|                 |                      | MSI clock, 65 kHz                                                                                         | Range 3,                                              | 65 kHz            | 19   | 60                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                        | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 33   | 90                 |      |

| I <sub>DD</sub> |                      | MSI clock, 4.2 MHz                                                                                        | VOS[1:0] = 11                                         | 4.2 MHz           | 145  | 210                |      |

| (Sleep)         |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 60.5 | 145                |      |

|                 |                      |                                                                                                           |                                                       | 2 MHz             | 89.5 | 225                |      |

|                 |                      |                                                                                                           |                                                       | 4 MHz             | 150  | 360                |      |

|                 |                      |                                                                                                           | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 4 MHz             | 180  | 370                |      |

|                 |                      |                                                                                                           |                                                       | 8 MHz             | 320  | 490                |      |

|                 |                      | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                      |                                                       | 16 MHz            | 605  | 895                |      |

|                 | Supply               |                                                                                                           | Range 1,                                              | 8 MHz             | 380  | 565                |      |

|                 | current in           |                                                                                                           | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 695  | 1070               |      |

|                 | Sleep                |                                                                                                           | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2200               | μA   |

|                 | mode,<br>Flash ON    | HSI clock source                                                                                          | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 650  | 970                |      |

|                 |                      | (16 MHz)                                                                                                  | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2320               |      |

|                 |                      | MSI clock, 65 kHz                                                                                         | Range 3,                                              | 65 kHz            | 29.5 | 65                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                        | V <sub>CORE</sub> =1.2V                               | 524 kHz           | 44   | 80                 |      |

|                 |                      | MSI clock, 4.2 MHz                                                                                        | VOS[1:0] = 11                                         | 4.2 MHz           | 155  | 220                |      |

Table 20. Current consumption in Sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

3. Guaranteed by test in production.

|                                            |           | Туріса                                                    | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                           |    |  |  |  |  |

|--------------------------------------------|-----------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|----|--|--|--|--|

| Per                                        | ipheral   | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] = 01 | V <sub>CORE</sub> =V <sub>CORE</sub> =V <sub>CORE</sub> =Low-power1.8 V1.5 V1.2 Vsleep and run |    |  |  |  |  |

| I <sub>DD (RTC)</sub>                      |           |                                                           | 0                                                                                              | .4 |  |  |  |  |

| I <sub>DD (LCD)</sub>                      |           |                                                           |                                                                                                |    |  |  |  |  |

| I <sub>DD (ADC)</sub> <sup>(4)</sup>       |           |                                                           |                                                                                                |    |  |  |  |  |

| I <sub>DD (DAC)</sub> <sup>(5)</sup>       |           |                                                           |                                                                                                |    |  |  |  |  |

| IDD (COMP1)                                |           |                                                           | μA                                                                                             |    |  |  |  |  |

|                                            | Slow mode |                                                           | 2                                                                                              |    |  |  |  |  |

| IDD (COMP2) Fast mode                      |           |                                                           |                                                                                                |    |  |  |  |  |

| I <sub>DD (PVD / BOR)</sub> <sup>(6)</sup> |           |                                                           |                                                                                                |    |  |  |  |  |

| I <sub>DD (IWDG)</sub>                     |           |                                                           | 0.25                                                                                           |    |  |  |  |  |

| Table 25. Peripheral | current consumption <sup>(1)</sup> | (continued) |

|----------------------|------------------------------------|-------------|

|----------------------|------------------------------------|-------------|

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Lowpower run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

- 3. In low-power sleep and run mode, the Flash memory must always be in power-down mode.

- 4. Data based on a differential IDD measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

- Data based on a differential IDD measurement between DAC in reset configuration and continuous DAC conversion of VDD/2. DAC is in buffered mode, output is left floating.

- 6. Including supply current of internal reference voltage.

## 6.3.5 Wakeup time from Low-power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

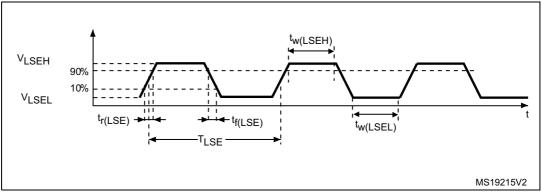

## Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                       | Parameter                             | Min                | Тур    | Max                | Unit |

|----------------------------------------------|---------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | -    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | -    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance            | -                  | 0.6    | -                  | pF   |

| Table 28. Low-speed external user clock characteristics <sup>(1)</sup> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

1. Guaranteed by design.

## Figure 16. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 29. | HSE | oscillator | characteristics <sup>(1)(2)</sup> |

|-----------|-----|------------|-----------------------------------|

|-----------|-----|------------|-----------------------------------|

| Symbol              | Parameter            | Conditions | Min | Тур | Мах | Unit |

|---------------------|----------------------|------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub> | Oscillator frequency | -          | 1   |     | 24  | MHz  |

| R <sub>F</sub>      | Feedback resistor    | -          |     | 200 | -   | kΩ   |

## **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 44*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 12*).

## **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                       | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|----------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA           | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA           | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.65 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 15 mA          | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V  | V <sub>DD</sub> -1.3  | -    |      |

### Table 44. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Guaranteed by test in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                                                   | Parameter                                                                              | Conditions                                                                 |                               | Min | Тур       | Max                       | Unit |

|----------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|-----|-----------|---------------------------|------|

| V <sub>DDA</sub>                                         | Analog supply voltage                                                                  | -                                                                          |                               | 1.8 | -         | 3.6                       | V    |

| V <sub>REF+</sub>                                        | Reference supply voltage                                                               | V <sub>REF+</sub> must<br>V <sub>DDA</sub>                                 | always be below               | 1.8 | -         | 3.6                       | V    |

| V <sub>REF-</sub>                                        | Lower reference voltage                                                                | -                                                                          |                               |     | $V_{SSA}$ |                           | V    |

| (4)                                                      | Current consumption on                                                                 | No load, mid                                                               | dle code (0x800)              | -   | 130       | 220                       | μA   |

| I <sub>DDVREF+</sub> (1)                                 | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V                                  | No load, wor                                                               | st code (0x000)               | -   | 220       | 350                       | μA   |

| (1)                                                      | Current consumption on                                                                 | No load, mid                                                               | ldle code (0x800)             | -   | 210       | 320                       | μA   |

| I <sub>DDA</sub> <sup>(1)</sup>                          | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V                                    | No load, wor                                                               | st code (0xF1C)               | -   | 320       | 520                       | μA   |

| D                                                        | Resistive load                                                                         | DAC output                                                                 | Connected to $V_{SSA}$        | 5   | -         | -                         | kΩ   |

| R <sub>L</sub>                                           | Resistive load                                                                         | buffer ON                                                                  | Connected to V <sub>DDA</sub> | 25  | -         | -                         | K52  |

| CL                                                       | Capacitive load                                                                        | DAC output                                                                 | buffer ON                     | -   | -         | 50                        | pF   |

| R <sub>O</sub>                                           | Output impedance                                                                       | DAC output buffer OFF                                                      |                               | 12  | 16        | 20                        | kΩ   |

| V <sub>DAC_OUT</sub>                                     | Voltage on DAC_OUT<br>output                                                           | DAC output buffer ON                                                       |                               | 0.2 | -         | V <sub>DDA</sub> –<br>0.2 | V    |

|                                                          |                                                                                        | DAC output buffer OFF                                                      |                               | 0.5 | -         | V <sub>REF+</sub><br>1LSB | mV   |

| DNL <sup>(1)</sup>                                       | Differential non linearity <sup>(2)</sup>                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | 1.5       | 3                         |      |

| Ditt                                                     |                                                                                        | No $R_L$ , $C_L \le DAC$ output                                            |                               | -   | 1.5       | 3                         |      |

| INL <sup>(1)</sup>                                       | $C_{L} \le 50 \text{ pF}, \text{ R}_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                            | -                             | 2   | 4         |                           |      |

| INL <sup>(1)</sup> Integral non linearity <sup>(3)</sup> |                                                                                        | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF   |                               | -   | 2         | 4                         | LSB  |

| or (1)                                                   | Offset error at code 0x800 <sup>(4)</sup>                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | ±10       | ±25                       |      |

| Offset <sup>(1)</sup>                                    | Unset error at code 0x800 (*)                                                          | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                               | -   | ±5        | ±8                        |      |

| Offset1 <sup>(1)</sup>                                   | Offset error at code 0x001 <sup>(5)</sup>                                              | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF   |                               | -   | ±1.5      | ±5                        |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

# 6.3.20 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |  |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|--|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |  |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |  |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | N32       |  |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                                     | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |  |  |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 |           |  |  |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | μs        |  |  |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |  |  |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |  |  |

Table 61. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

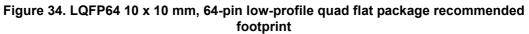

| Table 65. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data (continued)                                                             |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Тур                   | Min    | Max    |  |

| E3     | -           | 7.500 | -     | -                     | 0.2953 | -      |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| К      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |  |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are in millimeters.

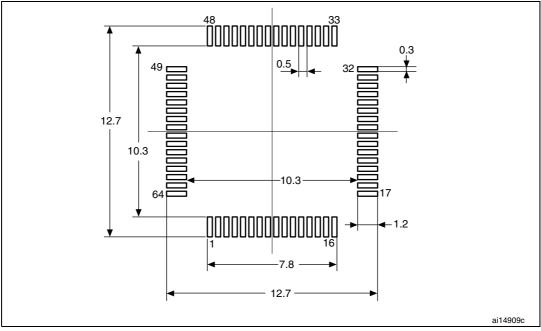

## **UFBGA100** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 44. UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

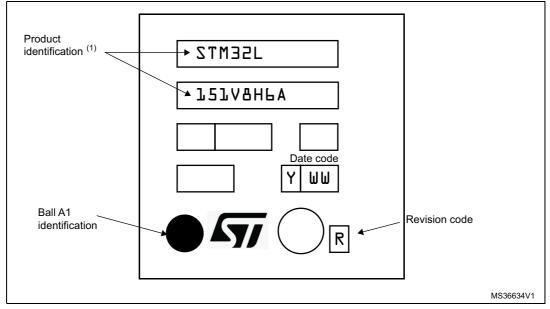

## **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 47. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.