## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151v8t6a  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | package outline                                                  | 21 |

|------------|------------------------------------------------------------------|----|

| Figure 46. | TFBGA64, 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |    |

|            | package recommended footprint1                                   | 22 |

| Figure 47. | TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example 1       | 23 |

| Figure 48. | Thermal resistance suffix 61                                     | 25 |

| Figure 49. | Thermal resistance suffix 71                                     | 25 |

57

## 2.1 Device overview

#### Table 2. Ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A device features and peripheral counts

| Periph                                 | eral                | STM                                                                                                    | 32L15xC | xxxA | STM                  | 32L15xR              | хххА               | STM32L1           | 5xVxxxA  |  |

|----------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|---------|------|----------------------|----------------------|--------------------|-------------------|----------|--|

| Flash (Kbytes)                         |                     | 32                                                                                                     | 64      | 128  | 32                   | 64                   | 128                | 64                | 128      |  |

| Data EEPROM (Kb                        | oytes)              |                                                                                                        |         |      |                      | 4                    |                    |                   |          |  |

| RAM (Kbytes)                           |                     | 16                                                                                                     | 32      | 32   | 16                   | 32                   | 32                 | 32                | 32       |  |

| Timers                                 | General-<br>purpose |                                                                                                        |         |      |                      | 6                    |                    |                   |          |  |

|                                        | Basic               |                                                                                                        |         |      |                      | 2                    |                    |                   |          |  |

|                                        | SPI                 |                                                                                                        |         |      |                      | 2                    |                    |                   |          |  |

| Communication                          | l <sup>2</sup> C    | 2                                                                                                      |         |      |                      |                      |                    |                   |          |  |

| interfaces                             | USART               |                                                                                                        |         |      |                      | 3                    |                    |                   |          |  |

|                                        | USB                 |                                                                                                        |         |      |                      | 1                    |                    |                   |          |  |

| GPIOs                                  |                     | 37                                                                                                     |         |      | 51/50 <sup>(1)</sup> |                      |                    | 83                |          |  |

| 12-bit synchronize<br>Number of channe |                     | 1<br>14 channels                                                                                       |         |      | 20/1                 | 1<br>9 channe        | els <sup>(1)</sup> | 1<br>24 channels  |          |  |

| 12-bit DAC<br>Number of channe         | els                 | 2 2                                                                                                    |         |      |                      |                      |                    |                   |          |  |

| LCD (STM32L152)<br>COM x SEG           | xxxA Only)          |                                                                                                        | 4x16    |      |                      | x32/4x31<br>x28/8x27 |                    |                   | 44<br>40 |  |

| Comparator                             |                     |                                                                                                        |         |      | L                    | 2                    |                    |                   |          |  |

| Capacitive sensing                     | g channels          |                                                                                                        | 13      |      |                      |                      | 20                 | )                 |          |  |

| Max. CPU frequen                       | су                  |                                                                                                        |         |      | <u>.</u>             | 32 MHz               |                    |                   |          |  |

| Operating voltage                      |                     | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option    |         |      |                      |                      |                    |                   |          |  |

| Operating tempera                      | atures              | Ambient operating temperatures: –40 to +85 °C / –40 to + 105 °C<br>Junction temperature: -40 to +110°C |         |      |                      |                      |                    |                   |          |  |

| Packages                               |                     | LQFP48, UFQFPN48                                                                                       |         |      | LQFP64, TFBGA64      |                      |                    | LQFP100, UFBGA100 |          |  |

1. For TFBGA64 package (instead of PC3 pin there is  $V_{\mathsf{REF}^+}$  pin).

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From a proprietary 8bit core up to the Cortex-M3, including the Cortex-M0+, the STM8Lx and STM32Lx series offer the best range of choices to meet your requirements in terms of ultra-low-power features. The STM32 Ultra-low-power series is an ideal fit for applications like gas/water meters, keyboard/mouse, or wearable devices for fitness and healthcare. Numerous built-in features like LCD drivers, dual-bank memory, low-power Run mode, op-amp, AES-128bit, DAC, crystal-less USB and many others, allow to build highly cost-optimized applications by reducing the BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lx and STM32Lx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, your existing applications can be upgraded to respond to the latest market features and efficiency demand.

## 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-Low-power performance to range from 5 up to 33.3 DMIPs.

## 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

## 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xxx and STM32L1xxxx families use a common architecture:

- Common power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xxx devices)

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultra-safe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

## 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 512 Kbytes

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

## 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See the application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

## 3.12 Ultra-low-power comparators and reference voltage

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- one comparator with fixed threshold

- one comparator with rail-to-rail inputs, fast or slow mode. The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage (V<sub>REFINT</sub>) or V<sub>REFINT</sub> submultiple (1/4, 1/2, 3/4)

Both comparators can wake up from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

## 3.13 Routing interface

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM3 and TIM4 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

## 3.14 Touch sensing

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 20 capacitive sensing channels distributed over 10 analog I/O groups. Both software and timer capacitive sensing acquisition modes are supported.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. The capacitive sensing acquisition only requires few external components to operate. This acquisition is managed directly by the GPIOs, timers and analog I/O groups (see Section 3.13: Routing interface).

Reliable touch sensing functionality can be quickly and easily implemented using the free STM32L1xx STMTouch touch sensing firmware library.

## 3.15 Timers and watchdogs

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices include six general-purpose timers, two basic timers and two watchdog timers.

Table 7 compares the features of the general-purpose and basic timers.

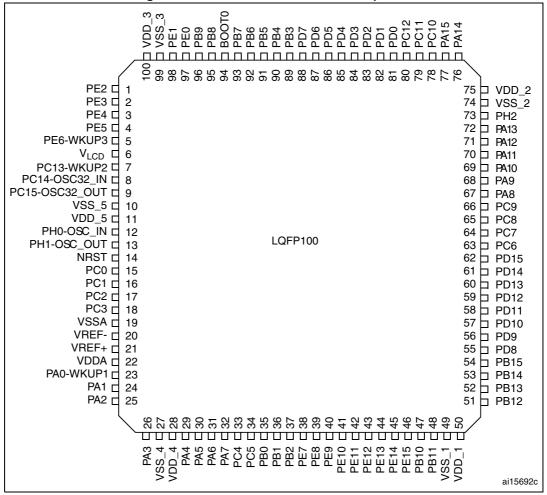

Figure 4. STM32L15xVxxxA LQFP100 pinout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functio                                       | ns                      |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|----------------------------------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                | Additional<br>functions |

| 67      | 41     | D7      | D11      | 29                 | PA8               | I/O                     | FT            | PA8                                              | USART1_CK/MCO/<br>LCD_COM0                         | -                       |

| 68      | 42     | C7      | D10      | 30                 | PA9               | I/O                     | FT            | PA9                                              | USART1_TX/<br>LCD_COM1                             | -                       |

| 69      | 43     | C6      | C12      | 31                 | PA10              | I/O                     | FT            | PA10                                             | USART1_RX/<br>LCD_COM2                             | -                       |

| 70      | 44     | C8      | B12      | 32                 | PA11              | I/O                     | FT            | PA11                                             | USART1_CTS/<br>SPI1_MISO                           | USB_DM                  |

| 71      | 45     | B8      | A12      | 33                 | PA12              | I/O                     | FT            | PA12                                             | USART1_RTS/<br>SPI1_MOSI                           | USB_DP                  |

| 72      | 46     | A8      | A11      | 34                 | PA13              | I/O                     | FT            | JTMS-<br>SWDIO                                   | JTMS-SWDIO                                         | -                       |

| 73      | -      | -       | C11      | -                  | PH2               | I/O                     | FT            | PH2                                              | -                                                  | -                       |

| 74      | 47     | D5      | F11      | 35                 | V <sub>SS_2</sub> | S                       | -             | V <sub>SS_2</sub>                                | -                                                  | -                       |

| 75      | 48     | E5      | G11      | 36                 | V <sub>DD_2</sub> | S                       | -             | V <sub>DD_2</sub>                                | -                                                  | -                       |

| 76      | 49     | A7      | A10      | 37                 | PA14              | I/O                     | FT            | JTCK-<br>SWCLK                                   | JCTK-SWCLK                                         | -                       |

| 77      | 50     | A6      | A9       | 38                 | PA15              | I/O                     | FT            | JTDI                                             | TIM2_CH1_ETR/PA15/<br>SPI1_NSS/<br>LCD_SEG17       | -                       |

| 78      | 51     | B7      | B11      | -                  | PC10              | I/O                     | FT            | PC10                                             | USART3_TX/<br>LCD_SEG28/<br>LCD_SEG40/<br>LCD_COM4 | -                       |

| 79      | 52     | B6      | C10      | -                  | PC11              | I/O                     | FT            | PC11                                             | USART3_RX/<br>LCD_SEG29/<br>LCD_SEG41/<br>LCD_COM5 | -                       |

| 80      | 53     | C5      | B10      | -                  | PC12              | I/O                     | FT            | PC12                                             | USART3_CK/<br>LCD_SEG30/<br>LCD_SEG42/<br>LCD_COM6 | -                       |

| 81      | -      | -       | C9       | -                  | PD0               | I/O                     | FT            | PD0                                              | SPI2_NSS/TIM9_CH1                                  | -                       |

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functio            | ns                      |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|-------------------------|-------------------------|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions     | Additional<br>functions |

| 98      | -      | -       | A2       | -                  | PE1               | I/O                     | FT            | PE1                                              | LCD_SEG37/<br>TIM11_CH1 | -                       |

| 99      | 63     | D4      | D3       | 47                 | V <sub>SS_3</sub> | S                       | -             | V <sub>SS_3</sub>                                | -                       | -                       |

| 100     | 64     | E4      | C4       | 48                 | V <sub>DD_3</sub> | S                       | -             | V <sub>DD_3</sub>                                | -                       | -                       |

#### Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

3. Applicable to STM32L152xxxxA devices only. In STM32L151xxxxA devices, this pin should be connected to V<sub>DD</sub>.

4. The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

|                    |        |       |          |            |        | Digital alterna | te functior | n number       |           |           |                            |            |            |          |         |

|--------------------|--------|-------|----------|------------|--------|-----------------|-------------|----------------|-----------|-----------|----------------------------|------------|------------|----------|---------|

| Dertheme           | AFIO0  | AFIO1 | AFIO2    | AFIO3      | AFIO4  | AFIO5           | AFOI6       | AFIO7          | AFI<br>O8 | AFI<br>O9 | AFIO11                     | AFIO<br>12 | AFIO<br>13 | AFIO14   | AFIO15  |

| Port name          | ·      |       |          |            |        | Altern          | ate functio | 'n             |           |           |                            |            |            |          |         |

|                    | SYSTEM | TIM2  | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2          | N/A         | USART<br>1/2/3 | N/A       | N/A       | LCD                        | N/A        | N/A        | RI       | SYSTEM  |

| PC10               | -      | -     | -        | -          | -      | -               | -           | USART3_TX      | -         | -         | COM4 /<br>SEG28 /<br>SEG40 | -          | -          | TIMx_IC3 | EVENTOU |

| PC11               | -      | -     | -        | -          | -      | -               | -           | USART3_RX      | -         | -         | COM5 /<br>SEG29 /<br>SEG41 | -          | -          | TIMx_IC4 | EVENTOL |

| PC12               | -      | -     | -        | -          | -      | -               | -           | USART3_CK      | -         | -         | COM6 /<br>SEG30 /<br>SEG42 | -          | -          | TIMx_IC1 | EVENTOL |

| PC13-<br>WKUP2     | -      | -     | -        | -          | -      | -               | -           | -              | -         | -         | -                          | -          | -          | TIMx_IC2 | EVENTOL |

| PC14-<br>OSC32_IN  | -      | -     | -        | -          | -      | -               | -           | -              | -         | -         | -                          | -          | -          | TIMx_IC3 | EVENTOL |

| PC15-<br>OSC32_OUT | -      | -     | -        | -          | -      | -               | -           | -              | -         | -         | -                          | -          | -          | TIMx_IC4 | EVENTOL |

| PD0                | -      | -     | -        | TIM9_CH1   | -      | SPI2_NSS        | -           | -              | -         | -         | -                          | -          | -          | TIMx_IC1 | EVENTOL |

| PD1                | -      | -     | -        | -          | -      | SPI2_SCK        | -           | -              | -         | -         | -                          | -          | -          | TIMx_IC2 | EVENTOL |

| PD2                | -      | -     | TIM3_ETR | -          | -      | -               | -           | -              | -         | -         | COM7 /<br>SEG31 /<br>SEG43 | -          | -          | TIMx_IC3 | EVENTOL |

| PD3                | -      | -     | -        | -          | -      | SPI2_MISO       | -           | USART2_CTS     | -         | -         | -                          | -          | -          | TIMx_IC4 | EVENTOL |

| PD4                | -      | -     | -        | -          | -      | SPI2_MOSI       | -           | USART2_RTS     | -         | -         | -                          | -          | -          | TIMx_IC1 | EVENTOL |

| PD5                | -      | -     | -        | -          | -      | -               | -           | USART2_TX      | -         | -         | -                          | -          | -          | TIMx_IC2 | EVENTOL |

| PD6                | -      | -     | -        | -          | -      | -               | -           | USART2_RX      | -         | -         | -                          | -          |            | TIMx_IC3 | EVENTOL |

| PD7                | -      | -     | -        | TIM9_CH2   | -      | -               | -           | USART2_CK      | -         | -         | -                          | -          | -          | TIMx_IC4 | EVENTOL |

| PD8                | -      | -     | -        | -          | -      | -               | -           | USART3_TX      | -         | -         | -                          | -          | -          | TIMx_IC1 | EVENTOL |

| PD9                | -      | -     | -        | -          | -      | -               | -           | USART3_RX      | -         | -         | -                          | -          | -          | TIMx_IC2 | EVENTOL |

Pin descriptions

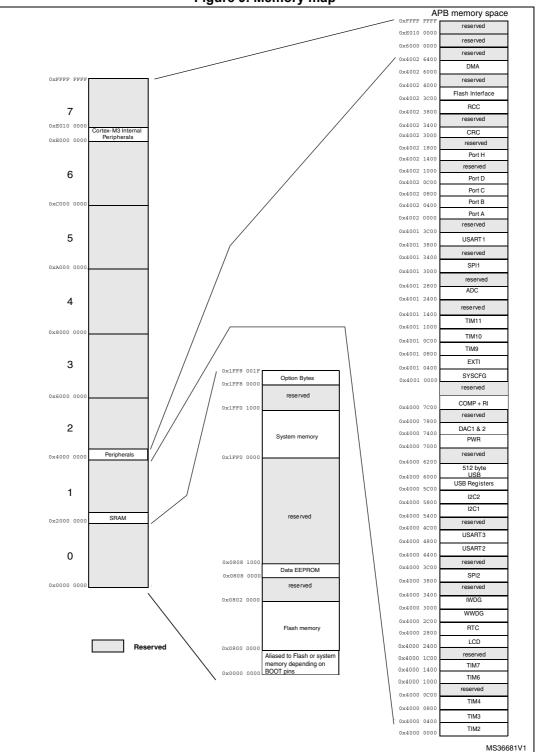

## 5 Memory mapping

The memory map is shown in the following figure.

- 3. Negative injection disturbs the analog performance of the device. See note in Section 6.3.17.

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11* for maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 11: Voltage characteristics* for the maximum allowed input voltage values.

- 6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol            | Ratings                                   | Value                   | Unit |

|-------------------|-------------------------------------------|-------------------------|------|

| T <sub>STG</sub>  | Storage temperature range                 | –65 to +150             | °C   |

| TJ                | Maximum junction temperature              | 150                     | °C   |

| T <sub>LEAD</sub> | Maximum lead temperature during soldering | see note <sup>(1)</sup> | °C   |

#### Table 13. Thermal characteristics

Compliant with JEDEC Std J-STD-020D (for small body, Sn-Pb or Pb assembly), the ST ECOPACK<sup>®</sup> 7191395 specification, and the European directive on Restrictions on Hazardous Substances (ROHS directive 2011/65/EU, July 2011).

## 6.3 Operating conditions

## 6.3.1 General operating conditions

| Table 14. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Symbol                          | Parameter                                          | Conditions                           | Min  | Max                                                         | Unit |  |  |  |

|---------------------------------|----------------------------------------------------|--------------------------------------|------|-------------------------------------------------------------|------|--|--|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                       | -                                    | 0    | 32                                                          |      |  |  |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                      | -                                    | 0    | 32                                                          | MHz  |  |  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                      | -                                    | 0    | 32                                                          |      |  |  |  |

|                                 |                                                    | BOR detector disabled                | 1.65 | 3.6                                                         |      |  |  |  |

| V <sub>DD</sub>                 | Standard operating voltage                         | BOR detector enabled,<br>at power on | 1.8  | 3.6                                                         | v    |  |  |  |

|                                 | BOR detector dis power of                          |                                      | 1.65 | 3.6                                                         |      |  |  |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC and DAC not used) | Must be the same voltage as          | 1.65 | 3.6                                                         | V    |  |  |  |

| VDDA` ′                         | Analog operating voltage<br>(ADC or DAC used)      | V <sub>DD</sub> <sup>(2)</sup>       | 1.8  | 32       32       32       32       3.6       3.6       3.6 |      |  |  |  |

|                                 |                                                    | FT pins: 2.0 V ≤V <sub>DD</sub>      | -0.3 | 5.5 <sup>(3)</sup>                                          |      |  |  |  |

| V                               | I/O input voltage                                  | FT pins: V <sub>DD</sub> < 2.0 V     | -0.3 | 5.25 <sup>(3)</sup>                                         | V    |  |  |  |

| V <sub>IN</sub>                 |                                                    | BOOT0                                | 0    | 5.5                                                         | v    |  |  |  |

|                                 |                                                    | Any other pin                        | -0.3 | V <sub>DD</sub> +0.3                                        |      |  |  |  |

| Symbol         | Parameter                                                                                                        | Conditions                               | Min | Max | Unit |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|------|--|--|

|                |                                                                                                                  | UFBGA100 package                         | -   | 339 |      |  |  |

|                |                                                                                                                  | LQFP100 package                          | -   | 435 |      |  |  |

| Р              | Power dissipation at TA = 85 °C for                                                                              | TFBGA64 package                          | -   | 308 |      |  |  |

| P <sub>D</sub> | suffix 6 or TA = 105 °C for suffix 7 <sup>(4)</sup> LQFP64 package         LQFP48 package       UFQFPN48 package | LQFP64 package                           | -   | 444 | mW   |  |  |

|                |                                                                                                                  | LQFP48 package                           | -   | 364 |      |  |  |

|                |                                                                                                                  | -                                        | 606 |     |      |  |  |

| Та             | Ambient temperature for 6 suffix version                                                                         | Maximum power dissipation <sup>(5)</sup> | -40 | 85  | °C   |  |  |

| IA             | Ambient temperature for 7 suffix version                                                                         | Maximum power dissipation                | -40 | 105 | C    |  |  |

| т.             | Junction temperature range                                                                                       | 6 suffix version                         | -40 | 105 | ŝ    |  |  |

| TJ             | Junction temperature range                                                                                       | 7 suffix version                         | -40 | 110 | °C   |  |  |

Table 14. General operating conditions (continued)

1. When the ADC is used, refer to *Table 55: ADC characteristics*.

2. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

3. To sustain a voltage higher than  $V_{DD}$ +0.3 V, the internal pull-up/pull-down resistors must be disabled.

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 13: Thermal characteristics on page 56).

In low-power dissipation state, T<sub>A</sub> can be extended to -40°C to 105°C temperature range as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see *Table 13: Thermal characteristics on page 56*).

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in the following table.

| Symbol                                                                                          | Parameter                      | Conditions                                          | Min | Тур | Max  | Unit |  |  |  |

|-------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|-----|-----|------|------|--|--|--|

|                                                                                                 | V <sub>DD</sub> rise time rate | BOR detector enabled                                | 0   | -   | ∞    | ×    |  |  |  |

| + (1)                                                                                           | V <sub>DD</sub> lise time late | BOR detector disabled                               | 0   | -   | 1000 |      |  |  |  |

| <sup>t</sup> VDD <sup>(*)</sup>                                                                 | V fall time rate               | BOR detector enabled                                | 20  | -   | ~    | µs/V |  |  |  |

|                                                                                                 | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0   | -   | 1000 |      |  |  |  |

| <b>T</b> (1)                                                                                    | Deast temperization            | V <sub>DD</sub> rising, BOR enabled                 | -   | 2   | 3.3  | ms   |  |  |  |

| t <sub>VDD</sub> <sup>(1)</sup><br>T <sub>RSTTEMPO</sub> <sup>(1)</sup><br>V <sub>POR/PDR</sub> | Reset temporization            | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4 | 0.7 | 1.6  |      |  |  |  |

| V                                                                                               | Power on/power down reset      | Falling edge                                        | 1   | 1.5 | 1.65 | V    |  |  |  |

| V POR/PDR                                                                                       | threshold                      | Rising edge                                         | 1.3 | 1.5 | 1.65 | V    |  |  |  |

#### Table 15. Embedded reset and power control block characteristics

| Symbol               | Parameter            | Cond                                                           | litions                                            | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup>                                                                                                                                                                                                                                           | Unit |

|----------------------|----------------------|----------------------------------------------------------------|----------------------------------------------------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                      |                      |                                                                |                                                    | 1 MHz             | 215   | 285                                                                                                                                                                                                                                                          |      |

|                      |                      |                                                                | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 2 MHz             | 400   | 490                                                                                                                                                                                                                                                          | μA   |

|                      |                      |                                                                |                                                    | 4 MHz             | 725   | 285       490       1000       5       1.3       5       2.15       4       2.9       5.2       5       9.6       4.4       10.2       1                                                                                                                     |      |

|                      |                      | $f_{HSE} = f_{HCLK}$<br>up to 16 MHz, included                 |                                                    | 4 MHz             | 0.915 | 1.3                                                                                                                                                                                                                                                          |      |

|                      |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above                  | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 8 MHz             | 1.75  | 2.15                                                                                                                                                                                                                                                         |      |

|                      | Supply               | 16 MHz<br>(PLL ON) <sup>(2)</sup>                              |                                                    | 16 MHz            | 3.4   | 5       285         0       490         5       1000         15       1.3         75       2.15         4       4         1       2.9         2       5.2         9.6         5       4.4         2       10.2         41       0.085         25       0.180 | -    |

|                      | Supply<br>current in | ( ,                                                            |                                                    | 8 MHz             | 2.1   | 2.9                                                                                                                                                                                                                                                          |      |

| I <sub>DD (Run</sub> | Run mode,<br>code    |                                                                | VOS[1:0] = 01<br>32 Mł                             | 16 MHz            | 4.2   | 5.2                                                                                                                                                                                                                                                          |      |

| from Flash)          | executed             |                                                                |                                                    | 32 MHz            | 8.25  | 9.6                                                                                                                                                                                                                                                          |      |

|                      | from Flash           | HSI clock source (16                                           |                                                    | 16 MHz            | 3.5   | 4.4                                                                                                                                                                                                                                                          | mA   |

|                      |                      | MHz) Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 32 MHz | 32 MHz                                             | 8.2               | 10.2  |                                                                                                                                                                                                                                                              |      |

|                      |                      | MSI clock, 65 kHz                                              |                                                    | 65 kHz            | 0.041 | 0.085                                                                                                                                                                                                                                                        |      |

|                      |                      | MSI clock, 524 kHz                                             | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 524 kHz           | 0.125 | 0.180                                                                                                                                                                                                                                                        |      |

|                      |                      | MSI clock, 4.2 MHz                                             |                                                    | 4.2 MHz           | 0.775 | 0.935                                                                                                                                                                                                                                                        |      |

#### Table 18. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter            | Cond                                                                                                      | litions                                               | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------|--------------------|------|

|                 |                      |                                                                                                           | Range 3,                                              | 1 MHz             | 50   | 155                |      |

|                 |                      |                                                                                                           | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 78.5 | 235                |      |

|                 |                      |                                                                                                           | VOS[1:0] = 11                                         | 4 MHz             | 140  | 370 <sup>(3)</sup> |      |

|                 |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                                            | Range 2,                                              | 4 MHz             | 165  | 375                |      |

|                 |                      | $f_{HSE} = f_{HCLK}/2$                                                                                    | V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10             | 8 MHz             | 310  | 530                |      |

|                 |                      | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                      |                                                       | 16 MHz            | 590  | 1000               |      |

|                 | Quanta               |                                                                                                           | Range 1,                                              | 8 MHz             | 350  | 615                |      |

|                 | Supply<br>current in |                                                                                                           | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 680  | 1200               |      |

|                 | Sleep                |                                                                                                           | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2350               | μA   |

|                 | mode,<br>Flash OFF   | HSI clock source                                                                                          | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 640  | 970                |      |

|                 |                      | V <sub>CO</sub>                                                                                           | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2350               |      |

|                 |                      | MSI clock, 65 kHz                                                                                         | Range 3,                                              | 65 kHz            | 19   | 60                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                        | V <sub>CORE</sub> =1.2 V                              | 524 kHz           | 33   | 90                 |      |

| I <sub>DD</sub> |                      | MSI clock, 4.2 MHz                                                                                        | VOS[1:0] = 11                                         | 4.2 MHz           | 145  | 210                |      |

| (Sleep)         |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 60.5 | 145                |      |

|                 |                      |                                                                                                           |                                                       | 2 MHz             | 89.5 | 225                |      |

|                 |                      |                                                                                                           |                                                       | 4 MHz             | 150  | 360                |      |

|                 |                      |                                                                                                           | ded, Range 2,<br>2 V <sub>CORE</sub> =1.5 V           | 4 MHz             | 180  | 370                |      |

|                 |                      |                                                                                                           |                                                       | 8 MHz             | 320  | 490                |      |

|                 |                      | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                      |                                                       | 16 MHz            | 605  | 895                |      |

|                 | Supply               | ,                                                                                                         | Range 1,                                              | 8 MHz             | 380  | 565                |      |

|                 | current in           |                                                                                                           | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 695  | 1070               |      |

|                 | Sleep                |                                                                                                           | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2200               | μA   |

|                 | mode,<br>Flash ON    | lash ON<br>HSI clock source<br>(16 MHz)                                                                   | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 650  | 970                |      |

|                 |                      |                                                                                                           | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2320               |      |

|                 |                      | MSI clock, 65 kHz                                                                                         | Range 3,                                              | 65 kHz            | 29.5 | 65                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                        | V <sub>CORE</sub> =1.2V                               | 524 kHz           | 44   | 80                 |      |

|                 |                      | MSI clock, 4.2 MHz                                                                                        | VOS[1:0] = 11                                         | 4.2 MHz           | 155  | 220                |      |

Table 20. Current consumption in Sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

3. Guaranteed by test in production.

| Symbol                         | Parameter                            | Conditions                                                          | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|--------------------------------|--------------------------------------|---------------------------------------------------------------------|---------------------|---------------------|------|

| Input leve                     | ls                                   |                                                                     |                     |                     |      |

| $V_{DD}$                       | USB operating voltage <sup>(2)</sup> | -                                                                   | 3.0                 | 3.6                 | V    |

| $V_{DI}^{(3)}$                 | Differential input sensitivity       | I(USB_DP, USB_DM)                                                   | 0.2                 | -                   |      |

| V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range       | Includes V <sub>DI</sub> range                                      | 0.8                 | 2.5                 | V    |

| $V_{SE}^{(3)}$                 | Single ended receiver threshold      | -                                                                   | 1.3                 | 2.0                 |      |

| Output le                      | vels                                 |                                                                     |                     |                     |      |

| $V_{OL}^{(4)}$                 | Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(5)}$          | -                   | 0.3                 | v    |

| V <sub>OH</sub> <sup>(4)</sup> | Static output level high             | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}^{(5)}$ | 2.8                 | 3.6                 |      |

Table 52. USB DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. Guaranteed by characterization results.

4. Guaranteed by test in production.

5.  $\ensuremath{\,R_L}$  is the load connected on the USB drivers.

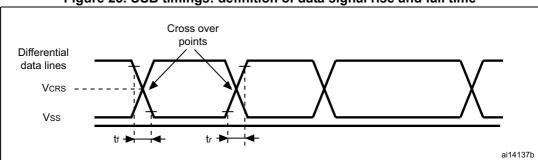

#### Figure 25. USB timings: definition of data signal rise and fall time

#### Table 53. USB: full speed electrical characteristics

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |      |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol                                | Parameter                       | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification section 7 (version 2.0).

## 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | C                                                                           | onditions              | Min   | Тур       | Max                       | Unit |

|---------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------|------------------------|-------|-----------|---------------------------|------|

| V <sub>DDA</sub>                | Analog supply voltage                                 |                                                                             | -                      |       | -         | 3.6                       | V    |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                  |                        | 1.8   | -         | 3.6                       | V    |

| V <sub>REF-</sub>               | Lower reference voltage                               | -                                                                           |                        |       | $V_{SSA}$ |                           | V    |

| (4)                             | Current consumption on                                | No load, mid                                                                | dle code (0x800)       | -     | 130       | 220                       | μA   |

| I <sub>DDVREF+</sub> (1)        | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                                                                | st code (0x000)        | -     | 220       | 350                       | μA   |

|                                 | Current consumption on                                | No load, mid                                                                | ldle code (0x800)      | -     | 210       | 320                       | μA   |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, worst code (0xF1C)                                                 |                        | -     | 320       | 520                       | μA   |

| D                               | Resistive load                                        | DAC output                                                                  | Connected to $V_{SSA}$ | 5     | -         | -                         | kΩ   |

| R <sub>L</sub>                  | Resistive load                                        | buffer ON Connected to V <sub>DDA</sub>                                     |                        | 25    | -         | -                         | K52  |

| CL                              | Capacitive load                                       | DAC output                                                                  | buffer ON              | -     | -         | 50                        | pF   |

| R <sub>O</sub>                  | Output impedance                                      | DAC output                                                                  | buffer OFF             | 12    | 16        | 20                        | kΩ   |

|                                 | Voltage on DAC_OUT                                    | DAC output                                                                  | buffer ON              | 0.2   | -         | V <sub>DDA</sub> –<br>0.2 | V    |

| V <sub>DAC_OUT</sub>            | output                                                | DAC output                                                                  | buffer OFF             | 0.5   | -         | V <sub>REF+</sub><br>1LSB | mV   |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>             | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                        | -     | 1.5       | 3                         |      |

| Ditt                            |                                                       | No $R_L$ , $C_L \le DAC$ output                                             |                        | - 1.5 |           | 3                         |      |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF, F}$<br>DAC output                                    | -                      | -     | 2         | 4                         |      |

|                                 | Integral nor linearity ·                              | No $R_L$ , $C_L \le DAC$ output                                             |                        | -     | 2         | 4                         | LSB  |

| Offset <sup>(1)</sup>           | Offset error at code 0x800 <sup>(4)</sup>             | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                        | -     | ±10       | ±25                       |      |

|                                 |                                                       | No $R_L$ , $C_L \le DAC$ output                                             | -                      | -     | ±5        | ±8                        |      |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>             | No $R_L$ , $C_L \le DAC$ output                                             |                        | -     | ±1.5      | ±5                        |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

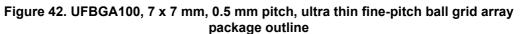

# 7.5 UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package information

1. Drawing is not to scale.

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |

|----------------------------------------------------------------------------------|

| package mechanical data                                                          |

| puolitigo moonaniour auta |      |             |      |                       |        |        |  |  |  |  |

|---------------------------|------|-------------|------|-----------------------|--------|--------|--|--|--|--|

| Cumhal                    |      | millimeters |      | inches <sup>(1)</sup> |        |        |  |  |  |  |

| Symbol                    | Min  | Тур         | Мах  | Min                   | Тур    | Мах    |  |  |  |  |

| А                         | -    | -           | 0.6  | -                     | -      | 0.0236 |  |  |  |  |

| A1                        | 0.05 | 0.08        | 0.11 | 0.002                 | 0.0031 | 0.0043 |  |  |  |  |

| A2                        | 0.4  | 0.45        | 0.5  | 0.0157                | 0.0177 | 0.0197 |  |  |  |  |

| A3                        | 0.08 | 0.13        | 0.18 | 0.0031                | 0.0051 | 0.0071 |  |  |  |  |

| A4                        | 0.27 | 0.32        | 0.37 | 0.0106                | 0.0126 | 0.0146 |  |  |  |  |

| b                         | 0.2  | 0.25        | 0.3  | 0.0079                | 0.0098 | 0.0118 |  |  |  |  |

| D                         | 6.95 | 7           | 7.05 | 0.2736                | 0.2756 | 0.2776 |  |  |  |  |

| D1                        | 5.45 | 5.5         | 5.55 | 0.2146                | 0.2165 | 0.2185 |  |  |  |  |

| Е                         | 6.95 | 7           | 7.05 | 0.2736                | 0.2756 | 0.2776 |  |  |  |  |

| E1                        | 5.45 | 5.5         | 5.55 | 0.2146                | 0.2165 | 0.2185 |  |  |  |  |

| е                         | -    | 0.5         | -    | -                     | 0.0197 | -      |  |  |  |  |

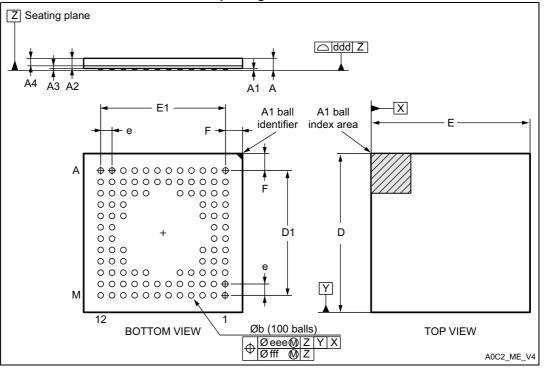

#### **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 47. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 8 Ordering information

| Table 73. Ordering info                                | ormation | schem | е  |       |   |      |

|--------------------------------------------------------|----------|-------|----|-------|---|------|

| Example:                                               | STM32    | L 152 | RB | Т 6   | А | D TR |

|                                                        |          |       |    |       |   |      |

| Device family                                          |          |       |    |       |   |      |

| STM32 = ARM-based 32-bit microcontroller               |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Product type                                           |          |       |    |       |   |      |

| L = Low-power                                          |          | _     |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Device subfamily                                       |          |       |    |       |   |      |

| 151: Devices without LCD                               |          |       |    |       |   |      |

| 152: Devices with LCD                                  |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Pin count                                              |          |       |    |       |   |      |

| C = 48 pins                                            |          |       |    |       |   |      |

| R = 64 pins                                            |          |       |    |       |   |      |

| V = 100 pins                                           |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Flash memory size                                      |          |       |    |       |   |      |

| 6 = 32 Kbytes of Flash memory                          |          |       |    |       |   |      |

| 8 = 64 Kbytes of Flash memory                          |          |       |    |       |   |      |

| B = 128 Kbytes of Flash memory                         |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Package                                                |          |       |    |       |   |      |

| H = BGA                                                |          |       |    |       |   |      |

| T = LQFP                                               |          |       |    |       |   |      |

| U = UFQFPN                                             |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Temperature range                                      |          |       |    |       |   |      |

| 6 = Industrial temperature range, -40 to 85 °C         |          |       |    | · · · |   |      |

| 7 = Industrial temperature range, -40 to 105 °C        |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| Options                                                |          |       |    |       |   |      |

| A = device generation A                                |          |       |    |       |   |      |

|                                                        |          |       |    |       |   |      |

| No character = VDD range: 1.8 to 3.6 V and BOR enabled |          |       |    |       |   |      |

| D = VDD range: 1.65 to 3.6 V and BOR disabled          |          |       |    |       |   |      |

| ,                                                      |          |       |    |       |   |      |

| Packing                                                |          |       |    |       |   |      |

| TR = tape and reel                                     |          |       |    |       |   |      |

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved