Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151vbh6a  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | Ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A block diagram 13            |

|------------|-------------------------------------------------------------------------------------|

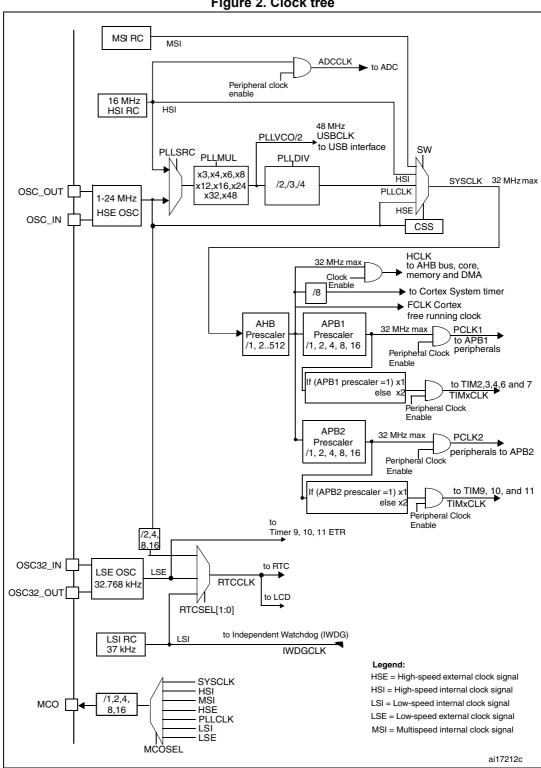

| Figure 2.  | Clock tree                                                                          |

| Figure 3.  | STM32L15xVxxxA UFBGA100 ballout                                                     |

| Figure 4.  | STM32L15xVxxxA LQFP100 pinout                                                       |

| Figure 5.  | STM32L15xRxxxA TFBGA64 ballout                                                      |

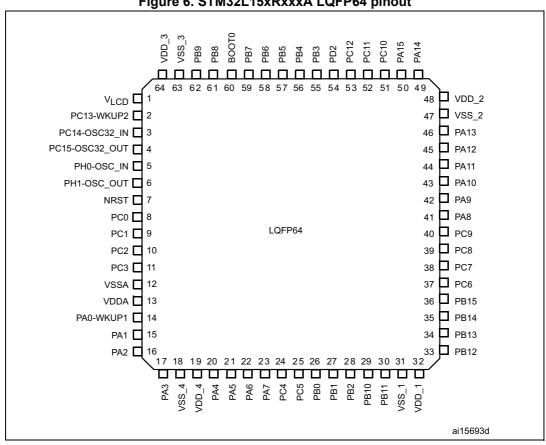

| Figure 6.  | STM32L15xRxxxA LQFP64 pinout                                                        |

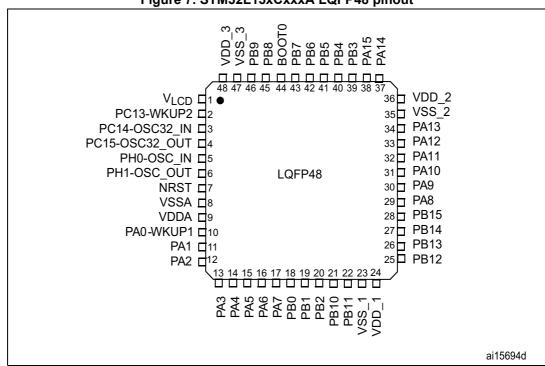

| Figure 7.  | STM32L15xCxxxA LQFP48 pinout                                                        |

| Figure 8.  | STM32L15xCxxxA UFQFPN48 pinout                                                      |

| Figure 9.  | Memory map                                                                          |

| Figure 10. | Pin loading conditions                                                              |

| Figure 11. | Pin input voltage                                                                   |

| Figure 12. | Power supply scheme                                                                 |

| Figure 13. | Optional LCD power supply scheme                                                    |

| Figure 14. | Current consumption measurement scheme                                              |

| Figure 15. | High-speed external clock source AC timing diagram                                  |

| Figure 16. | Low-speed external clock source AC timing diagram                                   |

| Figure 17. | HSE oscillator circuit diagram                                                      |

| Figure 18. | Typical application with a 32.768 kHz crystal                                       |

| Figure 19. | I/O AC characteristics definition                                                   |

| Figure 20. | Recommended NRST pin protection                                                     |

| Figure 21. | I <sup>2</sup> C bus AC waveforms and measurement circuit                           |

| Figure 22. | SPI timing diagram - slave mode and CPHA = 0                                        |

| Figure 23. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                         |

| Figure 24. | SPI timing diagram - master mode <sup>(1)</sup>                                     |

| Figure 25. | USB timings: definition of data signal rise and fall time                           |

| Figure 26. | ADC accuracy characteristics                                                        |

| Figure 27. | Typical connection diagram using the ADC                                            |

| Figure 28. | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC      |

| 5          | conversion                                                                          |

| Figure 29. | 12-bit buffered /non-buffered DAC                                                   |

| Figure 30. | LQFP100 14 x 14 mm, 100-pin low-profile quad flat package outline                   |

| Figure 31. | LQPF100 14 x 14 mm, 100-pin low-profile quad flat package recommended footprint 108 |

| Figure 32. | LQFP100 14 x 14 mm, 100-pin package top view example                                |

| Figure 33. | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline                     |

| Figure 34. | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package recommended footprint 110   |

| Figure 35. | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example 111        |

| Figure 36. | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package outline                       |

| Figure 37. | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package recommended footprint 114     |

| Figure 38. | LQFP48 7 x 7 mm, 48-pin low-profile quad flat package top view example              |

| Figure 39. | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline                                    |

| Figure 40. | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package recommended footprint                      |

| Figure 41. | UFQFPN48 7 x 7 mm, 0.5 mm pitch, package top view example                           |

| Figure 42. | UFBGA100, 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array             |

|            | package outline                                                                     |

| Figure 43. | UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array              |

|            | package recommended footprint                                                       |

| Figure 44. | UFBGA100 7 x 7 mm, 0.5 mm pitch, package top view example                           |

| Figure 45. | TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array                     |

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From a proprietary 8bit core up to the Cortex-M3, including the Cortex-M0+, the STM8Lx and STM32Lx series offer the best range of choices to meet your requirements in terms of ultra-low-power features. The STM32 Ultra-low-power series is an ideal fit for applications like gas/water meters, keyboard/mouse, or wearable devices for fitness and healthcare. Numerous built-in features like LCD drivers, dual-bank memory, low-power Run mode, op-amp, AES-128bit, DAC, crystal-less USB and many others, allow to build highly cost-optimized applications by reducing the BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lx and STM32Lx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, your existing applications can be upgraded to respond to the latest market features and efficiency demand.

## 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-Low-power performance to range from 5 up to 33.3 DMIPs.

## 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

## 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xxx and STM32L1xxxx families use a common architecture:

- Common power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xxx devices)

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultra-safe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

## 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 512 Kbytes

## 3.1 Low-power modes

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply:

- In Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), the CPU runs at up to 32 MHz (refer to Table 18 for consumption).

- In Range 2 (full V<sub>DD</sub> range), the CPU runs at up to 16 MHz (refer to *Table 18* for consumption)

- In Range 3 (full V<sub>DD</sub> range), the CPU runs at up to 4 MHz (generated only with the multispeed internal RC oscillator clock source). Refer to *Table 18* for consumption.

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Sleep mode power consumption: refer to Table 20.

Low-power Run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (less than 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In the low-power Run mode, the clock frequency and the number of enabled peripherals are both limited.

Low-power Run mode consumption: refer to Table 21.

• Low-power Sleep mode

This mode is achieved by entering the Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In the low-power Sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

Low-power Sleep mode consumption: refer to *Table 22*.

• Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

• Stop mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices embed a nested vectored interrupt controller able to handle up to 45 maskable interrupt channels (not including the 16 interrupt lines of Cortex-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.3 Reset and supply management

#### 3.3.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

#### 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the  $V_{DD}$  min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Figure 2. Clock tree

## 3.9 LCD (liquid crystal display)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rail decoupling capability

|                       |                      | Bias                 | Р                    | <b>1</b> 4 |      |  |

|-----------------------|----------------------|----------------------|----------------------|------------|------|--|

|                       | 1/2                  | 1/3                  | 1/4                  | Pin        |      |  |

| V <sub>LCDrail1</sub> | 1/2 V <sub>LCD</sub> | 2/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | PB2        |      |  |

| V <sub>LCDrail2</sub> | NA                   | 1/3 V <sub>LCD</sub> | 1/4 V <sub>LCD</sub> | PB12       | PE11 |  |

| V <sub>LCDrail3</sub> | NA                   | NA                   | 3/4 V <sub>LCD</sub> | PB0        | PE12 |  |

#### Table 6. V<sub>LCD</sub> rail decoupling

## 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L151x6/8/B-A and STM32L152x6/8/B-A devices with up to 24 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

|   |                        | Figure               | 5. STM3 | 2L15xRx              |                      | GA64 ball            | out            |        |

|---|------------------------|----------------------|---------|----------------------|----------------------|----------------------|----------------|--------|

|   | 1                      | 2                    | 3       | 4                    | 5                    | 6                    | 7              | 8      |

| A | , PC14-,<br>0\\$C32_lN | , PC13-,<br>WKUP2    | ( PB9 ) | , PB4 )              | ( PB3 )              | (PA15)               | (PA14)         | (PA13) |

| В | /PC15-\<br>O\$C32_OUT  | - (VLCD)             | ( PB8 ) | BOOTO                | (PD2)                | (PC11)               | (PC10)         | (PA12) |

| С | , ∕₽́ĤÒ`,<br>OSC_IN;   | Vss_4                | ( PB7 ) | ( PB5 )              | (PC12)               | (PA10)               | (PA9)          | (PA11) |

| D | OSC_OUT                | 'V <sub>DD_4</sub> ' | ( PB6 ) | VSS_3                | VSS_2                | ,V <sub>SS_1</sub> , | (PA8)          | (PC9)  |

| E | (NRST)                 | (PC1)                | ( PC0 ) | 'V <sub>DD_3</sub> ' | 'V <sub>DD_2</sub> ' | ,V <sub>DD_1</sub> , | (PC7)          | (PC8)  |

| F | VSSA                   | (PC2)                | ( PA2 ) | ( PA5 )              | ( PB0 )              | (PC6)                | (PB15)         | (PB14) |

| G | VREF+                  | PAO-WKUP1            | ( PA3 ) | ( PA6 )              | // PB1 )             | ( PB2 )              | (PB10)         | (PB13) |

| н | VDDA                   | ( PA1 )              | ( PA4 ) | ( PA7 )              | ( PC4 )              | (PC5)                | // (<br>(PB11) | (PB12) |

|   |                        |                      |         |                      |                      |                      |                | Al1609 |

Figure 5. STM32L15xRxxxA TFBGA64 ballout

1. This figure shows the package top view.

Figure 6. STM32L15xRxxxA LQFP64 pinout

1. This figure shows the package top view.

Figure 7. STM32L15xCxxxA LQFP48 pinout

1. This figure shows the package top view.

|         |        | Pins      | ;        |                    |                   |                         |               |                                                  | Pins functio                                     | ns                                            |

|---------|--------|-----------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64   | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                              | Additional<br>functions                       |

| 20      | -      | -         | K1       | -                  | V <sub>REF-</sub> | S                       | -             | V <sub>REF-</sub>                                | -                                                | -                                             |

| 21      | -      | G1<br>(6) | L1       | -                  | V <sub>REF+</sub> | S                       | -             | V <sub>REF+</sub>                                | -                                                | -                                             |

| 22      | 13     | H1        | M1       | 9                  | V <sub>DDA</sub>  | S                       | -             | V <sub>DDA</sub>                                 | -                                                | -                                             |

| 23      | 14     | G2        | L2       | 10                 | PA0-WKUP1         | I/O                     | FT            | PA0                                              | USART2_CTS/<br>TIM2_CH1_ETR                      | WKUP1/<br>ADC_IN0/<br>COMP1_INP<br>/RTC_TAMP2 |

| 24      | 15     | H2        | M2       | 11                 | PA1               | I/O                     | FT            | PA1                                              | USART2_RTS/<br>TIM2_CH2/LCD_SEG0                 | ADC_IN1/<br>COMP1_INP                         |

| 25      | 16     | F3        | КЗ       | 12                 | PA2               | I/O                     | FT            | PA2                                              | USART2_TX/<br>TIM2_CH3/<br>TIM9_CH1/<br>LCD_SEG1 | ADC_IN2/<br>COMP1_INP                         |

| 26      | 17     | G3        | L3       | 13                 | PA3               | I/O                     | тс            | PA3                                              | USART2_RX/<br>TIM2_CH4/<br>TIM9_CH2/<br>LCD_SEG2 | ADC_IN3/<br>COMP1_INP                         |

| 27      | 18     | C2        | E3       | -                  | V <sub>SS_4</sub> | S                       | -             | $V_{SS_4}$                                       | -                                                | -                                             |

| 28      | 19     | D2        | H3       | -                  | $V_{DD_4}$        | S                       | -             | $V_{DD_4}$                                       | -                                                | -                                             |

| 29      | 20     | H3        | М3       | 14                 | PA4               | I/O                     | тс            | PA4                                              | SPI1_NSS/<br>USART2_CK                           | ADC_IN4/<br>DAC_OUT1/<br>COMP1_INP            |

| 30      | 21     | F4        | K4       | 15                 | PA5               | I/O                     | тс            | PA5                                              | SPI1_SCK/<br>TIM2_CH1_ETR                        | ADC_IN5/<br>DAC_OUT2/<br>COMP1_INP            |

| 31      | 22     | G4        | L4       | 16                 | PA6               | I/O                     | FT            | PA6                                              | SPI1_MISO/TIM3_CH1/<br>LCD_SEG3/TIM10_CH1        | ADC_IN6/<br>COMP1_INP                         |

| 32      | 23     | H4        | M4       | 17                 | PA7               | I/O                     | FT            | PA7                                              | SPI1_MOSI/TIM3_CH2/<br>LCD_SEG4/TIM11_CH1        | ADC_IN7/<br>COMP1_INP                         |

| 33      | 24     | H5        | K5       | -                  | PC4               | I/O                     | FT            | PC4                                              | LCD_SEG22                                        | ADC_IN14/<br>COMP1_INP                        |

| 34      | 25     | H6        | L5       | -                  | PC5               | I/O                     | FT            | PC5                                              | LCD_SEG23                                        | ADC_IN15/<br>COMP1_INP                        |

## Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

|         |        |         |          | 1 11/32            |          | 14 31                   | INISZL        | 152X0/0/D-A                                      | pin definitions (contin                                      | •                                    |

|---------|--------|---------|----------|--------------------|----------|-------------------------|---------------|--------------------------------------------------|--------------------------------------------------------------|--------------------------------------|

|         | 1      | Pins    | ;        | 1                  |          |                         |               |                                                  | Pins functio                                                 | ns                                   |

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                          | Additional<br>functions              |

| 51      | 33     | H8      | L12      | 25                 | PB12     | I/O                     | FT            | PB12                                             | SPI2_NSS/I2C2_SMBA/<br>USART3_CK/<br>LCD_SEG12/<br>TIM10_CH1 | ADC_IN18/<br>COMP1_INP<br>/VLCDRAIL2 |

| 52      | 34     | G8      | K12      | 26                 | PB13     | I/O                     | FT            | PB13                                             | SPI2_SCK/<br>USART3_CTS/<br>LCD_SEG13/TIM9_CH1               | ADC_IN19/<br>COMP1_INP               |

| 53      | 35     | F8      | K11      | 27                 | PB14     | I/O                     | FT            | PB14                                             | SPI2_MISO/<br>USART3_RTS/<br>LCD_SEG14/TIM9_CH2              | ADC_IN20/<br>COMP1_INP               |

| 54      | 36     | F7      | K10      | 28                 | PB15     | I/O                     | FT            | PB15                                             | SPI2_MOSI/<br>LCD_SEG15/<br>TIM11_CH1                        | ADC_IN21/<br>COMP1_INP/<br>RTC_REFIN |

| 55      | -      | -       | K9       | -                  | PD8      | I/O                     | FT            | PD8                                              | USART3_TX/<br>LCD_SEG28                                      | -                                    |

| 56      | -      | -       | K8       | -                  | PD9      | I/O                     | FT            | PD9                                              | USART3_RX/<br>LCD_SEG29                                      | -                                    |

| 57      | -      | -       | J12      | -                  | PD10     | I/O                     | FT            | PD10                                             | USART3_CK/<br>LCD_SEG30                                      | -                                    |

| 58      | -      | -       | J11      | -                  | PD11     | I/O                     | FT            | PD11                                             | USART3_CTS/<br>LCD_SEG31                                     | -                                    |

| 59      | -      | -       | J10      | -                  | PD12     | I/O                     | FT            | PD12                                             | TIM4_CH1/<br>USART3_RTS/<br>LCD_SEG32                        | -                                    |

| 60      | -      | -       | H12      | -                  | PD13     | I/O                     | FT            | PD13                                             | TIM4_CH2/LCD_SEG33                                           | -                                    |

| 61      | -      | -       | H11      | -                  | PD14     | I/O                     | FT            | PD14                                             | TIM4_CH3/LCD_SEG34                                           | -                                    |

| 62      | -      | -       | H10      | -                  | PD15     | I/O                     | FT            | PD15                                             | TIM4_CH4/LCD_SEG35                                           | -                                    |

| 63      | 37     | F6      | E12      | -                  | PC6      | I/O                     | FT            | PC6                                              | TIM3_CH1/LCD_SEG24                                           | -                                    |

| 64      | 38     | E7      | E11      | -                  | PC7      | I/O                     | FT            | PC7                                              | TIM3_CH2/LCD_SEG25                                           | -                                    |

| 65      | 39     | E8      | E10      | -                  | PC8      | I/O                     | FT            | PC8                                              | TIM3_CH3/LCD_SEG26                                           | -                                    |

| 66      | 40     | D8      | D12      | -                  | PC9      | I/O                     | FT            | PC9                                              | TIM3_CH4/LCD_SEG27                                           | -                                    |

## Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

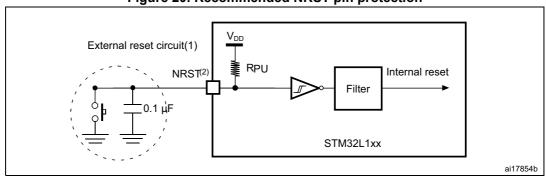

Figure 20. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 46. Otherwise the reset will not be taken into account by the device.

## 6.3.15 TIM timer characteristics

The parameters given in *Table 47* are guaranteed by design.

Refer to *Section 6.3.13: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter Conditions Mi                                                   |                               | Min    | Мах                     | Unit                 |  |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|--|--|--|--|--|

| t                      | Timer resolution time                                                     | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |  |  |  |  |  |  |

| <sup>t</sup> res(TIM)  |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |  |  |  |  |  |  |

| f                      | Timer external clock                                                      | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |  |  |  |  |  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                                                   | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |  |  |  |  |  |  |

| Res <sub>TIM</sub>     | Timer resolution                                                          | -                             | -      | 16                      | bit                  |  |  |  |  |  |  |

|                        | 16-bit counter clock                                                      | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |  |  |  |  |  |

| <sup>t</sup> COUNTER   | period when internal clock<br>is selected (timer's<br>prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |  |  |  |  |  |  |

| t                      | Maximum possible count                                                    | _                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |  |  |  |  |  |

| <sup>t</sup> MAX_COUNT |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |  |  |  |  |  |  |

Table 47. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM2, TIM3 and TIM4 timers.

### 6.3.16 Communication interfaces

## I<sup>2</sup>C interface characteristics

The STM32L151x6/8/B-A and STM32L152x6/8/B-A product line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            |     | rd mode<br>1)(2)    | Fast mode | Unit               |    |

|--------------------------------------------|----------------------------------------------------------------------|-----|---------------------|-----------|--------------------|----|

|                                            |                                                                      | Min | Мах                 | Min       | Мах                |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7 | -                   | 1.3       | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250 | -                   | 100       | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -   | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -   | 1000                | -         | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -   | 300                 | -         | 300                |    |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0 | -                   | 0.6       | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7 | -                   | 0.6       | -                  | μs |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7 | -                   | 1.3       | -                  | μs |

| Cb                                         | Capacitive load for each bus line                                    | -   | 400                 | -         | 400                | pF |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0   | 50 <sup>(4)</sup>   | 0         | 50 <sup>(4)</sup>  | ns |

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

## 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | C                                          | Conditions                    |     |                           | Max | Unit |

|---------------------------------|-------------------------------------------------------|--------------------------------------------|-------------------------------|-----|---------------------------|-----|------|

| V <sub>DDA</sub>                | Analog supply voltage                                 |                                            | 1.8                           | -   | 3.6                       | V   |      |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must<br>V <sub>DDA</sub> | always be below               | 1.8 | -                         | 3.6 | V    |

| V <sub>REF-</sub>               | Lower reference voltage                               | -                                          |                               |     | $V_{SSA}$                 |     | V    |

| (4)                             | Current consumption on                                | No load, mid                               | dle code (0x800)              | -   | 130                       | 220 | μA   |

| I <sub>DDVREF+</sub> (1)        | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                               | st code (0x000)               | -   | 220                       | 350 | μA   |

| (1)                             | Current consumption on                                | No load, mid                               | ldle code (0x800)             | -   | 210                       | 320 | μA   |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wor                               | st code (0xF1C)               | -   | 320                       | 520 | μA   |

| D                               | Resistive load                                        | DAC output                                 | Connected to $V_{SSA}$        | 5   | -                         | -   | kΩ   |

| R <sub>L</sub>                  | Resistive load                                        | buffer ON                                  | Connected to V <sub>DDA</sub> | 25  | -                         | -   | K52  |

| CL                              | Capacitive load                                       | DAC output                                 | buffer ON                     | -   | -                         | 50  | pF   |

| R <sub>O</sub>                  | Output impedance                                      | DAC output                                 | buffer OFF                    | 12  | 16                        | 20  | kΩ   |

|                                 | Voltage on DAC_OUT                                    | DAC output                                 | 0.2                           | -   | V <sub>DDA</sub> –<br>0.2 | V   |      |

| V <sub>DAC_OUT</sub>            | output                                                | DAC output                                 | 0.5                           | -   | V <sub>REF+</sub><br>1LSB | mV  |      |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>             | C <sub>L</sub> ≤50 pF, F<br>DAC output     | -                             | 1.5 | 3                         |     |      |

| Ditt                            |                                                       | No $R_L$ , $C_L \le DAC$ output            | -                             | 1.5 | 3                         |     |      |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF, F}$<br>DAC output   | -                             | 2   | 4                         |     |      |

|                                 | Integral nor linearity ·                              | No $R_L$ , $C_L \le DAC$ output            |                               | -   | 2                         | 4   | LSB  |

| Offset <sup>(1)</sup>           | Offset error at code 0x800 <sup>(4)</sup>             | $C_{L} \le 50 \text{ pF, F}$<br>DAC output | -                             | ±10 | ±25                       |     |      |

| UIISEL' '                       |                                                       | No $R_L$ , $C_L \le DAC$ output            | -                             | ±5  | ±8                        |     |      |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>             | No $R_L$ , $C_L \le DAC$ output            |                               | -   | ±1.5                      | ±5  |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

| Symbol                    | Parameter                                                                                                                                                    | Conditions                                                                           | Min | Тур             | Max              | Unit    |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------|------------------|---------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                     | $V_{DDA} = 3.3V, V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF    | -20 | -10             | 0                | - μV/°C |  |

| uonseva t                 | coefficient (code 0x800)                                                                                                                                     | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | 0   | 20              | 50               | μν/ Ο   |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                    | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON           | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %       |  |

| Gainty                    | Gainenor                                                                                                                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | +0 / -<br>0.2%  | +0 / -<br>0.4%   | 70      |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                       | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF | -10 | -2              | 0                | -μV/°C  |  |

| dGain/d1(")               | coefficient                                                                                                                                                  | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | -40 | -8              | 0                | μν/ Ο   |  |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                       | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON          | -   | 12              | 30               | LSB     |  |

|                           |                                                                                                                                                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | 8               | 12               | LOD     |  |

| tSETTLING                 | Settling time (full scale: for a<br>12-bit code transition<br>between the lowest and the<br>highest input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 7               | 12               | μs      |  |

| Update rate               | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -               | 1                | Msps    |  |

| t <sub>WAKEUP</sub>       | Wakeup time from off state<br>(setting the ENx bit in the<br>DAC Control register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 9               | 15               | μs      |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection ratio (static DC measurement)                                                                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -60             | -35              | dB      |  |

Table 58. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 5. Difference between the value measured at Code (0x001) and the ideal value.

- 6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

## 6.3.20 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |  |  |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|--|--|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |  |  |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |  |  |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | N32       |  |  |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                                     | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |  |  |  |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 |           |  |  |  |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | μs        |  |  |  |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |  |  |  |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |  |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |  |  |  |

Table 61. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

## 6.3.21 LCD controller (STM32L152x6/8/B-A devices only)

The STM32L152xx-A devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol                           | Parameter                                                                                        |                                  | Тур                  | Max       | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------|----------------------|-----------|------|

| $V_{LCD}$                        | LCD external voltage                                                                             | -                                | -                    | 3.6       |      |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                                                                 | -                                | 2.6                  | -         |      |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                                                                 | -                                | 2.73                 | -         |      |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2LCD internal reference voltage 3LCD internal reference voltage 4 |                                  | 2.86                 | -         |      |

| V <sub>LCD3</sub>                |                                                                                                  |                                  | 2.98                 | -         | V    |

| $V_{LCD4}$                       |                                                                                                  |                                  | 3.12                 | -         | 1    |

| $V_{LCD5}$                       | LCD internal reference voltage 5                                                                 | -                                | 3.26                 | -         | 1    |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                                                                 | -                                | 3.4                  | -         |      |

| V <sub>LCD7</sub>                | LCD internal reference voltage 7                                                                 | -                                | 3.55                 | -         |      |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                                                            |                                  | -                    | 2         | μF   |

| ı (1)                            | Supply current at V <sub>DD</sub> = 2.2 V                                                        | at V <sub>DD</sub> = 2.2 V - 3.3 |                      | -         |      |

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at V <sub>DD</sub> = 3.0 V                                                        | -                                | 3.1                  | -         | μA   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                                                        |                                  | 6.6                  | 7.92      | MΩ   |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                                                         | 192                              | 240                  | 288       | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                                                             | -                                | -                    | $V_{LCD}$ | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                                                                 | -                                | 3/4 V <sub>LCD</sub> | -         |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                                                                 | -                                | 2/3 V <sub>LCD</sub> | -         |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                                                                 | -                                | 1/2 V <sub>LCD</sub> | -         | V    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                                                                 | -                                | 1/3 V <sub>LCD</sub> | -         | V    |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                                                                 | -                                | 1/4 V <sub>LCD</sub> | -         | 1    |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                                                              | 0                                | -                    | -         | 1    |

| $\Delta Vxx^{(2)}$               | Segment/Common level voltage error $T_A = -40$ to 105 ° C                                        | -                                | -                    | ±50       | mV   |

#### Table 63. LCD controller characteristics

1. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

2. Guaranteed by characterization results.

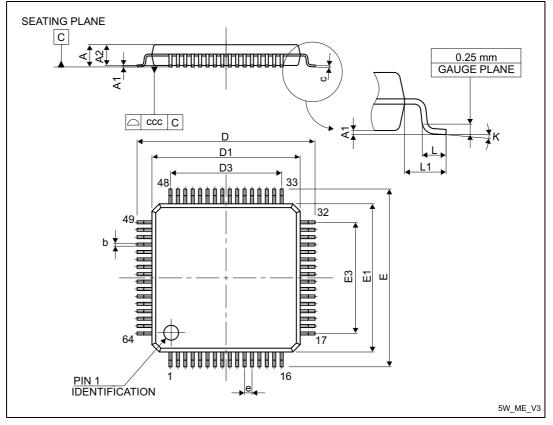

# 7.2 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 33. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 65. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical |

|------------------------------------------------------------------------------|

| data                                                                         |

|        |             |        | uata  |                       |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

| O      | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

| Symbol | Min         | Тур    | Мах   | Тур                   | Min    | Мах    |  |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |  |

| Е      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

#### **Package information**

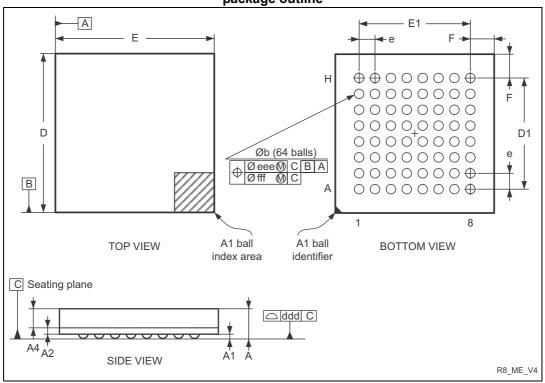

# 7.6 TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package information

Figure 45. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |

|---------------------------------------------------------------------------|

| package mechanical data                                                   |

| Quaracter at | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol       | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| А            | -           | -     | 1.200 | -                     | -      | 0.0472 |  |

| A1           | 0.150       | -     | -     | 0.0059                | -      | -      |  |

| A2           | -           | 0.200 | -     | -                     | 0.0079 | -      |  |

| A4           | -           | -     | 0.600 | -                     | -      | 0.0236 |  |

| b            | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |  |

| D            | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| D1           | -           | 3.500 | -     | -                     | 0.1378 | -      |  |

| E            | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |  |

| E1           | -           | 3.500 | -     | -                     | 0.1378 | -      |  |

| е            | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| F            | -           | 0.750 | -     | -                     | 0.0295 | -      |  |

## 8 Ordering information

| Table 73. Ordering info                                | ormation | scheme | ;  |     |   |         |

|--------------------------------------------------------|----------|--------|----|-----|---|---------|

| Example:                                               | STM32    | L 152  | RВ | T 6 | А | D TR    |

|                                                        |          |        |    |     |   |         |

| Device family                                          |          |        |    |     |   |         |

| STM32 = ARM-based 32-bit microcontroller               |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Product type                                           |          |        |    |     |   |         |

| L = Low-power                                          |          | -      |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Device subfamily                                       |          |        |    |     |   |         |

| 151: Devices without LCD                               |          |        |    |     |   |         |

| 152: Devices with LCD                                  |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Pin count                                              |          |        |    |     |   |         |

| C = 48 pins                                            |          |        | -  |     |   |         |

| R = 64 pins                                            |          |        |    |     |   |         |

| V = 100 pins                                           |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Flash memory size                                      |          |        |    |     |   |         |

| 6 = 32 Kbytes of Flash memory                          |          |        |    |     |   |         |

| 8 = 64 Kbytes of Flash memory                          |          |        |    |     |   |         |

| B = 128 Kbytes of Flash memory                         |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Package                                                |          |        |    |     |   |         |

| H = BGA                                                |          |        |    |     |   |         |

| T = LQFP                                               |          |        |    |     |   |         |

| U = UFQFPN                                             |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Temperature range                                      |          |        |    |     |   |         |

| 6 = Industrial temperature range, -40 to 85 °C         |          |        |    |     |   |         |

| 7 = Industrial temperature range, -40 to 105 °C        |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Options                                                |          |        |    |     |   |         |

| A = device generation A                                |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| No character = VDD range: 1.8 to 3.6 V and BOR enabled |          |        |    |     |   | <b></b> |

| D = VDD range: 1.65 to 3.6 V and BOR disabled          |          |        |    |     |   |         |

| ,                                                      |          |        |    |     |   |         |

| Packing                                                |          |        |    |     |   |         |

| TR = tape and reel                                     |          |        |    |     |   |         |

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.