# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, POR, PWM, WDT |

| Number of I/O              | 83                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 4K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l151vbt6a  |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 Introduction                                             | 9                             |  |  |  |  |  |  |

|------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| 2 Description                                              |                               |  |  |  |  |  |  |

| 2.1 Device overview                                        |                               |  |  |  |  |  |  |

| 2.2 Ultra-low-power device continuum                       |                               |  |  |  |  |  |  |

| 2.2.1 Performance                                          |                               |  |  |  |  |  |  |

| 2.2.2 Shared peripherals                                   |                               |  |  |  |  |  |  |

| 2.2.3 Common system strategy                               |                               |  |  |  |  |  |  |

| 2.2.4 Features                                             |                               |  |  |  |  |  |  |

| 3 Functional overview                                      | 13                            |  |  |  |  |  |  |

| 3.1 Low-power modes                                        |                               |  |  |  |  |  |  |

| 3.2 ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with MPU |                               |  |  |  |  |  |  |

| 3.3 Reset and supply management                            |                               |  |  |  |  |  |  |

| 3.3.1 Power supply schemes                                 |                               |  |  |  |  |  |  |

| 3.3.2 Power supply supervisor                              |                               |  |  |  |  |  |  |

| 3.3.3 Voltage regulator                                    |                               |  |  |  |  |  |  |

| 3.3.4 Boot modes                                           |                               |  |  |  |  |  |  |

| 3.4 Clock management                                       |                               |  |  |  |  |  |  |

| 3.5 Low-power real-time clock and backup registers         |                               |  |  |  |  |  |  |

| 3.6 GPIOs (general-purpose inputs/outputs)                 |                               |  |  |  |  |  |  |

| 3.7 Memories                                               | Memories                      |  |  |  |  |  |  |

| 3.8 DMA (direct memory access)                             | DMA (direct memory access) 24 |  |  |  |  |  |  |

| 3.9 LCD (liquid crystal display)                           | LCD (liquid crystal display)  |  |  |  |  |  |  |

| 3.10 ADC (analog-to-digital converter)                     |                               |  |  |  |  |  |  |

| 3.10.1 Temperature sensor                                  |                               |  |  |  |  |  |  |

| 3.10.2 Internal voltage reference (V <sub>REFINT</sub> )   |                               |  |  |  |  |  |  |

| 3.11 DAC (digital-to-analog converter)                     |                               |  |  |  |  |  |  |

| 3.12 Ultra-low-power comparators and reference voltage     |                               |  |  |  |  |  |  |

| 3.13 Routing interface                                     |                               |  |  |  |  |  |  |

| 3.14 Touch sensing                                         |                               |  |  |  |  |  |  |

| 3.15 Timers and watchdogs                                  |                               |  |  |  |  |  |  |

|                      |                     | Functionalities depending on the operating power supply range |                           |                                   |                      |  |  |

|----------------------|---------------------|---------------------------------------------------------------|---------------------------|-----------------------------------|----------------------|--|--|

| •                    | ng power<br>y range | DAC and ADC operation                                         | USB                       | Dynamic voltage<br>scaling range  | I/O operation        |  |  |

| V <sub>DD</sub> = 2. | .0 to 2.4 V         | Conversion time<br>up to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |

| V <sub>DD</sub> = 2. | .4 to 3.6 V         | Conversion time<br>up to 1 Msps                               | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.

2. Should be USB-compliant from I/O voltage standpoint, the minimum V<sub>DD</sub> is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                 | Dynamic voltage scaling range |

|-----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)    | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)      | Range 2                       |

| 2.1 MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

# 3.7 Memories

The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices have the following features:

- Up to 32 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32, 64 or 128 Kbyte of embedded Flash program memory

- 4 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect or read-out-protect the memory (with 4 KB granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature. The user area of the Flash memory can be protected against Dbus read access by the PCROP feature (see RM0038 for details).

# 3.8 DMA (direct memory access)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI,  $I^2C$ , USART, general-purpose timers and ADC.

## 3.10.1 Temperature sensor

The temperature sensor  $T_{\text{SENSE}}$  generates a voltage  $V_{\text{SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode, see *Table 59: Temperature sensor calibration values*.

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (when no external voltage, VREF+, is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode see *Table 17: Embedded internal reference voltage*.

# 3.11 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in non-inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channels' independent or simultaneous conversions

- DMA capability for each channel (including the underrun interrupt)

- external triggers for conversion

- input reference voltage V<sub>REF+</sub>

Eight DAC trigger inputs are used in the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 3.15.1 General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11)

There are six synchronizable general-purpose timers embedded in the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices (see *Table 7* for differences).

#### TIM2, TIM3, TIM4

These timers are based on a 16-bit auto-reload up/down-counter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or onepulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2, TIM3, TIM4 general-purpose timers can work together or with the TIM10, TIM11 and TIM9 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4 all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### TIM10, TIM11 and TIM9

TIM10 and TIM11 are based on a 16-bit auto-reload upcounter. TIM9 is based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4 full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

### 3.15.2 Basic timers (TIM6 and TIM7)

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

# 3.15.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit down-counter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches 0.

# 3.15.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit down-counter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

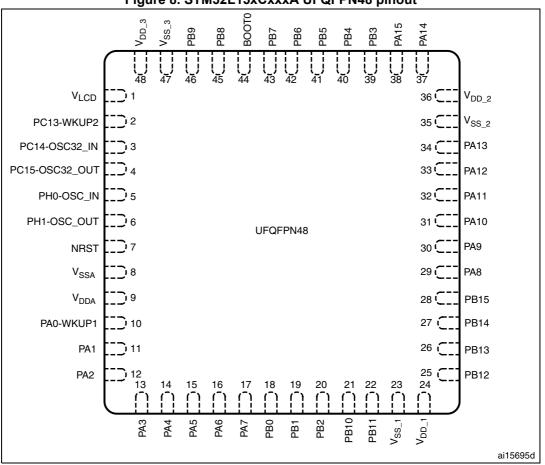

Figure 8. STM32L15xCxxxA UFQFPN48 pinout

1. This figure shows the package top view.

|         |        | Pins      | ;        |                    |                   |                         |               |                                                  | Pins functio                                     | ns                                            |

|---------|--------|-----------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|--------------------------------------------------|-----------------------------------------------|

| LQFP100 | LQFP64 | TFBGA64   | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                              | Additional<br>functions                       |

| 20      | -      | -         | K1       | -                  | V <sub>REF-</sub> | S                       | -             | V <sub>REF-</sub>                                | -                                                | -                                             |

| 21      | -      | G1<br>(6) | L1       | -                  | V <sub>REF+</sub> | S                       | -             | V <sub>REF+</sub>                                | -                                                | -                                             |

| 22      | 13     | H1        | M1       | 9                  | V <sub>DDA</sub>  | S                       | -             | V <sub>DDA</sub>                                 | -                                                | -                                             |

| 23      | 14     | G2        | L2       | 10                 | PA0-WKUP1         | I/O                     | FT            | PA0                                              | USART2_CTS/<br>TIM2_CH1_ETR                      | WKUP1/<br>ADC_IN0/<br>COMP1_INP<br>/RTC_TAMP2 |

| 24      | 15     | H2        | M2       | 11                 | PA1               | I/O                     | FT            | PA1                                              | USART2_RTS/<br>TIM2_CH2/LCD_SEG0                 | ADC_IN1/<br>COMP1_INP                         |

| 25      | 16     | F3        | КЗ       | 12                 | PA2               | I/O                     | FT            | PA2                                              | USART2_TX/<br>TIM2_CH3/<br>TIM9_CH1/<br>LCD_SEG1 | ADC_IN2/<br>COMP1_INP                         |

| 26      | 17     | G3        | L3       | 13                 | PA3               | I/O                     | тс            | PA3                                              | USART2_RX/<br>TIM2_CH4/<br>TIM9_CH2/<br>LCD_SEG2 | ADC_IN3/<br>COMP1_INP                         |

| 27      | 18     | C2        | E3       | -                  | V <sub>SS_4</sub> | S                       | -             | $V_{SS_4}$                                       | -                                                | -                                             |

| 28      | 19     | D2        | H3       | -                  | $V_{DD_4}$        | S                       | -             | $V_{DD_4}$                                       | -                                                | -                                             |

| 29      | 20     | H3        | М3       | 14                 | PA4               | I/O                     | тс            | PA4                                              | SPI1_NSS/<br>USART2_CK                           | ADC_IN4/<br>DAC_OUT1/<br>COMP1_INP            |

| 30      | 21     | F4        | K4       | 15                 | PA5               | I/O                     | тс            | PA5                                              | SPI1_SCK/<br>TIM2_CH1_ETR                        | ADC_IN5/<br>DAC_OUT2/<br>COMP1_INP            |

| 31      | 22     | G4        | L4       | 16                 | PA6               | I/O                     | FT            | PA6                                              | SPI1_MISO/TIM3_CH1/<br>LCD_SEG3/TIM10_CH1        | ADC_IN6/<br>COMP1_INP                         |

| 32      | 23     | H4        | M4       | 17                 | PA7               | I/O                     | FT            | PA7                                              | SPI1_MOSI/TIM3_CH2/<br>LCD_SEG4/TIM11_CH1        | ADC_IN7/<br>COMP1_INP                         |

| 33      | 24     | H5        | K5       | -                  | PC4               | I/O                     | FT            | PC4                                              | LCD_SEG22                                        | ADC_IN14/<br>COMP1_INP                        |

| 34      | 25     | H6        | L5       | -                  | PC5               | I/O                     | FT            | PC5                                              | LCD_SEG23                                        | ADC_IN15/<br>COMP1_INP                        |

# Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

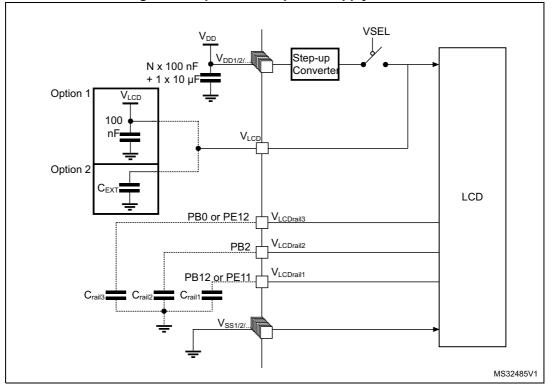

# 6.1.7 Optional LCD power supply scheme

Figure 13. Optional LCD power supply scheme

1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

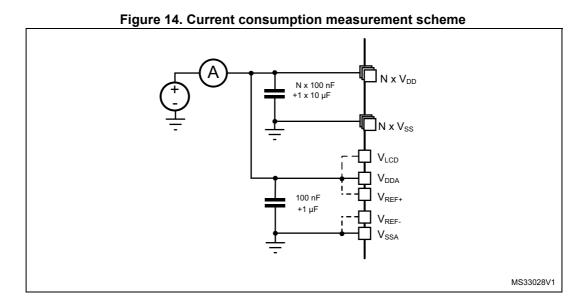

# 6.1.8 Current consumption measurement

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Мах  | Unit |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|

| V                 | Drown out react threshold 0   | Falling edge                              | 1.67 | 1.7  | 1.74 |      |

| V <sub>BOR0</sub> | Brown-out reset threshold 0   | Rising edge                               | 1.69 | 1.76 | 1.8  |      |

| M                 | Drown out react threshold 4   | Falling edge                              | 1.87 | 1.93 | 1.97 |      |

| V <sub>BOR1</sub> | Brown-out reset threshold 1   | Rising edge                               | 1.96 | 2.03 | 2.07 |      |

| V                 | Brown-out reset threshold 2   | Falling edge                              | 2.22 | 2.30 | 2.35 | v    |

| V <sub>BOR2</sub> | BIOWII-OULTESEL III ESHOIU Z  | Rising edge                               | 2.31 | 2.41 | 2.44 | v    |

| M                 | Drown out react threshold 2   | Falling edge                              | 2.45 | 2.55 | 2.60 |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 3   | Rising edge                               | 2.54 | 2.66 | 2.7  |      |

| M                 | Drown out react threshold 4   | Falling edge                              | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | Brown-out reset threshold 4   | Rising edge                               | 2.78 | 2.9  | 2.95 |      |

| M                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |

| V                 |                               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> | PVD threshold 1               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |

| M                 |                               | Falling edge                              | 2.20 | 2.24 | 2.28 |      |

| V <sub>PVD2</sub> | PVD threshold 2               | Rising edge                               | 2.28 | 2.34 | 2.38 |      |

|                   | DVD threads all a             | Falling edge                              | 2.39 | 2.44 | 2.48 |      |

| V <sub>PVD3</sub> | PVD threshold 3               | Rising edge                               | 2.47 | 2.54 | 2.58 | V    |

| M                 | DVD threehold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> | PVD threshold 4               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |

|                   | DVD threads ald 5             | Falling edge                              | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> | PVD threshold 5               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |

|                   | DVD threads all 0             | Falling edge                              | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> | PVD threshold 6               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

| Table 15. Embedded reset and | power control block characteristics (c | continued) |

|------------------------------|----------------------------------------|------------|

1. Guaranteed by characterization.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol                            | Parameter                                                  |                                            | Conditions                                                                   |                                         | Тур  | Max<br>(1) | Unit |

|-----------------------------------|------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|------|------------|------|

|                                   |                                                            |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz<br>Flash OFF                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 5.5  | -          |      |

|                                   |                                                            |                                            | MSI clock, 65 kHz                                                            | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 32 kHz                                                   | T <sub>A</sub> = 85 °C                  | 20   | 23         |      |

|                                   |                                                            | All                                        | Flash ON                                                                     | T <sub>A</sub> = 105 °C                 | 24   | 26         |      |

|                                   |                                                            | peripherals<br>OFF, V <sub>DD</sub>        | MSI clock, 65 kHz                                                            | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            | from 1.65 V<br>to 3.6 V                    | f <sub>HCLK</sub> = 65 kHz,                                                  | T <sub>A</sub> = 85 °C                  | 20.5 | 23         |      |

|                                   |                                                            | 10 3.0 V                                   | Flash ON                                                                     | T <sub>A</sub> = 105 °C                 | 25.4 | 27         |      |

|                                   |                                                            |                                            |                                                                              | $T_A$ = -40 °C to 25 °C                 | 18   | 20         |      |

|                                   | Supply<br>current in<br>Low-power<br>sleep                 |                                            | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz,<br>Flash ON               | T <sub>A</sub> = 55 °C                  | 21   | 22         | μΑ   |

| I <sub>DD</sub> (LP               |                                                            |                                            |                                                                              | T <sub>A</sub> = 85 °C                  | 23   | 27         |      |

| Sleep)                            |                                                            |                                            |                                                                              | T <sub>A</sub> = 105 °C                 | 28   | 31         |      |

|                                   | mode                                                       |                                            | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz                              | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            |                                            |                                                                              | T <sub>A</sub> = 85 °C                  | 20   | 22         |      |

|                                   |                                                            |                                            | HOLK OZ KIZ                                                                  | T <sub>A</sub> = 105 °C                 | 24   | 26         |      |

|                                   |                                                            | TIM9 and<br>USART1                         | USART1<br>enabled, MSI clock, 65 kHz<br>Flash ON, f <sub>HCLK</sub> = 65 kHz | $T_A$ = -40 °C to 25 °C                 | 15   | 16         |      |

|                                   |                                                            | enabled,                                   |                                                                              | T <sub>A</sub> = 85 °C                  | 20.5 | 23         |      |

|                                   |                                                            | V <sub>DD</sub> from                       |                                                                              | T <sub>A</sub> = 105 °C                 | 25.4 | 27         |      |

|                                   |                                                            | 1.65 V to<br>3.6 V                         |                                                                              | $T_A$ = -40 °C to 25 °C                 | 18   | 20         |      |

|                                   |                                                            | 5.0 V                                      | MSI clock, 131 kHz                                                           | T <sub>A</sub> = 55 °C                  | 21   | 22         |      |

|                                   |                                                            |                                            | f <sub>HCLK</sub> = 131 kHz                                                  | T <sub>A</sub> = 85 °C                  | 23   | 27         | 1    |

|                                   |                                                            |                                            |                                                                              | T <sub>A</sub> = 105 °C                 | 28   | 30         |      |

| I <sub>DD</sub> Max<br>(LP Sleep) | Max<br>allowed<br>current in<br>Low-power<br>Sleep<br>mode | V <sub>DD</sub> from<br>1.65 V to<br>3.6 V | -                                                                            | -                                       | -    | 200        |      |

Table 22. Current consumption in Low-power sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

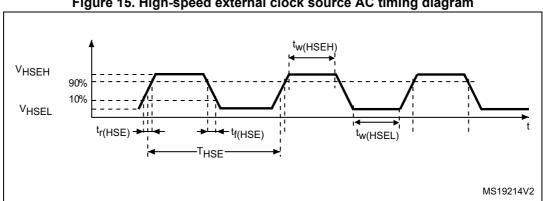

#### 6.3.6 **External clock source characteristics**

## High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in Section 6.3.13. However, the recommended clock input waveform is shown in Figure 15.

| Symbol                                       | Parameter                           | Conditions                  | Min             | Тур | Max             | Unit |

|----------------------------------------------|-------------------------------------|-----------------------------|-----------------|-----|-----------------|------|

| fure                                         | User external clock source          | CSS is on or<br>PLL is used | 1               | 8   | 32              | MHz  |

| f <sub>HSE_ext</sub>                         | frequency                           | CSS is off, PLL<br>not used | 0               | 0   | 52              |      |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |                             | $0.7V_{DD}$     | -   | V <sub>DD</sub> |      |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |                             | V <sub>SS</sub> |     | $0.3V_{DD}$     |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             | -                           | 12              | -   | -               | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |                             | -               | -   | 20              | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            | -                           | -               | 2.6 | -               | pF   |

1. Guaranteed by design.

Figure 15. High-speed external clock source AC timing diagram

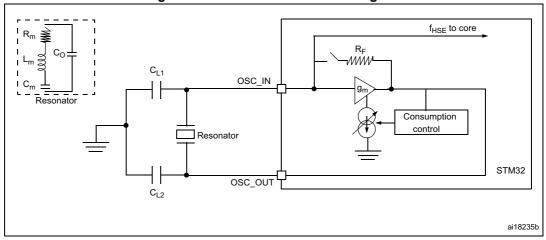

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 14*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                                     |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>               | LSE oscillator current consumption                                                            | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | $V_{DD}$ is stabilized                | -   | 1      | -   | S    |

| Table 30. LSE oscillator characteristics | ; (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small  $R_S$  value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 19* and *Table 45*, respectively.

Unless otherwise specified, the parameters given in *Table 45* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRx<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                         | Parameter                                                                                                                                                                | Conditions                                               | Min  | Max <sup>(2)</sup> | Unit |

|-----------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|--------------------|------|

|                                               | f                                              | Maximum frequency <sup>(3)</sup>                                                                                                                                         | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 400                | kHz  |

| 00                                            | f <sub>max(IO)out</sub>                        |                                                                                                                                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -    | 400                | KIIZ |

| 00                                            | t <sub>f(IO)out</sub>                          | Output rise and fall time                                                                                                                                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 625                | ne   |

|                                               | t <sub>r(IO)out</sub>                          |                                                                                                                                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -    | 625                | ns   |

|                                               | f                                              | Maximum fraguanov <sup>(3)</sup>                                                                                                                                         | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 2                  | MHz  |

| 01                                            | f <sub>max(IO)out</sub>                        | $\begin{array}{c} \text{Maximum frequency}^{(3)} \\ \hline C_{\text{L}} = 50 \text{ pF}, \text{ V}_{\text{DD}} = 1.65 \text{ V to } 2.7 \text{ V} \\ \hline \end{array}$ |                                                          | -    | 1                  |      |

| 01                                            | t <sub>f(IO)out</sub><br>t <sub>r(IO)out</sub> | Output rise and fall time                                                                                                                                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 125                | ns   |

|                                               |                                                |                                                                                                                                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -    | 250                | 115  |

|                                               | -                                              | Maximum fraguanau <sup>(3)</sup>                                                                                                                                         | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 10                 | MHz  |

| 10                                            | F <sub>max(IO)out</sub>                        | Maximum frequency <sup>(3)</sup>                                                                                                                                         | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -    | 2                  | WIL  |

| 10                                            | t <sub>f(IO)out</sub>                          | Output rise and fall time                                                                                                                                                | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 25                 |      |

|                                               | t <sub>r(IO)out</sub>                          | Output rise and fall time $C_L = 50 \text{ pF}, V_{DD} = 1.65 \text{ V to } 2.7 \text{ V}$                                                                               |                                                          | -    | 125                | ns   |

|                                               | F                                              | Maximum frequency <sup>(3)</sup>                                                                                                                                         | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 2.7 V to 3.6 V | -    | 50                 | MHz  |

| 11                                            | F <sub>max(IO)out</sub>                        |                                                                                                                                                                          | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | -    | 8                  |      |

|                                               | t <sub>f(IO)out</sub>                          | Output rise and fall time                                                                                                                                                | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V               | -    | 5                  |      |

|                                               | t <sub>r(IO)out</sub>                          | Output rise and fall time                                                                                                                                                | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V              | - 30 |                    |      |

| -                                             | t <sub>EXTIpw</sub>                            | Pulse width of external signals detected by the EXTI controller                                                                                                          | -                                                        | 8    | -                  | ns   |

| Table 45. I/O AC characteristics <sup>(1)</sup> | Table | 45. I/O | AC | characteristics <sup>(1)</sup> |  |

|-------------------------------------------------|-------|---------|----|--------------------------------|--|

|-------------------------------------------------|-------|---------|----|--------------------------------|--|

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure 19*.

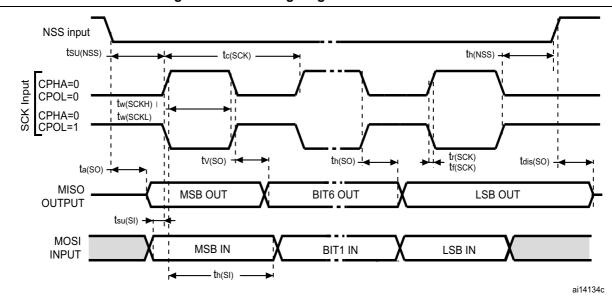

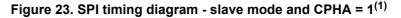

Figure 22. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | Conditions                                                                 |                                                                          | Min                 | Тур       | Max                       | Unit                      |    |

|---------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------|-----------|---------------------------|---------------------------|----|

| V <sub>DDA</sub>                | Analog supply voltage                                 | -                                                                          |                                                                          | 1.8                 | -         | 3.6                       | V                         |    |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must always be below<br>V <sub>DDA</sub>                 |                                                                          | 1.8                 | -         | 3.6                       | V                         |    |

| V <sub>REF-</sub>               | Lower reference voltage                               | -                                                                          |                                                                          |                     | $V_{SSA}$ |                           | V                         |    |

| (4)                             | Current consumption on                                | No load, mid                                                               | dle code (0x800)                                                         | -                   | 130       | 220                       | μA                        |    |

| I <sub>DDVREF+</sub> (1)        | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                                                               | st code (0x000)                                                          | -                   | 220       | 350                       | μA                        |    |

| (1)                             | Current consumption on                                | No load, mid                                                               | ldle code (0x800)                                                        | -                   | 210       | 320                       | μA                        |    |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wor                                                               | st code (0xF1C)                                                          | -                   | 320       | 520                       | μA                        |    |

| D                               | Resistive load                                        | DAC output                                                                 | Connected to $V_{SSA}$                                                   | 5                   | -         | -                         | kΩ                        |    |

| R <sub>L</sub>                  | Resistive load                                        | buffer ON                                                                  | Connected to V <sub>DDA</sub>                                            | 25                  | -         | -                         | K52                       |    |

| CL                              | Capacitive load                                       | DAC output                                                                 | buffer ON                                                                | -                   | -         | 50                        | pF                        |    |

| R <sub>O</sub>                  | Output impedance                                      | DAC output                                                                 | buffer OFF                                                               | 12                  | 16        | 20                        | kΩ                        |    |

| Voltage on DAC_OUT              |                                                       | DAC output buffer ON                                                       |                                                                          | 0.2                 | -         | V <sub>DDA</sub> –<br>0.2 | V                         |    |

| V <sub>DAC_OUT</sub>            | output                                                | DAC output buffer OFF                                                      |                                                                          | DAC output buffer O | 0.5       | -                         | V <sub>REF+</sub><br>1LSB | mV |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                          | -                   | 1.5       | 3                         |                           |    |

| Ditt                            |                                                       | No $R_L$ , $C_L \le DAC$ output                                            |                                                                          | -                   | 1.5       | 3                         |                           |    |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF, F}$<br>DAC output                                   | -                                                                        | -                   | 2         | 4                         |                           |    |

|                                 | No R <sub>L</sub> ,                                   |                                                                            | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF              |                     | 2         | 4                         | LSB                       |    |

| Offset <sup>(1)</sup>           | Offset error at code 0x800 <sup>(4)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                          | -                   | ±10       | ±25                       |                           |    |

| UIISEL' '                       | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF             |                                                                            | No R <sub>L</sub> , C <sub>L</sub> $\leq$ 50 pF<br>DAC output buffer OFF |                     | ±5        | ±8                        |                           |    |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>             | No R <sub>L</sub> , C <sub>L</sub> $\leq$ DAC output                       |                                                                          | -                   | ±1.5      | ±5                        |                           |    |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

# 6.3.20 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| $V_{DDA}$                | Analog supply voltage                                                | -                                                                         | 1.65               |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | K52       |

| V <sub>IN</sub>          | Comparator 1 input voltage range                                     | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 |           |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |

Table 61. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

# 6.3.21 LCD controller (STM32L152x6/8/B-A devices only)

The STM32L152xx-A devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the V<sub>DD</sub> voltage. An external capacitor C<sub>ext</sub> must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol                           | Parameter                                                 | Min  | Тур                  | Max       | Unit |

|----------------------------------|-----------------------------------------------------------|------|----------------------|-----------|------|

| $V_{LCD}$                        | LCD external voltage                                      | -    | -                    | 3.6       |      |

| V <sub>LCD0</sub>                | LCD internal reference voltage 0                          | -    | 2.6                  | -         |      |

| V <sub>LCD1</sub>                | LCD internal reference voltage 1                          | -    | 2.73                 | -         |      |

| V <sub>LCD2</sub>                | LCD internal reference voltage 2                          | -    | 2.86                 | -         |      |

| V <sub>LCD3</sub>                | LCD internal reference voltage 3                          | -    | 2.98                 | -         | V    |

| $V_{LCD4}$                       | LCD internal reference voltage 4                          | -    | 3.12                 | -         | 1    |

| $V_{LCD5}$                       | LCD internal reference voltage 5                          | -    | 3.26                 | -         | 1    |

| V <sub>LCD6</sub>                | LCD internal reference voltage 6                          | -    | 3.4                  | -         |      |

| V <sub>LCD7</sub>                | LCD internal reference voltage 7                          | -    | 3.55                 | -         | 1    |

| C <sub>ext</sub>                 | V <sub>LCD</sub> external capacitance                     | 0.1  | -                    | 2         | μF   |

| I <sub>LCD</sub> <sup>(1)</sup>  | (1) Supply current at V <sub>DD</sub> = 2.2 V             |      | 3.3                  | -         |      |

| LCD,                             | Supply current at V <sub>DD</sub> = 3.0 V                 |      | 3.1                  | -         | μA   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                 | 5.28 | 6.6                  | 7.92      | MΩ   |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                  | 192  | 240                  | 288       | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                      | -    | -                    | $V_{LCD}$ | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                          | -    | 3/4 V <sub>LCD</sub> | -         |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                          | -    | 2/3 V <sub>LCD</sub> | -         |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                          | -    | 1/2 V <sub>LCD</sub> | -         | V    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                          |      | 1/3 V <sub>LCD</sub> | -         | Ň    |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                          | -    | 1/4 V <sub>LCD</sub> | -         |      |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                       | 0    | -                    | -         |      |

| $\Delta Vxx^{(2)}$               | Segment/Common level voltage error $T_A = -40$ to 105 ° C | -    | -                    | ±50       | mV   |

#### Table 63. LCD controller characteristics

1. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected

2. Guaranteed by characterization results.

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |  |  |  |

|----------------------------------------------------------------------------------|--|--|--|

| package mechanical data (continued)                                              |  |  |  |

| Symbol | millimeters |      |      |        |        |        |

|--------|-------------|------|------|--------|--------|--------|

| Symbol | Min         | Тур  | Max  | Min    | Тур    | Max    |

| F      | 0.7         | 0.75 | 0.8  | 0.0276 | 0.0295 | 0.0315 |

| ddd    | -           | -    | 0.1  | -      | -      | 0.0039 |

| eee    | -           | -    | 0.15 | -      | -      | 0.0059 |

| fff    | -           | -    | 0.05 | -      | -      | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

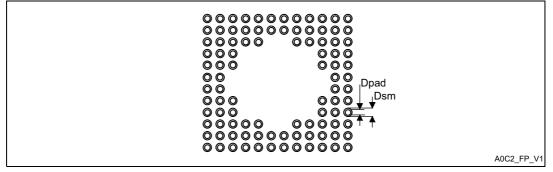

# Figure 43. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package recommended footprint

#### Table 69. UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Table 70. TFBGA64 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array |  |

|---------------------------------------------------------------------------|--|

| package mechanical data (continued)                                       |  |

| Symbol | millimeters |     |       |     | inches <sup>(1)</sup> |        |

|--------|-------------|-----|-------|-----|-----------------------|--------|

| Symbol | Min         | Тур | Мах   | Min | Тур                   | Мах    |

| ddd    | -           | -   | 0.080 | -   | -                     | 0.0031 |

| eee    | -           | -   | 0.15  | -   | -                     | 0.0059 |

| fff    | -           | -   | 0.05  | -   | -                     | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

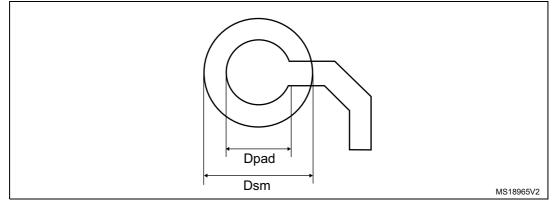

# Figure 46. TFBGA64, 5 x 5 mm, 0.5 mm pitch, thin fine-pitch ball grid array package recommended footprint

### Table 71. TFBGA64 5 x 5 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

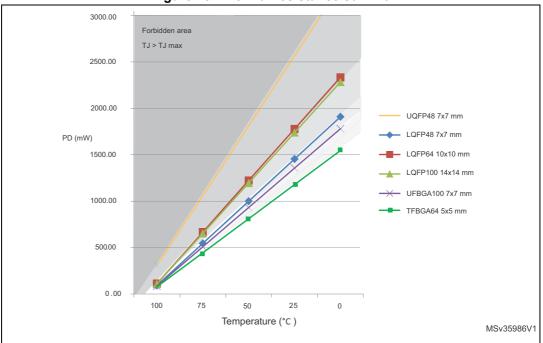

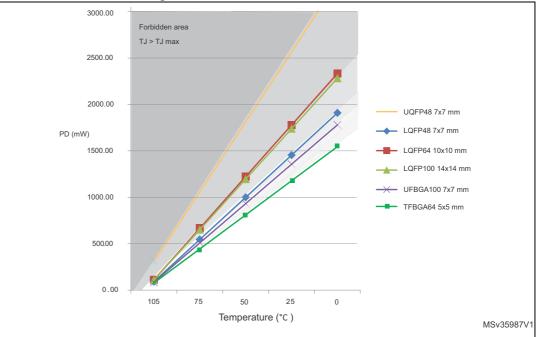

Figure 48. Thermal resistance suffix 6

# 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

DocID024330 Rev 4