# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 37                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152c8u6a       |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From a proprietary 8bit core up to the Cortex-M3, including the Cortex-M0+, the STM8Lx and STM32Lx series offer the best range of choices to meet your requirements in terms of ultra-low-power features. The STM32 Ultra-low-power series is an ideal fit for applications like gas/water meters, keyboard/mouse, or wearable devices for fitness and healthcare. Numerous built-in features like LCD drivers, dual-bank memory, low-power Run mode, op-amp, AES-128bit, DAC, crystal-less USB and many others, allow to build highly cost-optimized applications by reducing the BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lx and STM32Lx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, your existing applications can be upgraded to respond to the latest market features and efficiency demand.

# 2.2.1 Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-Low-power performance to range from 5 up to 33.3 DMIPs.

# 2.2.2 Shared peripherals

STM8L15xxx and STM32L1xxxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

# 2.2.3 Common system strategy

To offer flexibility and optimize performance, the STM8L15xxx and STM32L1xxxx families use a common architecture:

- Common power supply range from 1.65 V to 3.6 V, (1.65 V at power down only for STM8L15xxx devices)

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultra-safe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector.

# 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 512 Kbytes

|                                 |             | Functionalities depending on the operating power supply range |                           |                                   |                      |  |  |  |  |

|---------------------------------|-------------|---------------------------------------------------------------|---------------------------|-----------------------------------|----------------------|--|--|--|--|

| Operating power<br>supply range |             | DAC and ADC<br>operation USB                                  |                           | Dynamic voltage<br>scaling range  | I/O operation        |  |  |  |  |

| V <sub>DD</sub> = 2.            | .0 to 2.4 V | Conversion time<br>up to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

| V <sub>DD</sub> = 2.            | .4 to 3.6 V | Conversion time<br>up to 1 Msps                               | Functional <sup>(2)</sup> | Range 1,<br>Range 2 or<br>Range 3 | Full speed operation |  |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.

2. Should be USB-compliant from I/O voltage standpoint, the minimum V<sub>DD</sub> is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                 | Dynamic voltage scaling range |

|-----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)    | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)      | Range 2                       |

| 2.1 MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

|                                           |            |       | Low-         | Low-           |   | Stop                 |   | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|---|----------------------|---|----------------------|

| lps                                       | Run/Active | Sleep | power<br>Run | power<br>Sleep |   | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          | -     | Y            | -              | - | -                    | - | -                    |

| Flash                                     | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| RAM                                       | Y          | Y     | Y            | Y              | Y | -                    | - | -                    |

| Backup Registers                          | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| EEPROM                                    | Y          | Y     | Y            | Y              | Y | -                    | - | -                    |

| Brown-out reset<br>(BOR)                  | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| DMA                                       | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| Programmable<br>Voltage Detector<br>(PVD) | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| Power On Reset<br>(POR)                   | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| Power Down Rest<br>(PDR)                  | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| High Speed<br>Internal (HSI)              | Y          | Y     | -            | -              | - | -                    | - | -                    |

| High Speed<br>External (HSE)              | Y          | Y     | -            | -              | - | -                    | - | -                    |

| Low Speed Internal<br>(LSI)               | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| Low Speed<br>External (LSE)               | Y          | Y     | Y            | Y              | Y | -                    | Y | -                    |

| Multi-Speed<br>Internal (MSI)             | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| RTC                                       | Y          | Y     | Y            | Y              | Y | Y                    | Y | -                    |

| RTC Tamper                                | Y          | Y     | Y            | Y              | Y | Y                    | Y | Y                    |

| Auto Wakeup<br>(AWU)                      | Y          | Y     | Y            | Y              | Y | Y                    | Y | Y                    |

| LCD                                       | Y          | Y     | Y            | Y              | Y | -                    | - | -                    |

| USB                                       | Y          | Y     | -            | -              | - | Y                    | - | -                    |

| USART                                     | Y          | Y     | Y            | Y              | Y | (1)                  | - | -                    |

| SPI                                       | Y          | Y     | Y            | Y              | - | -                    | - | -                    |

| I2C                                       | Y          | Y     | Y            | Y              | - | (1)                  | - | -                    |

| ADC                                       | Y          | Y     | -            | -              | - | -                    | - | -                    |

# 3.4 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching**: clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management**: to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **Master clock source**: three different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz) with a consumption proportional to speed, down to 750 nA typical. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

- **Auxiliary clock source**: two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

- **RTC and LCD clock sources:** the LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **USB clock source:** the embedded PLL has a dedicated 48 MHz clock output to supply the USB interface.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

- Clock-out capability (MCO: microcontroller clock output): it outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

# 4 Pin descriptions

|   | 1                  | 2              | 3     | 4      | 5     | 6     | 7        | 8      | 9             | 10            | 11     | 12           |          |

|---|--------------------|----------------|-------|--------|-------|-------|----------|--------|---------------|---------------|--------|--------------|----------|

|   |                    |                |       |        |       |       |          |        |               |               |        |              |          |

| A | (PE3)              | (PE1)          | (PB8) | iBOOTO | (PD7) | (PD5) | (PB4)    | (PB3)  | (PA15)        | (PA14)        | (PA13) | (PA12)       |          |

| в | (PE4)              | (PE2)          | (PB9) | (PB7)  | (PB6) | (PD6) | (PD4)    | (PD3)  | /-\<br>(PD1)  | PC12)         | (PC10) | (PA11)       |          |

| С | PC13<br>WKUP2      | (PE5)          | (PEO) | VDD_B  | (PB5) |       | '<br>    | (PD2)  | (PD0)         | PC11)         | (PH2)  | (PA10)       |          |

| D | PC14)<br>0\$C32_IN | PE6)<br>WUKP3  | ŃSS_B |        |       |       |          |        |               | (PA9)         | (PA8)  | (PC9)        |          |

| E | PC15)<br>OSC32_C   | VLCD           | NSS_H |        |       |       |          |        |               | (PC8)         | (PC7)  | (PC6)        |          |

| F | PHO<br>QSCZIN      | a zzvi         |       |        |       |       | 1        |        |               |               | NSS_P  | vss_1        |          |

| G | PH1)               |                |       |        |       |       | ⊢ −<br>' |        |               |               |        | אַרַם אַ     |          |

| н | (PC0)              | INRST          |       |        |       |       |          |        |               | PD15)         | PD14)  | (PD13)       |          |

| J | VSSA)              | (PC1)          | (PC2) |        |       |       |          |        |               | PD12)         | (PD11) | (PD10)       |          |

| к | VREF               | (PC3)          | (PA2) | (PA5)  | (PC4) |       |          | (PD9)  | (PD8)         | (PB15)        | (PB14) | (PB13)       |          |

| L | (VRE俳+             | (PA0)<br>WKUP1 | (PA3) | (PA6)  | (PC5) | (PB2) | (PE8)    | (PE10) | /=\<br>IPE12  | (PB10)        | (PB11) | (PB12)       |          |

| М | NDDA               | (PA1)          | (PA4) | (PA7)  | (PB0) | (PB1) | (PE7)    | (PE9)  | /-\<br>(PE11) | /-\<br>(PE13) | PE14   | /~\<br>(PE19 |          |

|   |                    |                |       |        |       |       |          |        |               |               |        |              |          |

|   |                    |                |       |        |       |       |          |        |               |               |        |              | ai17096f |

### Figure 3. STM32L15xVxxxA UFBGA100 ballout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |                                  |                         |               |                                                  | Pins functions                  |                                            |  |

|---------|--------|---------|----------|--------------------|----------------------------------|-------------------------|---------------|--------------------------------------------------|---------------------------------|--------------------------------------------|--|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name                         | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions                    |  |

| 1       | -      | -       | B2       | -                  | PE2                              | I/O                     | FT            | PE2                                              | TRACECLK/<br>LCD_SEG38/TIM3_ETR | -                                          |  |

| 2       | -      | -       | A1       | -                  | PE3                              | I/O                     | FT            | PE3                                              | TRACED0/<br>LCD_SEG39/TIM3_CH1  | -                                          |  |

| 3       | -      | -       | B1       | -                  | PE4                              | I/O                     | FT            | PE4                                              | TRACED1/TIM3_CH2                | -                                          |  |

| 4       | -      | -       | C2       | -                  | PE5                              | I/O                     | FT            | PE5                                              | TRACED2/TIM9_CH1                | -                                          |  |

| 5       | -      | -       | D2       | -                  | PE6-WKUP3                        | I/O                     | FT            | PE6                                              | TRACED3/TIM9_CH2                | WKUP3<br>/RTC_TAMP3                        |  |

| 6       | 1      | B2      | E2       | 1                  | V <sub>LCD</sub> <sup>(3)</sup>  | S                       |               | V <sub>LCD</sub>                                 | -                               | -                                          |  |

| 7       | 2      | A2      | C1       | 2                  | PC13-WKUP2                       | I/O                     | FT            | PC13                                             | -                               | RTC_TAMP1/<br>RTC_TS/<br>RTC_OUT/<br>WKUP2 |  |

| 8       | 3      | A1      | D1       | 3                  | PC14-<br>OSC32_IN <sup>(4)</sup> | I/O                     | тс            | PC14                                             | -                               | OSC32_IN                                   |  |

| 9       | 4      | B1      | E1       | 4                  | PC15-<br>OSC32_OUT<br>(4)        | I/O                     | тс            | PC15                                             | -                               | OSC32_OUT                                  |  |

| 10      | -      | -       | F2       | -                  | V <sub>SS_5</sub>                | S                       | -             | V <sub>SS_5</sub>                                | -                               | -                                          |  |

| 11      | -      | -       | G2       | -                  | V <sub>DD_5</sub>                | S                       | -             | $V_{DD_5}$                                       | -                               | -                                          |  |

| 12      | 5      | C1      | F1       | 5                  | PH0-OSC_IN <sup>(5)</sup>        | I/O                     | TC            | PH0                                              | -                               | OSC_IN                                     |  |

| 13      | 6      | D1      | G1       | 6                  | PH1-OSC_OUT                      | I/O                     | тс            | PH1                                              | -                               | OSC_OUT                                    |  |

| 14      | 7      | E1      | H2       | 7                  | NRST                             | I/O                     | RST           | NRST                                             | -                               | -                                          |  |

| 15      | 8      | E3      | H1       | -                  | PC0                              | I/O                     | FT            | PC0                                              | LCD_SEG18                       | ADC_IN10/<br>COMP1_INP                     |  |

| 16      | 9      | E2      | J2       | -                  | PC1                              | I/O                     | FT            | PC1                                              | LCD_SEG19                       | ADC_IN11/<br>COMP1_INP                     |  |

| 17      | 10     | F2      | J3       | -                  | PC2                              | I/O                     | FT            | PC2                                              | LCD_SEG20                       | ADC_IN12/<br>COMP1_INP                     |  |

| 18      | 11     | _(6)    | K2       | -                  | PC3                              | I/O                     | тс            | PC3                                              | LCD_SEG21                       | ADC_IN13/<br>COMP1_INP                     |  |

| 19      | 12     | F1      | J1       | 8                  | V <sub>SSA</sub>                 | S                       | -             | V <sub>SSA</sub>                                 | -                               | -                                          |  |

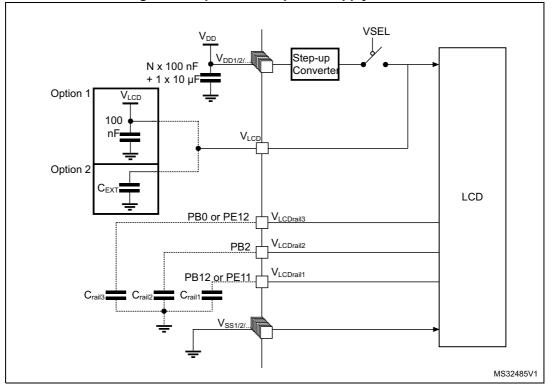

# 6.1.7 Optional LCD power supply scheme

Figure 13. Optional LCD power supply scheme

1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

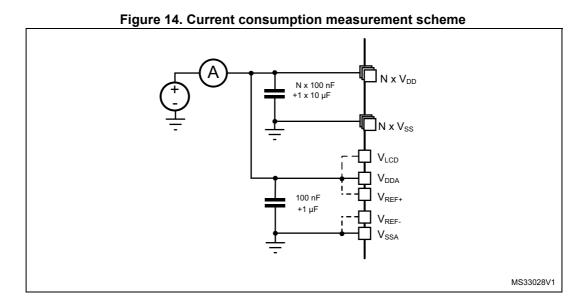

# 6.1.8 Current consumption measurement

| Symbol               | Parameter         | Cond                                               | litions                                            | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|----------------------|-------------------|----------------------------------------------------|----------------------------------------------------|-------------------|-------|--------------------|------|

|                      |                   |                                                    |                                                    | 1 MHz             | 215   | 285                |      |

|                      |                   |                                                    | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 2 MHz             | 400   | 490                | μA   |

|                      |                   |                                                    |                                                    | 4 MHz             | 725   | 1000               |      |

|                      |                   | $f_{HSE} = f_{HCLK}$<br>up to 16 MHz, included     |                                                    | 4 MHz             | 0.915 | 1.3                |      |

|                      |                   | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above      | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 8 MHz             | 1.75  | 2.15               |      |

|                      |                   | 16 MHz<br>(PLL ON) <sup>(2)</sup>                  |                                                    | 16 MHz            | 3.4   | 4                  | -    |

|                      |                   |                                                    | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz             | 2.1   | 2.9                |      |

| I <sub>DD (Run</sub> | Run mode,<br>code |                                                    |                                                    | 16 MHz            | 4.2   | 5.2                |      |

| from Flash)          | executed          |                                                    |                                                    | 32 MHz            | 8.25  | 9.6                |      |

|                      | from Flash        | HSI clock source (16                               | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 3.5   | 4.4                | mA   |

|                      | MHz)              | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz                                             | 8.2               | 10.2  |                    |      |

|                      | MSI clock, 65 kHz |                                                    | 65 kHz                                             | 0.041             | 0.085 |                    |      |

|                      |                   | MSI clock, 524 kHz                                 | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 524 kHz           | 0.125 | 0.180              |      |

|                      |                   | MSI clock, 4.2 MHz                                 | voo[1.0] – 11                                      | 4.2 MHz           | 0.775 | 0.935              |      |

#### Table 18. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                                         | Parameter                                          |                                         | Conditions                                      |                                         | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------------------------------|----------------------------------------------------|-----------------------------------------|-------------------------------------------------|-----------------------------------------|------|--------------------|------|

|                                                |                                                    |                                         |                                                 | $T_A$ = -40 °C to 25 °C                 | 10.9 | 12                 |      |

|                                                |                                                    |                                         | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                  | 16.5 | 23                 |      |

|                                                |                                                    |                                         | HOLK V- WH                                      | T <sub>A</sub> = 105 °C                 | 26   | 47                 |      |

|                                                |                                                    | All peripherals<br>OFF, code            |                                                 | $T_A$ = -40 °C to 25 °C                 | 15   | 16                 |      |

|                                                |                                                    | executed from<br>RAM, Flash             | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                  | 22   | 29                 |      |

|                                                |                                                    | switched OFF,                           | HOLK COMME                                      | T <sub>A</sub> = 105 °C                 | 32   | 51                 |      |

|                                                |                                                    | V <sub>DD</sub> from<br>1.65 V to 3.6 V |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 29   | 37                 |      |

|                                                |                                                    | 1.00 V 10 0.0 V                         | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 32.5 | 40                 |      |

|                                                | Supply                                             |                                         | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 35.5 | 54                 |      |

| I <sub>DD</sub>                                | Supply<br>current in<br>Low-power<br>run mode      |                                         |                                                 | T <sub>A</sub> = 105 °C                 | 45   | 65                 |      |

| (LP Run)                                       |                                                    | All peripherals                         | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A$ = -40 °C to 25 °C                 | 23   | 24                 |      |

|                                                |                                                    |                                         |                                                 | T <sub>A</sub> = 85 °C                  | 31   | 34                 | μA   |

|                                                |                                                    |                                         |                                                 | T <sub>A</sub> = 105 °C                 | 42.5 | 56                 |      |

|                                                |                                                    |                                         | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A$ = -40 °C to 25 °C                 | 29   | 31                 |      |

|                                                |                                                    | OFF, code<br>executed from              |                                                 | T <sub>A</sub> = 85 °C                  | 38   | 41                 |      |

|                                                |                                                    | Flash, V <sub>DD</sub> from             | HOLK OUT IN L                                   | T <sub>A</sub> = 105 °C                 | 49   | 63                 |      |

|                                                |                                                    | 1.65 V to 3.6 V                         |                                                 | $T_A$ = -40 °C to 25 °C                 | 46   | 55                 |      |

|                                                |                                                    |                                         | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 48   | 59                 |      |

|                                                |                                                    |                                         | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 53.5 | 72                 |      |

|                                                |                                                    |                                         | T <sub>A</sub> = 105 °C                         | 64.8                                    | 84   |                    |      |

| I <sub>DD</sub> Max<br>(LP Run) <sup>(2)</sup> | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to 3.6 V | -                                               | -                                       | -    | 200                |      |

Table 21. Current consumption in Low-power run mode

1. Guaranteed by characterization results, unless otherwise specified.

2. This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

| Symbol                  | Parameter                                    | Conditions                                                              | Тур     | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------------------------|-------------------------------------------------------------------------|---------|--------------------|------|

| twusleep                | Wakeup from Sleep mode                       | f <sub>HCLK</sub> = 32 MHz                                              | 0.4     | -                  |      |

| +                       | Wakeup from Low-power sleep mode             | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 46      | -                  |      |

| <sup>t</sup> wusleep_lp | f <sub>HCLK</sub> = 262 kHz                  | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 46      | -                  |      |

|                         | Wakeup from Stop mode, regulator in Run mode | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2     | -                  |      |

|                         |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 1 and 2 | 7.7     | 8.9                |      |

|                         | Wakeup from Stop mode,                       | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage Range 3       | 8.2     | 13.1               | μs   |

| t <sub>WUSTOP</sub>     |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                          | 10.2    | 13.4               |      |

|                         | regulator in low-power mode                  | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 16      | 20                 |      |

|                         |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 31      | 37                 |      |

|                         |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 57      | 66                 |      |

|                         |                                              | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 112 123 |                    |      |

|                         |                                              | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 221     | 236                |      |

|                         | Wakeup from Standby<br>mode<br>FWU bit = 1   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 58      | 104                |      |

| <sup>t</sup> wustdby    | Wakeup from Standby<br>mode<br>FWU bit = 0   | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.6     | 3.25               | ms   |

Table 26. Low-power mode wakeup timings

1. Guaranteed by characterization results, unless otherwise specified

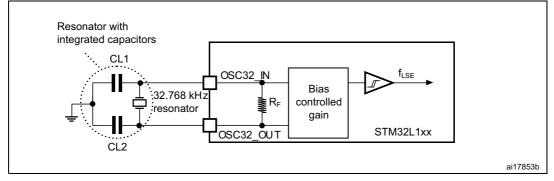

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- Caution: To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL ≤ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

| Symbol                                | Parameter                          | Condition                                | Тур | Max | Unit    |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|---------|

|                                       |                                    | MSI range 0                              | -   | 40  |         |

|                                       |                                    | MSI range 1                              | -   | 20  |         |

|                                       |                                    | MSI range 2                              | -   | 10  |         |

|                                       |                                    | MSI range 3                              | -   | 4   |         |

| + (2)                                 | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 |         |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 5                              | -   | 2   | μs      |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |         |

|                                       |                                    | MSI range 3,<br>Voltage Range 3          | -   | 3   |         |

| fourment                              | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz     |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                     | -   | 6   | 1011 12 |

Table 33. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Table 34. | PLL | chara | cteristics |

|-----------|-----|-------|------------|

|-----------|-----|-------|------------|

| Symbol                 | Parameter                                               |         | Unit |                    |      |

|------------------------|---------------------------------------------------------|---------|------|--------------------|------|

| Symbol                 | Parameter                                               | Min Typ |      | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(2)</sup>                          | 2       | -    | 24                 | MHz  |

|                        | PLL input clock duty cycle                              | 45      | -    | 55                 | %    |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2       | -    | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -       | 115  | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                                   | -       | -    | ± 600              | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -       | 220  | 450                |      |

| I <sub>DD</sub> (PLL)  | Current consumption on $V_{DD}$                         | -       | 120  | 150                | μA   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL\_OUT}}$ .

# 6.3.9 Memory characteristics

The characteristics are given at  $T_{\text{A}}$  = -40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

#### **RAM** memory

| Table | 35. | RAM | and | hardware | reaisters |

|-------|-----|-----|-----|----------|-----------|

| 10010 | ••• |     | ana | naranaro | regiotore |

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

#### Flash memory and data EEPROM

| Symbol          | Parameter                                             | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|-------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub> | Operating voltage<br>Read / Write / Erase             | -                                               | 1.65 | -    | 3.6                | V    |

| -               | Programming / erasing time for                        | Erasing                                         | -    | 3.28 | 3.94               |      |

|                 | byte / word / double word / half-<br>page             | Programming                                     | -    | 3.28 | 3.94               | ms   |

|                 | Average current during whole program/erase operation  | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 300  | -                  | μA   |

| I <sub>DD</sub> | Maximum current (peak) during program/erase operation | Γ <sub>A</sub> = 25° C, V <sub>DD</sub> = 3.0 V | -    | 1.5  | 2.5                | mA   |

#### Table 36. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

#### Table 37. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                      | Conditions              | Value              |     |     | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------|--------------------|-----|-----|---------|

| Symbol                          | Falameter                                                                      | Conditions              | Min <sup>(1)</sup> | Тур | Мах | Unit    |

| NCYC <sup>(2)</sup>             | Cycling (erase / write)<br>Program memory                                      | $T_A = -40^{\circ}C$ to | 10                 | -   | -   | kovolos |

| NCYC <sup>(-)</sup>             | Cycling (erase / write)<br>EEPROM data memory                                  | 105 °C                  | 300                | -   | -   | kcycles |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | TRET = +85 °C           | 30                 | -   | -   |         |

| + (2)                           | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 85 °C         | TRET - +05 C            | 30                 | -   | -   | voare   |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | TRET = +105 °C          | 10                 | -   | -   | years   |

|                                 | Data retention (EEPROM data memory) after 300 kcycles at $T_A$ = 105 °C        | 11121 - 1103 C          | 10                 | _   | -   |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

### 6.3.16 Communication interfaces

# I<sup>2</sup>C interface characteristics

The STM32L151x6/8/B-A and STM32L152x6/8/B-A product line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: SDA and SCL are not "true" open-drain I/O pins. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 48*. Refer also to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            |     | rd mode<br>1)(2)    | Fast mode | Unit               |    |

|--------------------------------------------|----------------------------------------------------------------------|-----|---------------------|-----------|--------------------|----|

|                                            |                                                                      | Min | Мах                 | Min       | Мах                |    |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7 | -                   | 1.3       | -                  |    |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250 | -                   | 100       | -                  |    |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -   | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup> |    |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -   | 1000                | -         | 300                | ns |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -   | 300                 | -         | 300                |    |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0 | -                   | 0.6       | -                  |    |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7 | -                   | 0.6       | -                  | μs |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0 | -                   | 0.6       | -                  | μs |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7 | -                   | 1.3       | -                  | μs |

| Cb                                         | Capacitive load for each bus line                                    | -   | 400                 | -         | 400                | pF |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0   | 50 <sup>(4)</sup>   | 0         | 50 <sup>(4)</sup>  | ns |

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

| Symbol | Parameter                            | Test conditions                                                                        | Min <sup>(3)</sup> | Тур | Max <sup>(3)</sup> | Unit |

|--------|--------------------------------------|----------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| ET     | Total unadjusted error               |                                                                                        | -                  | 2.5 | 4                  |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                            | -                  | 1   | 2                  |      |

| EG     | Gain error                           | 2.4 V ≤ V <sub>REF+</sub> ≤ 3.6 V<br>f <sub>ADC</sub> = 8 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 1.5 | 3.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                        | -                  | 2   | 3                  |      |

| ENOB   | Effective number of bits             | 2.4 V ≤ V <sub>DDA</sub> ≤ 3.6 V                                                       | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+}$<br>f <sub>ADC</sub> = 16 MHz, R <sub>AIN</sub> = 50 Ω             | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | $T_A = -40$ to 105 ° C                                                                 | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                             | -                  | -72 | -69                |      |

| ENOB   | Effective number of bits             | $1.8 \text{ V} \le \text{V}_{\text{DDA}} \le 2.4 \text{ V}$                            | 9.5                | 10  | -                  | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+}$<br>$f_{ADC} = 8 MHz \text{ or } 4 MHz,$                           | 59                 | 62  | -                  |      |

| SNR    | Signal-to-noise ratio                | — R <sub>AIN</sub> = 50 Ω<br>_ T <sub>A</sub> = -40 to 105 ° C                         | 60                 | 62  | -                  | dB   |

| THD    | Total harmonic distortion            | F <sub>input</sub> =10 kHz                                                             | -                  | -72 | -69                |      |

| ET     | Total unadjusted error               |                                                                                        | -                  | 4   | 6.5                |      |

| EO     | Offset error                         | $2.4 \text{ V} \le \text{V}_{\text{DDA}} \le 3.6 \text{ V}$                            | -                  | 1.5 | 3.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 3.5 | 6                  | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  |      |

| EL     | Integral linearity error             |                                                                                        | -                  | 2.5 | 3.5                |      |

| ET     | Total unadjusted error               |                                                                                        | -                  | 2   | 3                  |      |

| EO     | Offset error                         | $1.8 \text{ V} \le \text{V}_{\text{DDA}} \le 2.4 \text{ V}$                            | -                  | 1   | 1.5                |      |

| EG     | Gain error                           | 1.8 V ≤ V <sub>REF+</sub> ≤ 2.4 V<br>f <sub>ADC</sub> = 4 MHz, R <sub>AIN</sub> = 50 Ω | -                  | 1.5 | 2.5                | LSB  |

| ED     | Differential linearity error         | $T_A = -40$ to 105 ° C                                                                 | -                  | 1   | 2                  | 1    |

| EL     | Integral linearity error             |                                                                                        | -                  | 2   | 3                  |      |

Table 56. ADC accuracy<sup>(1)(2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

ADC accuracy vs. negative injection current: Injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

3. Guaranteed by characterization results.

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                             | C                                                                          | onditions                     | Min | Тур       | Max                       | Unit |

|---------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|-----|-----------|---------------------------|------|

| V <sub>DDA</sub>                | Analog supply voltage                                 |                                                                            | -                             | 1.8 | -         | 3.6                       | V    |

| V <sub>REF+</sub>               | Reference supply voltage                              | V <sub>REF+</sub> must<br>V <sub>DDA</sub>                                 | always be below               | 1.8 | -         | 3.6                       | V    |

| V <sub>REF-</sub>               | Lower reference voltage                               | -                                                                          |                               |     | $V_{SSA}$ |                           | V    |

| (4)                             | Current consumption on                                | No load, mid                                                               | dle code (0x800)              | -   | 130       | 220                       | μA   |

| I <sub>DDVREF+</sub> (1)        | V <sub>REF+</sub> supply<br>V <sub>REF+</sub> = 3.3 V | No load, wor                                                               | st code (0x000)               | -   | 220       | 350                       | μA   |

| (1)                             | Current consumption on                                | No load, mid                                                               | ldle code (0x800)             | -   | 210       | 320                       | μA   |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V   | No load, wor                                                               | st code (0xF1C)               | -   | 320       | 520                       | μA   |

| D                               | Resistive load                                        | DAC output                                                                 | Connected to $V_{SSA}$        | 5   | -         | -                         | kΩ   |

| R <sub>L</sub>                  | Resistive load                                        | buffer ON                                                                  | Connected to V <sub>DDA</sub> | 25  | -         | -                         | K52  |

| CL                              | Capacitive load                                       | DAC output                                                                 | buffer ON                     | -   | -         | 50                        | pF   |

| R <sub>O</sub>                  | Output impedance                                      | DAC output                                                                 | buffer OFF                    | 12  | 16        | 20                        | kΩ   |

|                                 | Voltage on DAC_OUT                                    | DAC output buffer ON                                                       |                               | 0.2 | -         | V <sub>DDA</sub> –<br>0.2 | V    |

| V <sub>DAC_OUT</sub>            | output                                                | DAC output buffer OFF                                                      |                               | 0.5 | -         | V <sub>REF+</sub><br>1LSB | mV   |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | 1.5       | 3                         |      |

| Ditt                            |                                                       | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF         |                               | -   | 1.5       | 3                         |      |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>                 | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | 2         | 4                         |      |

|                                 | Integral nor linearity ·                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                               | -   | 2         | 4                         | LSB  |

| Offset <sup>(1)</sup>           | Offset error at code 0x800 <sup>(4)</sup>             | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                               | -   | ±10       | ±25                       |      |

| UIISEL' '                       |                                                       | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                               | -   | ±5        | ±8                        |      |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>             | No R <sub>L</sub> , C <sub>L</sub> $\leq$ DAC output                       |                               | -   | ±1.5      | ±5                        |      |

| Table | 58.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| TUDIC | <b>vv</b> . | DAO | onunuotoristios |

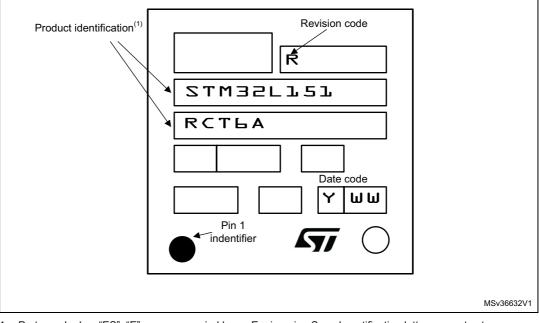

#### LQFP64 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

#### Figure 35. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

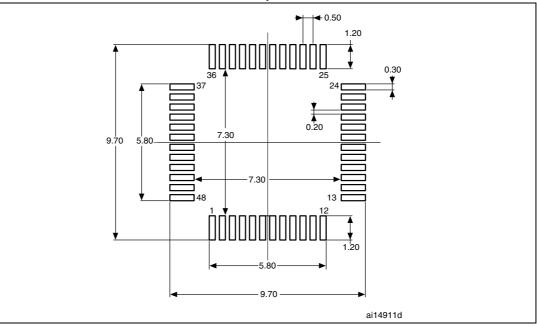

Figure 37. LQFP48 7 x 7 mm, 48-pin low-profile quad flat package recommended footprint

1. Dimensions are in millimeters.

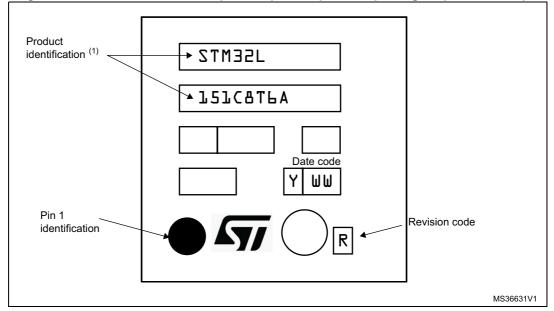

#### LQFP48 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

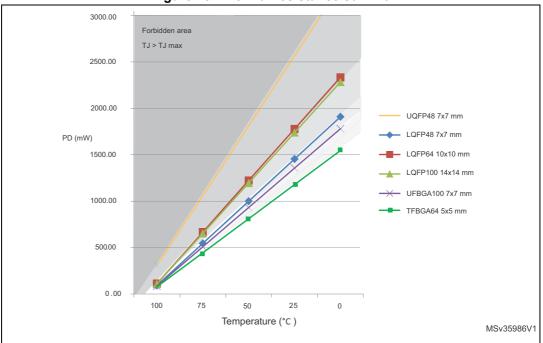

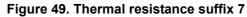

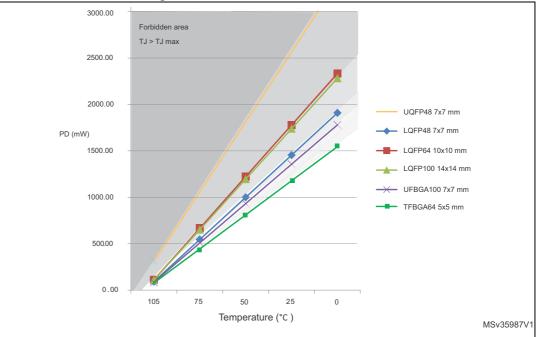

Figure 48. Thermal resistance suffix 6

# 7.7.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# 8 Ordering information

| Table 73. Ordering info                                | ormation | scheme | )  |     |   |         |

|--------------------------------------------------------|----------|--------|----|-----|---|---------|

| Example:                                               | STM32    | L 152  | RВ | T 6 | А | D TR    |

|                                                        |          |        |    |     |   |         |

| Device family                                          |          |        |    |     |   |         |

| STM32 = ARM-based 32-bit microcontroller               |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Product type                                           |          |        |    |     |   |         |

| L = Low-power                                          |          | -      |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Device subfamily                                       |          |        |    |     |   |         |

| 151: Devices without LCD                               |          |        |    |     |   |         |

| 152: Devices with LCD                                  |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Pin count                                              |          |        |    |     |   |         |

| C = 48 pins                                            |          |        | -  |     |   |         |

| R = 64 pins                                            |          |        |    |     |   |         |

| V = 100 pins                                           |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Flash memory size                                      |          |        |    |     |   |         |

| 6 = 32 Kbytes of Flash memory                          |          |        |    |     |   |         |

| 8 = 64 Kbytes of Flash memory                          |          |        |    |     |   |         |

| B = 128 Kbytes of Flash memory                         |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Package                                                |          |        |    |     |   |         |

| H = BGA                                                |          |        |    |     |   |         |

| T = LQFP                                               |          |        |    |     |   |         |

| U = UFQFPN                                             |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Temperature range                                      |          |        |    |     |   |         |

| 6 = Industrial temperature range, -40 to 85 °C         |          |        |    |     |   |         |

| 7 = Industrial temperature range, -40 to 105 °C        |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Options                                                |          |        |    |     |   |         |

| A = device generation A                                |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| No character = VDD range: 1.8 to 3.6 V and BOR enabled |          |        |    |     |   | <b></b> |

| D = VDD range: 1.65 to 3.6 V and BOR disabled          |          |        |    |     |   |         |

|                                                        |          |        |    |     |   |         |

| Packing                                                |          |        |    |     |   |         |

| TR = tape and reel                                     |          |        |    |     |   | ]       |

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.