Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectans                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, Cap Sense, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 51                                                                           |

| Program Memory Size        | 32KB (32K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 4K x 8                                                                       |

| RAM Size                   | 16K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                        |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 64-LQFP                                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l152r6t6a       |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 Introduction                                             | 9  |

|------------------------------------------------------------|----|

| 2 Description                                              |    |

| 2.1 Device overview                                        |    |

| 2.2 Ultra-low-power device continuum                       |    |

| 2.2.1 Performance                                          |    |

| 2.2.2 Shared peripherals                                   |    |

| 2.2.3 Common system strategy                               |    |

| 2.2.4 Features                                             |    |

| 3 Functional overview                                      | 13 |

| 3.1 Low-power modes                                        |    |

| 3.2 ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with MPU |    |

| 3.3 Reset and supply management                            |    |

| 3.3.1 Power supply schemes                                 |    |

| 3.3.2 Power supply supervisor                              |    |

| 3.3.3 Voltage regulator                                    |    |

| 3.3.4 Boot modes                                           |    |

| 3.4 Clock management                                       |    |

| 3.5 Low-power real-time clock and backup registers         |    |

| 3.6 GPIOs (general-purpose inputs/outputs)                 |    |

| 3.7 Memories                                               |    |

| 3.8 DMA (direct memory access)                             |    |

| 3.9 LCD (liquid crystal display)                           |    |

| 3.10 ADC (analog-to-digital converter)                     |    |

| 3.10.1 Temperature sensor                                  |    |

| 3.10.2 Internal voltage reference (V <sub>REFINT</sub> )   |    |

| 3.11 DAC (digital-to-analog converter)                     |    |

| 3.12 Ultra-low-power comparators and reference voltage     |    |

| 3.13 Routing interface                                     |    |

| 3.14 Touch sensing                                         |    |

| 3.15 Timers and watchdogs                                  |    |

# 2 Description

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a frequency of 32 MHz (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 128 Kbytes and RAM up to 32 Kbytes) and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

All the devices offer a 12-bit ADC, 2 DACs and 2 ultra-low-power comparators, six generalpurpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L151x6/8/B-A and STM32L152x6/8/B-A devices contain standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs and a USB. The STM32L151x6/8/B-A and STM32L152x6/8/B-A devices offer up to 20 capacitive sensing channels to simply add touch sensing functionality to any application.

They also include a real-time clock with sub-second counting and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller (except STM32L151x6/8/B-A devices) has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with contrast independent of the supply voltage.

The ultra-low-power STM32L151x6/8/B-A and STM32L152x6/8/B-A devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +85 °C and -40 to +105°C temperature ranges. A comprehensive set of power-saving modes allows the design of low-power applications.

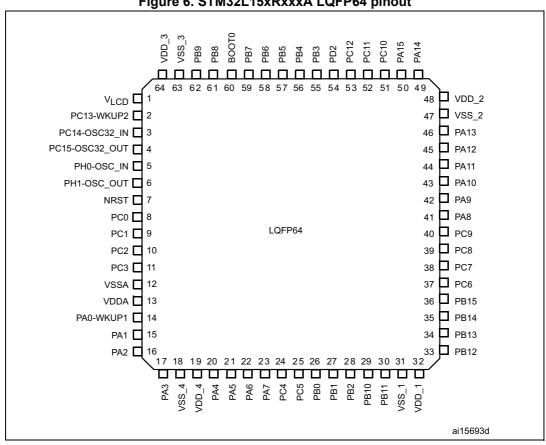

Figure 6. STM32L15xRxxxA LQFP64 pinout

1. This figure shows the package top view.

|         |        | Pins    | ;        |                    |                   |                         |               |                                                  | Pins functions          |                         |  |

|---------|--------|---------|----------|--------------------|-------------------|-------------------------|---------------|--------------------------------------------------|-------------------------|-------------------------|--|

| LQFP100 | LQFP64 | TFBGA64 | UFBGA100 | LQFP48 or UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions     | Additional<br>functions |  |

| 98      | -      | -       | A2       | -                  | PE1               | I/O                     | FT            | PE1                                              | LCD_SEG37/<br>TIM11_CH1 | -                       |  |

| 99      | 63     | D4      | D3       | 47                 | V <sub>SS_3</sub> | S                       | -             | V <sub>SS_3</sub>                                | -                       | -                       |  |

| 100     | 64     | E4      | C4       | 48                 | V <sub>DD_3</sub> | S                       | -             | V <sub>DD_3</sub>                                | -                       | -                       |  |

#### Table 9. STM32L151x6/8/B-A and STM32L152x6/8/B-A pin definitions (continued)

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 11*.

3. Applicable to STM32L152xxxxA devices only. In STM32L151xxxxA devices, this pin should be connected to V<sub>DD</sub>.

4. The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

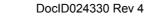

The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

6. Unlike in the LQFP64 package, there is no PC3 in the TFBGA64 package. The V<sub>REF+</sub> functionality is provided instead.

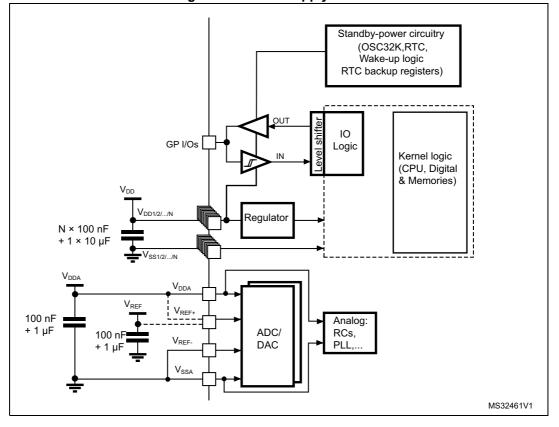

# 6.1.6 Power supply scheme

## Figure 12. Power supply scheme

| Symbol               | Parameter            | Cond                                           | litions                                            | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------|------------------------------------------------|----------------------------------------------------|-------------------|-------|--------------------|------|

|                      |                      |                                                |                                                    | 1 MHz             | 215   | 285                |      |

|                      |                      |                                                | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 2 MHz             | 400   | 490                | μA   |

|                      |                      |                                                |                                                    | 4 MHz             | 725   | 1000               |      |

|                      |                      | $f_{HSE} = f_{HCLK}$<br>up to 16 MHz, included |                                                    | 4 MHz             | 0.915 | 1.3                |      |

|                      |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above  | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 8 MHz             | 1.75  | 2.15               |      |

| 0                    | Supply               | 16 MHz<br>(PLL ON) <sup>(2)</sup>              |                                                    | 16 MHz            | 3.4   | 4                  |      |

|                      | Supply<br>current in |                                                | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 8 MHz             | 2.1   | 2.9                |      |

| I <sub>DD (Run</sub> | Run mode, code       |                                                |                                                    | 16 MHz            | 4.2   | 5.2                |      |

| from Flash)          | executed             |                                                |                                                    | 32 MHz            | 8.25  | 9.6                |      |

| from                 | from Flash           | HSI clock source (16<br>MHz)                   | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 3.5   | 4.4                | mA   |

|                      |                      |                                                | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 8.2   | 10.2               |      |

|                      |                      | MSI clock, 65 kHz                              |                                                    | 65 kHz            | 0.041 | 0.085              |      |

|                      |                      | MSI clock, 524 kHz                             | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 524 kHz           | 0.125 | 0.180              |      |

|                      |                      | MSI clock, 4.2 MHz                             |                                                    | 4.2 MHz           | 0.775 | 0.935              |      |

### Table 18. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                                         | Parameter                                          |                                              | Conditions                                      |                                         | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------------------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------|-----------------------------------------|------|--------------------|------|

|                                                |                                                    |                                              |                                                 | $T_A$ = -40 °C to 25 °C                 | 10.9 | 12                 |      |

|                                                |                                                    |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | T <sub>A</sub> = 85 °C                  | 16.5 | 23                 |      |

|                                                |                                                    |                                              | HOLK V- WH                                      | T <sub>A</sub> = 105 °C                 | 26   | 47                 |      |

|                                                |                                                    | All peripherals<br>OFF, code                 |                                                 | $T_A$ = -40 °C to 25 °C                 | 15   | 16                 |      |

|                                                |                                                    | executed from<br>RAM, Flash                  | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | T <sub>A</sub> = 85 °C                  | 22   | 29                 |      |

|                                                |                                                    | switched OFF,                                | HOLK COMME                                      | T <sub>A</sub> = 105 °C                 | 32   | 51                 |      |

|                                                |                                                    | V <sub>DD</sub> from<br>1.65 V to 3.6 V      |                                                 | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 29   | 37                 |      |

|                                                |                                                    | 1.00 V 10 0.0 V                              | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 32.5 | 40                 |      |

|                                                | Supply<br>current in<br>Low-power<br>run mode      |                                              | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 35.5 | 54                 | -    |

| I <sub>DD</sub>                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 45   | 65                 |      |

| (LP Run)                                       |                                                    | All peripherals<br>OFF, code                 | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz | $T_A$ = -40 °C to 25 °C                 | 23   | 24                 |      |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 85 °C                  | 31   | 34                 | μA   |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 42.5 | 56                 |      |

|                                                |                                                    |                                              | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 65 kHz | $T_A$ = -40 °C to 25 °C                 | 29   | 31                 |      |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 85 °C                  | 38   | 41                 |      |

|                                                |                                                    | executed from<br>Flash, V <sub>DD</sub> from |                                                 | T <sub>A</sub> = 105 °C                 | 49   | 63                 |      |

|                                                |                                                    | 1.65 V to 3.6 V                              |                                                 | $T_A$ = -40 °C to 25 °C                 | 46   | 55                 | 1    |

|                                                |                                                    |                                              | MSI clock, 131 kHz                              | T <sub>A</sub> = 55 °C                  | 48   | 59                 |      |

|                                                |                                                    |                                              | f <sub>HCLK</sub> = 131 kHz                     | T <sub>A</sub> = 85 °C                  | 53.5 | 72                 | 1    |

|                                                |                                                    |                                              |                                                 | T <sub>A</sub> = 105 °C                 | 64.8 | 84                 |      |

| I <sub>DD</sub> Max<br>(LP Run) <sup>(2)</sup> | Max allowed<br>current in<br>Low-power<br>run mode | V <sub>DD</sub> from<br>1.65 V to 3.6 V      | -                                               | -                                       | -    | 200                |      |

Table 21. Current consumption in Low-power run mode

1. Guaranteed by characterization results, unless otherwise specified.

2. This limitation is related to the consumption of the CPU core and the peripherals that are powered by the regulator. Consumption of the I/Os is not included in this limitation.

| Symbol                | Parameter                                          | Conditions                                                                                     |                                           |                                                                          | Typ <sup>(1)</sup> | Max<br>(1)(2) | Unit |

|-----------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------|--------------------|---------------|------|

|                       |                                                    |                                                                                                |                                           | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 1.8 \text{ V}$ | 1.13               | -             |      |

|                       |                                                    |                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.38               | 4             |      |

|                       |                                                    |                                                                                                | LCD OFF                                   | T <sub>A</sub> = 55°C                                                    | 1.70               | 6             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.30               | 10            |      |

|                       |                                                    | RTC clocked by LSI,                                                                            |                                           | T <sub>A</sub> = 105°C                                                   | 7.80               | 23            |      |

|                       |                                                    | regulator in LP mode, HSI                                                                      |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.50               | 6             |      |

|                       |                                                    | and HSE OFF<br>(no independent                                                                 | LCD ON<br>(static                         | T <sub>A</sub> = 55°C                                                    | 1.80               | 7             |      |

|                       |                                                    | watchdog)                                                                                      | duty) <sup>(3)</sup>                      | T <sub>A</sub> = 85°C                                                    | 3.45               | 12            |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 8.02               | 27            |      |

|                       |                                                    |                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.80               | 10            |      |

|                       |                                                    |                                                                                                | LCD ON<br>(1/8<br>duty) <sup>(4)</sup>    | T <sub>A</sub> = 55°C                                                    | 4.30               | 11            | μΑ   |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 6.10               | 16            |      |

|                       | Supply current in<br>Stop mode with<br>RTC enabled |                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 10.8               | 44            |      |

|                       |                                                    | RTC clocked by LSE<br>external clock (32.768<br>kHz), regulator in LP<br>mode, HSI and HSE OFF | LCD OFF                                   | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.50               | -             |      |

| I <sub>DD (Stop</sub> |                                                    |                                                                                                |                                           | T <sub>A</sub> = 55°C                                                    | 1.90               | -             |      |

| with RTC)             |                                                    |                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.65               | -             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 8.25               | -             |      |

|                       |                                                    |                                                                                                | LCD ON<br>(static<br>duty) <sup>(3)</sup> | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 1.60               | -             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 55°C                                                    | 2.05               | -             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 85°C                                                    | 3.75               | -             |      |

|                       |                                                    | (no independent<br>watchdog)                                                                   |                                           | T <sub>A</sub> = 105°C                                                   | 8.40               | -             |      |

|                       |                                                    |                                                                                                |                                           | $T_A = -40^{\circ}C$ to $25^{\circ}C$                                    | 3.90               | -             |      |

|                       |                                                    |                                                                                                | LCD ON<br>(1/8                            | T <sub>A</sub> = 55°C                                                    | 4.55               | -             |      |

|                       |                                                    |                                                                                                | duty) <sup>(4)</sup>                      | T <sub>A</sub> = 85°C                                                    | 6.35               | -             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = 105°C                                                   | 11.10              | -             |      |

|                       |                                                    |                                                                                                |                                           | T <sub>A</sub> = -40°C to 25°C<br>V <sub>DD</sub> = 1.8 V                | 1.23               | -             |      |

|                       |                                                    | RTC clocked by LSE (no independent watchdog) <sup>(5)</sup>                                    | LCD OFF                                   | T <sub>A</sub> = -40°C to 25°C<br>V <sub>DD</sub> = 3.0 V                | 1.50               | -             |      |

|                       |                                                    |                                                                                                |                                           | $T_A = -40^{\circ}C \text{ to } 25^{\circ}C$<br>$V_{DD} = 3.6 \text{ V}$ | 1.75               | -             |      |

# Table 23. Typical and maximum current consumptions in Stop mode

| Peripheral                                 |           | Туріса                                                    | Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                                                           |                            |      |  |

|--------------------------------------------|-----------|-----------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|----------------------------|------|--|

|                                            |           | Range 1,<br>V <sub>CORE</sub> =<br>1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =<br>1.5 V<br>VOS[1:0] = 10            | Range 3,<br>V <sub>CORE</sub> =<br>1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and run | Unit |  |

| I <sub>DD (RTC)</sub>                      |           |                                                           | 0.4                                                                  |                                                           |                            |      |  |

| I <sub>DD (LCD)</sub>                      |           |                                                           | 3.1                                                                  |                                                           |                            |      |  |

| I <sub>DD (ADC)</sub> <sup>(4)</sup>       |           |                                                           |                                                                      |                                                           |                            |      |  |

| I <sub>DD (DAC)</sub> <sup>(5)</sup>       |           |                                                           |                                                                      |                                                           |                            |      |  |

| IDD (COMP1)                                |           |                                                           | μA                                                                   |                                                           |                            |      |  |

| 1                                          | Slow mode |                                                           | 2                                                                    |                                                           |                            |      |  |

| IDD (COMP2)                                | Fast mode |                                                           | 5                                                                    |                                                           |                            |      |  |

| I <sub>DD (PVD / BOR)</sub> <sup>(6)</sup> |           |                                                           |                                                                      |                                                           |                            |      |  |

| I <sub>DD (IWDG)</sub>                     |           |                                                           | 0.25                                                                 |                                                           |                            |      |  |

| Table 25. Peripheral | current consumption <sup>(1)</sup> | (continued) |

|----------------------|------------------------------------|-------------|

|----------------------|------------------------------------|-------------|

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (Range 1), f<sub>HCLK</sub> = 16 MHz (Range 2), f<sub>HCLK</sub> = 4 MHz (Range 3), f<sub>HCLK</sub> = 64kHz (Lowpower run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling.

2. HSI oscillator is OFF for this measure.

- 3. In low-power sleep and run mode, the Flash memory must always be in power-down mode.

- 4. Data based on a differential Ibb measurement between ADC in reset configuration and continuous ADC conversion (HSI consumption not included).

- Data based on a differential IDD measurement between DAC in reset configuration and continuous DAC conversion of VDD/2. DAC is in buffered mode, output is left floating.

- 6. Including supply current of internal reference voltage.

# 6.3.5 Wakeup time from Low-power mode

The wakeup times given in the following table are measured with the MSI RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is the MSI oscillator in the range configured before entering Stop mode

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Figure 17. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

### Low-speed external clock generated from a crystal/ceramic resonator

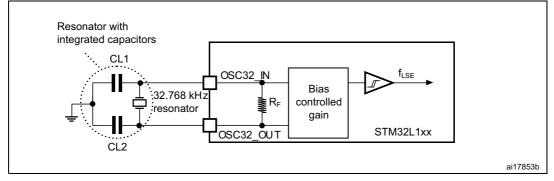

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 14*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                                                                     | Conditions                            | Min | Тур    | Мах | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |

| C <sup>(2)</sup>                    | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |

| I <sub>LSE</sub>                    | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |

|                                     | LSE oscillator current consumption                                                            | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |

| I <sub>DD (LSE)</sub>               |                                                                                               | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |

|                                     |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                                                                                  | $V_{DD}$ is stabilized                | -   | 1      | -   | S    |

| Table 30. LSE oscillator characteristics | ; (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> |

|------------------------------------------|--------------------------------------------------|

|------------------------------------------|--------------------------------------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small  $R_S$  value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

- Note: For CL1 and CL2, it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 18). CL1 and CL2, are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of CL1 and CL2. Load capacitance CL has the following formula: CL = CL1 x CL2 / (CL1 + CL2) + Cstray where Cstray is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- Caution: To avoid exceeding the maximum value of CL1 and CL2 (15 pF) it is strongly recommended to use a resonator with a load capacitance CL ≤ 7 pF. Never use a resonator with a load capacitance of 12.5 pF.

Example: if you choose a resonator with a load capacitance of CL = 6 pF and Cstray = 2 pF, then CL1 = CL2 = 8 pF.

# 6.3.7 Internal clock source characteristics

The parameters given in the following table are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                                         | Conditions                                                           | Min               | Тур  | Max              | Unit |

|-------------------------------------|---------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI</sub>                    | Frequency                                         | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>              | HSI user-trimmed                                  | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

| TRIM                                | resolution                                        | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                     |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the factory-calibrated HSI oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                | -1.5              | -    | 1.5              | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              | -2                | -    | 2                | %    |

| ACC <sub>HSI</sub> <sup>(2)</sup>   |                                                   | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 85 °C              | -2.5              | -    | 2                | %    |

|                                     |                                                   | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             | -4                | -    | 2                | %    |

|                                     |                                                   | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 105 °C | -4                | -    | 3                | %    |

| t <sub>SU(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>startup time                    | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator<br>power consumption               | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

# Low-speed internal (LSI) RC oscillator

| Table 32. LSI oscillator | r characteristics |

|--------------------------|-------------------|

|--------------------------|-------------------|

| Symbol                              | Parameter                                                   | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                               | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift<br>0°C ≤T <sub>A</sub> ≤85°C | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                 | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                            | _   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

| Symbol                                | Parameter                          | Condition                                | Тур | Max | Unit    |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|---------|

|                                       |                                    | MSI range 0                              | -   | 40  |         |

|                                       |                                    | MSI range 1                              | -   | 20  |         |

|                                       |                                    | MSI range 2                              | -   | 10  |         |

|                                       |                                    | MSI range 3                              | -   | 4   |         |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 | μs      |

|                                       |                                    | MSI range 5                              | -   | - 2 |         |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |         |

|                                       |                                    | MSI range 3,<br>Voltage Range 3          | -   | 3   |         |

| fourment                              | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz     |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                     | -   | 6   | 1011 12 |

Table 33. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Table 34. | PLL | chara | cteristics |

|-----------|-----|-------|------------|

|-----------|-----|-------|------------|

| Symbol                                         | Parameter                                                   |           | Value |                    | Unit |  |

|------------------------------------------------|-------------------------------------------------------------|-----------|-------|--------------------|------|--|

| Symbol Parameter                               |                                                             | Min       | Тур   | Max <sup>(1)</sup> | Unit |  |

| f                                              | PLL input clock <sup>(2)</sup>                              | 2         | -     | 24                 | MHz  |  |

| f <sub>PLL_IN</sub> PLL input clock duty cycle |                                                             | 45        | -     | 55                 | %    |  |

| f <sub>PLL_OUT</sub>                           | PLL output clock                                            | 2         | -     | 32                 | MHz  |  |

| t <sub>LOCK</sub>                              | PLL lock time<br>PLL input = 16 MHz - 1<br>PLL VCO = 96 MHz |           | 115   | 160                | μs   |  |

| Jitter                                         | Cycle-to-cycle jitter                                       | -         | -     | ± 600              | ps   |  |

| I <sub>DDA</sub> (PLL)                         | Current consumption on V <sub>DDA</sub>                     | - 220 450 |       |                    |      |  |

| I <sub>DD</sub> (PLL)                          | Current consumption on $V_{DD}$                             | -         | 120   | 150                | μA   |  |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL\_OUT}}$ .

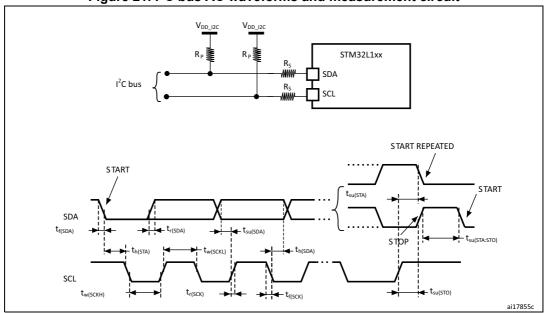

Figure 21. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistors

- 2.  $R_P$  = pull-up resistors

- 3.  $V_{DD_{12C}} = 12C$  bus supply

- 4. Measurement points are done at CMOS levels: 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

| £ (1.11-)              | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801B                  |

| 300                    | 0x8024                  |

| 200                    | 0x8035                  |

| 100                    | 0x00A0                  |

| 50                     | 0x0140                  |

| 20                     | 0x0320                  |

# Table 49. SCL frequency $(f_{PCLK1} = 32 \text{ MHz}, V_{DD} = V_{DD_12C} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol                         | Parameter                            | Conditions                                                          | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|--------------------------------|--------------------------------------|---------------------------------------------------------------------|---------------------|---------------------|------|

| Input leve                     | ls                                   |                                                                     |                     |                     |      |

| $V_{DD}$                       | USB operating voltage <sup>(2)</sup> | -                                                                   | 3.0                 | 3.6                 | V    |

| $V_{DI}^{(3)}$                 | Differential input sensitivity       | I(USB_DP, USB_DM)                                                   | 0.2                 | -                   |      |

| V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range       | Includes V <sub>DI</sub> range                                      | 0.8                 | 2.5                 | V    |

| $V_{SE}^{(3)}$                 | Single ended receiver threshold      | -                                                                   | 1.3                 | 2.0                 |      |

| Output le                      | vels                                 |                                                                     |                     |                     |      |

| $V_{OL}^{(4)}$                 | Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(5)}$          | -                   | 0.3                 | v    |

| V <sub>OH</sub> <sup>(4)</sup> | Static output level high             | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}^{(5)}$ | 2.8                 | 3.6                 |      |

Table 52. USB DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. Guaranteed by characterization results.

4. Guaranteed by test in production.

5.  $\ensuremath{\,R_L}$  is the load connected on the USB drivers.

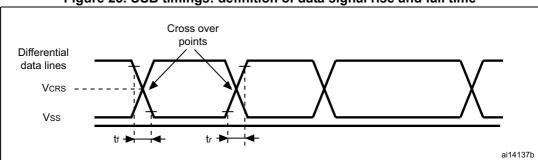

#### Figure 25. USB timings: definition of data signal rise and fall time

#### Table 53. USB: full speed electrical characteristics

|                  | Driver characteristics <sup>(1)</sup> |                                |     |     |    |  |  |

|------------------|---------------------------------------|--------------------------------|-----|-----|----|--|--|

| Symbol           | Parameter Conditions Min Max Uni      |                                |     |     |    |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |

| t <sub>f</sub>   | Fall Time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching              | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage       | -                              | 1.3 | 2.0 | V  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification section 7 (version 2.0).

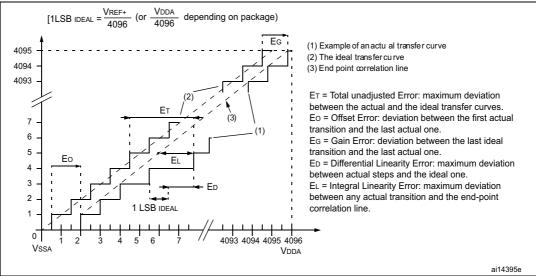

#### Figure 26. ADC accuracy characteristics

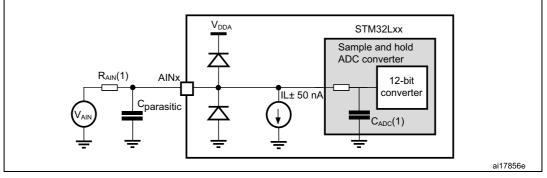

#### Figure 27. Typical connection diagram using the ADC

- 1. Refer to Table 57: Maximum source impedance RAIN max for the value of RAIN and Table 55: ADC characteristics for the value of CADC

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

| Symbol                    | Parameter                                                                                                                                                    | Conditions                                                                           | Min | Тур             | Max              | Unit    |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------|------------------|---------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature                                                                                                                                     | $V_{DDA} = 3.3V, V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF    | -20 | -10             | 0                | - μV/°C |  |

| uonseva t                 | coefficient (code 0x800)                                                                                                                                     | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | 0   | 20              | 50               | μν/ Ο   |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(6)</sup>                                                                                                                                    | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON           | -   | +0.1 /<br>-0.2% | +0.2 / -<br>0.5% | %       |  |

| Gainty                    | Gainenor                                                                                                                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | +0 / -<br>0.2%  | +0 / -<br>0.4%   | 70      |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                       | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF | -10 | -2              | 0                | -μV/°C  |  |

| coefficient               |                                                                                                                                                              | $V_{DDA} = 3.3V$ , $V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer ON  | -40 | -8              | 0                | μv/ C   |  |

| TUE <sup>(1)</sup>        | Total unadjusted error                                                                                                                                       | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON          | -   | 12              | 30               | LSB     |  |

|                           |                                                                                                                                                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                          | -   | 8               | 12               | LOD     |  |

| tSETTLING                 | Settling time (full scale: for a<br>12-bit code transition<br>between the lowest and the<br>highest input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 7               | 12               | μs      |  |

| Update rate               | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -               | 1                | Msps    |  |

| t <sub>WAKEUP</sub>       | Wakeup time from off state<br>(setting the ENx bit in the<br>DAC Control register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | 9               | 15               | μs      |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection ratio (static DC measurement)                                                                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                   | -   | -60             | -35              | dB      |  |

Table 58. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

4. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 5. Difference between the value measured at Code (0x001) and the ideal value.

- 6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

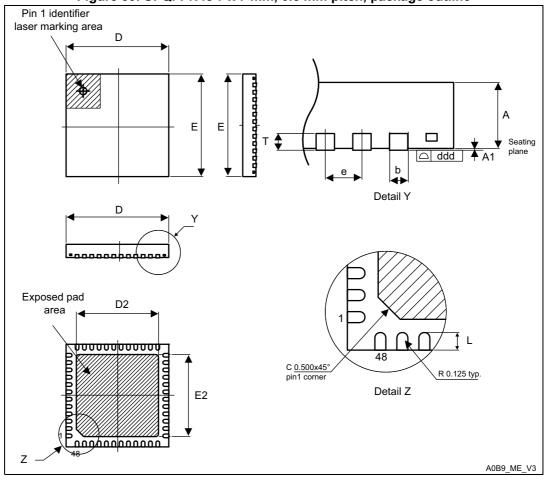

# 7.4 UFQFPN48 7 x 7 mm, 0.5 mm pitch, package information

Figure 39. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

| Table 68. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array |  |

|----------------------------------------------------------------------------------|--|

| package mechanical data (continued)                                              |  |

| Symbol |     | millimeters |      |        | inches <sup>(1)</sup> |        |

|--------|-----|-------------|------|--------|-----------------------|--------|

| Symbol | Min | Тур         | Max  | Min    | Тур                   | Max    |

| F      | 0.7 | 0.75        | 0.8  | 0.0276 | 0.0295                | 0.0315 |

| ddd    | -   | -           | 0.1  | -      | -                     | 0.0039 |

| eee    | -   | -           | 0.15 | -      | -                     | 0.0059 |

| fff    | -   | -           | 0.05 | -      | -                     | 0.002  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

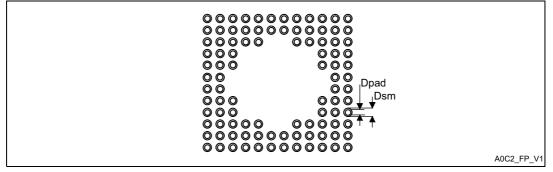

# Figure 43. UFBGA100 7 x 7 mm, 0.5 mm pitch, ultra thin fine-pitch ball grid array package recommended footprint

#### Table 69. UFBGA100 7 x 7 mm, 0.5 mm pitch, recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

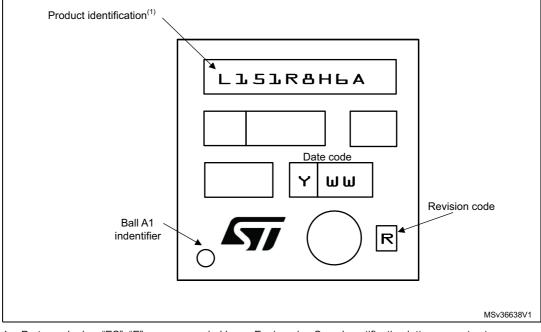

#### **TFBGA64** device marking

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Figure 47. TFBGA64 5 x 5 mm, 0.5 mm pitch, package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.