Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

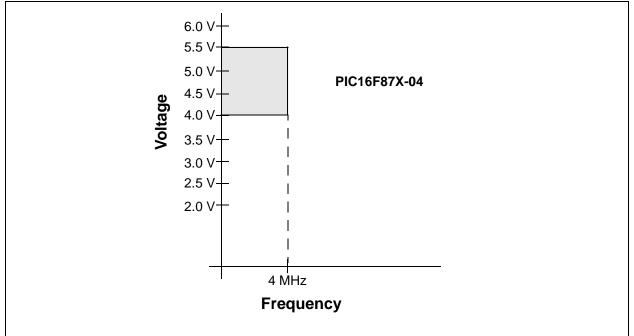

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

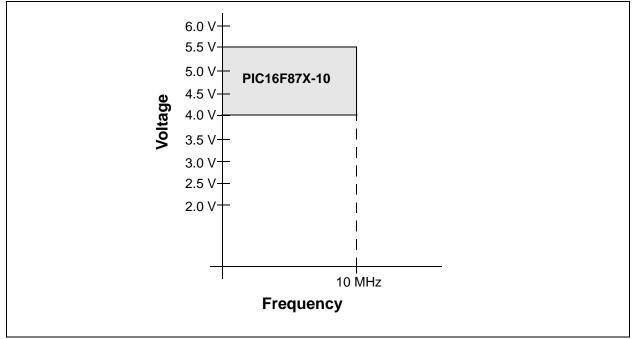

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be found in Section 4.0 of this data sheet. |

|-------|--------------------------------------------------------------------------------|

| 2.2.4 |                                                                                |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

## 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                                                                  | Freq.          | C1           | C2        |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------|--|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                        | 32 kHz         | 33 pF        | 33 pF     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 100 kHz        | 15 pF        | 15 pF     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           | 200 kHz        | 15 pF        | 15 pF     |  |  |  |  |  |

| These va                                                                                                                                                                                                                                                                                                                                                  | lues are for o | design guida | nce only. |  |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                                                                          |                |              |           |  |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                                                                | Epson C-00     | 1R32.768K-A  | ± 20 PPM  |  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                                                                   | Epson C-2      | ± 20 PPM     |           |  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                                                                   | STD XTL        | ± 20 PPM     |           |  |  |  |  |  |

| <ul> <li>200 kHz STD XTL 200.000 kHz ± 20 PPM</li> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                |              |           |  |  |  |  |  |

## 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

| REGISTER 0-1: | R 6-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 1717/1011)                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------|-------------|--------------|--------|--|--|--|

|               | U-0                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0      | R/W-0        | R/W-0    | R/W-0       | R/W-0        | R/W-0  |  |  |  |

|               | —                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CCPxX      | CCPxY        | CCPxM3   | CCPxM2      | CCPxM1       | CCPxM0 |  |  |  |

|               | bit 7                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              | bit 0  |  |  |  |

|               |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

|               | bit 7-6 Unimplemented: Read as '0'                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

| bit 5-4       |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Least Sign | ificant bits |          |             |              |        |  |  |  |

|               | <u>Capture mode</u> :<br>Unused                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

|               | <u>Compare n</u><br>Unused                                                                                         | node:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |              |          |             |              |        |  |  |  |

|               | <u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCP             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

| bit 3-0       | CCPxM3:C                                                                                                           | CPxM0: C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CPx Mode S | Select bits  |          |             |              |        |  |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res | <pre>CCPxM3:CCPxM0: CCPx Mode Select bits<br/>0000 = Capture/Compare/PWM disabled (resets CCPx module)<br/>0100 = Capture mode, every falling edge<br/>0101 = Capture mode, every rising edge<br/>0110 = Capture mode, every 4th rising edge<br/>0111 = Capture mode, every 16th rising edge<br/>1000 = Compare mode, every 16th rising edge<br/>1001 = Compare mode, set output on match (CCPxIF bit is set)<br/>1001 = Compare mode, clear output on match (CCPxIF bit is set)<br/>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is<br/>unaffected)<br/>1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP1<br/>resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is<br/>enabled)<br/>11xx = PWM mode</pre> |            |              |          |             |              |        |  |  |  |

|               | Legend:                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |              |          |             |              |        |  |  |  |

|               | R = Reada                                                                                                          | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VV = V     | Vritable bit | U = Unim | plemented l | bit, read as | ʻ0'    |  |  |  |

'1' = Bit is set

- n = Value at POR

## REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

|       | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                        | R/W-0                       | R/W-0                     | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|-------------------------|---------------|---------------|-------------|--|--|--|--|

|       | GCEN                                                                                                                                                                                                                        | ACKSTAT                                                                                                                                                                                                                                                      | ACKDT                       | ACKEN                     | RCEN                    | PEN           | RSEN          | SEN         |  |  |  |  |

|       | bit 7                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               | bit 0       |  |  |  |  |

| bit 7 | <b>GCEN</b> : General Call Enable bit (In I <sup>2</sup> C Slave mode only)<br>1 = Enable interrupt when a general call address (0000h) is received in the SSPSR<br>0 = General call address disabled                       |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               |             |  |  |  |  |

| bit 6 | ACKSTAT: Acknowledge Status bit (In I <sup>2</sup> C Master mode only)                                                                                                                                                      |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               |             |  |  |  |  |

|       | In Master Transmit mode:<br>1 = Acknowledge was not received from slave<br>0 = Acknowledge was received from slave                                                                                                          |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               |             |  |  |  |  |

| bit 5 | ACKDT: A                                                                                                                                                                                                                    | cknowledge [                                                                                                                                                                                                                                                 | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m   | ode only)               |               |               |             |  |  |  |  |

|       | Value that<br>end of a re<br>1 = Not Ac                                                                                                                                                                                     | ACKDT: Acknowledge Data bit (In I <sup>2</sup> C Master mode only)<br><u>In Master Receive mode:</u><br>Value that will be transmitted when the user initiates an Acknowledge sequence at the<br>end of a receive.<br>1 = Not Acknowledge<br>0 = Acknowledge |                             |                           |                         |               |               |             |  |  |  |  |

| bit 4 | ACKEN: A                                                                                                                                                                                                                    | cknowledge \$                                                                                                                                                                                                                                                | Sequence E                  | nable bit (In             | I <sup>2</sup> C Master | mode only)    |               |             |  |  |  |  |

|       | 1 = Initiate<br>Autom                                                                                                                                                                                                       | Receive mode<br>Acknowledge<br>atically cleare<br>wledge seque                                                                                                                                                                                               | e sequence<br>ed by hardw   |                           | I SCL pins a            | and transmit  | ACKDT da      | ta bit.     |  |  |  |  |

| bit 3 | RCEN: Re                                                                                                                                                                                                                    | ceive Enable<br>es Receive mo                                                                                                                                                                                                                                | bit (In I <sup>2</sup> C M  | laster mode               | only)                   |               |               |             |  |  |  |  |

| bit 2 | PEN: STC                                                                                                                                                                                                                    | P Condition I                                                                                                                                                                                                                                                | Enable bit (I               | n I <sup>2</sup> C Master | r mode only             | )             |               |             |  |  |  |  |

|       | 1 = Initiate                                                                                                                                                                                                                | ase Control:<br>STOP condit<br>condition idle                                                                                                                                                                                                                |                             | and SCL pir               | ns. Automat             | ically cleare | d by hardwa   | are.        |  |  |  |  |

| bit 1 | 1 = Initiate                                                                                                                                                                                                                | epeated STAR<br>Repeated ST/<br>ted START co                                                                                                                                                                                                                 | ART conditic                | on on SDA an              |                         |               |               | / hardware. |  |  |  |  |

| bit 0 | 1 = Initiate                                                                                                                                                                                                                | <ul> <li>START Condition Enable bit (In I<sup>2</sup>C Master mode only)</li> <li>1 = Initiate START condition on SDA and SCL pins. Automatically cleared by hardware.</li> <li>0 = START condition idle</li> </ul>                                          |                             |                           |                         |               |               |             |  |  |  |  |

|       | <b>Note:</b> For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I <sup>2</sup> C module is not in the IDLE mode, this bit may not be set (no spooling), and the SSPBUF may not be written (or writes to the SSPBUF are disabled). |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               |             |  |  |  |  |

|       | Logondi                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                              |                             |                           |                         |               |               |             |  |  |  |  |

|       | Legend:<br>R = Reada                                                                                                                                                                                                        | blo bit                                                                                                                                                                                                                                                      | ۱۸/ _ ۱۸/-                  | itable bit                |                         | plemented k   | hit road as f | 0'          |  |  |  |  |

|       | K = Keaua                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                              | vv = vvi                    |                           | 0 = 0.000               |               | n, reau as    | 0           |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

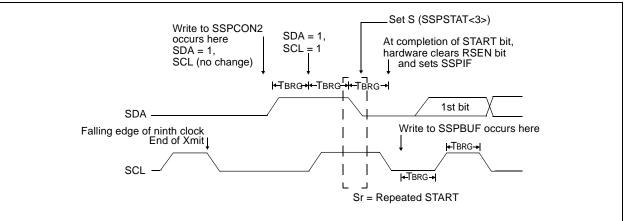

### 9.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the  $I^2C$ module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG, while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 9.2.10.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

#### FIGURE 9-13: REPEAT START CONDITION WAVEFORM

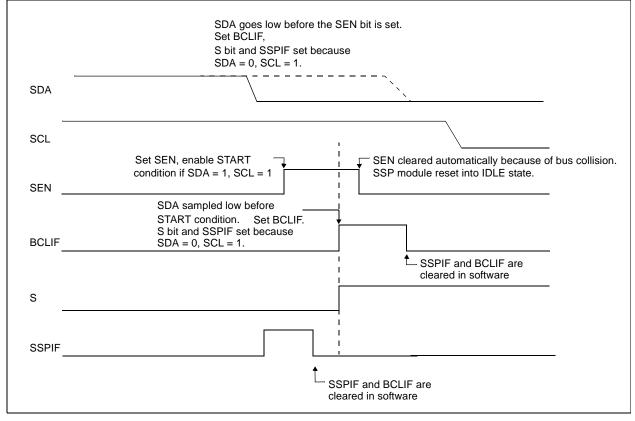

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

## 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                                                                                                                       | R/W-0         | R/W-0        | R/W-0          | U-0            | R/W-0     | R-1           | R/W-0      |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|---------------|--------------|----------------|----------------|-----------|---------------|------------|--|--|--|

|       | CSRC                                                                                                                        | TX9           | TXEN         | SYNC           | _              | BRGH      | TRMT          | TX9D       |  |  |  |

|       | bit 7                                                                                                                       |               |              |                |                |           |               | bit 0      |  |  |  |

|       |                                                                                                                             |               |              |                |                |           |               |            |  |  |  |

| bit 7 | CSRC: Clock Source Select bit                                                                                               |               |              |                |                |           |               |            |  |  |  |

|       | Asynchrono                                                                                                                  | us mode:      |              |                |                |           |               |            |  |  |  |

|       | Don't care<br>Synchronous mode:                                                                                             |               |              |                |                |           |               |            |  |  |  |

|       |                                                                                                                             |               | generated ir | nternally from | n BRG)         |           |               |            |  |  |  |

|       | <ul><li>1 = Master mode (clock generated internally from BRG)</li><li>0 = Slave mode (clock from external source)</li></ul> |               |              |                |                |           |               |            |  |  |  |

| bit 6 | TX9: 9-bit Tr                                                                                                               |               |              |                |                |           |               |            |  |  |  |

|       | 1 = Selects 9<br>0 = Selects 8                                                                                              |               |              |                |                |           |               |            |  |  |  |

| bit 5 | TXEN: Tran                                                                                                                  | smit Enable   | bit          |                |                |           |               |            |  |  |  |

|       | 1 = Transmit                                                                                                                |               |              |                |                |           |               |            |  |  |  |

|       | 0 = Transmit                                                                                                                | tdisabled     |              |                |                |           |               |            |  |  |  |

|       | Note: SREN                                                                                                                  | I/CREN ovei   | rides TXEN   | in SYNC m      | ode.           |           |               |            |  |  |  |

| bit 4 |                                                                                                                             | RT Mode S     | elect bit    |                |                |           |               |            |  |  |  |

|       | 1 = Synchro<br>0 = Asynchro                                                                                                 |               |              |                |                |           |               |            |  |  |  |

| bit 3 | Unimpleme                                                                                                                   |               |              |                |                |           |               |            |  |  |  |

| bit 2 | BRGH: High                                                                                                                  |               |              |                |                |           |               |            |  |  |  |

|       | Asynchrono                                                                                                                  |               | 000000       |                |                |           |               |            |  |  |  |

|       | 1 = High spe                                                                                                                | ed            |              |                |                |           |               |            |  |  |  |

|       | 0 = Low spe                                                                                                                 |               |              |                |                |           |               |            |  |  |  |

|       | Synchronous<br>Unused in th                                                                                                 |               |              |                |                |           |               |            |  |  |  |

| bit 1 | TRMT: Trans                                                                                                                 |               | aister Statu | s bit          |                |           |               |            |  |  |  |

|       | 1 = TSR em                                                                                                                  |               | 9            |                |                |           |               |            |  |  |  |

|       | 0 = TSR full                                                                                                                |               |              |                |                |           |               |            |  |  |  |

| bit 0 | <b>TX9D:</b> 9th b                                                                                                          | it of Transmi | t Data, can  | be parity bit  |                |           |               |            |  |  |  |

|       | Logondi                                                                                                                     |               |              |                |                |           |               |            |  |  |  |

|       | Legend:<br>R = Readab                                                                                                       | la hit        | W = Wri      | tahla hit      | U = Unimple    | amonted b | it road as "  | <b>)</b> ' |  |  |  |

|       | - n = Value a                                                                                                               |               | '1' = Bit    |                | '0' = Bit is c |           | x = Bit is ur |            |  |  |  |

|       |                                                                                                                             |               | i – Dil      | 10 301         |                |           |               | IN IOWIT   |  |  |  |

#### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |  |  |  |

|------|-------------------------------------------|----------------------------|--|--|--|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |  |  |  |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |  |  |  |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|-----------|-----------|-----------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9       | TXEN      | SYNC      |       | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9       | SREN      | CREN      | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | te Genera | 0000 0000 | 0000 0000 |       |       |       |       |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

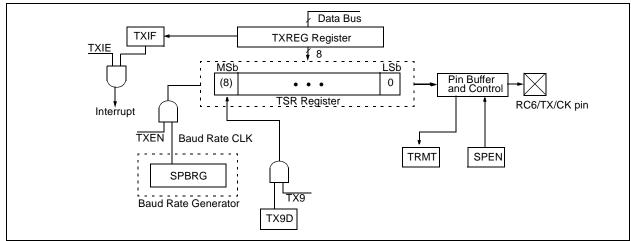

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

## 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

## 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5                                               | Bit 4         | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|------------|-----------------------------------------------------|---------------|------------|---------|--------|--------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE                                                | INTE          | RBIE       | TOIF    | INTF   | RBIF   | 0000 000x               | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF                                                | TXIF          | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE                                                | TXIE          | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                         |

| 1Eh                   | ADRESH | A/D Resul            | t Register | High By                                             | te            |            |         |        |        | xxxx xxxx               | uuuu uuuu                         |

| 9Eh                   | ADRESL | A/D Resul            | t Register | Low Byt                                             | e             |            |         |        |        | xxxx xxxx               | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2                                                | CHS1          | CHS0       | GO/DONE | _      | ADON   | 0000 00-0               | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | —          | _                                                   | _             | PCFG3      | PCFG2   | PCFG1  | PCFG0  | 0- 0000                 | 0- 0000                           |

| 85h                   | TRISA  | —                    | —          | PORTA                                               | Data Directio | n Register |         |        |        | 11 1111                 | 11 1111                           |

| 05h                   | PORTA  |                      | —          | PORTA Data Latch when written: PORTA pins when read |               |            |         |        |        | 0x 0000                 | 0u 0000                           |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV PSPMODE — PORTE Data Direction bits            |               |            |         |        |        | 0000 -111               | 0000 -111                         |

| 09h <sup>(1)</sup>    | PORTE  | —                    | —          |                                                     | —             | —          | RE2     | RE1    | RE0    | xxx                     | uuu                               |

## TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

## 15.0 ELECTRICAL CHARACTERISTICS

| Absolute Maximum Ratings † | Absolute | Maximum | Ratings † |

|----------------------------|----------|---------|-----------|

|----------------------------|----------|---------|-----------|

| Ambient temperature under bias                                                                              |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3 V to (VDD + 0.3 V)             |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5 V                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14 V                         |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +8.5 V                        |

| Total power dissipation (Note 1)                                                                            | 1.0 W                              |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into Vod pin                                                                                | 250 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| <b>2:</b> Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80   | mA <u>, may cause latch-up</u> .   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on PIC16F873/876 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

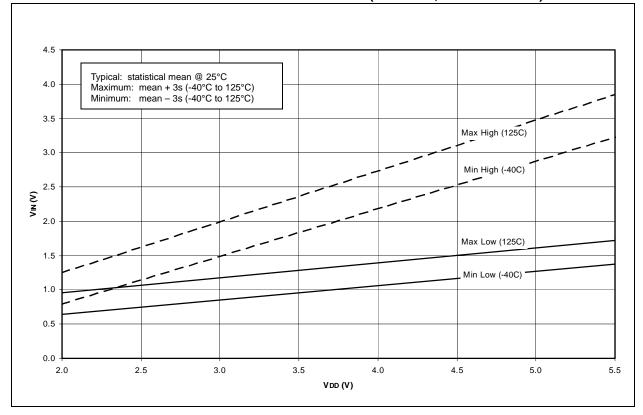

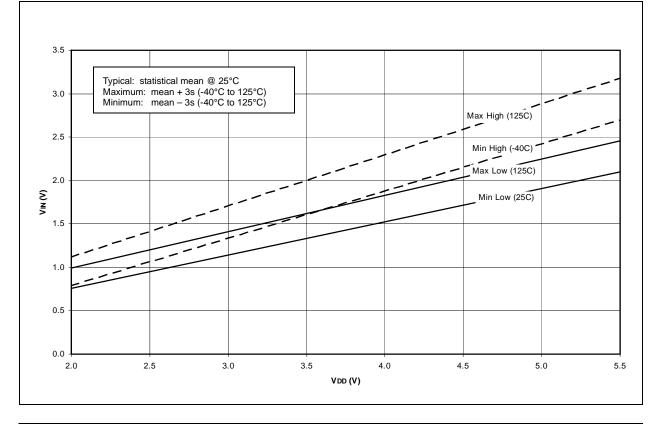

#### FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

#### 15.4 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended) (Continued)

| DC CHARACTERISTICS |       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40$ °C $\leq$ TA $\leq$ +125°C<br>Operating voltage VDD range as described in DC specification<br>(Section 15.1) |           |      |     |       |                                                                        |  |

|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-----|-------|------------------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                      | Min       | Тур† | Max | Units | Conditions                                                             |  |

|                    | Vol   | Output Low Voltage                                                                                                                                                                                  |           |      |     |       |                                                                        |  |

| D080A              |       | I/O ports                                                                                                                                                                                           | —         | —    | 0.6 | V     | IOL = 7.0 mA, VDD = 4.5V                                               |  |

| D083A              |       | OSC2/CLKOUT (RC osc config)                                                                                                                                                                         | —         | —    | 0.6 | V     | IOL = 1.2 mA, VDD = 4.5V                                               |  |

|                    | Voн   | Output High Voltage                                                                                                                                                                                 |           |      |     |       |                                                                        |  |

| D090A              |       | I/O ports <sup>(3)</sup>                                                                                                                                                                            | Vdd - 0.7 | —    | _   | V     | Юн = -2.5 mA, VDD = 4.5V                                               |  |

| D092A              |       | OSC2/CLKOUT (RC osc config)                                                                                                                                                                         | Vdd - 0.7 | —    |     | V     | Юн = -1.0 mA, VDD = 4.5V                                               |  |

| D150*              | Vod   | Open Drain High Voltage                                                                                                                                                                             | —         | —    | 8.5 | V     | RA4 pin                                                                |  |

|                    |       | Capacitive Loading Specs on Output Pins                                                                                                                                                             |           |      |     |       |                                                                        |  |

| D100               | Cosc2 | OSC2 pin                                                                                                                                                                                            | _         | —    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |  |

| D101               | Сю    | All I/O pins and OSC2 (RC mode)                                                                                                                                                                     | _         | _    | 50  | pF    |                                                                        |  |

| D102               | Св    | SCL, SDA (I <sup>2</sup> C mode)                                                                                                                                                                    | —         | —    | 400 | pF    |                                                                        |  |

|                    |       | Data EEPROM Memory                                                                                                                                                                                  |           |      |     |       |                                                                        |  |

| D120               | ED    | Endurance                                                                                                                                                                                           | 100K      | —    | _   | E/W   | 25°C at 5V                                                             |  |

| D121               | Vdrw  | VDD for read/write                                                                                                                                                                                  | Vmin      | —    | 5.5 | V     | Using EECON to read/write<br>VMIN = min. operating voltage             |  |

| D122               | TDEW  | ······                                                                                                                                                                                              | _         | 4    | 8   | ms    |                                                                        |  |

|                    |       | Program FLASH Memory                                                                                                                                                                                |           |      |     |       |                                                                        |  |

| D130               | Eр    | Endurance                                                                                                                                                                                           | 1000      | —    |     | E/W   | 25°C at 5V                                                             |  |

| D131               | Vpr   | VDD for read                                                                                                                                                                                        | VMIN      | —    | 5.5 | V     | VMIN = min operating voltage                                           |  |

| D132A              |       | VDD for erase/write                                                                                                                                                                                 | VMIN      | —    | 5.5 | V     | Using EECON to read/write,<br>VMIN = min. operating voltage            |  |

| D133               | TPEW  | Erase/Write cycle time                                                                                                                                                                              | —         | 4    | 8   | ms    |                                                                        |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

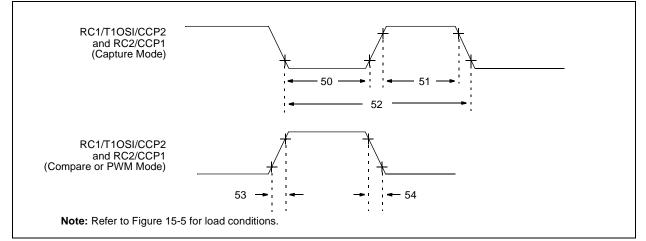

#### FIGURE 15-11: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

#### TABLE 15-5: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym             | Characteristic                 |                 |                       | Min         | Тур† | Max | Units                              | Conditions |  |

|--------------|-----------------|--------------------------------|-----------------|-----------------------|-------------|------|-----|------------------------------------|------------|--|

|              |                 | CCP1 and CCP2                  | No Prescaler    |                       | 0.5Tcy + 20 | —    | _   | ns                                 |            |  |

|              | input low       | input low time                 |                 | Standard(F)           | 10          | _    | _   | ns                                 |            |  |

|              |                 |                                | With Prescaler  | Extended(LF)          | 20          | _    | _   | ns                                 |            |  |

| 51*          |                 |                                | No Prescaler    |                       | 0.5Tcy + 20 | _    | _   | ns                                 |            |  |