Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873-04e-so |

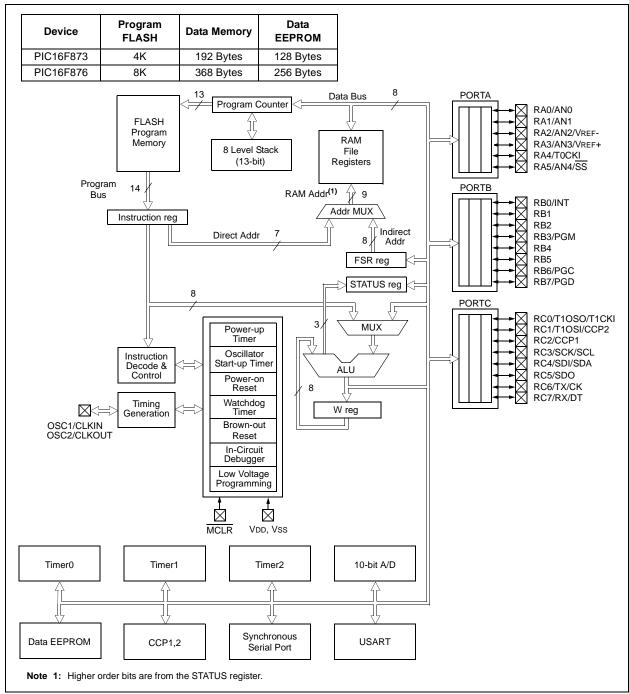

#### 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC® MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

FIGURE 1-1: PIC16F873 AND PIC16F876 BLOCK DIAGRAM

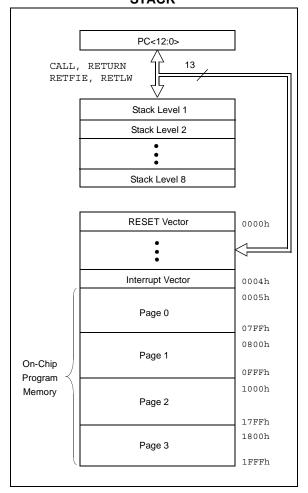

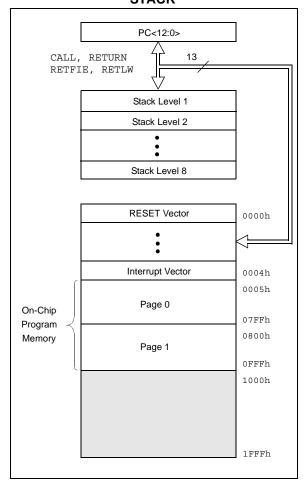

#### 2.0 MEMORY ORGANIZATION

There are three memory blocks in each of the PIC16F87X MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The EEPROM data memory block is detailed in Section 4.0.

Additional information on device memory may be found in the  $PIC^{\circledR}$  MCU Mid-Range Reference Manual, (DS33023).

FIGURE 2-1: PIC16F877/876 PROGRAM MEMORY MAP AND STACK

#### 2.1 Program Memory Organization

The PIC16F87X devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. The PIC16F877/876 devices have 8K x 14 words of FLASH program memory, and the PIC16F873/874 devices have 4K x 14. Accessing a location above the physically implemented address will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-2: PIC16F874/873 PROGRAM MEMORY MAP AND STACK

## PIC16F87X

**TABLE 2-1:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                      |            |                      |                                                                                                                                 |                            |                |               | -                 |                |          |                          |                        |

|----------------------|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|---------------|-------------------|----------------|----------|--------------------------|------------------------|

| Address              | Name       | Bit 7                | Bit 6                                                                                                                           | Bit 5                      | Bit 4          | Bit 3         | Bit 2             | Bit 1          | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

| Bank 1               |            |                      |                                                                                                                                 |                            |                |               |                   |                |          |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressin            | g this locatio                                                                                                                  | n uses conte               | ents of FSR to | address data  | a memory (no      | t a physical r | egister) | 0000 0000                | 27                     |

| 81h                  | OPTION_REG | RBPU                 | INTEDG                                                                                                                          | T0CS                       | T0SE           | PSA           | PS2               | PS1            | PS0      | 1111 1111                | 19                     |

| 82h <sup>(3)</sup>   | PCL        | Program C            | Counter (PC)                                                                                                                    | Least Signif               | icant Byte     |               |                   |                |          | 0000 0000                | 26                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | $\overline{RP}$ $\overline{RP1}$ $\overline{RP0}$ $\overline{TO}$ $\overline{PD}$ $\overline{Z}$ $\overline{DC}$ $\overline{C}$ |                            |                |               |                   |                |          | 0001 1xxx                | 18                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ata Memory /                                                                                                                    | Address Poir               | nter           |               |                   |                |          | xxxx xxxx                | 27                     |

| 85h                  | TRISA      | _                    |                                                                                                                                 | PORTA Da                   | ta Direction R | legister      |                   |                |          | 11 1111                  | 29                     |

| 86h                  | TRISB      | PORTB D              | ata Direction                                                                                                                   | Register                   |                |               |                   |                |          | 1111 1111                | 31                     |

| 87h                  | TRISC      | PORTC D              | ata Direction                                                                                                                   | Register                   |                |               |                   |                |          | 1111 1111                | 33                     |

| 88h <sup>(4)</sup>   | TRISD      | PORTD D              | ata Direction                                                                                                                   | Register                   |                |               |                   |                |          | 1111 1111                | 35                     |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF                                                                                                                             | IBOV                       | PSPMODE        | _             | PORTE Data        | Direction Bi   | ts       | 0000 -111                | 37                     |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _                    | _                                                                                                                               | _                          | Write Buffer   | for the upper | r 5 bits of the F | Program Cou    | ınter    | 0 0000                   | 26                     |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE                                                                                                                            | TOIE                       | INTE           | RBIE          | TOIF              | INTF           | RBIF     | 0000 000x                | 20                     |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE                                                                                                                            | RCIE                       | TXIE           | SSPIE         | CCP1IE            | TMR2IE         | TMR1IE   | 0000 0000                | 21                     |

| 8Dh                  | PIE2       | _                    | (5)                                                                                                                             | _                          | EEIE           | BCLIE         | _                 | _              | CCP2IE   | -r-0 00                  | 23                     |

| 8Eh                  | PCON       | _                    | _                                                                                                                               | _                          | _              | _             | _                 | POR            | BOR      | qq                       | 25                     |

| 8Fh                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 90h                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT                                                                                                                         | ACKDT                      | ACKEN          | RCEN          | PEN               | RSEN           | SEN      | 0000 0000                | 68                     |

| 92h                  | PR2        | Timer2 Pe            | riod Registe                                                                                                                    | r                          |                |               |                   |                |          | 1111 1111                | 55                     |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po                                                                                                                   | ort (I <sup>2</sup> C mode | ) Address Re   | gister        |                   |                |          | 0000 0000                | 73, 74                 |

| 94h                  | SSPSTAT    | SMP                  | CKE                                                                                                                             | D/A                        | Р              | S             | R/W               | UA             | BF       | 0000 0000                | 66                     |

| 95h                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 96h                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 97h                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 98h                  | TXSTA      | CSRC                 | TX9                                                                                                                             | TXEN                       | SYNC           | _             | BRGH              | TRMT           | TX9D     | 0000 -010                | 95                     |

| 99h                  | SPBRG      | Baud Rate            | Generator F                                                                                                                     | Register                   |                |               |                   |                |          | 0000 0000                | 97                     |

| 9Ah                  | _          | Unimplem             | Inimplemented                                                                                                                   |                            |                |               |                   |                | _        | _                        |                        |

| 9Bh                  | _          | Unimplem             | Jnimplemented —                                                                                                                 |                            |                |               |                   | _              | _        |                          |                        |

| 9Ch                  | _          | Unimplem             | ented                                                                                                                           |                            |                |               |                   |                |          | _                        | _                      |

| 9Dh                  | _          | Unimplem             | Inimplemented —                                                                                                                 |                            |                |               |                   | _              |          |                          |                        |

| 9Eh                  | ADRESL     | A/D Resul            | t Register Lo                                                                                                                   | w Byte                     |                |               |                   |                |          | xxxx xxxx                | 116                    |

| 9Fh                  | ADCON1     | ADFM                 | _                                                                                                                               | _                          | _              | PCFG3         | PCFG2             | PCFG1          | PCFG0    | 0 0000                   | 112                    |

|                      |            |                      |                                                                                                                                 |                            |                |               |                   |                |          |                          |                        |

- Legend: x = unknown, u = unchanged, q = value depends on condition, = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

Note: The <u>C</u> and <u>DC</u> bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the <u>SUBLW</u> and <u>SUBWF</u> instructions for examples.

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7 |       |       |     |     |       |       | bit 0 |

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h - 1FFh)

0 = Bank 0, 1 (00h - FFh)

bit 6-5 RP1:RP0: Register Bank Select bits (used for direct addressing)

11 = Bank 3 (180h - 1FFh)

10 = Bank 2 (100h - 17Fh)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

Each bank is 128 bytes

bit 4 **TO**: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

bit 3 **PD**: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

(for borrow, the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

**Note:** For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is

loaded with either the high, or low order bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7  | Bit 6      | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other RESETS |

|-----------------------|------------|--------|------------|---------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | Module's F | Registe | -     |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE    | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | T0CS    | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 6.0 TIMER1 MODULE

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L), which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- · As a timer

- · As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In Timer mode, Timer1 increments every instruction cycle. In Counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "RESET input". This RESET can be generated by either of the two CCP modules (Section 8.0). Register 6-1 shows the Timer1 control register.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored, and these pins read as '0'.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|---------|---------|---------|--------|--------|--------|

| _     | _   | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |     |         |         |         |        |        | bit 0  |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits

11 = 1:8 Prescale value

10 = 1:4 Prescale value

01 = 1:2 Prescale value

00 = 1:1 Prescale value

bit 3 T10SCEN: Timer1 Oscillator Enable Control bit

1 = Oscillator is enabled

0 = Oscillator is shut-off (the oscillator inverter is turned off to eliminate power drain)

bit 2 T1SYNC: Timer1 External Clock Input Synchronization Control bit

When TMR1CS = 1:

1 = Do not synchronize external clock input

0 = Synchronize external clock input

When TMR1CS = 0:

This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0.

bit 1 TMR1CS: Timer1 Clock Source Select bit

1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge)

0 = Internal clock (Fosc/4)

bit 0 TMR10N: Timer1 On bit

1 = Enables Timer1

0 = Stops Timer1

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

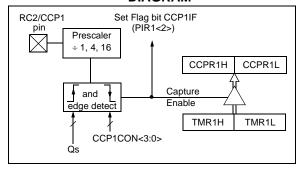

#### 8.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as one of the following:

- · Every falling edge

- · Every rising edge

- · Every 4th rising edge

- · Every 16th rising edge

The type of event is configured by control bits CCP1M3:CCP1M0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. The interrupt flag must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new value.

#### 8.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 pin is configured as an output, a write to the port can cause a capture condition.

## FIGURE 8-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 8.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 8.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF, following any such change in operating mode.

#### 8.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 8-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 8-1: CHANGING BETWEEN CAPTURE PRESCALERS

```

CLRF CCP1CON ; Turn CCP module off

MOVLW NEW_CAPT_PS ; Load the W reg with

; the new prescaler

; move value and CCP ON

MOVWF CCP1CON ; Load CCP1CON with this

; value

```

#### 9.2.15 CLOCK ARBITRATION

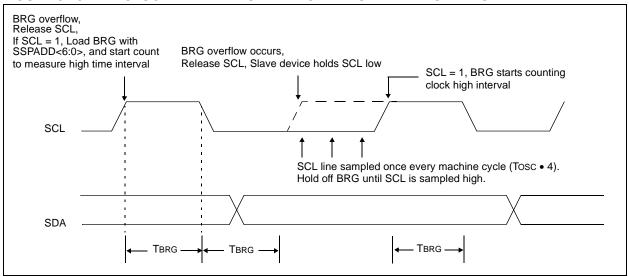

Clock arbitration occurs when the master, during any receive, transmit, or Repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 9-18).

#### 9.2.16 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

#### 9.2.17 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

#### FIGURE 9-18: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

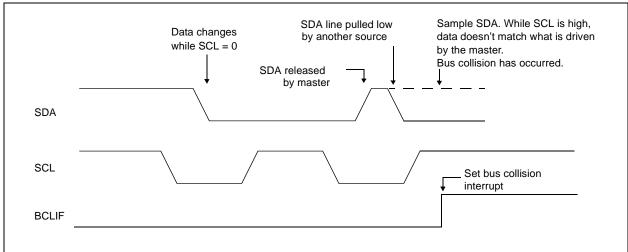

# 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $\rm I^2C$  port to its IDLE state (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $\rm I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the I<sup>2</sup>C bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

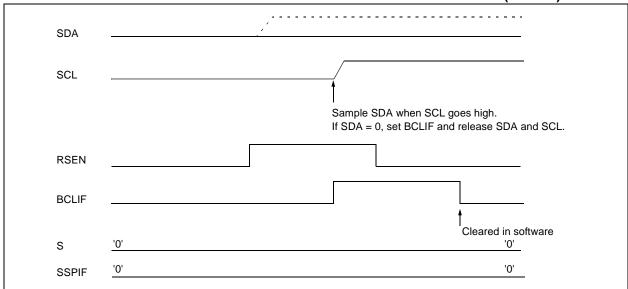

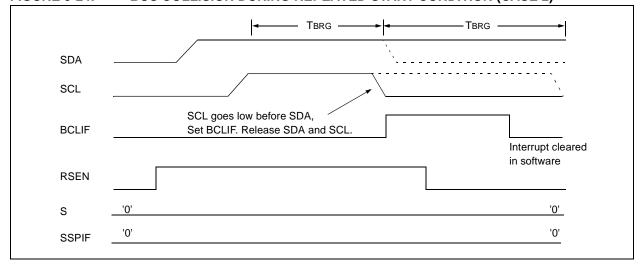

## 9.2.18.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data'0'). If, however,

SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data'1' during the Repeated START condition.

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete (Figure 9-23).

FIGURE 9-24: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| DALID       | %       |      | F                       | osc = 16 N | lHz                       | F   | Fosc = 10 MHz |            |                             |

|-------------|---------|------|-------------------------|------------|---------------------------|-----|---------------|------------|-----------------------------|

| RATE<br>(K) |         |      | E SPBRG SPBRG Value KBA |            | % value KBAUD ERROR value |     | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -    | -                       | -          | -                         | -   | -             | -          | -                           |

| 1.2         | 1.221   | 1.75 | 255                     | 1.202      | 0.17                      | 207 | 1.202         | 0.17       | 129                         |

| 2.4         | 2.404   | 0.17 | 129                     | 2.404      | 0.17                      | 103 | 2.404         | 0.17       | 64                          |

| 9.6         | 9.766   | 1.73 | 31                      | 9.615      | 0.16                      | 25  | 9.766         | 1.73       | 15                          |

| 19.2        | 19.531  | 1.72 | 15                      | 19.231     | 0.16                      | 12  | 19.531        | 1.72       | 7                           |

| 28.8        | 31.250  | 8.51 | 9                       | 27.778     | 3.55                      | 8   | 31.250        | 8.51       | 4                           |

| 33.6        | 34.722  | 3.34 | 8                       | 35.714     | 6.29                      | 6   | 31.250        | 6.99       | 4                           |

| 57.6        | 62.500  | 8.51 | 4                       | 62.500     | 8.51                      | 3   | 52.083        | 9.58       | 2                           |

| HIGH        | 1.221   | -    | 255                     | 0.977      | -                         | 255 | 0.610         | -          | 255                         |

| LOW         | 312.500 | -    | 0                       | 250.000    | -                         | 0   | 156.250       | -          | 0                           |

| DALID               |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |  |

|---------------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |  |

| 1.2                 | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |  |

| 2.4                 | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |  |

| 9.6                 | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |  |

| 19.2                | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |  |

| 28.8                | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |  |

| 33.6                | -      | -          | -                           | -                 | -          | -                           |  |  |

| 57.6                | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |  |

| HIGH                | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |  |

| LOW                 | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |  |

#### TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | F        | Fosc = 20 MHz |                             |          | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |

|-------------|----------|---------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR    | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -        | -             | -                           | -        | -          | -                           | -             | -          | -                           |

| 1.2         | -        | -             | -                           | -        | -          | -                           | -             | -          | -                           |

| 2.4         | -        | -             | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |

| 9.6         | 9.615    | 0.16          | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |

| 19.2        | 19.231   | 0.16          | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |

| 28.8        | 29.070   | 0.94          | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |

| 33.6        | 33.784   | 0.55          | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |

| 57.6        | 59.524   | 3.34          | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |

| HIGH        | 4.883    | -             | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |

| LOW         | 1250.000 | -             | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |

| BAUD        | F       | osc = 4 MH | łz                          | Fos   | c = 3.6864 | MHz                         |  |

|-------------|---------|------------|-----------------------------|-------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -          | -                           | -     | -          | -                           |  |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2   | 0          | 191                         |  |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4   | 0          | 95                          |  |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6   | 0          | 23                          |  |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2  | 0          | 11                          |  |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8  | 0          | 7                           |  |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9  | 2.04       | 6                           |  |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6  | 0          | 3                           |  |

| HIGH        | 0.977   | -          | 255                         | 0.9   | -          | 255                         |  |

| LOW         | 250.000 | -          | 0                           | 230.4 | -          | 0                           |  |

#### 11.4 A/D Conversions

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D result register pair will NOT be updated with the partially completed A/D conversion sample. That is, the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers). After the A/D conversion is aborted, a 2TAD wait is required before the next

acquisition is started. After this 2TAD wait, acquisition on the selected channel is automatically started. The GO/DONE bit can then be set to start the conversion.

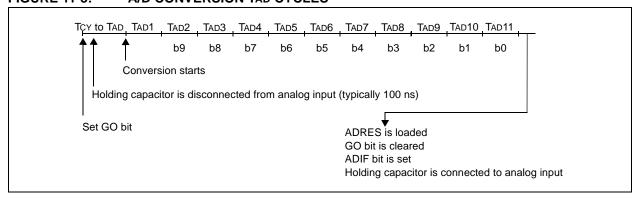

In Figure 11-3, after the GO bit is set, the first time segment has a minimum of TCY and a maximum of TAD.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

FIGURE 11-3: A/D CONVERSION TAD CYCLES

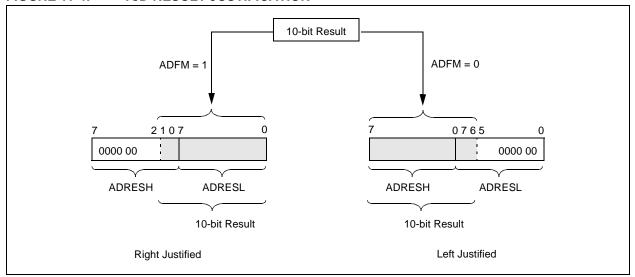

#### 11.4.1 A/D RESULT REGISTERS

The ADRESH:ADRESL register pair is the location where the 10-bit A/D result is loaded at the completion of the A/D conversion. This register pair is 16-bits wide. The A/D module gives the flexibility to left or right justify the 10-bit result in the 16-bit result register. The A/D

Format Select bit (ADFM) controls this justification. Figure 11-4 shows the operation of the A/D result justification. The extra bits are loaded with '0's'. When an A/D result will not overwrite these locations (A/D disable), these registers may be used as two general purpose 8-bit registers.

FIGURE 11-4: A/D RESULT JUSTIFICATION

#### 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  ${\tt SLEEP}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on  $\overline{\text{MCLR}}$  pin.

- Watchdog Timer Wake-up (if WDT was enabled).

- Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### PIC16F87X

TABLE 13-2: PIC16F87X INSTRUCTION SET

| Mnem   | Mnemonic, Description                  |                              | Cycles  |        | 14-Bit ( | Opcode | )    | Status   | Notes |  |

|--------|----------------------------------------|------------------------------|---------|--------|----------|--------|------|----------|-------|--|

| Opera  | ands                                   | Description                  | Cycles  | MSb    |          |        | LSb  | Affected | Notes |  |

|        | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |         |        |          |        |      |          |       |  |

| ADDWF  | f, d                                   | Add W and f                  | 1       | 00     | 0111     | dfff   | ffff | C,DC,Z   | 1,2   |  |

| ANDWF  | f, d                                   | AND W with f                 | 1       | 00     | 0101     | dfff   | ffff | Z        | 1,2   |  |

| CLRF   | f                                      | Clear f                      | 1       | 0.0    | 0001     | lfff   | ffff | Z        | 2     |  |

| CLRW   | -                                      | Clear W                      | 1       | 00     | 0001     | 0xxx   | xxxx | Z        |       |  |

| COMF   | f, d                                   | Complement f                 | 1       | 0.0    | 1001     | dfff   | ffff | Z        | 1,2   |  |

| DECF   | f, d                                   | Decrement f                  | 1       | 00     | 0011     | dfff   | ffff | Z        | 1,2   |  |

| DECFSZ | f, d                                   | Decrement f, Skip if 0       | 1(2)    | 00     | 1011     | dfff   | ffff |          | 1,2,3 |  |

| INCF   | f, d                                   | Increment f                  | 1       | 00     | 1010     | dfff   | ffff | Z        | 1,2   |  |

| INCFSZ | f, d                                   | Increment f, Skip if 0       | 1(2)    | 00     | 1111     | dfff   | ffff |          | 1,2,3 |  |

| IORWF  | f, d                                   | Inclusive OR W with f        | 1       | 00     | 0100     | dfff   | ffff | Z        | 1,2   |  |

| MOVF   | f, d                                   | Move f                       | 1       | 00     | 1000     | dfff   | ffff | Z        | 1,2   |  |

| MOVWF  | f                                      | Move W to f                  | 1       | 00     | 0000     | lfff   | ffff |          |       |  |

| NOP    | -                                      | No Operation                 | 1       | 0.0    | 0000     | 0xx0   | 0000 |          |       |  |

| RLF    | f, d                                   | Rotate Left f through Carry  | 1       | 0.0    | 1101     | dfff   | ffff | С        | 1,2   |  |

| RRF    | f, d                                   | Rotate Right f through Carry | 1       | 0.0    | 1100     | dfff   | ffff | С        | 1,2   |  |

| SUBWF  | f, d                                   | Subtract W from f            | 1       | 00     | 0010     | dfff   | ffff | C,DC,Z   | 1,2   |  |

| SWAPF  | f, d                                   | Swap nibbles in f            | 1       | 0.0    | 1110     | dfff   | ffff | -, -,    | 1,2   |  |

| XORWF  | f, d                                   | Exclusive OR W with f        | 1       | 00     | 0110     | dfff   | ffff | Z        | 1,2   |  |

|        |                                        | BIT-ORIENTED FILE REGIST     | ER OPER | RATION | NS       |        |      |          |       |  |

| BCF    | f, b                                   | Bit Clear f                  | 1       | 01     | 00bb     | bfff   | ffff |          | 1,2   |  |

| BSF    | f, b                                   | Bit Set f                    | 1       | 01     | 01bb     | bfff   | ffff |          | 1,2   |  |

| BTFSC  | f, b                                   | Bit Test f, Skip if Clear    | 1 (2)   | 01     | 10bb     | bfff   | ffff |          | 3     |  |

| BTFSS  | f, b                                   | Bit Test f, Skip if Set      | 1 (2)   | 01     | 11bb     | bfff   | ffff |          | 3     |  |

|        |                                        | LITERAL AND CONTROL          | OPERATI | ONS    |          |        |      |          |       |  |

| ADDLW  | k                                      | Add literal and W            | 1       | 11     | 111x     | kkkk   | kkkk | C,DC,Z   |       |  |

| ANDLW  | k                                      | AND literal with W           | 1       | 11     | 1001     | kkkk   | kkkk | Z        |       |  |

| CALL   | k                                      | Call subroutine              | 2       | 10     | 0kkk     | kkkk   | kkkk |          |       |  |

| CLRWDT | -                                      | Clear Watchdog Timer         | 1       | 00     | 0000     | 0110   | 0100 | TO,PD    |       |  |

| GOTO   | k                                      | Go to address                | 2       | 10     | 1kkk     | kkkk   | kkkk |          |       |  |

| IORLW  | k                                      | Inclusive OR literal with W  | 1       | 11     | 1000     | kkkk   | kkkk | Z        |       |  |

| MOVLW  | k                                      | Move literal to W            | 1       | 11     | 00xx     | kkkk   | kkkk |          |       |  |

| RETFIE | -                                      | Return from interrupt        | 2       | 0.0    | 0000     | 0000   | 1001 |          |       |  |

| RETLW  | k                                      | Return with literal in W     | 2       | 11     | 01xx     | kkkk   | kkkk |          |       |  |

| RETURN | -                                      | Return from Subroutine       | 2       | 0.0    | 0000     | 0000   | 1000 |          |       |  |

| SLEEP  | -                                      | Go into standby mode         | 1       | 0.0    | 0000     | 0110   | 0011 | TO,PD    |       |  |

| SUBLW  | k                                      | Subtract W from literal      | 1       | 11     | 110x     | kkkk   | kkkk | C,DC,Z   |       |  |

| XORLW  | k                                      | Exclusive OR literal with W  | 1       | 11     | 1010     | kkkk   | kkkk | Z        |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

<sup>2:</sup> If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

<sup>3:</sup> If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2Tcy instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] INCFSZ f,d                                                                                                                                                                                                                                                                           |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                                                                                                           |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead, making it a 2Tcy instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                              |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] GOTO k                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORLW k                                                                                                |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                              |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the eight bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| Syntax:          | [ label ] INCF f,d                                                                                                                                         |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                          |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

Increment f

**INCF**

| IORWF            | Inclusive OR W with f                                                                                                                                     |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                        |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. |  |  |  |  |  |

#### 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- · Integrated Development Environment

- MPLAB® IDE Software

- · Assemblers/Compilers/Linkers

- MPASM™ Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK™ Object Linker/ MPLIB™ Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- · In-Circuit Debugger

- MPLAB ICD for PIC16F87X

- · Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART® Plus Entry-Level Development Programmer

- · Low Cost Demonstration Boards

- PICDEM™ 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ® Demonstration Board

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows®-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- · A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- · On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

#### 14.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC® MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- · Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process.

## 14.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

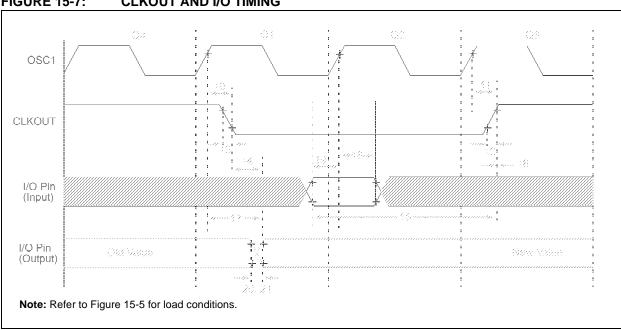

**FIGURE 15-7: CLKOUT AND I/O TIMING**

TABLE 15-2: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Symbol       | Charac                                        | teristic               | Min        | Тур† | Max         | Units | Conditions |

|--------------|--------------|-----------------------------------------------|------------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL     | OSC1↑ to CLKOUT↓                              |                        | _          | 75   | 200         | ns    | (Note 1)   |

| 11*          | TosH2ck<br>H | OSC1↑ to CLKOUT↑                              |                        | _          | 75   | 200         | ns    | (Note 1)   |

| 12*          | TckR         | CLKOUT rise time                              |                        | _          | 35   | 100         | ns    | (Note 1)   |

| 13*          | TckF         | CLKOUT fall time                              |                        | _          | 35   | 100         | ns    | (Note 1)   |

| 14*          | TckL2ioV     | CLKOUT ↓ to Port out val                      | id                     | _          | _    | 0.5Tcy + 20 | ns    | (Note 1)   |

| 15*          | TioV2ckH     | Port in valid before CLKOUT ↑                 |                        | Tosc + 200 | _    | _           | ns    | (Note 1)   |

| 16*          | TckH2iol     | Port in hold after CLKOUT ↑                   |                        | 0          | _    | _           | ns    | (Note 1)   |

| 17*          | TosH2ioV     | OSC1↑ (Q1 cycle) to<br>Port out valid         |                        | _          | 100  | 255         | ns    |            |

| 18*          | TosH2iol     | OSC1↑ (Q2 cycle) to                           | Standard (F)           | 100        | _    | _           | ns    |            |

|              |              | Port input invalid (I/O in hold time)         | Extended ( <b>LF</b> ) | 200        | _    | _           | ns    |            |

| 19*          | TioV2osH     | Port input valid to OSC1↑ (I/O in setup time) |                        | 0          | _    | _           | ns    |            |

| 20*          | TioR         | Port output rise time                         | Standard (F)           | _          | 10   | 40          | ns    |            |

|              |              |                                               | Extended (LF)          | _          | _    | 145         | ns    |            |

| 21*          | TioF         | Port output fall time                         | Standard (F)           | _          | 10   | 40          | ns    |            |

|              |              |                                               | Extended (LF)          | _          | _    | 145         | ns    |            |

| 22††*        | Tinp         | INT pin high or low time                      |                        | Tcy        | _    | _           | ns    |            |

| 23††*        | Trbp         | RB7:RB4 change INT high or low time           |                        | Tcy        | _    | _           | ns    |            |

These parameters are characterized but not tested.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

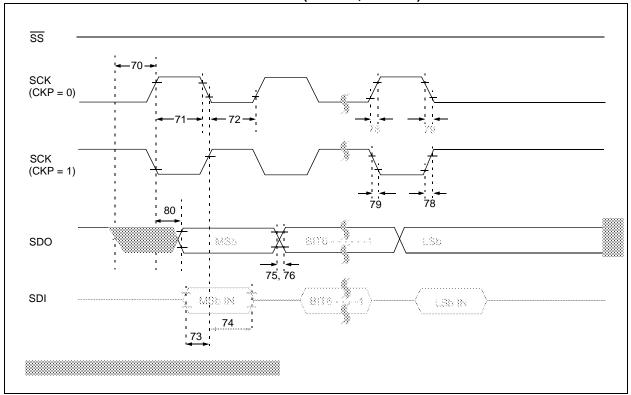

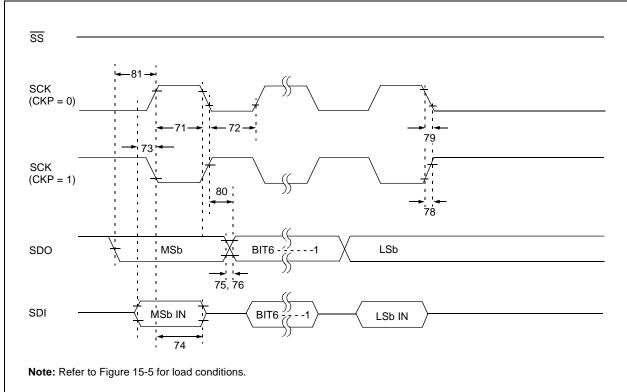

FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

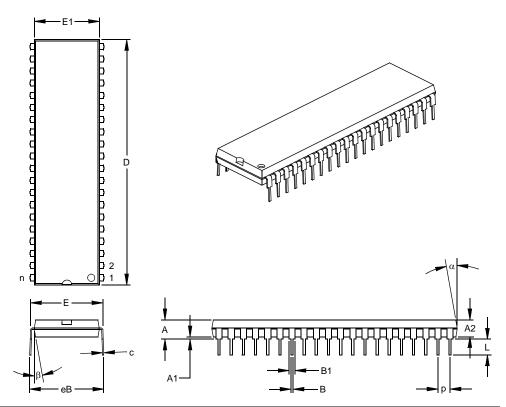

#### 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |  |

|----------------------------|-------|---------|-------|-------|-------------|-------|-------|--|

| Dimension                  | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |       |  |

| Number of Pins             | n     |         | 40    |       |             | 40    |       |  |

| Pitch                      | р     |         | .100  |       |             | 2.54  |       |  |

| Top to Seating Plane       | Α     | .160    | .175  | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2    | .140    | .150  | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1    | .015    |       |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | Е     | .595    | .600  | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1    | .530    | .545  | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D     | 2.045   | 2.058 | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L     | .120    | .130  | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С     | .008    | .012  | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1    | .030    | .050  | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В     | .014    | .018  | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eВ    | .620    | .650  | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α     | 5       | 10    | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β     | 5       | 10    | 15    | 5           | 10    | 15    |  |

<sup>\*</sup> Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

<sup>§</sup> Significant Characteristic

## PIC16F87X

**NOTES:**