Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873-10e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16F87X

**TABLE 2-1:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                      |            |                      |                 |                            |                |               | -                 |              |        |                          |                        |  |  |

|----------------------|------------|----------------------|-----------------|----------------------------|----------------|---------------|-------------------|--------------|--------|--------------------------|------------------------|--|--|

| Address              | Name       | Bit 7                | Bit 6           | Bit 5                      | Bit 4          | Bit 3         | Bit 2             | Bit 1        | Bit 0  | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |  |  |

| Bank 1               |            |                      |                 |                            |                |               |                   |              |        |                          |                        |  |  |

| 80h <sup>(3)</sup>   | INDF       | Addressin            | g this locatio  | egister)                   | 0000 0000      | 27            |                   |              |        |                          |                        |  |  |

| 81h                  | OPTION_REG | RBPU                 | INTEDG          | T0CS                       | T0SE           | PSA           | PS2               | PS1          | PS0    | 1111 1111                | 19                     |  |  |

| 82h <sup>(3)</sup>   | PCL        | Program C            | Counter (PC)    | Least Signif               | icant Byte     |               |                   |              |        | 0000 0000                | 26                     |  |  |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1             | RP0                        | TO             | PD            | Z                 | DC           | С      | 0001 1xxx                | 18                     |  |  |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | ata Memory /    | Address Poir               | nter           |               |                   |              |        | xxxx xxxx                | 27                     |  |  |

| 85h                  | TRISA      | _                    |                 | PORTA Da                   | ta Direction R | legister      |                   |              |        | 11 1111                  | 29                     |  |  |

| 86h                  | TRISB      | PORTB D              | ata Direction   | Register                   |                |               |                   |              |        | 1111 1111                | 31                     |  |  |

| 87h                  | TRISC      | PORTC D              | ata Direction   | Register                   |                |               |                   |              |        | 1111 1111                | 33                     |  |  |

| 88h <sup>(4)</sup>   | TRISD      | PORTD D              | ata Direction   | Register                   |                |               |                   |              |        | 1111 1111                | 35                     |  |  |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF             | IBOV                       | PSPMODE        | _             | PORTE Data        | Direction Bi | ts     | 0000 -111                | 37                     |  |  |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _                    | _               | _                          | Write Buffer   | for the upper | r 5 bits of the F | Program Cou  | ınter  | 0 0000                   | 26                     |  |  |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE            | TOIE                       | INTE           | RBIE          | TOIF              | INTF         | RBIF   | 0000 000x                | 20                     |  |  |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE            | RCIE                       | TXIE           | SSPIE         | CCP1IE            | TMR2IE       | TMR1IE | 0000 0000                | 21                     |  |  |

| 8Dh                  | PIE2       | _                    | (5)             | _                          | EEIE           | BCLIE         | _                 | _            | CCP2IE | -r-0 00                  | 23                     |  |  |

| 8Eh                  | PCON       | _                    | _               | _                          | _              | _             | _                 | POR          | BOR    | qq                       | 25                     |  |  |

| 8Fh                  | _          | Unimplem             | ented           |                            |                |               |                   |              |        | _                        | _                      |  |  |

| 90h                  | _          | Unimplem             | ented           |                            |                |               |                   |              |        | _                        | _                      |  |  |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT         | ACKDT                      | ACKEN          | RCEN          | PEN               | RSEN         | SEN    | 0000 0000                | 68                     |  |  |

| 92h                  | PR2        | Timer2 Pe            | riod Registe    | r                          |                |               |                   |              |        | 1111 1111                | 55                     |  |  |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po   | ort (I <sup>2</sup> C mode | ) Address Re   | gister        |                   |              |        | 0000 0000                | 73, 74                 |  |  |

| 94h                  | SSPSTAT    | SMP                  | CKE             | D/A                        | Р              | S             | R/W               | UA           | BF     | 0000 0000                | 66                     |  |  |

| 95h                  | _          | Unimplem             | ented           |                            |                |               |                   |              |        | _                        | _                      |  |  |

| 96h                  | _          | Unimplem             | ented           |                            |                |               |                   |              |        | _                        | _                      |  |  |

| 97h                  | _          | Unimplem             | ented           |                            |                |               |                   |              |        | _                        | _                      |  |  |

| 98h                  | TXSTA      | CSRC                 | TX9             | TXEN                       | SYNC           | _             | BRGH              | TRMT         | TX9D   | 0000 -010                | 95                     |  |  |

| 99h                  | SPBRG      | Baud Rate            | Generator F     | Register                   |                |               |                   |              |        | 0000 0000                | 97                     |  |  |

| 9Ah                  | _          | Unimplem             | Unimplemented   |                            |                |               |                   |              |        |                          | _                      |  |  |

| 9Bh                  | _          | Unimplem             | ented           |                            | _              | _             |                   |              |        |                          |                        |  |  |

| 9Ch                  | _          | Unimplem             | Jnimplemented   |                            |                |               |                   |              |        |                          |                        |  |  |

| 9Dh                  | _          | Unimplem             | Inimplemented — |                            |                |               |                   |              |        |                          |                        |  |  |

| 9Eh                  | ADRESL     | A/D Resul            | t Register Lo   | w Byte                     |                |               |                   |              |        | xxxx xxxx                | 116                    |  |  |

| 9Fh                  | ADCON1     | ADFM                 | _               | _                          | _              | PCFG3         | PCFG2             | PCFG1        | PCFG0  | 0 0000                   | 112                    |  |  |

|                      |            |                      |                 |                            |                |               |                   |              |        |                          |                        |  |  |

- Legend: x = unknown, u = unchanged, q = value depends on condition, = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

### 2.2.2.6 PIE2 Register

The PIE2 register contains the individual enable bits for the CCP2 peripheral interrupt, the SSP bus collision interrupt, and the EEPROM write operation interrupt.

### REGISTER 2-6: PIE2 REGISTER (ADDRESS 8Dh)

| U-0   | R/W-0    | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|----------|-----|-------|-------|-----|-----|--------|

| _     | Reserved | _   | EEIE  | BCLIE | _   | _   | CCP2IE |

| bit 7 |          |     |       |       |     |     | bit 0  |

bit 7 Unimplemented: Read as '0'

bit 6 Reserved: Always maintain this bit clear

bit 5 Unimplemented: Read as '0'

bit 4 **EEIE**: EEPROM Write Operation Interrupt Enable

1 = Enable EE Write Interrupt0 = Disable EE Write Interrupt

bit 3 BCLIE: Bus Collision Interrupt Enable

1 = Enable Bus Collision Interrupt

0 = Disable Bus Collision Interrupt

bit 2-1 Unimplemented: Read as '0'

bit 0 CCP2IE: CCP2 Interrupt Enable bit

1 = Enables the CCP2 interrupt

0 = Disables the CCP2 interrupt

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

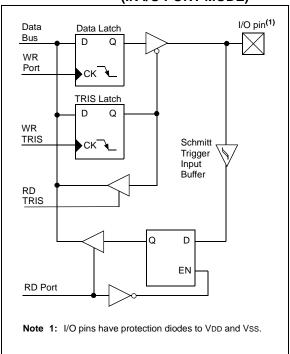

## FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

TABLE 3-9: PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                                    |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:         RD         1 = Idle         0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected)     </li> </ul> |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:</li> <li>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul>  |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:  CS  1 = Device is not selected  0 = Device is selected                                                                                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | _     |       | _     | _       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE I | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | _     | _     | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

## REGISTER 3-1: TRISE REGISTER (ADDRESS 89h)

| R-0   | R-0 | R/W-0 | R/W-0   | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV  | PSPMODE | _   | Bit2  | Bit1  | Bit0  |

| bit 7 |     |       |         |     |       |       | bit 0 |

#### Parallel Slave Port Status/Control Bits:

bit 7 IBF: Input Buffer Full Status bit

1 = A word has been received and is waiting to be read by the CPU

0 = No word has been received

bit 6 **OBF**: Output Buffer Full Status bit

1 = The output buffer still holds a previously written word

0 = The output buffer has been read

bit 5 IBOV: Input Buffer Overflow Detect bit (in Microprocessor mode)

1 = A write occurred when a previously input word has not been read (must be cleared in software)

0 = No overflow occurred

bit 4 **PSPMODE**: Parallel Slave Port Mode Select bit

1 = PORTD functions in Parallel Slave Port mode

0 = PORTD functions in general purpose I/O mode

bit 3 Unimplemented: Read as '0'

**PORTE Data Direction Bits:**

bit 2 Bit2: Direction Control bit for pin RE2/CS/AN7

1 = Input

0 = Output

bit 1 Bit1: Direction Control bit for pin RE1/WR/AN6

1 = Input

0 = Output

bit 0 Bit0: Direction Control bit for pin RE0/RD/AN5

1 = Input

0 = Output

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# PIC16F87X

NOTES:

## **PIC16F87X**

TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4    | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|----------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE     | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF     | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE     | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ive Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP      | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р        | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

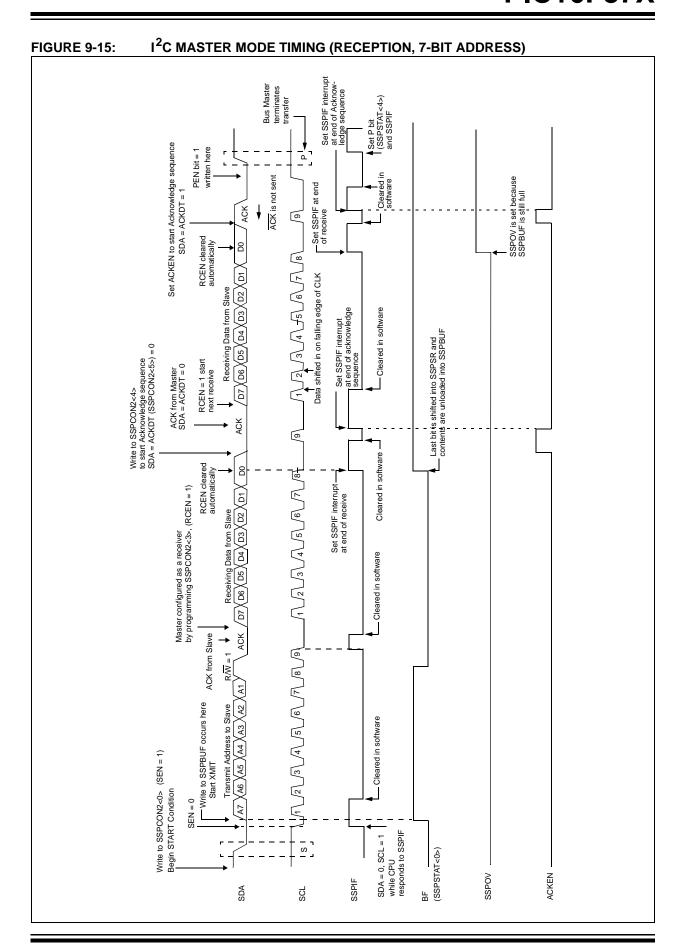

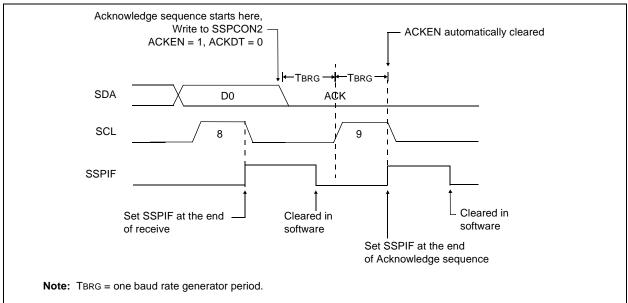

## 9.2.13 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted high. When the SCL pin is sampled high (clock arbitration), the baud

rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode (Figure 9-16).

## 9.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

FIGURE 9-16: ACKNOWLEDGE SEQUENCE WAVEFORM

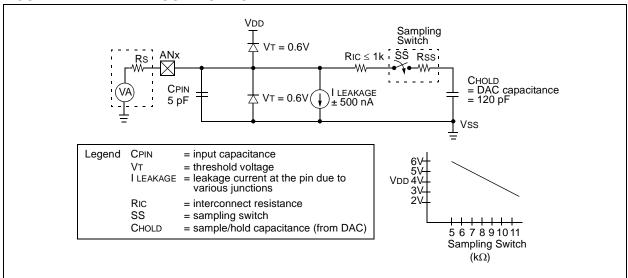

## 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (RsS) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (RsS) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is  $10~\mathrm{k}\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC® MCU Mid-Range Reference Manual (DS33023).

#### **EQUATION 11-1: ACQUISITION TIME**

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

#### 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

## 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

#### 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

## 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

# 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Power            | -up       | Brown-out        | Wake-up from |  |

|--------------------------|------------------|-----------|------------------|--------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |  |

| RC                       | 72 ms —          |           | 72 ms            | _            |  |

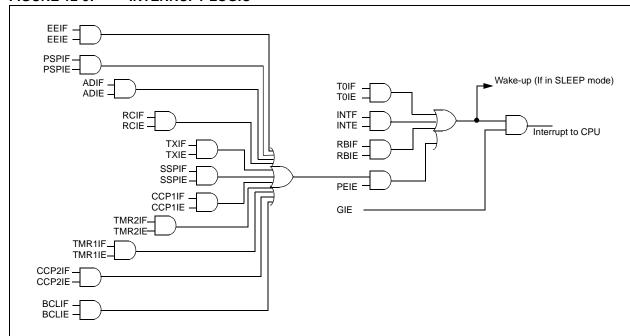

#### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

**Note:** Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

FIGURE 12-9: INTERRUPT LOGIC

The following table shows which devices have which interrupts.

| Device        | TOIF | INTF | RBIF | PSPIF | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | EEIF | BCLIF | CCP2IF |

|---------------|------|------|------|-------|------|------|------|-------|--------|--------|--------|------|-------|--------|

| PIC16F876/873 | Yes  | Yes  | Yes  |       | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes  | Yes   | Yes    |

| PIC16F877/874 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes  | Yes   | Yes    |

## 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

## 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- **2:** While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- **4:** RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- 5: LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

### 15.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                | 55 to +125°C           |

|---------------------------------------------------------------|------------------------|

| Storage temperature                                           | 65°C to +150°C         |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and |                        |

| Voltage on VDD with respect to Vss                            | 0.3 to +7.5 V          |

| Voltage on MCLR with respect to Vss (Note 2)                  | 0 to +14 V             |

| Voltage on RA4 with respect to Vss                            | 0 to +8.5 V            |

| Total power dissipation (Note 1)                              | 1.0 W                  |

| Maximum current out of Vss pin                                | 300 mA                 |

| Maximum current into VDD pin                                  | 250 mA                 |

| Input clamp current, lik (VI < 0 or VI > VDD)                 | ± 20 mA                |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                | ± 20 mA                |

| Maximum output current sunk by any I/O pin                    | 25 mA                  |

| Maximum output current sourced by any I/O pin                 | 25 mA                  |

| Maximum current sunk by PORTA, PORTB, and PORTE (comb         | ined) (Note 3)200 mA   |

| Maximum current sourced by PORTA, PORTB, and PORTE (co        | mbined) (Note 3)200 mA |

| Maximum current sunk by PORTC and PORTD (combined) (No        | te 3)200 mA            |

| Maximum current sourced by PORTC and PORTD (combined)         | (Note 3)200 mA         |

|                                                               |                        |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $\Sigma$  IOH} +  $\Sigma$  {(VDD VOH) x IOH} +  $\Sigma$ (VOI x IOL)

- 2: Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

- **3:** PORTD and PORTE are not implemented on PIC16F873/876 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

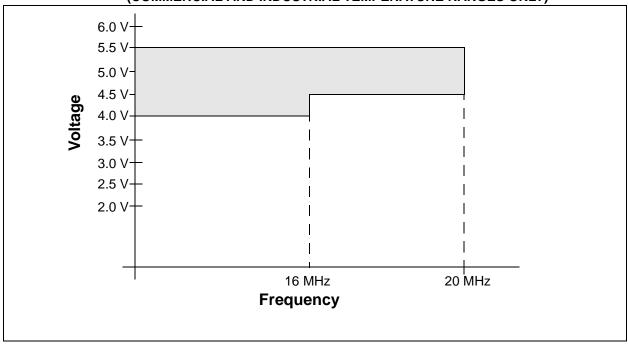

FIGURE 15-1: PIC16F87X-20 VOLTAGE-FREQUENCY GRAPH (COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES ONLY)

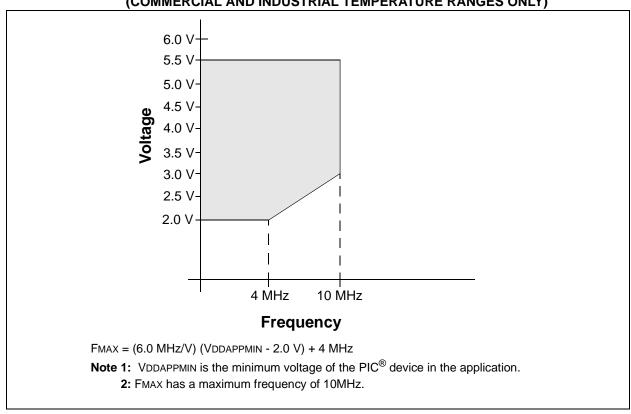

FIGURE 15-2: PIC16LF87X-04 VOLTAGE-FREQUENCY GRAPH (COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES ONLY)

15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial)

PIC16F873/874/876/877-20 (Commercial, Industrial)

**PIC16LF873/874/876/877-04 (Commercial, Industrial)**

| PIC16LF8<br>(Comme             | <b>73/874/87</b><br>ercial, Indu | <b>.,</b>                                                        |      | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \leq \text{Ta} \leq +70^{\circ}\text{C}$ for commercial |      |       |                                            |  |  |  |  |

|--------------------------------|----------------------------------|------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|--|--|--|

| PIC16F87<br>PIC16F87<br>(Comme |                                  | /877-20                                                          |      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial      |      |       |                                            |  |  |  |  |

| Param<br>No.                   | Symbol                           | Characteristic/<br>Device                                        | Min  | Тур†                                                                                                                                                                                                                                   | Max  | Units | Conditions                                 |  |  |  |  |

|                                | Vdd                              | Supply Voltage                                                   |      |                                                                                                                                                                                                                                        |      |       |                                            |  |  |  |  |

| D001                           |                                  | 16LF87X                                                          | 2.0  | _                                                                                                                                                                                                                                      | 5.5  | V     | LP, XT, RC osc configuration (DC to 4 MHz) |  |  |  |  |

| D001                           |                                  | 16F87X                                                           | 4.0  | _                                                                                                                                                                                                                                      | 5.5  | V     | LP, XT, RC osc configuration               |  |  |  |  |

| D001A                          |                                  |                                                                  | 4.5  |                                                                                                                                                                                                                                        | 5.5  | V     | HS osc configuration                       |  |  |  |  |

|                                |                                  |                                                                  | VBOR |                                                                                                                                                                                                                                        | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>  |  |  |  |  |

| D002                           | VDR                              | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | _    | 1.5                                                                                                                                                                                                                                    | _    | V     |                                            |  |  |  |  |

| D003                           | VPOR                             | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _    | Vss                                                                                                                                                                                                                                    | _    | V     | See section on Power-on Reset for details  |  |  |  |  |

| D004                           | SVDD                             | <b>VDD Rise Rate</b> to ensure internal Power-on Reset signal    | 0.05 | _                                                                                                                                                                                                                                      | _    | V/ms  | See section on Power-on Reset for details  |  |  |  |  |

| D005                           | VBOR                             | Brown-out Reset<br>Voltage                                       | 3.7  | 4.0                                                                                                                                                                                                                                    | 4.35 | V     | BODEN bit in configuration word enabled    |  |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is

- measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20  $\mu$ A to the specification. This value is from characterization and is for design guidance only. This is not tested.

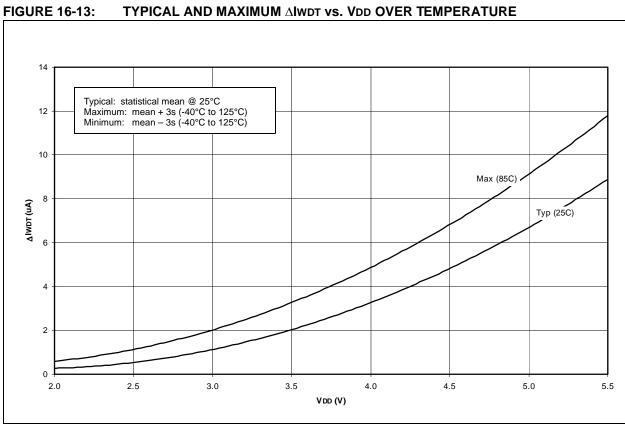

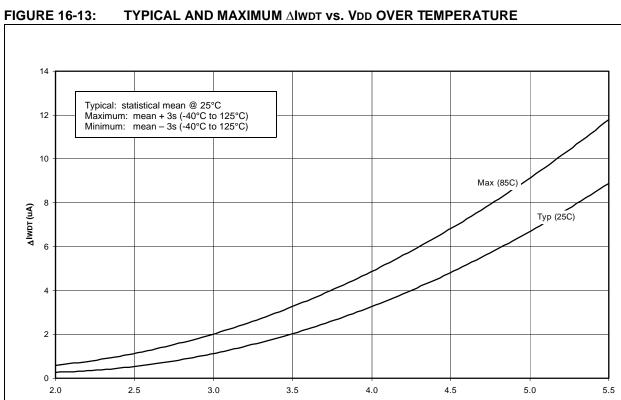

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial)

PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

(Continued)

| PIC16LF8<br>(Comme             | <b>73/874/87</b><br>ercial, Indu |                                           | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial |                                                                                                                                                                                                                                    |     |       |                                            |  |  |  |

|--------------------------------|----------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------------|--|--|--|

| PIC16F87<br>PIC16F87<br>(Comme |                                  | /877-20                                   |                                                                                                                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \le \text{Ta} \le +70^{\circ}\text{C}$ for commercial |     |       |                                            |  |  |  |

| Param<br>No.                   | Symbol                           | Characteristic/<br>Device                 | Min                                                                                                                                                                                                                                | Тур†                                                                                                                                                                                                                               | Max | Units | Conditions                                 |  |  |  |

|                                | IPD                              | Power-down Current <sup>(3,5)</sup>       |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |     |       |                                            |  |  |  |

| D020                           |                                  | 16LF87X                                   | _                                                                                                                                                                                                                                  | 7.5                                                                                                                                                                                                                                | 30  | μА    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D020                           |                                  | 16F87X                                    | _                                                                                                                                                                                                                                  | 10.5                                                                                                                                                                                                                               | 42  | μА    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021                           |                                  | 16LF87X                                   | _                                                                                                                                                                                                                                  | 0.9                                                                                                                                                                                                                                | 5   | μА    | VDD = 3.0V, WDT enabled,<br>0°C to +70°C   |  |  |  |

| D021                           |                                  | 16F87X                                    | _                                                                                                                                                                                                                                  | 1.5                                                                                                                                                                                                                                | 16  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021A                          |                                  | 16LF87X                                   |                                                                                                                                                                                                                                    | 0.9                                                                                                                                                                                                                                | 5   | μА    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021A                          |                                  | 16F87X                                    |                                                                                                                                                                                                                                    | 1.5                                                                                                                                                                                                                                | 19  | μА    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D023                           | Δlbor                            | Brown-out<br>Reset Current <sup>(6)</sup> | _                                                                                                                                                                                                                                  | 85                                                                                                                                                                                                                                 | 200 | μΑ    | BOR enabled, VDD = 5.0V                    |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20  $\mu$ A to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

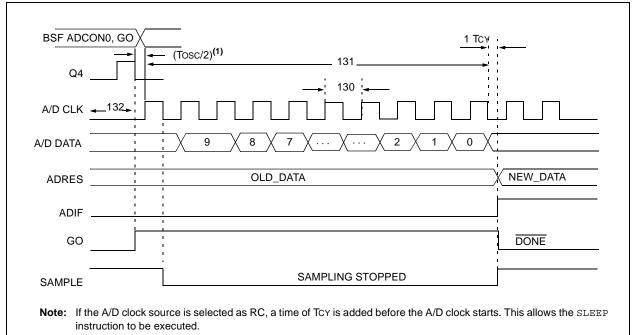

FIGURE 15-21: A/D CONVERSION TIMING

TABLE 15-13: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Charact                         | eristic               | Min      | Тур†     | Max | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|---------------------------------|-----------------------|----------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                | Standard(F)           | 1.6      | _        |     | μS    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                 | Extended( <b>LF</b> ) | 3.0      | _        | _   | μS    | Tosc based, VREF ≥ 2.0V                                                                                                                                                                                     |

|              |      |                                 | Standard(F)           | 2.0      | 4.0      | 6.0 | μS    | A/D RC mode                                                                                                                                                                                                 |

|              |      |                                 | Extended( <b>LF</b> ) | 3.0      | 6.0      | 9.0 | μS    | A/D RC mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not i (Note 1) | ncluding S/H time)    |          | _        | 12  | TAD   |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                |                       | (Note 2) | 40       | _   | μS    |                                                                                                                                                                                                             |

|              |      |                                 |                       | 10*      |          | Ι   | μS    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 20.0 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start           |                       | _        | Tosc/2 § | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>§</sup> This specification ensured by design.

<sup>2:</sup> See Section 11.1 for minimum conditions.

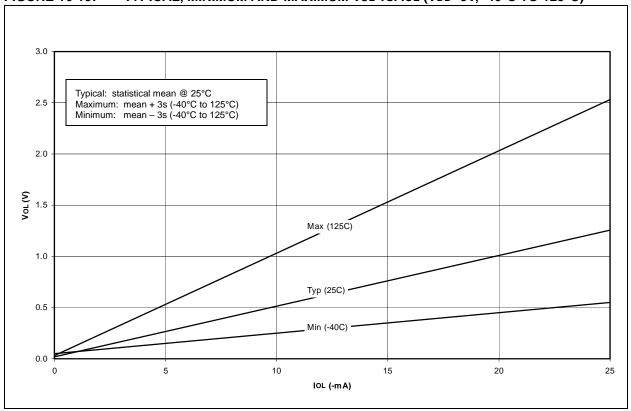

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD=3V, -40°C TO 125°C)

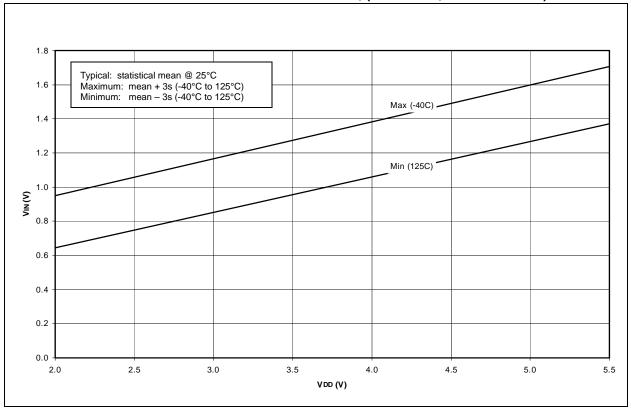

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO 125°C)

| Master Mode Operation                            | 79         |

|--------------------------------------------------|------------|

| Master Mode START Condition                      | 80         |

| Master Mode Transmission                         |            |

|                                                  |            |

| Master Mode Transmit Sequence                    |            |

| Multi-Master Communication                       | 89         |

| Multi-master Mode                                | 78         |

| Operation                                        |            |

|                                                  |            |

| Repeat START Condition Timing                    | 81         |

| Slave Mode                                       | 74         |

| Block Diagram                                    |            |

| Slave Reception                                  |            |

|                                                  |            |

| Slave Transmission                               |            |

| SSPBUF                                           | 73         |

| STOP Condition Receive or Transmit Timing        |            |

| •                                                |            |

| STOP Condition Timing                            | 87         |

| Waveforms for 7-bit Reception                    | 75         |

| Waveforms for 7-bit Transmission                 | 76         |

| I <sup>2</sup> C Module Address Register, SSPADD |            |

| 120 Oleve Marie                                  | 73         |

| I <sup>2</sup> C Slave Mode                      |            |

| ICEPIC In-Circuit Emulator                       | 144        |

| ID Locations                                     | 119, 133   |

| In-Circuit Serial Programming (ICSP)             |            |

|                                                  |            |

| INDF                                             |            |

| INDF Register                                    | 15, 16, 27 |

| Indirect Addressing                              | 27         |

| FSR Register                                     |            |

| •                                                |            |

| Instruction Format                               | 135        |

| Instruction Set                                  | 135        |

| ADDLW                                            | 137        |

| ADDWF                                            |            |

|                                                  |            |

| ANDLW                                            | 137        |

| ANDWF                                            | 137        |

| BCF                                              |            |

|                                                  |            |

| BSF                                              |            |

| BTFSC                                            | 137        |

| BTFSS                                            | 137        |

| CALL                                             |            |

|                                                  |            |

| CLRF                                             |            |

| CLRW                                             | 138        |

| CLRWDT                                           | 138        |

| COMF                                             |            |

|                                                  |            |

| DECF                                             |            |

| DECFSZ                                           | 139        |

| GOTO                                             | 139        |

| INCF                                             |            |

|                                                  |            |

| INCFSZ                                           |            |

| IORLW                                            | 139        |

| IORWF                                            | 139        |

| MOVF                                             |            |

|                                                  |            |

| MOVLW                                            | 140        |

| MOVWF                                            | 140        |

| NOP                                              | _          |

|                                                  |            |

| RETFIE                                           | 140        |

| RETLW                                            | 140        |

| RETURN                                           | 141        |

| RLF                                              |            |

|                                                  |            |

| RRF                                              | 141        |

| SLEEP                                            | 141        |

| SUBLW                                            |            |

|                                                  |            |

| SUBWF                                            |            |

| SWAPF                                            | 142        |

| XORLW                                            | 142        |

| XORWF                                            |            |

| Summary Table                                    |            |

|                                                  |            |

| INT Interrupt (RB0/INT). See Interrupt Sources                         |          |

|------------------------------------------------------------------------|----------|

| INTCON                                                                 |          |

| INTCON Register                                                        |          |

| GIE Bit                                                                | 20       |

| INTE Bit                                                               | 20       |

| INTF Bit                                                               |          |

| PEIE Bit                                                               | 20       |

| RBIE Bit                                                               | 20       |

| RBIF Bit                                                               | 20, 31   |

| T0IE Bit                                                               | 20       |

| T0IF Bit                                                               |          |

| Inter-Integrated Circuit (I <sup>2</sup> C)                            | 65       |

| Internal Sampling Switch (Rss) Impedence                               |          |

| Interrupt Sources                                                      |          |

| Block Diagram                                                          |          |

| Interrupt-on-Change (RB7:RB4)                                          | 31       |

| RB0/INT Pin, External                                                  |          |

| TMR0 Overflow                                                          |          |

| USART Receive/Transmit Complete                                        |          |

| Interrupts                                                             |          |

| Bus Collision Interrupt                                                | 2/       |

| Synchronous Serial Port Interrupt                                      |          |

| Interrupts, Context Saving During                                      |          |

|                                                                        | 130      |

| Interrupts, Enable Bits                                                | 20 420   |

| Global Interrupt Enable (GIE Bit)                                      | .20, 128 |

| Interrupt-on-Change (RB7:RB4) Enable                                   | 400      |

| (RBIE Bit)                                                             | 130      |

| Interrupt-on-Change (RB7:RB4) Enable                                   |          |

| (RBIE Bit)                                                             | 20       |

| Peripheral Interrupt Enable (PEIE Bit)                                 | 20       |

| RB0/INT Enable (INTE Bit)                                              |          |

| TMR0 Overflow Enable (T0IE Bit)                                        | 20       |

| Interrupts, Flag Bits                                                  |          |

| Interrupt-on-Change (RB7:RB4) Flag                                     |          |

| (RBIF Bit)                                                             | 130      |

| Interrupt-on-Change (RB7:RB4) Flag                                     |          |

| (RBIF Bit)                                                             |          |

| RB0/INT Flag (INTF Bit)                                                |          |

| TMR0 Overflow Flag (T0IF Bit)                                          | .20, 130 |

| V                                                                      |          |

| K                                                                      |          |

| KEELOQ Evaluation and Programming Tools                                | 146      |

|                                                                        |          |

| L                                                                      |          |

| Loading of PC                                                          | 26       |

|                                                                        |          |

| M                                                                      |          |

| Master Clear (MCLR)                                                    | 7, 8     |

| MCLR Reset, Normal Operation123,                                       | 125, 126 |

| MCLR Reset, SLEEP123,                                                  | 125, 126 |

| Memory Organization                                                    |          |

| Data Memory                                                            | 12       |

| Program Memory                                                         |          |

| MPLAB C17 and MPLAB C18 C Compilers                                    |          |

| MPLAB ICD In-Circuit Debugger                                          |          |

| MPLAB ICE High Performance Universal In-Circuit                        | 1-70     |

| Emulator with MPLAB IDE                                                | 144      |

| MPLAB Integrated Development Environment Softwa                        |          |

|                                                                        |          |

| MPLINK Object Linker/MPLIB Object Librarian Multi-Master Communication |          |

|                                                                        |          |

| Multi-Master Mode                                                      | /8       |