#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873-20-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PIC <sup>®</sup> MCU Mid-Range Reference<br>Manual (DS33023) | PIC16F873               | PIC16F874               | PIC16F876               | PIC16F877               |

|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Operating Frequency                                                          | DC - 20 MHz             |

| RESETS (and Delays)                                                          | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) |

| FLASH Program Memory<br>(14-bit words)                                       | 4K                      | 4K                      | 8K                      | 8K                      |

| Data Memory (bytes)                                                          | 192                     | 192                     | 368                     | 368                     |

| EEPROM Data Memory                                                           | 128                     | 128                     | 256                     | 256                     |

| Interrupts                                                                   | 13                      | 14                      | 13                      | 14                      |

| I/O Ports                                                                    | Ports A,B,C             | Ports A,B,C,D,E         | Ports A,B,C             | Ports A,B,C,D,E         |

| Timers                                                                       | 3                       | 3                       | 3                       | 3                       |

| Capture/Compare/PWM Modules                                                  | 2                       | 2                       | 2                       | 2                       |

| Serial Communications                                                        | MSSP, USART             | MSSP, USART             | MSSP, USART             | MSSP, USART             |

| Parallel Communications                                                      | —                       | PSP                     | —                       | PSP                     |

| 10-bit Analog-to-Digital Module                                              | 5 input channels        | 8 input channels        | 5 input channels        | 8 input channels        |

| Instruction Set                                                              | 35 instructions         | 35 instructions         | 35 instructions         | 35 instructions         |

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|---------------------|--------------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                  | 10           | 0             | —                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                   | 1            | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                     |              |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                   | 2            | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                   | 3            | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                   | 4            | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                   | 5            | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                   | 6            | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                   | 7            | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                     |              |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                  | 22           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                  | 23           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                  | 24           | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                  | 25           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                  | 26           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                     |              |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                  | 11           | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                  | 12           | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                  | 13           | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                  | 14           | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                  | 15           | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                  | 16           | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                  | 17           | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                  | 18           | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19               | 8, 19        | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                  | 20           | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not |              |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2             | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|----------------------|----------------|---------------|----------------|----------------|-------------------|-------------|---------|--------------------------|------------------------|

| Bank 0               |         |                      |                |               |                |                |                   |             |         |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio | egister)      | 0000 0000      | 27             |                   |             |         |                          |                        |

| 01h                  | TMR0    | Timer0 Mc            | dule Registe   | er            |                |                |                   |             |         | xxxx xxxx                | 47                     |

| 02h <sup>(3)</sup>   | PCL     | Program C            | Counter (PC)   | Least Signif  | icant Byte     |                |                   |             |         | 0000 0000                | 26                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1            | RP0           | TO             | PD             | Z                 | DC          | С       | 0001 1xxx                | 18                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ata Memory /   | Address Poir  | nter           |                |                   |             |         | xxxx xxxx                | 27                     |

| 05h                  | PORTA   | _                    | _              | PORTA Da      | ta Latch whe   | n written: POI | RTA pins whe      | n read      |         | 0x 0000                  | 29                     |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh   | en written: P | ORTB pins w    | /hen read      |                   |             |         | xxxx xxxx                | 31                     |

| 07h                  | PORTC   | PORTC D              | ata Latch wh   | en written: F | ORTC pins v    | vhen read      |                   |             |         | xxxx xxxx                | 33                     |

| 08h <sup>(4)</sup>   | PORTD   | PORTD D              | ata Latch wh   | en written: F | ORTD pins v    | vhen read      |                   |             |         | xxxx xxxx                | 35                     |

| 09h <sup>(4)</sup>   | PORTE   | _                    | _              | _             | _              | _              | RE2               | RE1         | RE0     | xxx                      | 36                     |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    |                |               | Write Buffer   | for the upper  | r 5 bits of the I | Program Cou | unter   | 0 0000                   | 26                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE           | T0IE          | INTE           | RBIE           | T0IF              | INTF        | RBIF    | 0000 000x                | 20                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF           | RCIF          | TXIF           | SSPIF          | CCP1IF            | TMR2IF      | TMR1IF  | 0000 0000                | 22                     |

| 0Dh                  | PIR2    | —                    | (5)            | _             | EEIF           | BCLIF          | —                 |             | CCP2IF  | -r-0 00                  | 24                     |

| 0Eh                  | TMR1L   | Holding re           | gister for the | Least Signif  | ficant Byte of | the 16-bit TM  | IR1 Register      |             |         | xxxx xxxx                | 52                     |

| 0Fh                  | TMR1H   | Holding re           | gister for the | Most Signifi  | cant Byte of t | the 16-bit TM  | R1 Register       |             |         | xxxx xxxx                | 52                     |

| 10h                  | T1CON   | _                    | _              | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC            | TMR1CS      | TMR10N  | 00 0000                  | 51                     |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe   | er            |                |                |                   |             |         | 0000 0000                | 55                     |

| 12h                  | T2CON   | _                    | TOUTPS3        | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON            | T2CKPS1     | T2CKPS0 | -000 0000                | 55                     |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po  | rt Receive B  | uffer/Transm   | it Register    |                   |             |         | xxxx xxxx                | 70, 73                 |

| 14h                  | SSPCON  | WCOL                 | SSPOV          | SSPEN         | CKP            | SSPM3          | SSPM2             | SSPM1       | SSPM0   | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI     | M Register1   | (LSB)          |                |                   |             |         | XXXX XXXX                | 57                     |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI     | M Register1   | (MSB)          |                |                   |             |         | XXXX XXXX                | 57                     |

| 17h                  | CCP1CON | _                    | _              | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2            | CCP1M1      | CCP1M0  | 00 0000                  | 58                     |

| 18h                  | RCSTA   | SPEN                 | RX9            | SREN          | CREN           | ADDEN          | FERR              | OERR        | RX9D    | 0000 000x                | 96                     |

| 19h                  | TXREG   | USART Tr             | ansmit Data    | Register      |                |                |                   |             |         | 0000 0000                | 99                     |

| 1Ah                  | RCREG   | USART Re             | eceive Data I  | Register      |                |                |                   |             |         | 0000 0000                | 101                    |

| 1Bh                  | CCPR2L  | Capture/C            | ompare/PWI     | V Register2   | (LSB)          |                |                   |             |         | xxxx xxxx                | 57                     |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI     | M Register2   | (MSB)          |                |                   |             |         | xxxx xxxx                | 57                     |

| 1Dh                  | CCP2CON | _                    | _              | CCP2X         | CCP2Y          | CCP2M3         | CCP2M2            | CCP2M1      | CCP2M0  | 00 0000                  | 58                     |

| 1Eh                  | ADRESH  | A/D Result           | t Register Hi  | gh Byte       |                |                |                   |             |         | xxxx xxxx                | 116                    |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0          | CHS2          | CHS1           | CHS0           | GO/DONE           | _           | ADON    | 0000 00-0                | 111                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

#### 2.2.2.2 OPTION\_REG Register

The OPTION\_REG Register is a readable and writable register, which contains various control bits to configure the TMR0 prescaler/WDT postscaler (single assignable register known also as the prescaler), the External INT Interrupt, TMR0 and the weak pull-ups on PORTB.

| Note: | To achieve a 1:1 prescaler assignment for  |

|-------|--------------------------------------------|

|       | the TMR0 register, assign the prescaler to |

|       | the Watchdog Timer.                        |

#### **R/W-1** R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 RBPU INTEDG T0CS TOSE PSA PS2 PS1 PS0 bit 7 bit 0 **RBPU:** PORTB Pull-up Enable bit bit 7 1 = PORTB pull-ups are disabled 0 = PORTB pull-ups are enabled by individual port latch values bit 6 **INTEDG:** Interrupt Edge Select bit 1 = Interrupt on rising edge of RB0/INT pin 0 = Interrupt on falling edge of RB0/INT pin bit 5 TOCS: TMR0 Clock Source Select bit 1 = Transition on RA4/T0CKI pin 0 = Internal instruction cycle clock (CLKOUT) bit 4 TOSE: TMR0 Source Edge Select bit 1 = Increment on high-to-low transition on RA4/T0CKI pin 0 = Increment on low-to-high transition on RA4/T0CKI pin bit 3 PSA: Prescaler Assignment bit 1 = Prescaler is assigned to the WDT 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS2:PS0: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 000 1:1 1:2 1:2 001 1:4 010 1:4 1:8 011 1:8 1:16 1:16 100 1:32 101 1:32 1:64 110 1:128 1:64 111 1:128 1:256 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

**Note:** When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device

### **REGISTER 2-2: OPTION\_REG REGISTER (ADDRESS 81h, 181h)**

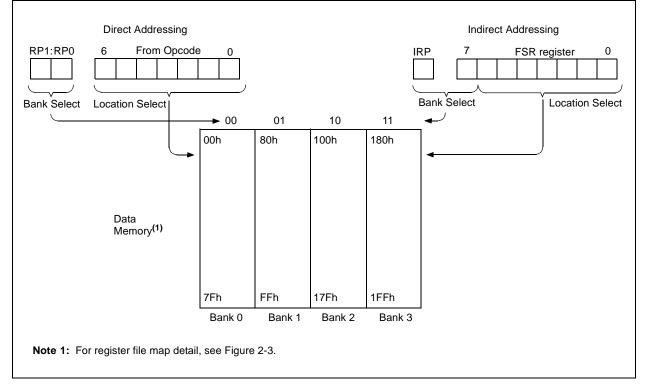

## 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

# PIC16F87X

NOTES:

### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                      | Bit 5        | Bit 4         | Bit 3         | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------------------------------------------------------------------------|--------------|---------------|---------------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                                                                       | TOIE         | INTE          | RBIE          | TOIF      | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                       | RCIF         | TXIF          | SSPIF         | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                       | RCIE         | TXIE          | SSPIE         | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            | egister for th                                                             | ne Least Sig | nificant Byte | of the 16-bit | TMR1 Regi | ster   |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H  | Holding R            | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |              |               |               |           |        |        | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON  | —                    | —                                                                          | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC    | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

# PIC16F87X

| REGISTER 0-1: | CCPTCON REGISTER/CCP2CON REGISTER (ADDRESS: 1/11/1011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |             |              |                |             |              |        |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|--------------|----------------|-------------|--------------|--------|--|--|

|               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0      | R/W-0       | R/W-0        | R/W-0          | R/W-0       | R/W-0        | R/W-0  |  |  |

|               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _        | CCPxX       | CCPxY        | CCPxM3         | CCPxM2      | CCPxM1       | CCPxM0 |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |             |              |                |             |              | bit 0  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |             |              |                |             |              |        |  |  |

|               | bit 7-6 <b>Unimplemented:</b> Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |             |              |                |             |              |        |  |  |

| bit 5-4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          | Least Sign  | ificant bits |                |             |              |        |  |  |

|               | <u>Capture m</u><br>Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ode:     |             |              |                |             |              |        |  |  |

|               | <u>Compare n</u><br>Unused                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | node:    |             |              |                |             |              |        |  |  |

|               | <u>PWM mode</u><br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | LSbs of the | e PWM duty   | cycle. The eig | ght MSbs ar | e found in C | CPRxL. |  |  |

| bit 3-0       | CCPxM3:C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CPxM0: C | CPx Mode S  | Select bits  |                |             |              |        |  |  |

|               | <ul> <li>bit 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits</li> <li>0000 = Capture/Compare/PWM disabled (resets CCPx module)</li> <li>0100 = Capture mode, every falling edge</li> <li>0101 = Capture mode, every falling edge</li> <li>0110 = Capture mode, every 4th rising edge</li> <li>0111 = Capture mode, every 16th rising edge</li> <li>1000 = Compare mode, set output on match (CCPxIF bit is set)</li> <li>1001 = Compare mode, clear output on match (CCPxIF bit is set)</li> <li>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)</li> <li>1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP<sup>2</sup> resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled)</li> <li>11xx = PWM mode</li> </ul> |          |             |              |                |             |              |        |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |             |              |                |             |              |        |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ble bit  | VV = V      | Vritable bit | U = Unim       | plemented l | bit, read as | ʻ0'    |  |  |

'1' = Bit is set

- n = Value at POR

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

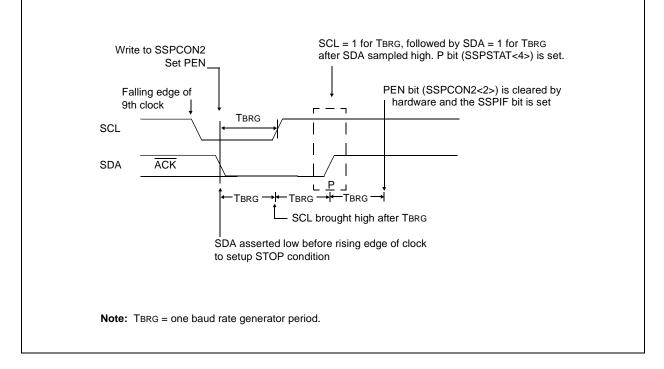

#### 9.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-17).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

#### 9.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined. It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9                          | TXEN  | SYNC  |       | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9                          | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | Baud Rate Generator Register |       |       |       |       |       |       |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

## TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | F       | osc = 20 M       | IHz | F       | osc = 16 N | IHz | F       | Fosc = 10 MHz               |       |            |                             |

|-------------|---------|------------------|-----|---------|------------|-----|---------|-----------------------------|-------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>KBAUD ERROR |     | Value   |            |     |         | SPBRG<br>value<br>(decimal) | KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -                | -   | -       | -          | -   | -       | -                           | -     |            |                             |

| 1.2         | 1.221   | 1.75             | 255 | 1.202   | 0.17       | 207 | 1.202   | 0.17                        | 129   |            |                             |

| 2.4         | 2.404   | 0.17             | 129 | 2.404   | 0.17       | 103 | 2.404   | 0.17                        | 64    |            |                             |

| 9.6         | 9.766   | 1.73             | 31  | 9.615   | 0.16       | 25  | 9.766   | 1.73                        | 15    |            |                             |

| 19.2        | 19.531  | 1.72             | 15  | 19.231  | 0.16       | 12  | 19.531  | 1.72                        | 7     |            |                             |

| 28.8        | 31.250  | 8.51             | 9   | 27.778  | 3.55       | 8   | 31.250  | 8.51                        | 4     |            |                             |

| 33.6        | 34.722  | 3.34             | 8   | 35.714  | 6.29       | 6   | 31.250  | 6.99                        | 4     |            |                             |

| 57.6        | 62.500  | 8.51             | 4   | 62.500  | 8.51       | 3   | 52.083  | 9.58                        | 2     |            |                             |

| HIGH        | 1.221   | -                | 255 | 0.977   | -          | 255 | 0.610   | -                           | 255   |            |                             |

| LOW         | 312.500 | -                | 0   | 250.000 | -          | 0   | 156.250 | -                           | 0     |            |                             |

| DAUD                |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |

|---------------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |

| 1.2                 | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |

| 2.4                 | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |

| 9.6                 | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |

| 19.2                | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |

| 28.8                | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |

| 33.6                | -      | -          | -                           | -                 | -          | -                           |  |

| 57.6                | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |

| HIGH                | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |

| LOW                 | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |

## TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 20 MHz |            | F                           | osc = 16 M | Hz         | Fosc = 10 MHz               |         |            |                             |

|-------------|---------------|------------|-----------------------------|------------|------------|-----------------------------|---------|------------|-----------------------------|

| RATE<br>(K) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -             | -          | -                           | -          | -          | -                           | -       | -          | -                           |

| 1.2         | -             | -          | -                           | -          | -          | -                           | -       | -          | -                           |

| 2.4         | -             | -          | -                           | -          | -          | -                           | 2.441   | 1.71       | 255                         |

| 9.6         | 9.615         | 0.16       | 129                         | 9.615      | 0.16       | 103                         | 9.615   | 0.16       | 64                          |

| 19.2        | 19.231        | 0.16       | 64                          | 19.231     | 0.16       | 51                          | 19.531  | 1.72       | 31                          |

| 28.8        | 29.070        | 0.94       | 42                          | 29.412     | 2.13       | 33                          | 28.409  | 1.36       | 21                          |

| 33.6        | 33.784        | 0.55       | 36                          | 33.333     | 0.79       | 29                          | 32.895  | 2.10       | 18                          |

| 57.6        | 59.524        | 3.34       | 20                          | 58.824     | 2.13       | 16                          | 56.818  | 1.36       | 10                          |

| HIGH        | 4.883         | -          | 255                         | 3.906      | -          | 255                         | 2.441   | -          | 255                         |

| LOW         | 1250.000      | -          | 0                           | 1000.000   |            | 0                           | 625.000 | -          | 0                           |

| BAUD        | F       | osc = 4 MH | łz                          | Fosc = 3.6864 MHz |            |                             |

|-------------|---------|------------|-----------------------------|-------------------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -                 | -          | -                           |

| 1.2         | 1.202   | 0.17       | 207                         | 1.2               | 0          | 191                         |

| 2.4         | 2.404   | 0.17       | 103                         | 2.4               | 0          | 95                          |

| 9.6         | 9.615   | 0.16       | 25                          | 9.6               | 0          | 23                          |

| 19.2        | 19.231  | 0.16       | 12                          | 19.2              | 0          | 11                          |

| 28.8        | 27.798  | 3.55       | 8                           | 28.8              | 0          | 7                           |

| 33.6        | 35.714  | 6.29       | 6                           | 32.9              | 2.04       | 6                           |

| 57.6        | 62.500  | 8.51       | 3                           | 57.6              | 0          | 3                           |

| HIGH        | 0.977   | -          | 255                         | 0.9               | -          | 255                         |

| LOW         | 250.000 | -          | 0                           | 230.4             | -          | 0                           |

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1              | CP0 | DEBUG                                                         | —                                                                                                                                                                                                                                                                                                                                                                  | WRT      | CPD       | LVP                | BODEN                                      | CP1                 | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |

|------------------|-----|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------------------|--------------------------------------------|---------------------|-----|-------|------|-------|-------|

| bit13<br>bit 13- | 12, |                                                               |                                                                                                                                                                                                                                                                                                                                                                    | -        | n Memor   | y Code             | Protection b                               | <sub>Dits</sub> (2) |     |       |      |       | bit0  |

| bit 5-4          |     | 10 = 1F00<br>10 = 0F00<br>01 = 1000<br>01 = 0800<br>00 = 0000 | 11 = Code protection off<br>10 = 1F00h to 1FFFh code protected (PIC16F877, 876)<br>10 = 0F00h to 0FFFh code protected (PIC16F874, 873)<br>01 = 1000h to 1FFFh code protected (PIC16F877, 876)<br>01 = 0800h to 0FFFh code protected (PIC16F874, 873)<br>00 = 0000h to 1FFFh code protected (PIC16F877, 876)<br>00 = 0000h to 0FFFh code protected (PIC16F874, 873) |          |           |                    |                                            |                     |     |       |      |       |       |

| bit 11           |     | 1 = In-Cir                                                    | <b>DEBUG:</b> In-Circuit Debugger Mode<br>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger.                                                                                                                                                                |          |           |                    |                                            |                     |     |       |      |       |       |

| bit 10           |     | Unimpler                                                      | nented:                                                                                                                                                                                                                                                                                                                                                            | Read as  | '1'       |                    |                                            |                     |     |       |      |       |       |

| bit 9            |     | 1 = Unpro                                                     | WRT: FLASH Program Memory Write Enable<br>1 = Unprotected program memory may be written to by EECON control<br>0 = Unprotected program memory may not be written to by EECON control                                                                                                                                                                               |          |           |                    |                                            |                     |     |       |      |       |       |

| bit 8            |     | 1 = Code                                                      | <b>CPD:</b> Data EE Memory Code Protection<br>1 = Code protection off<br>0 = Data EEPROM memory code protected                                                                                                                                                                                                                                                     |          |           |                    |                                            |                     |     |       |      |       |       |

| bit 7            |     | 1 = RB3/F                                                     | PGM pin                                                                                                                                                                                                                                                                                                                                                            | has PGN  | 1 functio | n, low v           | iming Enabl<br>oltage prog<br>e used for p | ramming             |     | 1     |      |       |       |

| bit 6            |     | <b>BODEN</b> :<br>1 = BOR<br>0 = BOR                          | enabled                                                                                                                                                                                                                                                                                                                                                            | ut Reset | Enable t  | <sub>Dit</sub> (3) |                                            |                     |     |       |      |       |       |

| bit 3            |     | <b>PWRTE</b> :<br>1 = PWR<br>0 = PWR                          | T disable                                                                                                                                                                                                                                                                                                                                                          | d        | nable b   | it(3)              |                                            |                     |     |       |      |       |       |

| bit 2            |     | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                         | enabled                                                                                                                                                                                                                                                                                                                                                            |          | nable bit |                    |                                            |                     |     |       |      |       |       |

| bit 1-0          |     | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (   | oscillator<br>oscillator<br>oscillator                                                                                                                                                                                                                                                                                                                             |          | Selectio  | n bits             |                                            |                     |     |       |      |       |       |

- **Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

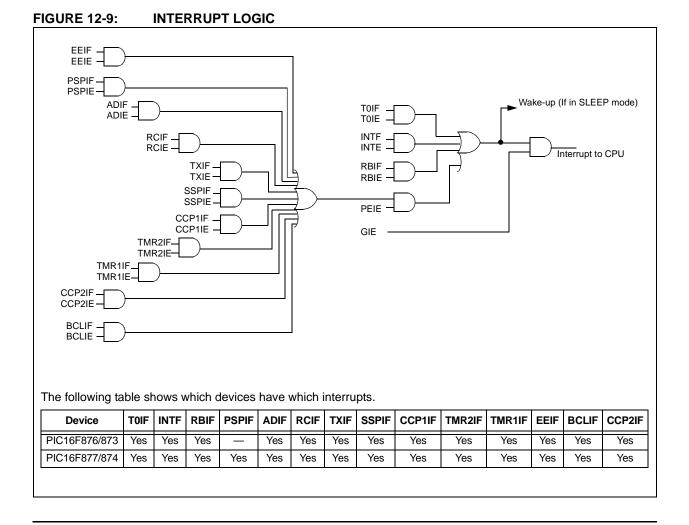

## 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

© 1998-2013 Microchip Technology Inc.

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| (Commercial, Industrial)                                                         |        |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                      |      |       |                                               |  |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|-------|-----------------------------------------------|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                                  |                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                               |  |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                                        | Min                                                  | Тур†                                                 | Мах  | Units | Conditions                                    |  |

|                                                                                  | Vdd    | Supply Voltage                                                   |                                                      |                                                      |      |       |                                               |  |

| D001                                                                             |        | 16LF87X                                                          | 2.0                                                  |                                                      | 5.5  | V     | LP, XT, RC osc configuration<br>(DC to 4 MHz) |  |

| D001                                                                             |        | 16F87X                                                           | 4.0                                                  | _                                                    | 5.5  | V     | LP, XT, RC osc configuration                  |  |

| D001A                                                                            |        |                                                                  | 4.5                                                  |                                                      | 5.5  | V     | HS osc configuration                          |  |

|                                                                                  |        |                                                                  | VBOR                                                 |                                                      | 5.5  | V     | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>     |  |

| D002                                                                             | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                    | 1.5                                                  |      | V     |                                               |  |

| D003                                                                             | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                    | Vss                                                  | _    | V     | See section on Power-on Reset for details     |  |

| D004                                                                             | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                 | —                                                    | —    | V/ms  | See section on Power-on Reset for details     |  |

| D005                                                                             | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                  | 4.0                                                  | 4.35 | V     | BODEN bit in configuration word<br>enabled    |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

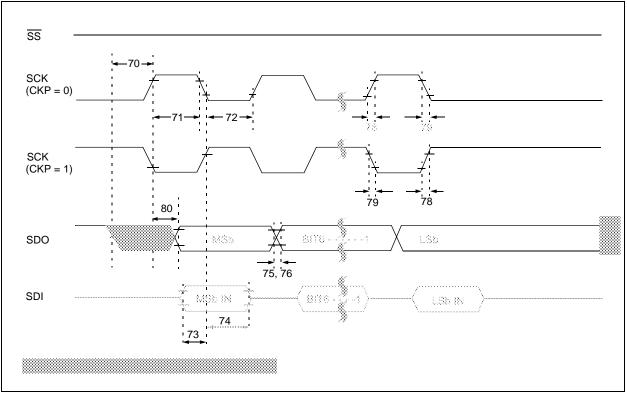

#### FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

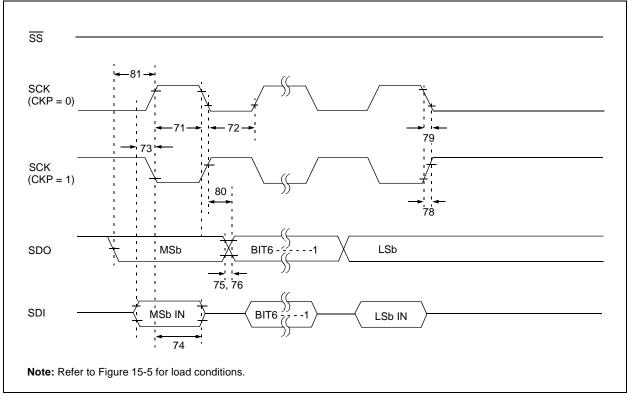

### FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

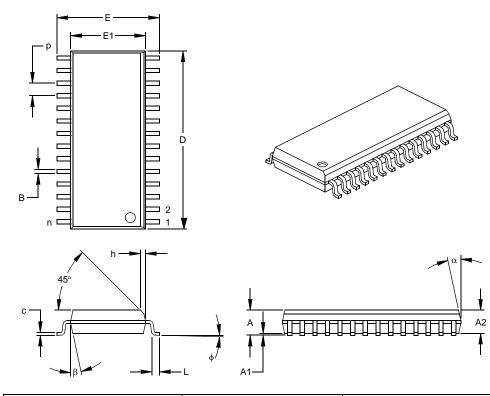

## 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    |      | INCHES* |      | N     | <b>1ILLIMETERS</b> | 5     |

|--------------------------|----------|------|---------|------|-------|--------------------|-------|

| Dimensio                 | n Limits | MIN  | NOM     | MAX  | MIN   | NOM                | MAX   |

| Number of Pins           | n        |      | 28      |      |       | 28                 |       |

| Pitch                    | р        |      | .050    |      |       | 1.27               |       |

| Overall Height           | Α        | .093 | .099    | .104 | 2.36  | 2.50               | 2.64  |

| Molded Package Thickness | A2       | .088 | .091    | .094 | 2.24  | 2.31               | 2.39  |

| Standoff §               | A1       | .004 | .008    | .012 | 0.10  | 0.20               | 0.30  |

| Overall Width            | Е        | .394 | .407    | .420 | 10.01 | 10.34              | 10.67 |

| Molded Package Width     | E1       | .288 | .295    | .299 | 7.32  | 7.49               | 7.59  |

| Overall Length           | D        | .695 | .704    | .712 | 17.65 | 17.87              | 18.08 |

| Chamfer Distance         | h        | .010 | .020    | .029 | 0.25  | 0.50               | 0.74  |

| Foot Length              | L        | .016 | .033    | .050 | 0.41  | 0.84               | 1.27  |

| Foot Angle Top           | ф        | 0    | 4       | 8    | 0     | 4                  | 8     |

| Lead Thickness           | С        | .009 | .011    | .013 | 0.23  | 0.28               | 0.33  |

| Lead Width               | В        | .014 | .017    | .020 | 0.36  | 0.42               | 0.51  |

| Mold Draft Angle Top     | α        | 0    | 12      | 15   | 0     | 12                 | 15    |

| Mold Draft Angle Bottom  | β        | 0    | 12      | 15   | 0     | 12                 | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013 Drawing No. C04-052

## APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|

| Pins              | 28/40                                               | 28/40                                                      |

| Timers            | 3                                                   | 3                                                          |