Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873-20i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

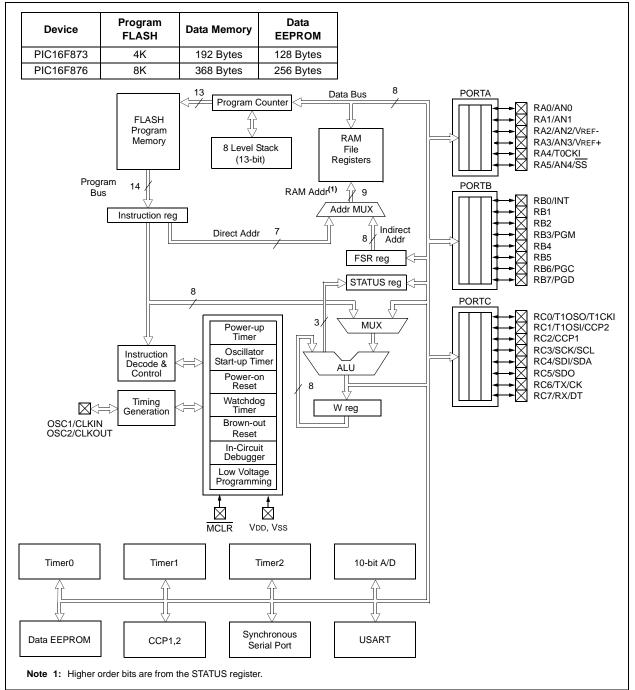

## 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                              | File<br>Address             | A                                                                     | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>  | 00h                         | Indirect addr.(*)                                                     | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                           | 01h                         | OPTION_REG                                                            | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                            | 02h                         | PCL                                                                   | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                         | 03h                         | STATUS                                                                | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                            | 04h                         | FSR                                                                   | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                          | 05h                         | TRISA                                                                 | 85h            |                     | 105h            |                         | 185h           |

| PORTB                          | 06h                         | TRISB                                                                 | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                          | 07h                         | TRISC                                                                 | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>           | 08h                         | TRISD <sup>(1)</sup>                                                  | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>           | 09h                         | TRISE <sup>(1)</sup>                                                  | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                         | 0Ah                         | PCLATH                                                                | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                         | 0Bh                         | INTCON                                                                | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                           | 0Ch                         | PIE1                                                                  | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                           | 0Dh                         | PIE2                                                                  | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                          | 0Eh                         | PCON                                                                  | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                          | 0Fh                         |                                                                       | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                          | 10h                         |                                                                       | 90h            |                     | 110h            |                         | 190h           |

| TMR2                           | 11h                         | SSPCON2                                                               | 91h            |                     |                 |                         |                |

| T2CON                          | 12h                         | PR2                                                                   | 92h            |                     |                 |                         |                |

| SSPBUF                         | 13h                         | SSPADD                                                                | 93h            |                     |                 |                         |                |

| SSPCON                         | 14h                         | SSPSTAT                                                               | 94h            |                     |                 |                         |                |

| CCPR1L                         | 15h                         |                                                                       | 95h            |                     |                 |                         |                |

| CCPR1H                         | 16h                         |                                                                       | 96h            |                     |                 |                         |                |

| CCP1CON                        | 17h                         |                                                                       | 97h            |                     |                 |                         |                |

| RCSTA                          | 18h                         | TXSTA                                                                 | 98h            |                     |                 |                         |                |

| TXREG                          | 19h                         | SPBRG                                                                 | 99h            |                     |                 |                         |                |

| RCREG                          | 1Ah                         |                                                                       | 9Ah            |                     |                 |                         |                |

| CCPR2L                         | 1Bh                         |                                                                       | 9Bh            |                     |                 |                         |                |

| CCPR2H                         | 1Ch                         |                                                                       | 9Ch            |                     |                 |                         |                |

| CCP2CON                        | 1Dh                         |                                                                       | 9Dh            |                     |                 |                         |                |

| ADRESH                         | 1Eh                         | ADRESL                                                                | 9Eh            |                     |                 |                         |                |

| ADCON0                         | 1Fh                         | ADCON1                                                                | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                | 20h                         |                                                                       | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register |                             | General<br>Purpose<br>Register                                        |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                       |                             | 96 Bytes                                                              |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                | 754                         |                                                                       |                |                     | 1756            |                         | 4              |

| Bank 0                         | J 7Fh                       | Bank 1                                                                | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| * Not a<br>Note 1: These       | physical reg<br>e registers | data memory locat<br>gister.<br>are not implemen<br>are reserved, mai | ted on the     | e PIC16F873.        |                 |                         |                |

#### 2.2.2.1 STATUS Register

The STATUS register contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable, therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions not affecting any status bits, see the "Instruction Set Summary."

| Note: | The C and DC bits operate as a borrow       |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | and digit borrow bit, respectively, in sub- |  |  |  |  |  |  |  |  |  |  |

|       | traction. See the SUBLW and SUBWF           |  |  |  |  |  |  |  |  |  |  |

|       | instructions for examples.                  |  |  |  |  |  |  |  |  |  |  |

#### REGISTER 2-1: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

|         | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                                                | R/W-0            | R-1           | R-1                                    | R/W-x      | R/W-x | R/W-x |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------|---------------|----------------------------------------|------------|-------|-------|--|--|--|--|

|         | IRP                                                                                                                                                                                                                                                      | RP1                                                                                  | RP0              | TO            | PD                                     | Z          | DC    | С     |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                    |                                                                                      |                  |               |                                        |            |       | bit 0 |  |  |  |  |

|         |                                                                                                                                                                                                                                                          |                                                                                      |                  |               | <i>.</i>                               |            |       |       |  |  |  |  |

| bit 7   | -                                                                                                                                                                                                                                                        |                                                                                      | -                | d for indire  | ct addressing)                         |            |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | 2, 3 (100h - <sup>2</sup><br>0, 1 (00h - Fl                                          | ,                |               |                                        |            |       |       |  |  |  |  |

| bit 6-5 | RP1:RP0                                                                                                                                                                                                                                                  | : Register Ba                                                                        | nk Select bi     | its (used for | direct addressi                        | ng)        |       |       |  |  |  |  |

|         | 10 = Ban<br>01 = Ban<br>00 = Ban                                                                                                                                                                                                                         | k 3 (180h - 1 <br>k 2 (100h - 1]<br>k 1 (80h - FF<br>k 0 (00h - 7F <br>k is 128 byte | 7Fh)<br>h)<br>h) |               |                                        |            |       |       |  |  |  |  |

| bit 4   | <b>TO</b> : Time                                                                                                                                                                                                                                         | -out bit                                                                             |                  |               |                                        |            |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | power-up, CL<br>T time-out o                                                         |                  | iction, or SI | EEP instruction                        |            |       |       |  |  |  |  |

| bit 3   | PD: Powe                                                                                                                                                                                                                                                 | er-down bit                                                                          |                  |               |                                        |            |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | power-up or l<br>ecution of the                                                      |                  |               | on                                     |            |       |       |  |  |  |  |

| bit 2   | Z: Zero bi                                                                                                                                                                                                                                               | it                                                                                   |                  |               |                                        |            |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | esult of an ar<br>esult of an ar                                                     |                  |               | on is zero<br>on is not zero           |            |       |       |  |  |  |  |

| bit 1   | DC: Digit                                                                                                                                                                                                                                                | carry/borrow                                                                         | bit (ADDWF,      | ADDLW, SU     | BLW, SUBWF ins                         | tructions) |       |       |  |  |  |  |

|         | (for borro                                                                                                                                                                                                                                               | w, the polarity                                                                      | / is reversed    | d)            |                                        |            |       |       |  |  |  |  |

|         | <ul> <li>1 = A carry-out from the 4th low order bit of the result occurred</li> <li>0 = No carry-out from the 4th low order bit of the result</li> </ul>                                                                                                 |                                                                                      |                  |               |                                        |            |       |       |  |  |  |  |

| bit 0   | C: Carry/                                                                                                                                                                                                                                                | borrow bit (AI                                                                       | DDWF, ADDLI      | W,SUBLW,S     | UBWF instruction                       | ons)       |       |       |  |  |  |  |

|         |                                                                                                                                                                                                                                                          | •                                                                                    | •                |               | f the result occu<br>of the result occ |            |       |       |  |  |  |  |

|         | <b>Note:</b> For borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high, or low order bit of the source register. |                                                                                      |                  |               |                                        |            |       |       |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                  |                                                                                      |                  |               |                                        |            |       |       |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name         | Bit# | Buffer | Function                                                                        |

|--------------|------|--------|---------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input.                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input.                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input.                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF.                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0. Output is open drain type.     |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input. |

#### TABLE 3-1: PORTA FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|--------|-------|-------|-------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 05h     | PORTA  | —     |       | RA5   | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                         |

| 85h     | TRISA  | —     | _     | PORTA | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                         |

| 9Fh     | ADCON1 | ADFM  |       | _     |                               | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0- 0000                  | 0-0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note: When using the SSP module in SPI Slave mode and  $\overline{SS}$  enabled, the A/D converter must be set to one of the following modes, where PCFG3:PCFG0 = 0100,0101, 011x, 1101, 1110, 1111.

#### TABLE 3-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or Synchronous Clock.                          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |

Legend: ST = Schmitt Trigger input

### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|-------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                          | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | ORTC Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                       |

Legend: x = unknown, u = unchanged

Write operations have two control bits, WR and WREN, and two status bits, WRERR and EEIF. The WREN bit is used to enable or disable the write operation. When WREN is clear, the write operation will be disabled. Therefore, the WREN bit must be set before executing a write operation. The WR bit is used to initiate the write operation. It also is automatically cleared at the end of the write operation. The interrupt flag EEIF is used to determine when the memory write completes. This flag must be cleared in software before setting the WR bit. For EEPROM data memory, once the WREN bit and the WR bit have been set, the desired memory address in EEADR will be erased, followed by a write of the data in EEDATA. This operation takes place in parallel with the microcontroller continuing to execute normally. When the write is complete, the EEIF flag bit will be set. For program memory, once the WREN bit and the WR bit have been set, the microcontroller will cease to execute instructions. The desired memory location pointed to by EEADRH:EEADR will be erased. Then, the data value in EEDATH:EEDATA will be programmed. When complete, the EEIF flag bit will be set and the microcontroller will continue to execute code.

The WRERR bit is used to indicate when the PIC16F87X device has been reset during a write operation. WRERR should be cleared after Power-on Reset. Thereafter, it should be checked on any other RESET. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset, during normal operation. In these situations, following a RESET, the user should check the WRERR bit and rewrite the memory location, if set. The contents of the data registers, address registers and EEPGD bit are not affected by either MCLR Reset, or WDT Timeout Reset, during normal operation.

|         | R/W-x             | U-0                                                       | U-0                     | U-0          | R/W-x             | R/W-0        | R/S-0         | R/S-0      |  |  |  |  |  |

|---------|-------------------|-----------------------------------------------------------|-------------------------|--------------|-------------------|--------------|---------------|------------|--|--|--|--|--|

|         | EEPGD             | —                                                         |                         | _            | WRERR             | WREN         | WR            | RD         |  |  |  |  |  |

|         | bit 7             |                                                           |                         |              |                   |              |               | bit 0      |  |  |  |  |  |

|         |                   |                                                           |                         |              |                   |              |               |            |  |  |  |  |  |

| bit 7   | EEPGD: PI         | rogram/Data                                               | a EEPROM                | Select bit   |                   |              |               |            |  |  |  |  |  |

|         |                   | es program                                                |                         |              |                   |              |               |            |  |  |  |  |  |

|         |                   | es data me                                                |                         | a read or w  | rite operation is | in progres   | s)            |            |  |  |  |  |  |

| bit 6-4 |                   | ented: Rea                                                |                         |              |                   | in progree   | ,             |            |  |  |  |  |  |

| bit 3   | •                 | /RERR: EEPROM Error Flag bit                              |                         |              |                   |              |               |            |  |  |  |  |  |

|         |                   | = A write operation is prematurely terminated             |                         |              |                   |              |               |            |  |  |  |  |  |

|         | (any M            | (any MCLR Reset or any WDT Reset during normal operation) |                         |              |                   |              |               |            |  |  |  |  |  |

|         | 0 <b>= The wr</b> | 0 = The write operation completed                         |                         |              |                   |              |               |            |  |  |  |  |  |

| bit 2   | WREN: EE          | PROM Writ                                                 | e Enable bi             | t            |                   |              |               |            |  |  |  |  |  |

|         |                   | write cycles                                              |                         |              |                   |              |               |            |  |  |  |  |  |

|         |                   | write to the                                              | EEPROM                  |              |                   |              |               |            |  |  |  |  |  |

| bit 1   | WR: Write         |                                                           | · / <del>*</del> · · ·· |              |                   | ., .         | <del>.</del>  |            |  |  |  |  |  |

|         |                   | s a write cyc<br>y be set (no                             |                         |              | y hardware onc    | e write is o | complete. I   | ne VVR bit |  |  |  |  |  |

|         |                   | ycle to the E                                             | ,                       | ,            |                   |              |               |            |  |  |  |  |  |

| bit 0   | RD: Read (        | •                                                         |                         | ·            |                   |              |               |            |  |  |  |  |  |

|         | 1 = Initiates     | s an EEPRO                                                | OM read. (R             | D is cleared | l in hardware. T  | he RD bit    | can only be   | set (not   |  |  |  |  |  |

|         |                   | ) in software                                             | ,                       |              |                   |              |               |            |  |  |  |  |  |

|         | 0 = Does n        | ot initiate ar                                            | n EEPROM                | read         |                   |              |               |            |  |  |  |  |  |

|         | r                 |                                                           |                         |              |                   |              |               |            |  |  |  |  |  |

|         | Legend:           |                                                           |                         |              |                   |              |               |            |  |  |  |  |  |

|         | R = Reada         | ble bit                                                   | W = V                   | Vritable bit | U = Unimple       | emented b    | it, read as ' | 0'         |  |  |  |  |  |

|         | - n = Value       | at POR                                                    | '1' = E                 | Bit is set   | '0' = Bit is c    | leared       | x = Bit is ur | nknown     |  |  |  |  |  |

#### **REGISTER 4-1:** EECON1 REGISTER (ADDRESS 18Ch)

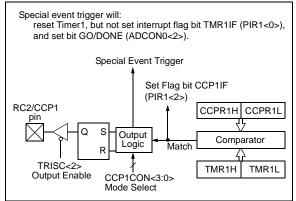

### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

# PIC16F87X

|       | R/W-0                  | R/W-0                                                          | R/W-0                       | R/W-0                      | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |

|-------|------------------------|----------------------------------------------------------------|-----------------------------|----------------------------|-------------------------|---------------|---------------|-------------|

|       | GCEN                   | ACKSTAT                                                        | ACKDT                       | ACKEN                      | RCEN                    | PEN           | RSEN          | SEN         |

|       | bit 7                  |                                                                |                             |                            |                         |               |               | bit 0       |

| bit 7 | 1 = Enable             | eneral Call En<br>e interrupt whe                              | en a genera                 |                            |                         | received in   | the SSPSR     | 2           |

| bit 6 | ACKSTAT                | Acknowledg                                                     | e Status bit                | (In I <sup>2</sup> C Maste | er mode onl             | у)            |               |             |

|       | 1 = Acknow             | <u>Transmit mod</u><br>wledge was n<br>wledge was re           | ot received                 |                            |                         |               |               |             |

| bit 5 | ACKDT: A               | cknowledge [                                                   | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m    | ode only)               |               |               |             |

|       | Value that end of a re | knowledge                                                      |                             | the user initi             | ates an Ack             | nowledge s    | equence at    | the         |

| bit 4 | ACKEN: A               | cknowledge \$                                                  | Sequence E                  | nable bit (In              | I <sup>2</sup> C Master | mode only)    |               |             |

|       | 1 = Initiate<br>Autom  | Receive mode<br>Acknowledge<br>atically cleare<br>wledge seque | e sequence<br>ed by hardw   |                            | I SCL pins a            | and transmit  | ACKDT da      | ta bit.     |

| bit 3 | RCEN: Re               | ceive Enable<br>es Receive mo                                  | bit (In I <sup>2</sup> C M  | laster mode                | only)                   |               |               |             |

| bit 2 | PEN: STC               | P Condition I                                                  | Enable bit (I               | n I <sup>2</sup> C Master  | r mode only             | )             |               |             |

|       | 1 = Initiate           | ase Control:<br>STOP condit<br>condition idle                  |                             | and SCL pir                | ns. Automat             | ically cleare | d by hardwa   | are.        |

| bit 1 | 1 = Initiate           | epeated STAR<br>Repeated ST/<br>ted START co                   | ART conditic                | on on SDA an               |                         |               |               | / hardware. |

| bit 0 | 1 = Initiate           | RT Condition<br>START cond<br>condition idl                    | lition on SD/               |                            |                         |               | ed by hardv   | vare.       |

|       |                        | For bits ACK<br>mode, this bit<br>writes to the \$             | may not be                  | set (no spo                |                         |               |               |             |

|       | Logondi                |                                                                |                             |                            |                         |               |               |             |

|       | Legend:<br>R = Reada   | blo bit                                                        | \\/ _ \\/.                  | itable bit                 |                         | plemented k   | hit road as f | 0'          |

|       | K = Keaua              |                                                                | vv = vvi                    |                            | 0 = 0.000               |               | n, reau as    | 0           |

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

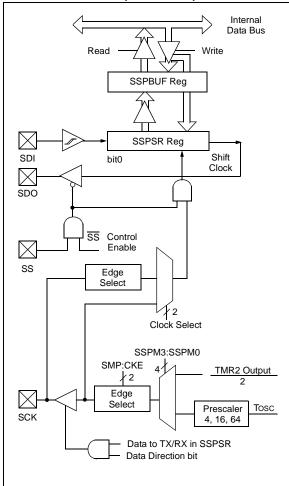

### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

#### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

#### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address                | Name    | Bit 7                  | Bit 6          | Bit 5        | Bit 4       | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR,<br>WDT |

|------------------------|---------|------------------------|----------------|--------------|-------------|-----------|--------|--------|--------|-----------------------|------------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE           | TOIE         | INTE        | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u                          |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup>   | ADIF           | RCIF         | TXIF        | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                          |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup>   | ADIE           | RCIE         | TXIE        | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                          |

| 0Dh                    | PIR2    | _                      | (2)            | _            | EEIF        | BCLIF     | _      | _      | CCP2IF | -r-0 00               | -r-0 00                            |

| 8Dh                    | PIE2    | _                      | (2)            | _            | EEIE        | BCLIE     | _      | —      | CCP2IE | -r-0 00               | -r-0 00                            |

| 13h                    | SSPBUF  | Synchrono              | ous Serial Por | rt Receive I | Buffer/Trar | nsmit Reg | ister  |        |        | xxxx xxxx             | uuuu uuuu                          |

| 14h                    | SSPCON  | WCOL                   | SSPOV          | SSPEN        | CKP         | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000 0000             | 0000 0000                          |

| 91h                    | SSPCON2 | GCEN                   | ACKSTAT        | ACKDT        | ACKEN       | RCEN      | PEN    | RSEN   | SEN    | 0000 0000             | 0000 0000                          |

| 93h                    | SSPADD  | I <sup>2</sup> C Slave | Address/Mas    |              | 0000 0000   | 0000 0000 |        |        |        |                       |                                    |

| 94h                    | SSPSTAT | SMP                    | CKE            | D/A          | Р           | S         | R/W    | UA     | BF     | 0000 0000             | 0000 0000                          |

## TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

**Note 1:** These bits are reserved on PIC16F873/876 devices; always maintain these bits clear.

2: These bits are reserved on these devices; always maintain these bits clear.

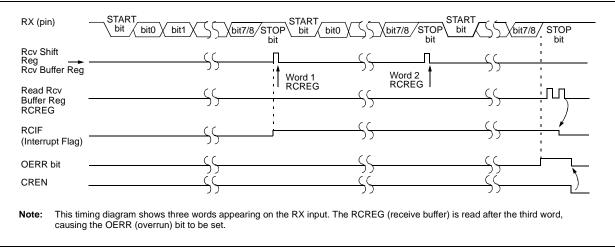

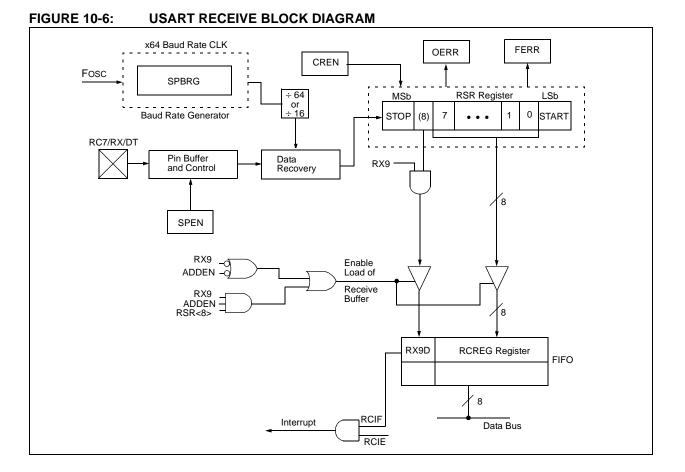

#### FIGURE 10-5: ASYNCHRONOUS RECEPTION

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                                | Name   | Bit 7                | Bit 6       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|----------------------------------------|--------|----------------------|-------------|--------|-------|-------|--------|-----------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE        | TOIE   | INTE  | RBIE  | TOIF   | INTF      | R0IF      | x000 0000x               | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF        | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9         | SREN   | CREN  | _     | FERR   | OERR      | RX9D      | 0000 -00x                | 0000 -00x                       |

| 1Ah                                    | RCREG  | USART R              | leceive Reg | gister |       |       |        |           |           | 0000 0000                | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE        | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9         | TXEN   | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010                | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |             |        |       |       |        | 0000 0000 | 0000 0000 |                          |                                 |

#### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

#### 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                                | Name   | Bit 7                | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|----------------------------------------|--------|----------------------|----------|---------|-------|-------|-----------|-----------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                  | PEIE     | TOIE    | INTE  | RBIE  | T0IF      | INTF      | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF    | TXIF  | SSPIF | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                 | RX9      | SREN    | CREN  | ADDEN | FERR      | OERR      | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                                    | RCREG  | USART R              | eceive R | egister |       |       |           |           |        | 0000 0000                | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE    | TXIE  | SSPIE | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                 | TX9      | TXEN    | SYNC  | _     | BRGH      | TRMT      | TX9D   | 0000 -010                | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                      |          |         |       |       | 0000 0000 | 0000 0000 |        |                          |                                 |

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception. **Note** 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.

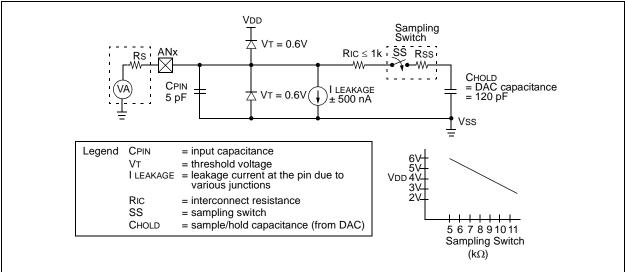

#### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

#### EQUATION 11-1: ACQUISITION TIME

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the  $PIC^{\textcircled{R}}$  MCU Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient    |

|------|---------------------------------------------------------------------------------------------|

|      | = $TAMP + TC + TCOFF$                                                                       |

|      | $= 2\mu s + TC + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$                         |

| TC   | = CHOLD (RIC + RSS + RS) $In(1/2047)$                                                       |

|      | = $-120 \text{pF} (1 \text{k}\Omega + 7 \text{k}\Omega + 10 \text{k}\Omega) \ln(0.0004885)$ |

|      | $= 16.47 \mu s$                                                                             |

| TACQ | = $2\mu s + 16.47\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$                |

|      | $= 19.72 \mu s$                                                                             |

| L    |                                                                                             |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

# PIC16F87X

NOTES:

# TABLE 12-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                            |          |  |  |  |  |  |

|---------------|----------------------------|----------|--|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A      | ± 20 PPM |  |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz         | ± 20 PPM |  |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1            | ± 50 PPM |  |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1            | ± 50 PPM |  |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C      | ± 30 PPM |  |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-<br>C | ± 30 PPM |  |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the startup time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- R<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PIC<sup>®</sup> MCU devices, oscillator performance should be verified.

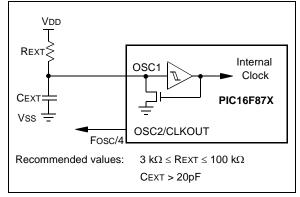

### 12.2.3 RC OSCILLATOR

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F87X.

### 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial) |        |                                           |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                                                                    |  |  |

|--------------------------------------------------------------|--------|-------------------------------------------|-----|------------------------------------------------------|-----|-------|--------------------------------------------------------------------|--|--|

| PIC16F87<br>PIC16F87<br>(Comme                               |        | /877-20                                   |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                                                                    |  |  |

| Param<br>No.                                                 | Symbol | Characteristic/<br>Device                 | Min | Тур†                                                 | Max | Units | Conditions                                                         |  |  |

|                                                              | IDD    | Supply Current <sup>(2,5)</sup>           |     |                                                      |     |       |                                                                    |  |  |

| D010                                                         |        | 16LF87X                                   | —   | 0.6                                                  | 2.0 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V               |  |  |

| D010                                                         |        | 16F87X                                    | —   | 1.6                                                  | 4   | mA    | RC osc configurations<br>FOSC = 4 MHz, VDD = 5.5V                  |  |  |

| D010A                                                        |        | 16LF87X                                   | —   | 20                                                   | 35  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled |  |  |

| D013                                                         |        | 16F87X                                    | _   | 7                                                    | 15  | mA    | HS osc configuration,<br>Fosc = 20 MHz, VDD = 5.5V                 |  |  |

| D015                                                         | ∆IBOR  | Brown-out<br>Reset Current <sup>(6)</sup> | —   | 85                                                   | 200 | μΑ    | BOR enabled, VDD = 5.0V                                            |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

| Param<br>No. | Symbol                | Characteristic                                                        | Min                                           | Тур†        | Мах      | Units     | Conditions |  |

|--------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|-------------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсу                                           | —           | —        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mode)                                      |                                               | TCY + 20    | —        | —         | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mode)                                       |                                               | Tcy + 20    | _        | _         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK                                   | 100                                           | _           | —        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK e                                  | 100                                           | _           | —        | ns        |            |  |

| 75*          | TdoR                  | SDO data output rise time                                             | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) |             | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                             |                                               |             | 10       | 25        | ns         |  |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-impedance                                        |                                               | 10          | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK output rise time (Master mode)                                    | Standard(F)<br>Extended(LF)                   |             | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master mode)                                    |                                               |             | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | _        | 50<br>145 | ns         |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                                     | Тсу                                           | _           | —        | ns        |            |  |

| 82*          | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edg             | _                                             | _           | 50       | ns        |            |  |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                                               | 1.5Tcy + 40 | _        | —         | ns         |  |

#### TABLE 15-7: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

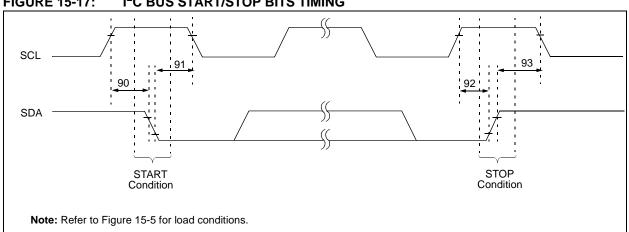

#### I<sup>2</sup>C BUS START/STOP BITS TIMING FIGURE 15-17:

| TABLE 15-9: I <sup>2</sup> C BUS DATA REQUI |

|---------------------------------------------|

|---------------------------------------------|

| Param<br>No. | Sym     | Characte               | Min          | Max        | Units | Conditions |                                                |

|--------------|---------|------------------------|--------------|------------|-------|------------|------------------------------------------------|

| 100          | Thigh   | Clock high time        | 100 kHz mode | 4.0        | —     | μS         | Device must operate at a minimum of 1.5 MHz    |

|              |         |                        | 400 kHz mode | 0.6        | —     | μs         | Device must operate at a<br>minimum of 10 MHz  |

|              |         |                        | SSP Module   | 0.5Tcy     |       |            |                                                |

| 101          | Tlow    | Clock low time         | 100 kHz mode | 4.7        | —     | μs         | Device must operate at a<br>minimum of 1.5 MHz |

|              |         |                        | 400 kHz mode | 1.3        | —     | μs         | Device must operate at a minimum of 10 MHz     |

|              |         |                        | SSP Module   | 0.5TCY     |       |            |                                                |

| 102          | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000  | ns         |                                                |

|              |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300   | ns         | Cb is specified to be from<br>10 to 400 pF     |

| 103          | Tf      | SDA and SCL fall time  | 100 kHz mode | —          | 300   | ns         |                                                |

|              |         |                        | 400 kHz mode | 20 + 0.1Cb | 300   | ns         | Cb is specified to be from<br>10 to 400 pF     |

| 90           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | —     | μs         | Only relevant for Repeated                     |

|              |         | setup time             | 400 kHz mode | 0.6        |       | μs         | START condition                                |

| 91           | Thd:sta | START condition hold   | 100 kHz mode | 4.0        | —     | μs         | After this period, the first clock             |

|              |         | time                   | 400 kHz mode | 0.6        |       | μS         | pulse is generated                             |

| 106          | Thd:dat | Data input hold time   | 100 kHz mode | 0          | —     | ns         |                                                |

|              |         |                        | 400 kHz mode | 0          | 0.9   | μs         |                                                |

| 107          | Tsu:dat | Data input setup time  | 100 kHz mode | 250        | —     | ns         | (Note 2)                                       |

|              |         |                        | 400 kHz mode | 100        | —     | ns         |                                                |

| 92           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | —     | μs         |                                                |

|              |         | time                   | 400 kHz mode | 0.6        | —     | μs         |                                                |

| 109          | Таа     | Output valid from      | 100 kHz mode | —          | 3500  | ns         | (Note 1)                                       |

|              |         | clock                  | 400 kHz mode | —          | —     | ns         |                                                |

| 110          | Tbuf    | Bus free time          | 100 kHz mode | 4.7        | —     | μS         | Time the bus must be free                      |

|              |         |                        | 400 kHz mode | 1.3        | —     | μS         | before a new transmission<br>can start         |

|              | Cb      | Bus capacitive loading |              | —          | 400   | pF         |                                                |

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that Tsu:dat ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ Tsu:dat = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

## INDEX

Α

| A/D1                                       | 11  |

|--------------------------------------------|-----|

| Acquisition Requirements1                  |     |

| ADCON0 Register                            |     |

| ADCON1 Register                            |     |

| ADIF bit                                   |     |

| Analog Input Model Block Diagram1          |     |

| Analog Port Pins                           |     |

| Associated Registers and Bits              |     |

| Block Diagram                              |     |

| Calculating Acquisition Time1              |     |

| Configuring Analog Port Pins1              |     |

| Configuring the Interrupt1                 |     |

| Configuring the Module1                    |     |

| Conversion Clock                           |     |

| Conversions1                               |     |

| Delays1                                    |     |

| Effects of a RESET1                        |     |

| GO/DONE bit                                |     |

| Internal Sampling Switch (Rss) Impedence   |     |

| Operation During SLEEP1                    |     |

| Result Registers1                          |     |

| Sampling Requirements1                     |     |

| Source Impedence1                          |     |

| Time Delays1                               |     |

| Absolute Maximum Ratings                   |     |

| ACK                                        |     |

| Acknowledge Data bit                       |     |

| Acknowledge Pulse                          |     |

| Acknowledge Sequence Enable bit            |     |