Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f873t-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                        | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |

|---------------|----------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|

|               | GIE                                                                                          | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |

|               | bit 7                                                                                        |                               |               |              |                  |             |                | bit 0      |  |  |

|               |                                                                                              |                               |               |              |                  |             |                |            |  |  |

| bit 7         | GIE: Globa                                                                                   | al Interrupt E                | nable bit     |              |                  |             |                |            |  |  |

|               | <ul> <li>1 = Enables all unmasked interrupts</li> <li>0 = Disables all interrupts</li> </ul> |                               |               |              |                  |             |                |            |  |  |

| <b>h</b> :+ C |                                                                                              |                               |               | L:4          |                  |             |                |            |  |  |

| bit 6         | -                                                                                            | pheral Interr                 | •             |              | -                |             |                |            |  |  |

|               |                                                                                              | s all unmas                   |               | •            | 5                |             |                |            |  |  |

| bit 5         |                                                                                              | 0 Overflow                    | =             |              |                  |             |                |            |  |  |

|               |                                                                                              | s the TMR0                    |               |              |                  |             |                |            |  |  |

|               | 0 = Disable                                                                                  | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |

| bit 4         |                                                                                              | /INT Externa                  | •             |              |                  |             |                |            |  |  |

|               |                                                                                              | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |

| bit 3         |                                                                                              | Port Change                   |               | •            |                  |             |                |            |  |  |

| bit 0         |                                                                                              | s the RB po                   | •             |              |                  |             |                |            |  |  |

|               |                                                                                              | es the RB po                  |               |              |                  |             |                |            |  |  |

| bit 2         | TOIF: TMR                                                                                    | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |

|               |                                                                                              |                               |               |              | eared in softwa  | re)         |                |            |  |  |

|               |                                                                                              | register did                  |               |              |                  |             |                |            |  |  |

| bit 1         |                                                                                              | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |

|               |                                                                                              | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |

| bit 0         |                                                                                              | Port Change                   | •             |              |                  |             |                |            |  |  |

|               |                                                                                              | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |

|               |                                                                                              | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |

|               |                                                                                              | be cleared in<br>of the RB7:R | ,             | ve changed   | stato            |             |                |            |  |  |

|               |                                                                                              |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |

|               | Legend:                                                                                      |                               |               |              |                  |             |                |            |  |  |

|               | R = Reada                                                                                    | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |

|               | - n = Value                                                                                  |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |

|               |                                                                                              |                               |               |              |                  |             |                | -          |  |  |

2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R-0                                         | R-0                                          | R/W-0                                  | R/W-0         | R/W-0          | R/W-0       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------|---------------|----------------|-------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PSPIF <sup>(1)</sup>                                                                      | ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RCIF                                        | TXIF                                         | SSPIF                                  | CCP1IF        | TMR2IF         | TMR1IF      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 7                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                                              |                                        |               |                | bit 0       |  |  |  |  |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           | or a write o                                                                                                                                                                                                                                                                                                                                                                                                                                                              | peration has                                |                                              | rupt Flag bit<br>e (must be c          | leared in sof | ítware)        |             |  |  |  |  |

| bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 = An A/D                                                                                | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed<br>0 = The A/D conversion is not complete                                                                                                                                                                                                                                                                                                                                                       |                                             |                                              |                                        |               |                |             |  |  |  |  |

| bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 = The US                                                                                | <b>RCIF</b> : USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                                                                                                           |                                             |                                              |                                        |               |                |             |  |  |  |  |

| bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TXIF: USAI<br>1 = The US                                                                  | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                                                                                                                        |                                             |                                              |                                        |               |                |             |  |  |  |  |

| bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 = The SSI<br>from the<br>• SPI<br>- A<br>• I <sup>2</sup> C S                           | P interrupt o<br>e Interrupt S<br>A transmiss<br>Slave<br>A transmiss                                                                                                                                                                                                                                                                                                                                                                                                     |                                             | s occurred, a<br>tine. The co<br>n has taken | and must be<br>nditions that<br>place. | cleared in so |                | e returning |  |  |  |  |

| <ul> <li>A transmission/reception has taken place.</li> <li>The initiated START condition was completed by the SSP module.</li> <li>The initiated STOP condition was completed by the SSP module.</li> <li>The initiated Restart condition was completed by the SSP module.</li> <li>The initiated Acknowledge condition was completed by the SSP m</li> <li>A START condition occurred while the SSP module was idle (Multi-I</li> <li>A STOP condition occurred while the SSP module was idle (Multi-I</li> </ul> |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                                              |                                        |               |                | r system).  |  |  |  |  |

| bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           | <ul> <li>0 = No SSP interrupt condition has occurred.</li> <li>CCP1IF: CCP1 Interrupt Flag bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |                                             |                                              |                                        |               |                |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 = A TMR<br>0 = No TMF<br><u>Compare m</u><br>1 = A TMR<br>0 = No TMF<br><u>PWM mode</u> | CCP11F: CCP1 Interrupt Flag bit         Capture mode:         1 = A TMR1 register capture occurred (must be cleared in software)         0 = No TMR1 register capture occurred         Compare mode:         1 = A TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred         PWM mode:         Unused in this mode |                                             |                                              |                                        |               |                |             |  |  |  |  |

| bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 = TMR2 t                                                                                | o PR2 mate                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 Match Inte<br>ch occurred<br>natch occur  | (must be cle                                 | it<br>eared in soft                    | ware)         |                |             |  |  |  |  |

| bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 = TMR1 r                                                                                | egister ove                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ow Interrupt<br>rflowed (mu<br>not overflow | st be cleare                                 | d in software                          | e)            |                |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Note 1: P                                                                                 | SPIF is res                                                                                                                                                                                                                                                                                                                                                                                                                                                               | erved on PI                                 | C16F873/87                                   | 76 devices; a                          | always maint  | ain this bit c | lear.       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Legend:                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |                                              |                                        |               |                |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R = Reada                                                                                 | ole bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W = Writat                                  |                                              | U = Unimp                              | lemented bit  | t, read as '0' |             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - n = Value                                                                               | at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is                                | set                                          | '0' = Bit is                           | cleared       | x = Bit is ur  | nknown      |  |  |  |  |

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

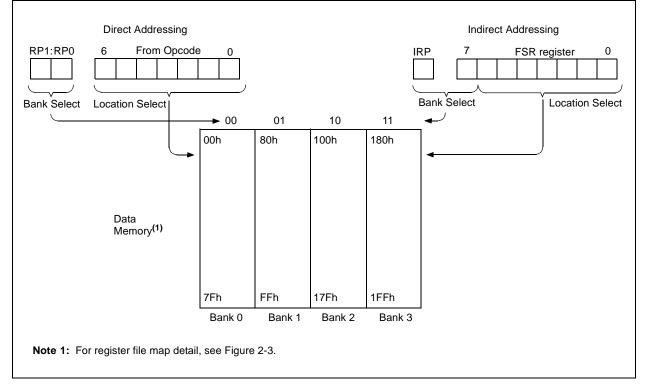

#### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

#### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

| Name                   | Bit# | Buffer                | Function                                                                                                                                          |

|------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 3-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

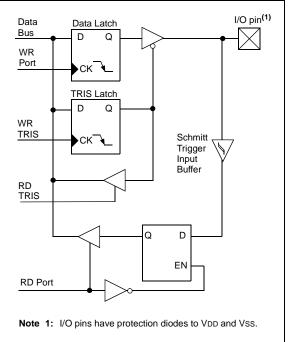

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

#### FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                              |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| REU/RD/ANS | bito | 51/112 /              | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE [ | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

| REGISTER 0-1: | CUPICON                                                                                                            | CCPTCON REGISTER/CCP2CON REGISTER (ADDRESS: 1/11/1011)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |              |          |             |              |        |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|----------|-------------|--------------|--------|--|--|--|--|

|               | U-0                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0      | R/W-0        | R/W-0    | R/W-0       | R/W-0        | R/W-0  |  |  |  |  |

|               | —                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CCPxX      | CCPxY        | CCPxM3   | CCPxM2      | CCPxM1       | CCPxM0 |  |  |  |  |

|               | bit 7                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |              |          |             |              | bit 0  |  |  |  |  |

|               |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |              |          |             |              |        |  |  |  |  |

| bit 7-6       | •                                                                                                                  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |              |          |             |              |        |  |  |  |  |

| bit 5-4       |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Least Sign | ificant bits |          |             |              |        |  |  |  |  |

|               | <u>Capture m</u><br>Unused                                                                                         | ode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |              |          |             |              |        |  |  |  |  |

|               | <u>Compare n</u><br>Unused                                                                                         | node:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |              |          |             |              |        |  |  |  |  |

|               |                                                                                                                    | <u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |              |          |             |              |        |  |  |  |  |

| bit 3-0       | CCPxM3:C                                                                                                           | CPxM0: C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CPx Mode S | Select bits  |          |             |              |        |  |  |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res | <ul> <li>CCPxM3:CCPxM0: CCPx Mode Select bits</li> <li>0000 = Capture/Compare/PWM disabled (resets CCPx module)</li> <li>0100 = Capture mode, every falling edge</li> <li>0101 = Capture mode, every rising edge</li> <li>0110 = Capture mode, every 4th rising edge</li> <li>0111 = Capture mode, every 16th rising edge</li> <li>1000 = Compare mode, set output on match (CCPxIF bit is set)</li> <li>1001 = Compare mode, clear output on match (CCPxIF bit is set)</li> <li>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)</li> <li>1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled)</li> <li>11xx = PWM mode</li> </ul> |            |              |          |             |              |        |  |  |  |  |

|               | Legend:                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |              |          |             |              |        |  |  |  |  |

|               | R = Reada                                                                                                          | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VV = V     | Vritable bit | U = Unim | plemented l | bit, read as | ʻ0'    |  |  |  |  |

'1' = Bit is set

- n = Value at POR

## REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

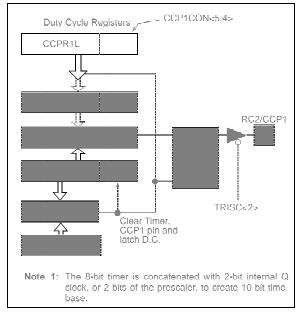

### 8.3 PWM Mode (PWM)

In Pulse Width Modulation mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force  |

|-------|-------------------------------------------|

|       | the CCP1 PWM output latch to the default  |

|       | low level. This is not the PORTC I/O data |

|       | latch.                                    |

Figure 8-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 8.3.3.

#### FIGURE 8-3: SIMPLIFIED PWM BLOCK DIAGRAM

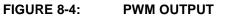

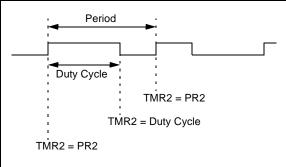

A PWM output (Figure 8-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### 8.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$PWM period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

Note: The Timer2 postscaler (see Section 7.1) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 8.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

PWM duty cycle =(CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitch-free PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock, or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the formula:

Resolution =

$$\frac{\log(\frac{FOSC}{FPWM})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

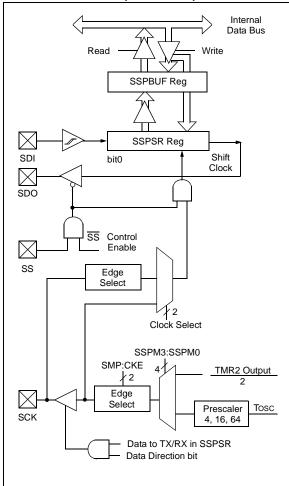

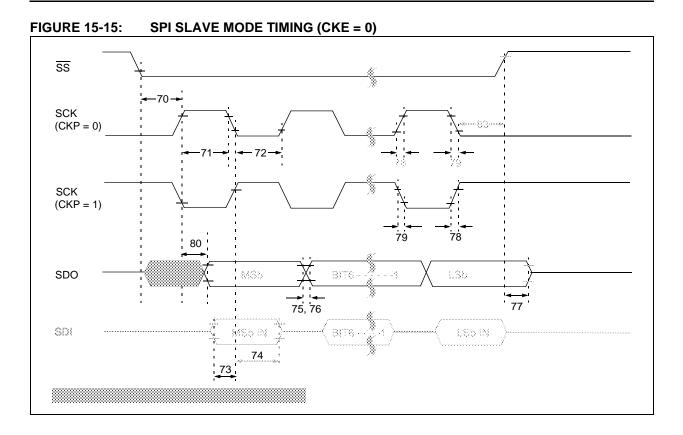

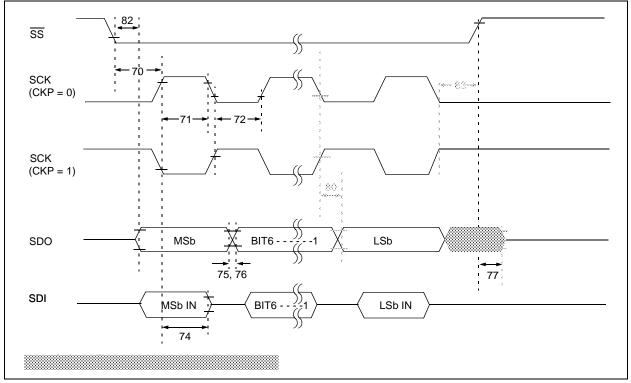

#### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

#### TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|---------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ve Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р       | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

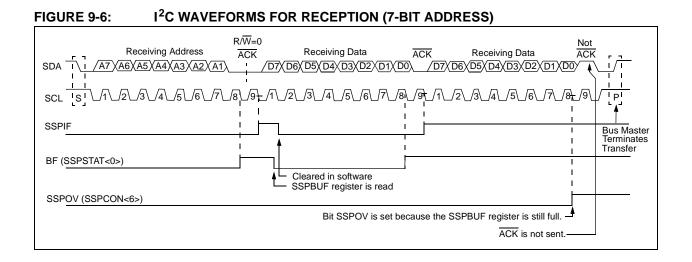

|    | its as Data<br>s Received | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|----|---------------------------|---------------------------|-----------------------|----------------------------------------|--|--|

| BF | SSPOV                     |                           | ruise                 | if enabled)                            |  |  |

| 0  | 0                         | Yes                       | Yes                   | Yes                                    |  |  |

| 1  | 0                         | No                        | No                    | Yes                                    |  |  |

| 1  | 1                         | No                        | No                    | Yes                                    |  |  |

| 0  | 1                         | Yes                       | No                    | Yes                                    |  |  |

TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 9.2.1.3 Slave Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7). An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting the CKP bit.

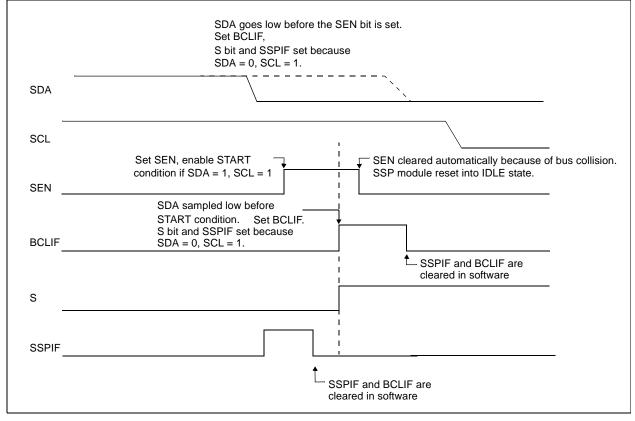

#### 9.2.18.1 Bus Collision During a START Condition

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 9-20).

- b) SCL is sampled low before SDA is asserted low (Figure 9-21).

During a START condition, both the SDA and the SCL pins are monitored. If either the SDA pin <u>or</u> the SCL pin is already low, then these events all occur:

- the START condition is aborted,

- and the BCLIF flag is set,

- <u>and</u> the SSP module is reset to its IDLE state (Figure 9-20).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 9-22). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0. During this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision, because the two masters must be allowed to arbitrate the first address following the START condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated START, or STOP conditions.

|                            | Q1 Q2 Q3 Q4                                                          | Q1 Q2 Q3 Q4       | Q1          |             | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      |

|----------------------------|----------------------------------------------------------------------|-------------------|-------------|-------------|--------------|-------------------|-------------------|------------------|

| OSC1                       | ·/~~~~/                                                              |                   |             | -           |              | <u>;</u> ~~~~~~   |                   |                  |

| CLKOUT <sup>(4)</sup>      | \/\                                                                  |                   | <u> </u>    | Tost(2)     | /            | \                 | ¦/ \              |                  |

| INT pin                    | · · ·                                                                | 1                 |             | · ·         |              | 1<br>1            | 1 I<br>1 I        |                  |

| INTF Flag<br>(INTCON<1>)   |                                                                      | י<br>י<br>י<br>י  | 4           | /           |              | Interrupt Latency | (2)               | <br>  <br> <br>  |

| GIE bit<br>(INTCON<7>)     | 1 I<br>1 I<br>1 I<br>1 I<br>1 I                                      | i<br>             | Processor i | n           |              | ·                 | 1 1<br>1 1<br>1 1 | ו<br>ו<br>ו<br>ו |

| INSTRUCTIO                 | N FLOW                                                               |                   |             | · ·         |              | 1                 | 1 1<br>1 1        | 1                |

| PC                         | Х РС Х                                                               | PC+1              | ХР          | C+2         | PC+2         | X PC + 2          | <u>X 0004h X</u>  | 0005h            |

| Instruction {<br>Fetched { | Inst(PC) = SLEEP                                                     | Inst(PC + 1)      |             | 1           | Inst(PC + 2) | 1<br>1<br>1       | Inst(0004h)       | Inst(0005h)      |

| Instruction                | Inst(PC - 1)                                                         | SLEEP             |             | ,<br>,<br>, | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h)      |

| 2: Tost                    | HS or LP oscillator n<br>τ = 1024Tosc (drawi<br>= '1' assumed. In th | ing not to scale) |             |             |              |                   |                   |                  |

## F

If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

## 12.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-8 shows which features are consumed by the background debugger.

| TABLE 12-8: DE | BUGGER RESOURCES |

|----------------|------------------|

|----------------|------------------|

| I/O pins       | RB6, RB7                                     |

|----------------|----------------------------------------------|

| Stack          | 1 level                                      |

| Program Memory | Address 0000h must be NOP                    |

|                | Last 100h words                              |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                               |

| Operation:       | See description below                                                                                                                                                                                         |

| Status Affected: | C                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

|                  |                                                                                                                                                                                                               |

## SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                             |