Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-04-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC® MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

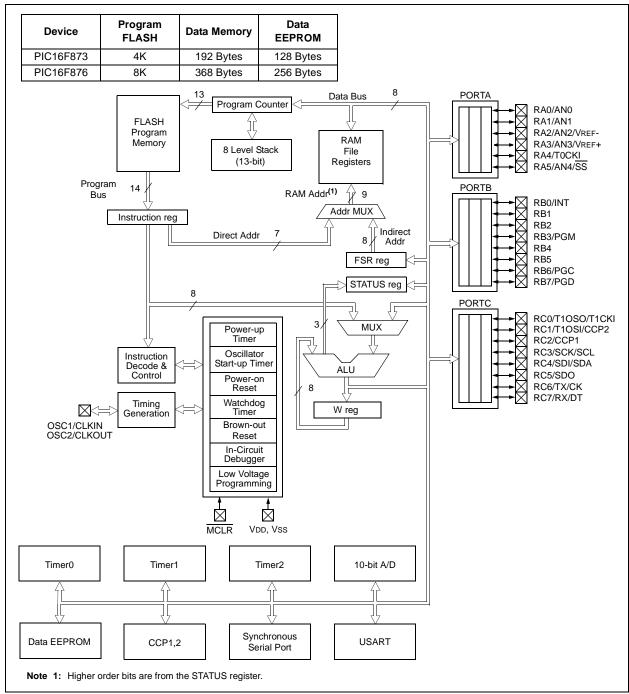

There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

FIGURE 1-1: PIC16F873 AND PIC16F876 BLOCK DIAGRAM

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |  |  |  |  |

|---------|------|--|--|--|--|

| 00      | 0    |  |  |  |  |

| 01      | 1    |  |  |  |  |

| 10      | 2    |  |  |  |  |

| 11      | 3    |  |  |  |  |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be    |

|-------|------------------------------------------|

|       | found in Section 4.0 of this data sheet. |

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| bit 7 |       | •     |       |       |       |       | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE  | T0IF  | INTF  | RBIF  |

| R/W-0 | R/W-x |

Note:

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

bit 6 **PEIE**: Peripheral Interrupt Enable bit

1 = Enables all unmasked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 **T0IE**: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 **T0IF**: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state; a mismatch condition will continue to set the bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared (must be cleared in software).

0 = None of the RB7:RB4 pins have changed state

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

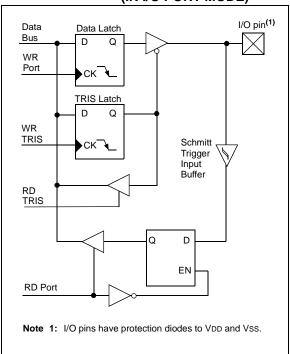

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

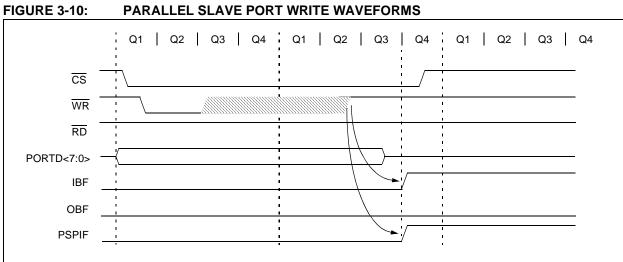

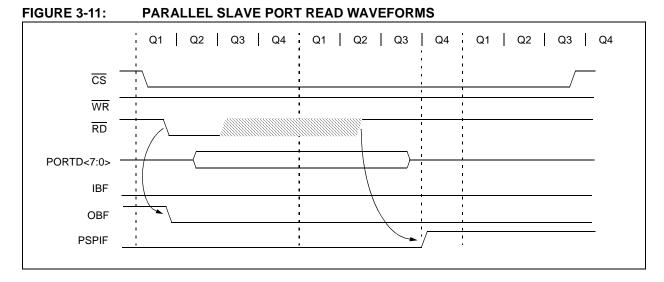

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

## FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

TABLE 3-9: PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                                    |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or read control input in Parallel Slave Port mode or analog input:         RD         1 = Idle         0 = Read operation. Contents of PORTD register are output to PORTD I/O pins (if chip selected)     </li> </ul> |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:</li> <li>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul>  |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:  CS  1 = Device is not selected  0 = Device is selected                                                                                              |

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1      | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|------------|-----------|-----------------------|---------------------------------|

| 09h     | PORTE  | _     |       | _     | _       | _     | RE2     | RE1        | RE0       | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE I | Data Direc | tion Bits | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | _     | _     | _       | PCFG3 | PCFG2   | PCFG1      | PCFG0     | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

**TABLE 3-11:** REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                                             | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|---------------------------------------------------|-------|-------|---------|-------|---------|-------------|---------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data Latch when written: Port pins when read |       |       |         |       |         |             |         | xxxx xxxx             | uuuu uuuu                       |

| 09h     | PORTE  | _                                                 | _     | _     | _       | _     | RE2     | RE1         | RE0     | xxx                   | uuu                             |

| 89h     | TRISE  | IBF                                               | OBF   | IBOV  | PSPMODE | _     | PORTE D | ata Directi | on Bits | 0000 -111             | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup>                              | ADIF  | RCIF  | TXIF    | SSPIF | CCP1IF  | TMR2IF      | TMR1IF  | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup>                              | ADIE  | RCIE  | TXIE    | SSPIE | CCP1IE  | TMR2IE      | TMR1IE  | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                                              |       | _     | _       | PCFG3 | PCFG2   | PCFG1       | PCFG0   | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

## 4.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F87X device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

TABLE 4-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Cor | nfiguration | Bits | Moment Leastion    | Internal | Internal | ICSP Read | ICSP Write |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |

| 0   | 0           | х    | All program memory | Yes      | No       | No        | No         |

| 0   | 1           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 0   | 1           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 0   | 1           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 0   | 1           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 1   | 0           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 1   | 0           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |

TABLE 4-2: REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH

| Address                 | Name   | Bit 7  | Bit 6                                              | Bit 5  | Bit 4     | Bit 3        | Bit 2  | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|----------------------------------------------------|--------|-----------|--------------|--------|-------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE                                               | TOIE   | INTE      | RBIE         | TOIF   | INTF  | RBIF   | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPROM | EEPROM Address Register, Low Byte                  |        |           |              |        |       |        |                          | uuuu uuuu                       |

| 10Fh                    | EEADRH | _      | — — EEPROM Address, High Byte                      |        |           |              |        |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPROM | EEPROM Data Register, Low Byte                     |        |           |              |        |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | _      | _                                                  | EEPROI | M Data Re | egister, Hig | h Byte |       |        | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | _                                                  | _      | _         | WRERR        | WREN   | WR    | RD     | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPROM | EEPROM Control Register2 (not a physical register) |        |           |              |        |       |        | _                        | _                               |

| 8Dh                     | PIE2   | _      | (1)                                                | _      | EEIE      | BCLIE        | _      | _     | CCP2IE | -r-0 00                  | -r-0 00                         |

| 0Dh                     | PIR2   | _      | (1)                                                | _      | EEIF      | BCLIF        | _      | _     | CCP2IF | -r-0 00                  | -r-0 00                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'.

Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|--------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Fimer0 Module's Register |       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                     | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                   | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

| R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|---------|-------|-------|-------|-------|-------|-------|

| GCEN  | ACKSTAT | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit 7 |         |       |       |       |       |       | bit 0 |

bit 7 GCEN: General Call Enable bit (In I<sup>2</sup>C Slave mode only)

1 = Enable interrupt when a general call address (0000h) is received in the SSPSR

0 = General call address disabled

bit 6 **ACKSTAT**: Acknowledge Status bit (In I<sup>2</sup>C Master mode only)

In Master Transmit mode:

1 = Acknowledge was not received from slave

0 = Acknowledge was received from slave

bit 5 **ACKDT**: Acknowledge Data bit (In I<sup>2</sup>C Master mode only)

In Master Receive mode:

Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

1 = Not Acknowledge

0 = Acknowledge

bit 4 **ACKEN**: Acknowledge Sequence Enable bit (In I<sup>2</sup>C Master mode only)

In Master Receive mode:

1 = Initiate Acknowledge sequence on SDA and SCL pins and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence idle

bit 3 RCEN: Receive Enable bit (In I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for  $I^2C$

0 = Receive idle

bit 2 **PEN**: STOP Condition Enable bit (In I<sup>2</sup>C Master mode only)

**SCK Release Control:**

1 = Initiate STOP condition on SDA and SCL pins. Automatically cleared by hardware.

0 = STOP condition idle

bit 1 **RSEN**: Repeated START Condition Enable bit (In I<sup>2</sup>C Master mode only)

1 = Initiate Repeated START condition on SDA and SCL pins. Automatically cleared by hardware.

0 = Repeated START condition idle

bit 0 **SEN**: START Condition Enable bit (In I<sup>2</sup>C Master mode only)

1 = Initiate START condition on SDA and SCL pins. Automatically cleared by hardware.

0 = START condition idle

**Note:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the IDLE mode, this bit may not be set (no spooling), and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

| Legend:            |                  |                          |                  |

|--------------------|------------------|--------------------------|------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit,   | read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = | = Bit is unknown |

#### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

#### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                | Name    | Bit 7                  | Bit 6                                                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR,<br>WDT |

|------------------------|---------|------------------------|---------------------------------------------------------|-------|-------|-------|--------|--------|-----------|-----------------------|------------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE                                                    | TOIE  | INTE  | RBIE  | TOIF   | INTF   | RBIF      | 0000 000x             | 0000 000u                          |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup>   | ADIF                                                    | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000             | 0000 0000                          |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup>   | ADIE                                                    | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000             | 0000 0000                          |

| 0Dh                    | PIR2    | _                      | (2)                                                     | _     | EEIF  | BCLIF | _      | _      | CCP2IF    | -r-0 00               | -r-0 00                            |

| 8Dh                    | PIE2    | _                      | (2)                                                     | _     | EEIE  | BCLIE | _      | _      | CCP2IE    | -r-0 00               | -r-0 00                            |

| 13h                    | SSPBUF  | Synchrono              | ynchronous Serial Port Receive Buffer/Transmit Register |       |       |       |        |        |           | xxxx xxxx             | uuuu uuuu                          |

| 14h                    | SSPCON  | WCOL                   | SSPOV                                                   | SSPEN | CKP   | SSPM3 | SSPM2  | SSPM1  | SSPM0     | 0000 0000             | 0000 0000                          |

| 91h                    | SSPCON2 | GCEN                   | ACKSTAT                                                 | ACKDT | ACKEN | RCEN  | PEN    | RSEN   | SEN       | 0000 0000             | 0000 0000                          |

| 93h                    | SSPADD  | I <sup>2</sup> C Slave | <sup>2</sup> C Slave Address/Master Baud Rate Register  |       |       |       |        |        | 0000 0000 | 0000 0000             |                                    |

| 94h                    | SSPSTAT | SMP                    | CKE                                                     | D/A   | Р     | S     | R/W    | UA     | BF        | 0000 0000             | 0000 0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

Note 1: These bits are reserved on PIC16F873/876 devices; always maintain these bits clear.

<sup>2:</sup> These bits are reserved on these devices; always maintain these bits clear.

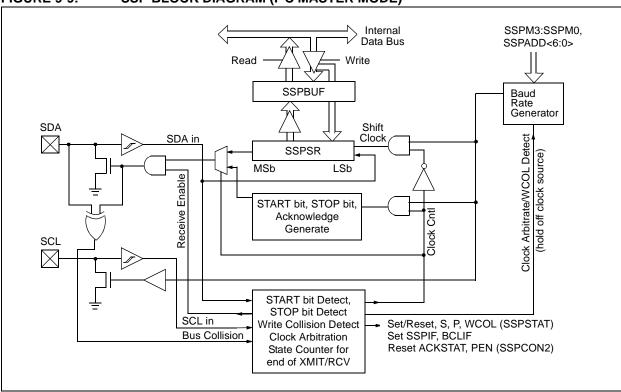

#### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- · START condition

- STOP condition

- Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated START

FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- · A START Condition

- A Repeated START Condition

- · An Acknowledge Condition

#### 9.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

**Note:** The SSP module must be in an IDLE state before the RCEN bit is set, or the RCEN bit will be disregarded.

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high), and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an Acknowledge bit at the end of reception, by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 9.2.12.1 BF Status Flag

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 9.2.12.2 SSPOV Status Flag

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 9.2.12.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

# 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

TABLE 10-1: BAUD RATE FORMULA

|   | SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|---|------|-------------------------------------------|----------------------------|

| Ī | 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

|   | 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7                        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|------------------------------|-------|-------|-------|-------|-------|-----------|-----------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC                         | TX9   | TXEN  | SYNC  | _     | BRGH  | TRMT      | TX9D      | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN                         | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR      | RX9D      | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Rate Generator Register |       |       |       |       |       | 0000 0000 | 0000 0000 |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

# PIC16F87X

**NOTES:**

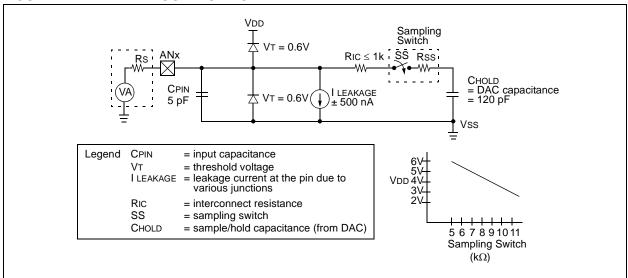

#### 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (RsS) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (RsS) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is  $10~\mathrm{k}\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC® MCU Mid-Range Reference Manual (DS33023).

#### **EQUATION 11-1: ACQUISITION TIME**

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

# 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHA       | RACTE | RISTICS                                 | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \le \text{TA} \le +70^{\circ}\text{C}$ for commercial Operating voltage VDD range as described in DC specification (Section 15.1) |      |         |       |                                                   |  |  |  |

|--------------|-------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-------|---------------------------------------------------|--|--|--|

| Param<br>No. | Sym   | Characteristic                          | Min                                                                                                                                                                                                                                                                                                            | Тур† | Max     | Units | Conditions                                        |  |  |  |

|              | VIL   | Input Low Voltage                       |                                                                                                                                                                                                                                                                                                                |      |         |       |                                                   |  |  |  |

|              |       | I/O ports                               |                                                                                                                                                                                                                                                                                                                |      |         |       |                                                   |  |  |  |

| D030         |       | with TTL buffer                         | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.15VDD | V     | For entire VDD range                              |  |  |  |

| D030A        |       |                                         | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                           |  |  |  |

| D031         |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.2Vdd  | V     |                                                   |  |  |  |

| D032         |       | MCLR, OSC1 (in RC mode)                 | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.2Vdd  | V     |                                                   |  |  |  |

| D033         |       | OSC1 (in XT, HS and LP)                 | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.3VDD  | V     | (Note 1)                                          |  |  |  |

|              |       | Ports RC3 and RC4                       |                                                                                                                                                                                                                                                                                                                | _    |         |       |                                                   |  |  |  |

| D034         |       | with Schmitt Trigger buffer             | Vss                                                                                                                                                                                                                                                                                                            | _    | 0.3VDD  | V     | For entire VDD range                              |  |  |  |

| D034A        |       | with SMBus                              | -0.5                                                                                                                                                                                                                                                                                                           | _    | 0.6     | V     | for VDD = 4.5 to 5.5V                             |  |  |  |

|              | VIH   | Input High Voltage                      |                                                                                                                                                                                                                                                                                                                |      | •       | •     |                                                   |  |  |  |

|              |       | I/O ports                               |                                                                                                                                                                                                                                                                                                                | _    |         |       |                                                   |  |  |  |

| D040         |       | with TTL buffer                         | 2.0                                                                                                                                                                                                                                                                                                            | _    | Vdd     | V     | $4.5V \le VDD \le 5.5V$                           |  |  |  |

| D040A        |       |                                         | 0.25VDD<br>+ 0.8V                                                                                                                                                                                                                                                                                              | _    | VDD     | V     | For entire VDD range                              |  |  |  |

| D041         |       | with Schmitt Trigger buffer             | 0.8VDD                                                                                                                                                                                                                                                                                                         | _    | Vdd     | V     | For entire VDD range                              |  |  |  |

| D042         |       | MCLR                                    | 0.8VDD                                                                                                                                                                                                                                                                                                         | _    | Vdd     | V     |                                                   |  |  |  |

| D042A        |       | OSC1 (XT, HS and LP)                    | 0.7Vdd                                                                                                                                                                                                                                                                                                         | _    | Vdd     | V     | (Note 1)                                          |  |  |  |

| D043         |       | OSC1 (in RC mode) Ports RC3 and RC4     | 0.9Vdd                                                                                                                                                                                                                                                                                                         | _    | VDD     | V     |                                                   |  |  |  |

| D044         |       | with Schmitt Trigger buffer             | 0.7Vdd                                                                                                                                                                                                                                                                                                         | _    | Vdd     | V     | For entire VDD range                              |  |  |  |

| D044A        |       | with SMBus                              | 1.4                                                                                                                                                                                                                                                                                                            | _    | 5.5     | V     | for VDD = 4.5 to 5.5V                             |  |  |  |

| D070         | IPURB | PORTB Weak Pull-up Current              | 50                                                                                                                                                                                                                                                                                                             | 250  | 400     | μА    | VDD = 5V, VPIN = VSS,<br>-40°C TO +85°C           |  |  |  |

|              | lıL   | Input Leakage Current <sup>(2, 3)</sup> |                                                                                                                                                                                                                                                                                                                |      | •       |       |                                                   |  |  |  |

| D060         |       | I/O ports                               | _                                                                                                                                                                                                                                                                                                              | _    | ±1      | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at hi-impedance          |  |  |  |

| D061         |       | MCLR, RA4/T0CKI                         | _                                                                                                                                                                                                                                                                                                              | _    | ±5      | μА    | Vss ≤ Vpin ≤ Vdd                                  |  |  |  |

| D063         |       | OSC1                                    | _                                                                                                                                                                                                                                                                                                              | _    | ±5      | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc configuration |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**<sup>3:</sup>** Negative current is defined as current sourced by the pin.

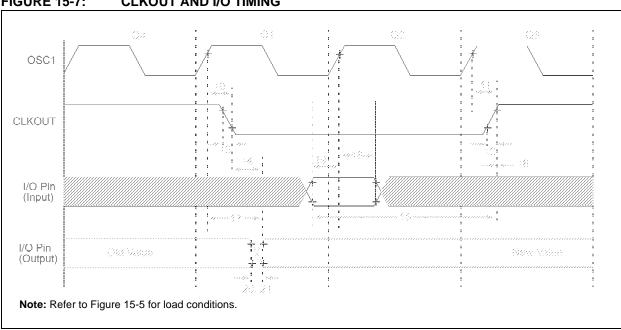

**FIGURE 15-7: CLKOUT AND I/O TIMING**

TABLE 15-2: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Symbol       | Charac                                | Min                    | Тур† | Max         | Units | Conditions |          |

|--------------|--------------|---------------------------------------|------------------------|------|-------------|-------|------------|----------|

| 10*          | TosH2ckL     | OSC1↑ to CLKOUT↓                      | _                      | 75   | 200         | ns    | (Note 1)   |          |

| 11*          | TosH2ck<br>H | OSC1↑ to CLKOUT↑                      | _                      | 75   | 200         | ns    | (Note 1)   |          |

| 12*          | TckR         | CLKOUT rise time                      |                        | _    | 35          | 100   | ns         | (Note 1) |

| 13*          | TckF         | CLKOUT fall time                      |                        | _    | 35          | 100   | ns         | (Note 1) |

| 14*          | TckL2ioV     | CLKOUT ↓ to Port out val              | _                      | _    | 0.5Tcy + 20 | ns    | (Note 1)   |          |

| 15*          | TioV2ckH     | Port in valid before CLKO             | Tosc + 200             | _    | _           | ns    | (Note 1)   |          |

| 16*          | TckH2iol     | Port in hold after CLKOUT             | 0                      | _    | _           | ns    | (Note 1)   |          |

| 17*          | TosH2ioV     | OSC1↑ (Q1 cycle) to<br>Port out valid |                        | _    | 100         | 255   | ns         |          |

| 18*          | TosH2iol     | OSC1↑ (Q2 cycle) to                   | Standard (F)           | 100  | _           | _     | ns         |          |

|              |              | Port input invalid (I/O in hold time) | Extended ( <b>LF</b> ) | 200  | _           | _     | ns         |          |

| 19*          | TioV2osH     | Port input valid to OSC11             | (I/O in setup time)    | 0    | _           | _     | ns         |          |

| 20*          | TioR         | Port output rise time                 | Standard (F)           | _    | 10          | 40    | ns         |          |

|              |              |                                       | Extended (LF)          | _    | _           | 145   | ns         |          |

| 21*          | TioF         | Port output fall time                 | Standard (F)           | _    | 10          | 40    | ns         |          |

|              |              |                                       | Extended (LF)          | _    | _           | 145   | ns         |          |

| 22††*        | Tinp         | INT pin high or low time              |                        | Tcy  | _           | _     | ns         |          |

| 23††*        | Trbp         | RB7:RB4 change INT high               | Tcy                    | _    | _           | ns    |            |          |

These parameters are characterized but not tested.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

## PIC16F87X

TABLE 15-7: SPI MODE REQUIREMENTS

| Param<br>No. | Symbol                | Characteristic                                              | Min                                           | Тур†        | Max      | Units     | Conditions |  |

|--------------|-----------------------|-------------------------------------------------------------|-----------------------------------------------|-------------|----------|-----------|------------|--|

| 70*          | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                                   | Тсу                                           | _           | _        | ns        |            |  |

| 71*          | TscH                  | SCK input high time (Slave mode)                            |                                               | Tcy + 20    | _        | _         | ns         |  |

| 72*          | TscL                  | SCK input low time (Slave mode)                             |                                               | Tcy + 20    | _        | _         | ns         |  |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK                         | 100                                           | _           | _        | ns        |            |  |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                     |                                               | 100         | _        | _         | ns         |  |

| 75*          | TdoR                  | SDO data output rise time                                   | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 76*          | TdoF                  | SDO data output fall time                                   |                                               | _           | 10       | 25        | ns         |  |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-impedance                              |                                               | 10          | _        | 50        | ns         |  |

| 78*          | TscR                  | SCK output rise time (Master mode) Standard(F) Extended(LF) |                                               |             | 10<br>25 | 25<br>50  | ns<br>ns   |  |

| 79*          | TscF                  | SCK output fall time (Master mode)                          |                                               | _           | 10       | 25        | ns         |  |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                        | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) |             | _        | 50<br>145 | ns         |  |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                           |                                               | Tcy         | _        | _         | ns         |  |

| 82*          | TssL2doV              | SDO data output valid after <del>SS</del> ↓ edge            |                                               | _           | _        | 50        | ns         |  |

| 83*          | TscH2ssH,<br>TscL2ssH | <del>1</del> .                                              |                                               | 1.5Tcy + 40 | _        | _         | ns         |  |

<sup>\*</sup> These parameters are characterized but not tested.

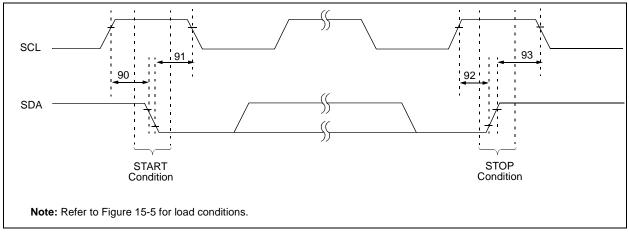

FIGURE 15-17: I<sup>2</sup>C BUS START/STOP BITS TIMING

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

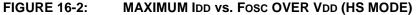

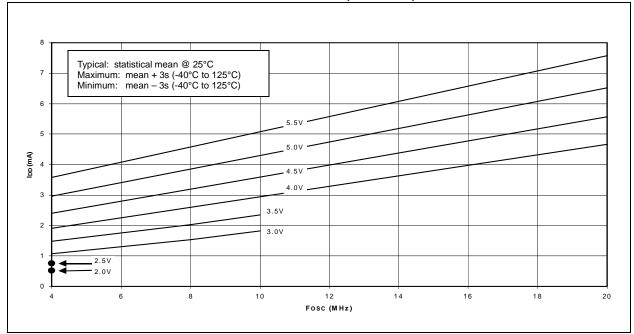

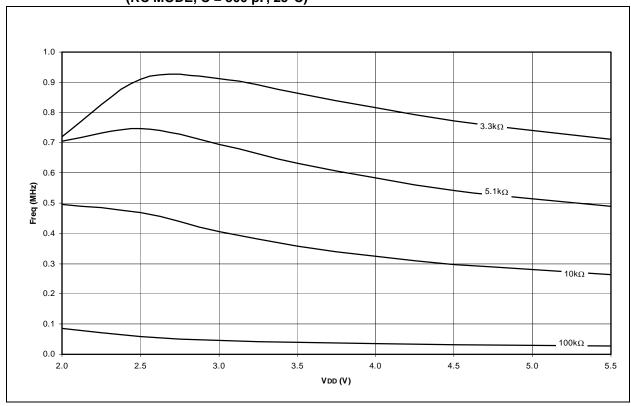

#### 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented is **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at  $25^{\circ}$ C. 'max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

**FIGURE 16-1:** TYPICAL IDD vs. Fosc OVER VDD (HS MODE) Typical: statistical mean @ 25°C Maximum: mean + 3s (-40°C to 125°C) Minimum: mean - 3s (-40°C to 125°C) lop (mA) 4 0 V 3.5V 3.0V 2.5V 6 10 12 14 16 18 20 Fosc (MHz)

FIGURE 16-9: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 300 pF, 25°C)

FIGURE 16-10: IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

# PIC16F87X

## W

| Wake-up from SLEEP119, 132                   |

|----------------------------------------------|

| Interrupts                                   |

| MCLR Reset126                                |

| Timing Diagram133                            |

| WDT Reset126                                 |

| Watchdog Timer (WDT)119, 131                 |

| Block Diagram131                             |

| Enable (WDTE Bit)131                         |

| Postscaler. See Postscaler, WDT              |

| Programming Considerations131                |

| RC Oscillator131                             |

| Time-out Period131                           |

| WDT Reset, Normal Operation 123, 125, 126    |

| WDT Reset, SLEEP 123, 125, 126               |

| Waveform for General Call Address Sequence76 |

| WCOL67, 80, 82, 84, 86, 87                   |

| WCOL Status Flag80                           |

| Write Collision Detect bit, WCOL67           |

| Write Verify                                 |

| Data EEPROM and FLASH Program Memory45       |

| WWW, On-Line Support4                        |