Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 × 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FI | GU | IRF | 2-3      | - |

|----|----|-----|----------|---|

|    |    |     | <u> </u> |   |

# PIC16F877/876 REGISTER FILE MAP

| Indirect addr.(*)              | 00h        | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 18              |

|--------------------------------|------------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----------------|

| TMR0                           | 01h        | OPTION_REG                                 | 81h        | TMR0                                       | 101h         | OPTION_REG                                 | 18              |

| PCL                            | 02h        | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182             |

| STATUS                         | 03h        | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183             |

| FSR                            | 04h        | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184             |

| PORTA                          | 05h        | TRISA                                      | 85h        |                                            | 105h         |                                            | 18              |

| PORTB                          | 06h        | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186             |

| PORTC                          | 07h        | TRISC                                      | 87h        |                                            | 107h         |                                            | 187             |

| PORTD <sup>(1)</sup>           | 08h        | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188             |

| PORTE <sup>(1)</sup>           | 09h        | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h         |                                            | 189             |

| PCLATH                         | 0Ah        | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18/             |

| INTCON                         | 0Bh        | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18              |

| PIR1                           | 0Ch        | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch         | EECON1                                     | 180             |

| PIR2                           | 0Dh        | PIE2                                       | 8Dh        | EEADR                                      | 10Dh         | EECON2                                     | 181             |

| TMR1L                          | 0Eh        | PCON                                       | 8Eh        | EEDATH                                     | 10Eh         | Reserved <sup>(2)</sup>                    | 18              |

| TMR1H                          | 0Fh        |                                            | 8Fh        | EEADRH                                     | 10Fh         | Reserved <sup>(2)</sup>                    | 18              |

| T1CON                          | 10h        |                                            | 90h        |                                            | 110h         |                                            | 190             |

| TMR2                           | 11h        | SSPCON2                                    | 91h        |                                            | 111h         |                                            | 19 <sup>.</sup> |

| T2CON                          | 12h        | PR2                                        | 92h        |                                            | 112h         |                                            | 192             |

| SSPBUF                         | 13h        | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193             |

| SSPCON                         | 14h        | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194             |

| CCPR1L                         | 15h        |                                            | 95h        |                                            | 115h         |                                            | 19              |

| CCPR1H                         | 16h        |                                            | 96h        |                                            | 116h         |                                            | 196             |

| CCP1CON                        | 17h        |                                            | 97h        | General                                    | 117h         | General                                    | 197             |

| RCSTA                          | 18h        | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198             |

| TXREG                          | 19h        | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199             |

| RCREG                          | 1Ah        |                                            | 9Ah        | -                                          | 11Ah         |                                            | 19/             |

| CCPR2L                         | 1Bh        |                                            | 9Bh        |                                            | 11Bh         |                                            | 198             |

| CCPR2H                         | 1Ch        |                                            | 9Ch        |                                            | 11Ch         |                                            | 190             |

| CCP2CON                        | 1Dh        |                                            | 9Dh        |                                            | 11Dh         |                                            | 19[             |

| ADRESH                         | 1Eh        | ADRESL                                     | 9Eh        |                                            | 11Eh         |                                            | 19              |

| ADCON0                         | 1Fh        | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 191             |

|                                | 20h        |                                            | A0h        |                                            | 120h         |                                            | 1A              |

| General<br>Purpose<br>Register |            | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |                 |

| 96 Bytes                       |            | UU Dyico                                   | EFh        | 00 Dytos                                   | 16Fh         | 00 Dyi00                                   | 1EI             |

|                                | 7Fh        | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | 1F(<br>1Fl      |

| Bank 0                         |            | Bank 1                                     | FFII       | Bank 2                                     | /. !!        | Bank 3                                     | 11.1            |

| 1 1 m 1 m m 1                  | بارار منعم | a memory location                          | a          |                                            |              |                                            |                 |

2: These registers are reserved, maintain these registers clear.

#### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt, the SSP bus collision interrupt and the EEPROM write operation interrupt.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

R = Readable bit

- n = Value at POR

| U-0   | R/W-0    | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|----------|-----|-------|-------|-----|-----|--------|

| -     | Reserved | —   | EEIF  | BCLIF | —   | —   | CCP2IF |

| bit 7 |          |     |       |       |     |     | bit 0  |

| Unimplemented: Read as '0'                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                             |

| Reserved: Always maintain this bit clear                                                                                                                                    |

| Unimplemented: Read as '0'                                                                                                                                                  |

| EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                             |

| <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                   |

| BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                     |

| <ul> <li>1 = A bus collision has occurred in the SSP, when configured for I2C Master mode</li> <li>0 = No bus collision has occurred</li> </ul>                             |

| Unimplemented: Read as '0'                                                                                                                                                  |

| CCP2IF: CCP2 Interrupt Flag bit                                                                                                                                             |

| Capture mode:                                                                                                                                                               |

| <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> <li><u>Compare mode:</u></li> </ul>         |

| <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> <li><u>PWM mode:</u></li> </ul> |

| Unused<br>Leaend:                                                                                                                                                           |

|                                                                                                                                                                             |

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

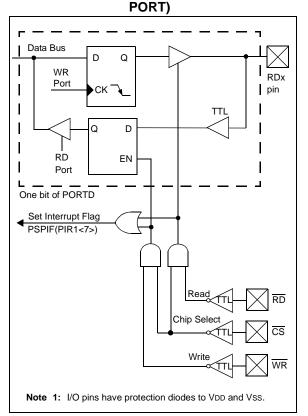

# 3.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873 or PIC16F876.

PORTD operates as an 8-bit wide Parallel Slave Port or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin RE0/RD and WR control input pin RE1/WR.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output, and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 3-10). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 3-11), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

# PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE

# 4.4 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program the memory and insert value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

#### EXAMPLE 4-3: FLASH PROGRAM READ

| BSF   | STATUS, RP1   | ;                        |

|-------|---------------|--------------------------|

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | ADDRL, W      | ;Write the               |

| MOVWF | EEADR         | ;address bytes           |

| MOVF  | ADDRH,W       | ;for the desired         |

| MOVWF | EEADRH        | ;address to read         |

| BSF   | STATUS, RPO   | ;Bank 3                  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |

| BSF   | EECON1, RD    | ;Start read operation    |

| NOP   |               | ;Required two NOPs       |

| NOP   |               | ;                        |

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |

| MOVWF | DATAL         | ;                        |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |

| MOVWF | DATAH         | ;                        |

|       |               |                          |

# 4.5 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory, is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 4-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

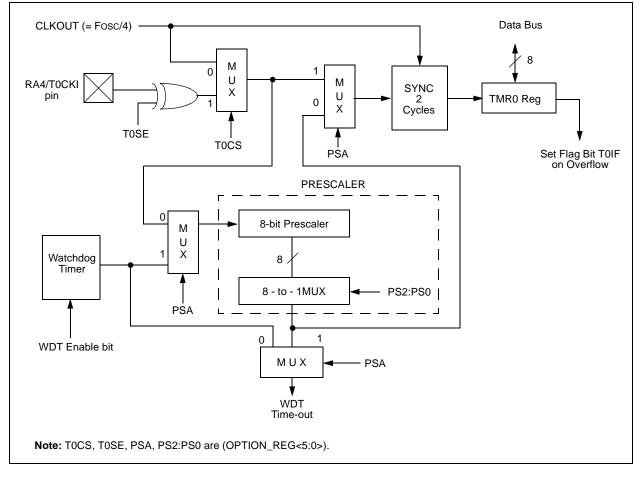

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

# 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

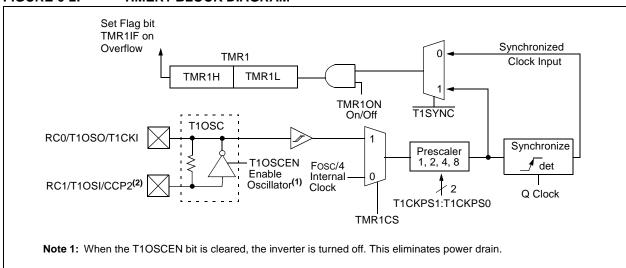

# 6.1 Timer1 Operation in Timer Mode

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect, since the internal clock is always in sync.

# 6.2 Timer1 Counter Operation

Timer1 may operate in either a Synchronous, or an Asynchronous mode, depending on the setting of the TMR1CS bit.

When Timer1 is being incremented via an external source, increments occur on a rising edge. After Timer1 is enabled in Counter mode, the module must first have a falling edge before the counter begins to increment.

# FIGURE 6-1: TIMER1 INCREMENTING EDGE

#### 6.3 Timer1 Operation in Synchronized Counter Mode

Counter mode is selected by setting bit TMR1CS. In this mode, the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2, when bit T1OSCEN is set, or on pin RC0/T1OSO/T1CKI, when bit T1OSCEN is cleared.

If  $\overline{\text{T1SYNC}}$  is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut-off. The prescaler, however, will continue to increment.

# FIGURE 6-2: TIMER1 BLOCK DIAGRAM

# 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

# 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6                    | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|----------------------|--------------------------|---------|---------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                     | TOIE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                     | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                     | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 Mod           | Timer2 Module's Register |         |         |         |        |         |         |                          | 0000 0000                       |

| 12h                   | T2CON  | _                    | TOUTPS3                  | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri          | imer2 Period Register    |         |         |         |        |         |         |                          | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

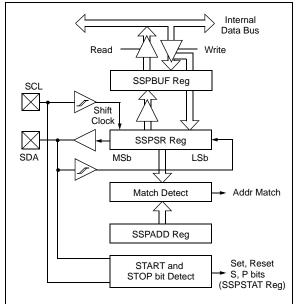

# 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware, to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

#### FIGURE 9-5:

I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C firmware modes (provided for compatibility to other mid-range products)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode. Pull-up resistors must be provided externally to the SCL and SDA pins for the proper operation of the  $I^2C$  module.

The CKE bit (SSPSTAT<6:7>) sets the levels of the SDA and SCL pins in either Master or Slave mode. When CKE = 1, the levels will conform to the SMBus specification. When CKE = 0, the levels will conform to the  $I^2C$  specification.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written to, or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

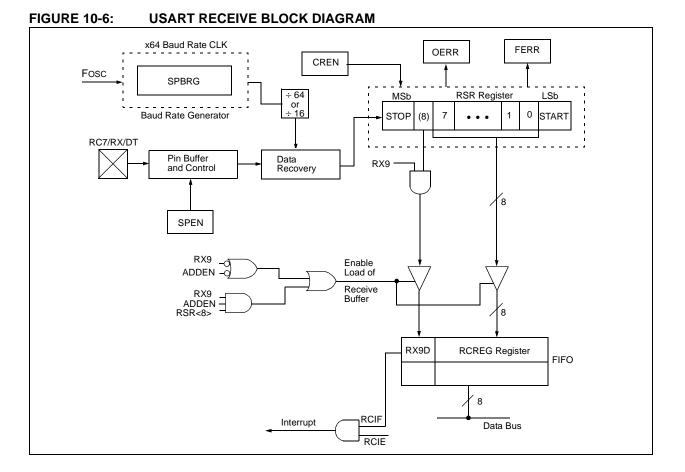

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

# 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

# TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock                | AD Clock Source (TAD) |          |  |  |  |

|-------------------------|-----------------------|----------|--|--|--|

| Operation               | ADCS1:ADCS0           | Max.     |  |  |  |

| 2Tosc                   | 0 0                   | 1.25 MHz |  |  |  |

| 8Tosc                   | 01                    | 5 MHz    |  |  |  |

| 32Tosc                  | 10                    | 20 MHz   |  |  |  |

| RC <sup>(1, 2, 3)</sup> | 11                    | (Note 1) |  |  |  |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s, but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 15.1 and 15.2).

# 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

| Note | 1: When reading the port register, any pin   |

|------|----------------------------------------------|

|      | configured as an analog input channel will   |

|      | read as cleared (a low level). Pins config-  |

|      | ured as digital inputs will convert an ana-  |

|      | log input. Analog levels on a digitally      |

|      | configured input will not affect the conver- |

|      | sion accuracy.                               |

2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

# 12.3 **RESET**

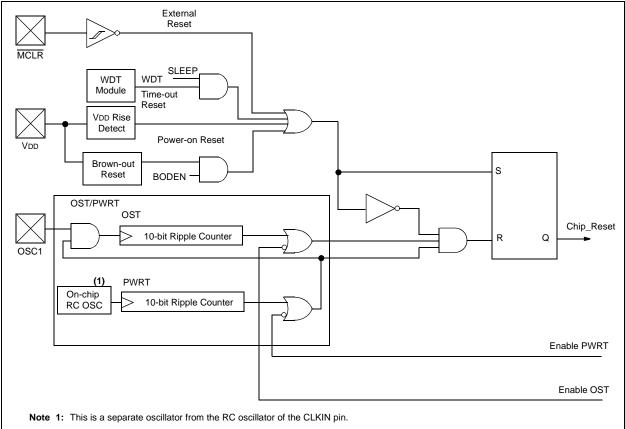

The PIC16F87X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (during normal operation)

- WDT Wake-up (during SLEEP)

- Brown-out Reset (BOR)

Some registers are not affected in any RESET condition. Their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset (POR), on the MCLR and WDT Reset, on MCLR Reset during SLEEP, and Brown-out Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different RESET situations as indicated in Table 12-4. These bits are used in software to determine the nature of the RESET. See Table 12-6 for a full description of RESET states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-4.

These devices have a MCLR noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

# 14.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

# 14.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC MCU series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

# 14.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC MCU microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

# 14.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

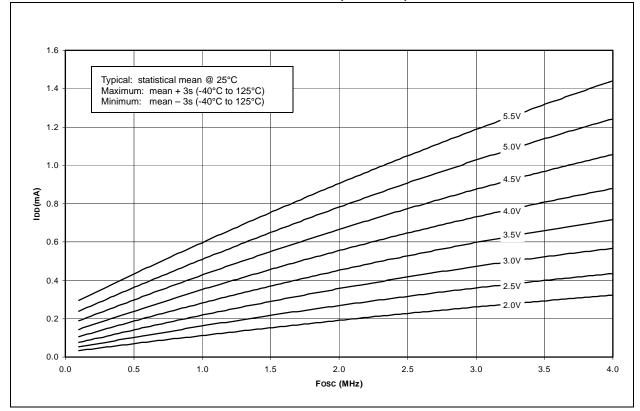

# 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |       |                                            |  |  |  |

|--------------------------------------------------------------------|--------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------------|--|--|--|

| Param<br>No.                                                       | Symbol | Symbol Characteristic/<br>Device                                 |                                                                                                                          | Тур† | Max  | Units | Conditions                                 |  |  |  |

|                                                                    | Vdd    | Supply Voltage                                                   | upply Voltage                                                                                                            |      |      |       |                                            |  |  |  |

| D001                                                               |        |                                                                  | 4.0                                                                                                                      | —    | 5.5  | V     | LP, XT, RC osc configuration               |  |  |  |

| D001A                                                              |        |                                                                  | 4.5                                                                                                                      |      | 5.5  | V     | HS osc configuration                       |  |  |  |

| D001A                                                              |        |                                                                  | VBOR                                                                                                                     |      | 5.5  | V     | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |  |  |  |

| D002                                                               | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                                                                                        | 1.5  | _    | V     |                                            |  |  |  |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                        | Vss  | _    | V     | See section on Power-on Reset for details  |  |  |  |

| D004                                                               | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                     | —    | —    | V/ms  | See section on Power-on Reset for details  |  |  |  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                                                                                      | 4.0  | 4.35 | V     | BODEN bit in configuration word<br>enabled |  |  |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

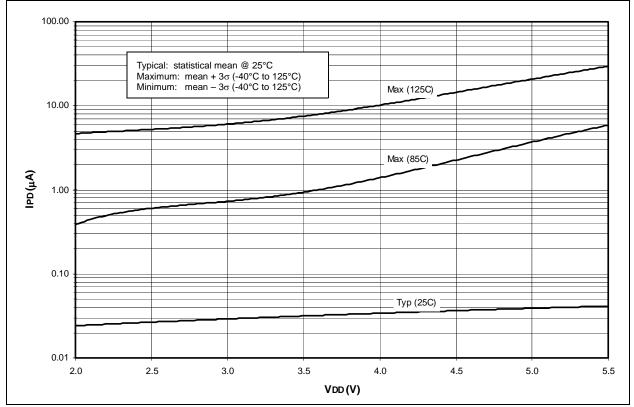

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# PIC16F87X

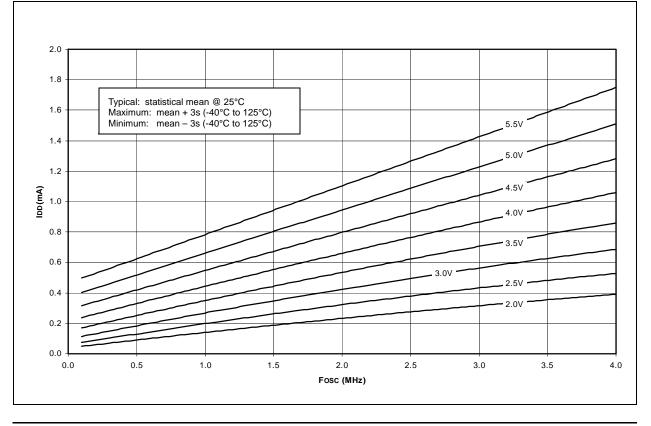

# FIGURE 16-3: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

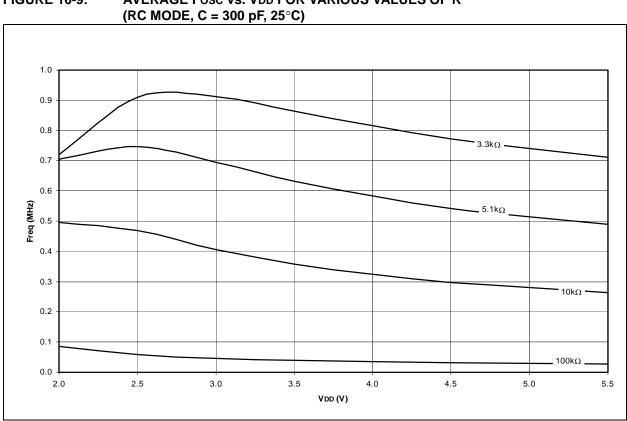

**FIGURE 16-9:** AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R

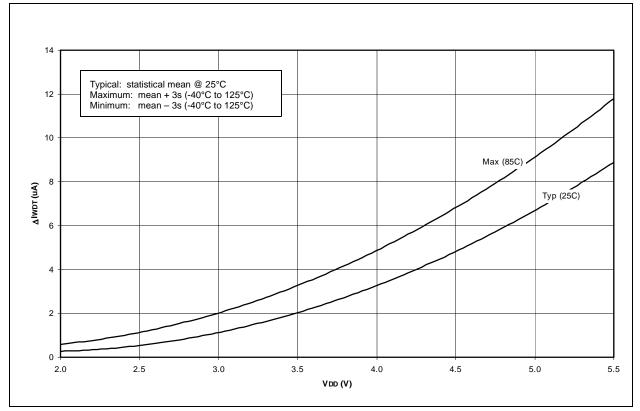

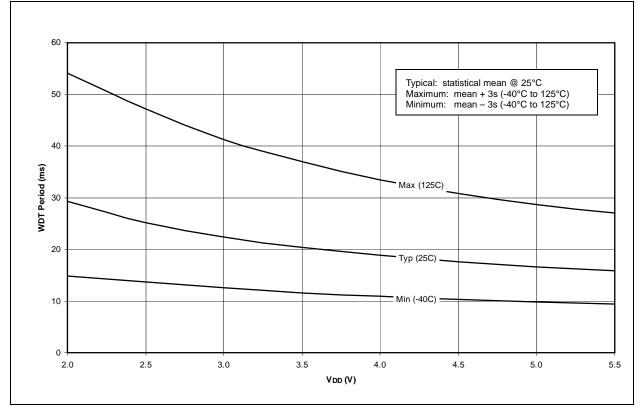

FIGURE 16-13: TYPICAL AND MAXIMUM AlwDT vs. VDD OVER TEMPERATURE

© 1998-2013 Microchip Technology Inc.

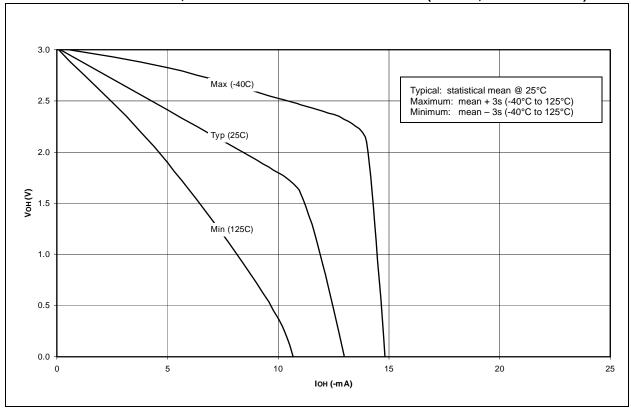

FIGURE 16-17: TYPICAL, MINIMUM AND MAXIMUM VOH vs. IOH (VDD=3V, -40°C TO 125°C)

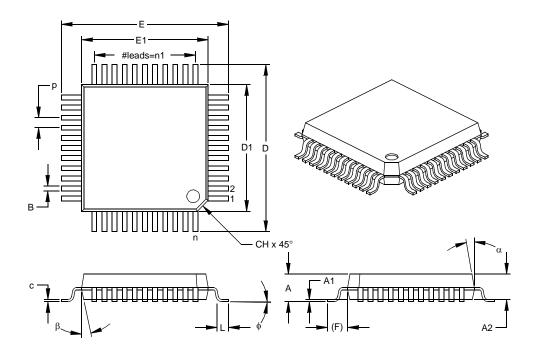

# 44-Lead Plastic Metric Quad Flatpack (PQ) 10x10x2 mm Body, 1.6/0.15 mm Lead Form (MQFP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      |      |      | MILLIMETERS* |       |       |  |

|--------------------------|-------|------|------|------|--------------|-------|-------|--|

| Dimension Limits         |       | MIN  | NOM  | MAX  | MIN          | NOM   | MAX   |  |

| Number of Pins           | n     |      | 44   |      |              | 44    |       |  |

| Pitch                    | р     |      | .031 |      |              | 0.80  |       |  |

| Pins per Side            | n1    |      | 11   |      |              | 11    |       |  |

| Overall Height           | А     | .079 | .086 | .093 | 2.00         | 2.18  | 2.35  |  |

| Molded Package Thickness | A2    | .077 | .080 | .083 | 1.95         | 2.03  | 2.10  |  |

| Standoff §               | A1    | .002 | .006 | .010 | 0.05         | 0.15  | 0.25  |  |

| Foot Length              | L     | .029 | .035 | .041 | 0.73         | 0.88  | 1.03  |  |

| Footprint (Reference)    | (F)   |      | .063 |      |              | 1.60  |       |  |

| Foot Angle               | ø     | 0    | 3.5  | 7    | 0            | 3.5   | 7     |  |

| Overall Width            | E     | .510 | .520 | .530 | 12.95        | 13.20 | 13.45 |  |

| Overall Length           | D     | .510 | .520 | .530 | 12.95        | 13.20 | 13.45 |  |

| Molded Package Width     | E1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Molded Package Length    | D1    | .390 | .394 | .398 | 9.90         | 10.00 | 10.10 |  |

| Lead Thickness           | С     | .005 | .007 | .009 | 0.13         | 0.18  | 0.23  |  |

| Lead Width               | В     | .012 | .015 | .018 | 0.30         | 0.38  | 0.45  |  |

| Pin 1 Corner Chamfer     | СН    | .025 | .035 | .045 | 0.64         | 0.89  | 1.14  |  |

| Mold Draft Angle Top     | α     | 5    | 10   | 15   | 5            | 10    | 15    |  |

| Mold Draft Angle Bottom  | β     | 5    | 10   | 15   | 5            | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-022 Drawing No. C04-071

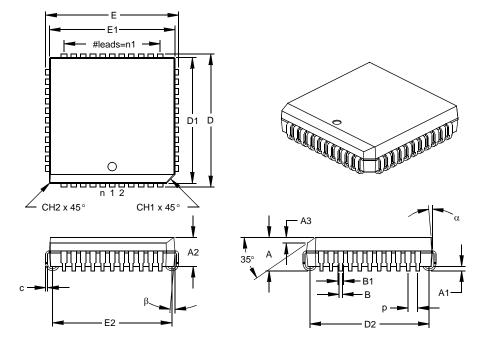

# 44-Lead Plastic Leaded Chip Carrier (L) – Square (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          |     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----|---------|------|-------------|-------|-------|-------|

| Dimension                | MIN | NOM     | MAX  | MIN         | NOM   | MAX   |       |

| Number of Pins           | n   |         | 44   |             |       | 44    |       |

| Pitch                    | р   |         | .050 |             |       | 1.27  |       |

| Pins per Side            | n1  |         | 11   |             |       | 11    |       |

| Overall Height           | А   | .165    | .173 | .180        | 4.19  | 4.39  | 4.57  |

| Molded Package Thickness | A2  | .145    | .153 | .160        | 3.68  | 3.87  | 4.06  |

| Standoff §               | A1  | .020    | .028 | .035        | 0.51  | 0.71  | 0.89  |

| Side 1 Chamfer Height    | A3  | .024    | .029 | .034        | 0.61  | 0.74  | 0.86  |

| Corner Chamfer 1         | CH1 | .040    | .045 | .050        | 1.02  | 1.14  | 1.27  |

| Corner Chamfer (others)  | CH2 | .000    | .005 | .010        | 0.00  | 0.13  | 0.25  |

| Overall Width            | Е   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Overall Length           | D   | .685    | .690 | .695        | 17.40 | 17.53 | 17.65 |

| Molded Package Width     | E1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Molded Package Length    | D1  | .650    | .653 | .656        | 16.51 | 16.59 | 16.66 |

| Footprint Width          | E2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Footprint Length         | D2  | .590    | .620 | .630        | 14.99 | 15.75 | 16.00 |

| Lead Thickness           | С   | .008    | .011 | .013        | 0.20  | 0.27  | 0.33  |

| Upper Lead Width         | B1  | .026    | .029 | .032        | 0.66  | 0.74  | 0.81  |

| Lower Lead Width         | В   | .013    | .020 | .021        | 0.33  | 0.51  | 0.53  |

| Mold Draft Angle Top     | α   | 0       | 5    | 10          | 0     | 5     | 10    |

| Mold Draft Angle Bottom  | β   | 0       | 5    | 10          | 0     | 5     | 10    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-047

Drawing No. C04-048

| PWM Mode61                                   |

|----------------------------------------------|

| Block Diagram61                              |

| Duty Cycle61                                 |

| Example Frequencies/Resolutions (Table)62    |

| PWM Period61                                 |

| Special Event Trigger and A/D Conversions60  |

| CCP. See Capture/Compare/PWM                 |

| CCP1CON                                      |

| CCP2CON                                      |

| CCPR1H Register 15, 17, 57                   |

| CCPR1L Register 17, 57                       |

| CCPR2H Register                              |

| CCPR2L Register 15, 17                       |

| CCPxM0 bit58                                 |

| CCPxM1 bit58                                 |

| CCPxM2 bit58                                 |

| CCPxM3 bit58                                 |

| CCPxX bit                                    |

| CCPxY bit58                                  |

| CKE                                          |

| CKP67                                        |

| Clock Polarity Select bit, CKP67             |

| Code Examples                                |

| Call of a Subroutine in Page 1 from Page 026 |

| EEPROM Data Read43                           |

| EEPROM Data Write43                          |

| FLASH Program Read44                         |

| FLASH Program Write45                        |

| Indirect Addressing27                        |

| Initializing PORTA29                         |

| Saving STATUS, W and PCLATH Registers        |

| Code Protected Operation                     |

| Data EEPROM and FLASH Program Memory45       |

| Code Protection                              |

| Computed GOTO26                              |

| Configuration Bits119                        |

| Configuration Word120                        |

| Conversion Considerations                    |

|                                              |

# D

| D/Ā                                           |         |

|-----------------------------------------------|---------|

| Data EEPROM                                   |         |

| Associated Registers                          | 46      |

| Code Protection                               | 45      |

| Reading                                       |         |

| Special Functions Registers                   | 41      |

| Spurious Write Protection                     | 45      |

| Write Verify                                  | 45      |

| Writing to                                    | 43      |

| Data Memory                                   | 12      |

| Bank Select (RP1:RP0 Bits)                    | 12, 18  |

| General Purpose Registers                     | 12      |

| Register File Map                             | 13, 14  |

| Special Function Registers                    | 15      |

| Data/Address bit, D/A                         | 66      |

| DC and AC Characteristics Graphs and Tables . |         |

| DC Characteristics                            |         |

| Commercial and Industrial                     | 152–156 |

| Extended                                      | 157–160 |

| Development Support                           | 143     |

| Device Differences                            | 197     |

| Device Overview                               | 5       |

| Direct Addressing                             | 27      |

|                                               |         |

# Е

| Electrical Characteristics                               | 149 |

|----------------------------------------------------------|-----|

| Errata<br>External Clock Input (RA4/T0CKI). See Timer0   | 4   |

| External Interrupt Input (RB0/INT). See Interrupt Source | s   |

| F                                                        | -   |

| Firmware Instructions                                    | 135 |

| ELASH Program Memory                                     | 11  |

| FLASH Program Memory                    | 41         |

|-----------------------------------------|------------|

| Associated Registers                    | 46         |

| Code Protection                         | 45         |

| Configuration Bits and Read/Write State | 46         |

| Reading                                 | 44         |

| Special Function Registers              | 41         |

| Spurious Write Protection               | 45         |

| Write Protection                        | 46         |

| Write Verify                            | 45         |

| Writing to                              | 44         |

| FSR Register15,                         | 16, 17, 27 |

| -                                       |            |

# G

| General Call Address Sequence | 76 |

|-------------------------------|----|

| General Call Address Support  |    |

| General Call Enable bit       | 68 |

# L

| -                                                     |    |

|-------------------------------------------------------|----|

| I/O Ports                                             | 29 |

| I <sup>2</sup> C                                      | 73 |

| I <sup>2</sup> C Bus                                  |    |

| Connection Considerations                             | -  |

| Sample Device Configuration                           |    |

| I <sup>2</sup> C Master Mode Reception                |    |

| I <sup>2</sup> C Master Mode Repeated START Condition |    |

| I <sup>2</sup> C Mode Selection                       | 73 |

| I <sup>2</sup> C Module                               |    |

| Acknowledge Sequence Timing                           |    |

| Addressing                                            |    |

| Associated Registers                                  |    |

| Baud Rate Generator                                   |    |

| Block Diagram                                         |    |

| BRG Block Diagram                                     |    |

| BRG Reset due to SDA Collision                        |    |

| BRG Timing                                            |    |

| Bus Arbitration                                       |    |

| Bus Collision                                         |    |

| Acknowledge<br>Repeated START Condition               |    |

| Repeated START Condition Timing                       | 92 |

| (Case1)                                               | 02 |

| Repeated START Condition Timing                       | 92 |

| (Case2)                                               | 92 |

| START Condition                                       |    |

| START Condition Timing                                |    |

| STOP Condition                                        |    |

| STOP Condition Timing (Case1)                         |    |

| STOP Condition Timing (Case2)                         |    |

| Transmit Timing                                       |    |

| Bus Collision Timing                                  |    |

| Clock Arbitration                                     | 88 |

| Clock Arbitration Timing (Master Transmit)            |    |

| Conditions to not give ACK Pulse                      |    |

| General Call Address Support                          |    |

| Master Mode                                           |    |

| Master Mode 7-bit Reception Timing                    | 85 |

| Master Mode Block Diagram                             | 78 |