#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PIC <sup>®</sup> MCU Mid-Range Reference<br>Manual (DS33023) | PIC16F873               | PIC16F874               | PIC16F876               | PIC16F877               |

|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Operating Frequency                                                          | DC - 20 MHz             |

| RESETS (and Delays)                                                          | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) |

| FLASH Program Memory<br>(14-bit words)                                       | 4K                      | 4K                      | 8K                      | 8K                      |

| Data Memory (bytes)                                                          | 192                     | 192                     | 368                     | 368                     |

| EEPROM Data Memory                                                           | 128                     | 128                     | 256                     | 256                     |

| Interrupts                                                                   | 13                      | 14                      | 13                      | 14                      |

| I/O Ports                                                                    | Ports A,B,C             | Ports A,B,C,D,E         | Ports A,B,C             | Ports A,B,C,D,E         |

| Timers                                                                       | 3                       | 3                       | 3                       | 3                       |

| Capture/Compare/PWM Modules                                                  | 2                       | 2                       | 2                       | 2                       |

| Serial Communications                                                        | MSSP, USART             | MSSP, USART             | MSSP, USART             | MSSP, USART             |

| Parallel Communications                                                      | —                       | PSP                     | —                       | PSP                     |

| 10-bit Analog-to-Digital Module                                              | 5 input channels        | 8 input channels        | 5 input channels        | 8 input channels        |

| Instruction Set                                                              | 35 instructions         | 35 instructions         | 35 instructions         | 35 instructions         |

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin#     | l/O/P<br>Type        | Buffer<br>Type         | Description                                                                                            |

|-------------------|----------------|-------------------|-----------------|----------------------|------------------------|--------------------------------------------------------------------------------------------------------|

|                   |                |                   |                 |                      |                        | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15             | 16                | 32              | I/O                  | ST                     | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16             | 18                | 35              | I/O                  | ST                     | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17             | 19                | 36              | I/O                  | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                        |

| RC3/SCK/SCL       | 18             | 20                | 37              | I/O                  | ST                     | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23             | 25                | 42              | I/O                  | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                        |

| RC5/SDO           | 24             | 26                | 43              | I/O                  | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25             | 27                | 44              | I/O                  | ST                     | RC6 can also be the USART Asynchronous Transmi<br>or Synchronous Clock.                                |

| RC7/RX/DT         | 26             | 29                | 1               | I/O                  | ST                     | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                   |                |                   |                 |                      |                        | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19             | 21                | 38              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD1/PSP1          | 20             | 22                | 39              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD2/PSP2          | 21             | 23                | 40              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD3/PSP3          | 22             | 24                | 41              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD4/PSP4          | 27             | 30                | 2               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD5/PSP5          | 28             | 31                | 3               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD6/PSP6          | 29             | 32                | 4               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD7/PSP7          | 30             | 33                | 5               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

|                   |                |                   |                 |                      |                        | PORTE is a bi-directional I/O port.                                                                    |

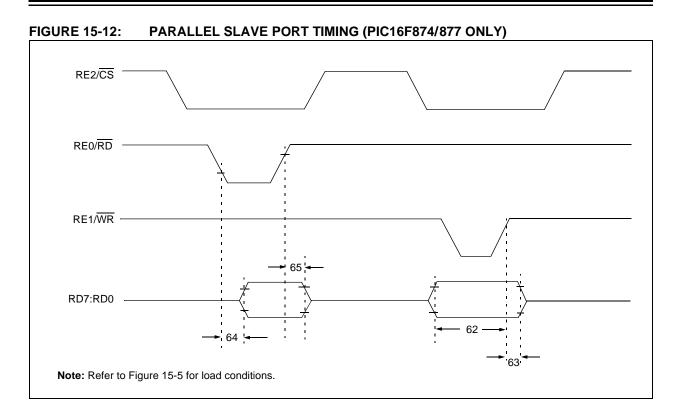

| RE0/RD/AN5        | 8              | 9                 | 25              | I/O                  | ST/TTL <sup>(3)</sup>  | RE0 can also be read control for the parallel slave port, or analog input5.                            |

| RE1/WR/AN6        | 9              | 10                | 26              | I/O                  | ST/TTL <sup>(3)</sup>  | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10             | 11                | 27              | I/O                  | ST/TTL <sup>(3)</sup>  | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31          | 13,34             | 6,29            | Р                    | _                      | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32          | 12,35             | 7,28            | Р                    | _                      | Positive supply for logic and I/O pins.                                                                |

| NC                | -              | 1,17,28,<br>40    | 12,13,<br>33,34 |                      | —                      | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |                 | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                |

### TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## 2.2 Data Memory Organization

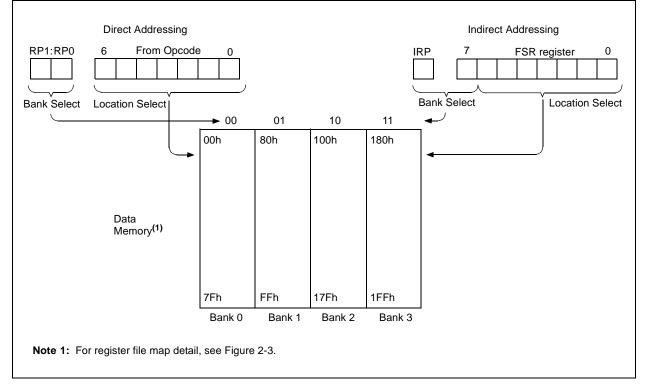

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be found in Section 4.0 of this data sheet. |

|-------|--------------------------------------------------------------------------------|

| 2.2.4 |                                                                                |

### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

### 2.2.2.7 PIR2 Register

The PIR2 register contains the flag bits for the CCP2 interrupt, the SSP bus collision interrupt and the EEPROM write operation interrupt.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-7: PIR2 REGISTER (ADDRESS 0Dh)

R = Readable bit

- n = Value at POR

| U-0   | R/W-0    | U-0 | R/W-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|----------|-----|-------|-------|-----|-----|--------|

| -     | Reserved | —   | EEIF  | BCLIF | —   | —   | CCP2IF |

| bit 7 |          |     |       |       |     |     | bit 0  |

| Unimplemented: Read as '0'                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                             |

| Reserved: Always maintain this bit clear                                                                                                                                    |

| Unimplemented: Read as '0'                                                                                                                                                  |

| EEIF: EEPROM Write Operation Interrupt Flag bit                                                                                                                             |

| <ul><li>1 = The write operation completed (must be cleared in software)</li><li>0 = The write operation is not complete or has not been started</li></ul>                   |

| BCLIF: Bus Collision Interrupt Flag bit                                                                                                                                     |

| <ul> <li>1 = A bus collision has occurred in the SSP, when configured for I2C Master mode</li> <li>0 = No bus collision has occurred</li> </ul>                             |

| Unimplemented: Read as '0'                                                                                                                                                  |

| CCP2IF: CCP2 Interrupt Flag bit                                                                                                                                             |

| Capture mode:                                                                                                                                                               |

| <ul> <li>1 = A TMR1 register capture occurred (must be cleared in software)</li> <li>0 = No TMR1 register capture occurred</li> <li><u>Compare mode:</u></li> </ul>         |

| <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> <li><u>PWM mode:</u></li> </ul> |

| Unused<br>Leaend:                                                                                                                                                           |

|                                                                                                                                                                             |

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

### 2.5 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-6. A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-2.

### EXAMPLE 2-2: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | clear INDF register; |

|          | INCF  | FSR,F | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       |                      |

|          | :     |       | ;yes continue        |

|          |       |       |                      |

NOTES:

NOTES:

### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

### TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                                       | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|---------------------------------------------|--------------|---------------|---------------|------------|----------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                        | TOIE         | INTE          | RBIE          | TOIF       | INTF     | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                        | RCIF         | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF | 0000 0000                | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | _                                           | _            | _             | —             | —          | _        | CCP2IF | 0                        | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                        | RCIE         | TXIE          | SSPIE         | CCP1IE     | TMR2IE   | TMR1IE | 0000 0000                | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | _                                           | —            | _             | _             | —          | —        | CCP2IE | 0                        | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direct                                  | tion Registe | er            |               |            |          |        | 1111 1111                | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister for                                 | r the Least  | Significant E | Byte of the 1 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister for                                 | r the Most S | Significant B | yte of the 16 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                           | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N | 00 0000                  | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | ompare/F                                    | WM Regist    | ter1 (LSB)    |               |            |          |        | XXXX XXXX                | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | ompare/F                                    | WM Regist    | ter1 (MSB)    |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |

| 17h                    | CCP1CON | —                    | — — CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP1M0 |              |               |               |            |          |        |                          | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB)         |              |               |               |            |          |        |                          | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | ompare/F                                    |              | xxxx xxxx     | uuuu uuuu     |            |          |        |                          |                                 |

| 1Dh                    | CCP2CON | —                    | —                                           | CCP2X        | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0 | 00 0000                  | 00 0000                         |

$\label{eq:legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.$

Note 1: The PSP is not implemented on the PIC16F873/876; always maintain these bits clear.

NOTES:

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Figure 9-1 shows a block diagram for the SPI mode, while Figure 9-5 and Figure 9-9 show the block diagrams for the two different  $I^2C$  modes of operation.

The Application Note AN734, "Using the PIC<sup>®</sup> MCU SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication" describes the slave operation of the MSSP module on the PIC16F87X devices. AN735, "Using the PIC<sup>®</sup> MCU MSSP Module for I<sup>2</sup>C<sup>TM</sup> Communications" describes the master operation of the MSSP module on the PIC16F87X devices.

# 9.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode, fully implements all master and slave functions (including general call support) and provides interrupts on START and STOP bits in hardware, to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications, as well as 7-bit and 10-bit addressing.

Refer to Application Note AN578, "Use of the SSP Module in the  $I^2C$  Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

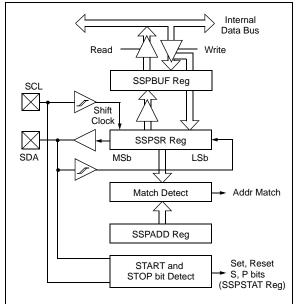

### FIGURE 9-5:

I<sup>2</sup>C SLAVE MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C firmware modes (provided for compatibility to other mid-range products)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode. Pull-up resistors must be provided externally to the SCL and SDA pins for the proper operation of the  $I^2C$  module.

The CKE bit (SSPSTAT<6:7>) sets the levels of the SDA and SCL pins in either Master or Slave mode. When CKE = 1, the levels will conform to the SMBus specification. When CKE = 0, the levels will conform to the  $I^2C$  specification.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START (S) or STOP (P) bit, specifies if the received byte was data or address, if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer.

SSPBUF is the register to which the transfer data is written to, or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

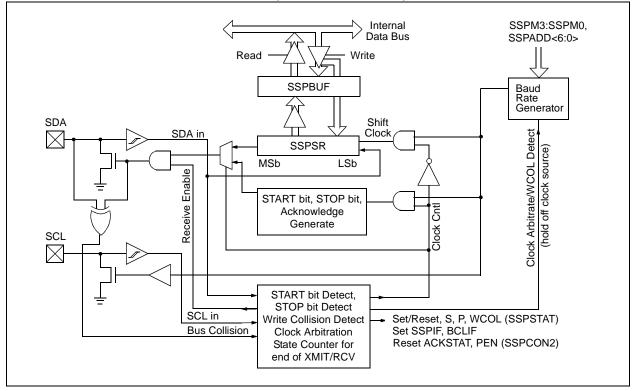

### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

### FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

# TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | F       | osc = 20 M | IHz                         | F       | osc = 16 N | IHz                         | Fosc = 10 MHz |            |                             |

|-------------|---------|------------|-----------------------------|---------|------------|-----------------------------|---------------|------------|-----------------------------|

| RATE<br>(K) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -       | -          | -                           | -       | -          | -                           | -             | -          | -                           |

| 1.2         | 1.221   | 1.75       | 255                         | 1.202   | 0.17       | 207                         | 1.202         | 0.17       | 129                         |

| 2.4         | 2.404   | 0.17       | 129                         | 2.404   | 0.17       | 103                         | 2.404         | 0.17       | 64                          |

| 9.6         | 9.766   | 1.73       | 31                          | 9.615   | 0.16       | 25                          | 9.766         | 1.73       | 15                          |

| 19.2        | 19.531  | 1.72       | 15                          | 19.231  | 0.16       | 12                          | 19.531        | 1.72       | 7                           |

| 28.8        | 31.250  | 8.51       | 9                           | 27.778  | 3.55       | 8                           | 31.250        | 8.51       | 4                           |

| 33.6        | 34.722  | 3.34       | 8                           | 35.714  | 6.29       | 6                           | 31.250        | 6.99       | 4                           |

| 57.6        | 62.500  | 8.51       | 4                           | 62.500  | 8.51       | 3                           | 52.083        | 9.58       | 2                           |

| HIGH        | 1.221   | -          | 255                         | 0.977   | -          | 255                         | 0.610         | -          | 255                         |

| LOW         | 312.500 | -          | 0                           | 250.000 | -          | 0                           | 156.250       | -          | 0                           |

| DAUD                |        | Fosc = 4 M | Hz                          | Fosc = 3.6864 MHz |            |                             |  |

|---------------------|--------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | 0.300  | 0          | 207                         | 0.3               | 0          | 191                         |  |

| 1.2                 | 1.202  | 0.17       | 51                          | 1.2               | 0          | 47                          |  |

| 2.4                 | 2.404  | 0.17       | 25                          | 2.4               | 0          | 23                          |  |

| 9.6                 | 8.929  | 6.99       | 6                           | 9.6               | 0          | 5                           |  |

| 19.2                | 20.833 | 8.51       | 2                           | 19.2              | 0          | 2                           |  |

| 28.8                | 31.250 | 8.51       | 1                           | 28.8              | 0          | 1                           |  |

| 33.6                | -      | -          | -                           | -                 | -          | -                           |  |

| 57.6                | 62.500 | 8.51       | 0                           | 57.6              | 0          | 0                           |  |

| HIGH                | 0.244  | -          | 255                         | 0.225             | -          | 255                         |  |

| LOW                 | 62.500 | -          | 0                           | 57.6              | -          | 0                           |  |

# TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD<br>RATE<br>(K) | Fosc = 20 MHz |            |                             | Fosc = 16 MHz |            |                             | Fosc = 10 MHz |            |                             |  |

|---------------------|---------------|------------|-----------------------------|---------------|------------|-----------------------------|---------------|------------|-----------------------------|--|

|                     | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | -             | -          | -                           | -             | -          | -                           | -             | -          | -                           |  |

| 1.2                 | -             | -          | -                           | -             | -          | -                           | -             | -          | -                           |  |

| 2.4                 | -             | -          | -                           | -             | -          | -                           | 2.441         | 1.71       | 255                         |  |

| 9.6                 | 9.615         | 0.16       | 129                         | 9.615         | 0.16       | 103                         | 9.615         | 0.16       | 64                          |  |

| 19.2                | 19.231        | 0.16       | 64                          | 19.231        | 0.16       | 51                          | 19.531        | 1.72       | 31                          |  |

| 28.8                | 29.070        | 0.94       | 42                          | 29.412        | 2.13       | 33                          | 28.409        | 1.36       | 21                          |  |

| 33.6                | 33.784        | 0.55       | 36                          | 33.333        | 0.79       | 29                          | 32.895        | 2.10       | 18                          |  |

| 57.6                | 59.524        | 3.34       | 20                          | 58.824        | 2.13       | 16                          | 56.818        | 1.36       | 10                          |  |

| HIGH                | 4.883         | -          | 255                         | 3.906         | -          | 255                         | 2.441         | -          | 255                         |  |

| LOW                 | 1250.000      | -          | 0                           | 1000.000      |            | 0                           | 625.000       | -          | 0                           |  |

| BAUD        | F       | osc = 4 MH                            | lz  | Fosc = 3.6864 MHz |            |                             |  |

|-------------|---------|---------------------------------------|-----|-------------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD   | % SPBRG<br>value<br>D ERROR (decimal) |     | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -                                     | -   | -                 | -          | -                           |  |

| 1.2         | 1.202   | 0.17                                  | 207 | 1.2               | 0          | 191                         |  |

| 2.4         | 2.404   | 0.17                                  | 103 | 2.4               | 0          | 95                          |  |

| 9.6         | 9.615   | 0.16                                  | 25  | 9.6               | 0          | 23                          |  |

| 19.2        | 19.231  | 0.16                                  | 12  | 19.2              | 0          | 11                          |  |

| 28.8        | 27.798  | 3.55                                  | 8   | 28.8              | 0          | 7                           |  |

| 33.6        | 35.714  | 6.29                                  | 6   | 32.9              | 2.04       | 6                           |  |

| 57.6        | 62.500  | 8.51                                  | 3   | 57.6              | 0          | 3                           |  |

| HIGH        | 0.977   | -                                     | 255 | 0.9               | -          | 255                         |  |

| LOW         | 250.000 | -                                     | 0   | 230.4             | -          | 0                           |  |

#### 12.2 **Oscillator Configurations**

#### 12.2.1 **OSCILLATOR TYPES**

The PIC16F87X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- Crystal/Resonator • XT

- High Speed Crystal/Resonator HS

- RC Resistor/Capacitor

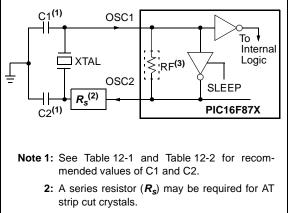

#### 12.2.2 **CRYSTAL OSCILLATOR/CERAMIC** RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-1). The PIC16F87X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 12-2).

### **FIGURE 12-1: CRYSTAL/CERAMIC RESONATOR OPERATION** (HS, XT OR LP **OSC CONFIGURATION)**

3: RF varies with the crystal chosen.

### **EXTERNAL CLOCK INPUT OPERATION (HS, XT OR** LP OSC **CONFIGURATION**) OSC1 Clock from Ext. System PIC16F87X OSC2 Open

### TABLE 12-1: CERAMIC RESONATORS

| Ranges Tested: |          |             |             |  |  |  |

|----------------|----------|-------------|-------------|--|--|--|

| Mode           | Freq.    | OSC1        | OSC2        |  |  |  |

| ХТ             | 455 kHz  | 68 - 100 pF | 68 - 100 pF |  |  |  |

|                | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

|                | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |  |  |  |

| HS             | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |  |  |  |

|                | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |  |  |  |

These values are for design guidance only. See notes following Table 12-2.

### **Resonators Used:**

| 455 kHz                                               | Panasonic EFO-A455K04B | $\pm 0.3\%$ |  |

|-------------------------------------------------------|------------------------|-------------|--|

| 2.0 MHz                                               | Murata Erie CSA2.00MG  | $\pm 0.5\%$ |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG  | $\pm 0.5\%$ |  |

| 8.0 MHz                                               | Murata Erie CSA8.00MT  | $\pm 0.5\%$ |  |

| 16.0 MHz                                              | Murata Erie CSA16.00MX | $\pm 0.5\%$ |  |

| All resonators used did not have built-in capacitors. |                        |             |  |

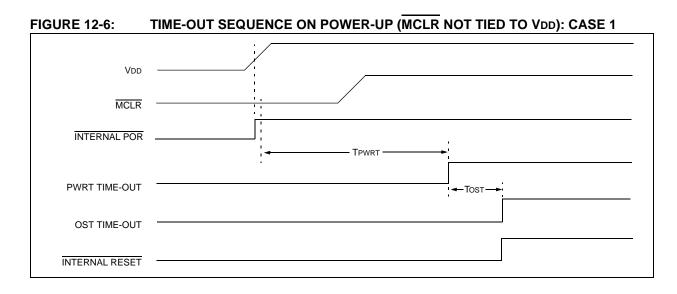

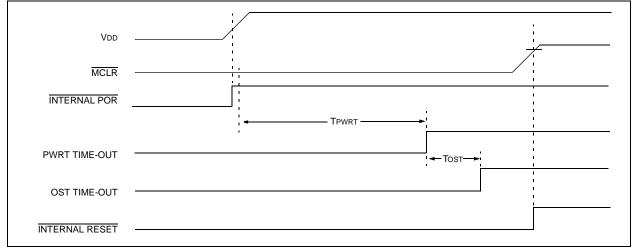

## FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

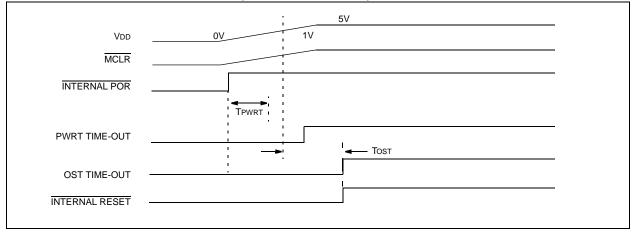

# FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

# 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

### 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

### 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

### 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        |                                                                  | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                   |      |      |                                            |

|--------------------------------------------------------------------|--------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|--------------------------------------------|

| Param<br>No.                                                       | Symbol | Characteristic/<br>Device                                        | Min                                                                                                                      | Typ†         Max         Units         Conditions |      |      | Conditions                                 |

|                                                                    | Vdd    | Supply Voltage                                                   |                                                                                                                          |                                                   |      |      |                                            |

| D001                                                               |        |                                                                  | 4.0                                                                                                                      | —                                                 | 5.5  | V    | LP, XT, RC osc configuration               |

| D001A                                                              |        |                                                                  | 4.5                                                                                                                      |                                                   | 5.5  | V    | HS osc configuration                       |

| D001A                                                              |        |                                                                  | VBOR                                                                                                                     |                                                   | 5.5  | V    | BOR enabled, FMAX = 10 MHz <sup>(7)</sup>  |

| D002                                                               | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                                                                                        | 1.5                                               | _    | V    |                                            |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                        | Vss                                               | _    | V    | See section on Power-on Reset for details  |

| D004                                                               | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                                                                                     | —                                                 | —    | V/ms | See section on Power-on Reset for details  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                                                                                      | 4.0                                               | 4.35 | V    | BODEN bit in configuration word<br>enabled |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F874/877 ONLY)

| Parameter<br>No. | Symbol   | Characteristic                                                                                        |              |          | Тур† | Max      | Units    | Conditions             |

|------------------|----------|-------------------------------------------------------------------------------------------------------|--------------|----------|------|----------|----------|------------------------|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (setup time)                  |              | 20<br>25 | _    | _        | ns<br>ns | Extended<br>Range Only |

| 63*              | TwrH2dtl | $\overline{\text{WR}}^{\uparrow}$ or $\overline{\text{CS}}^{\uparrow}$ to data–in invalid (hold time) | Standard(F)  | 20       |      | —        | ns       |                        |

|                  |          |                                                                                                       | Extended(LF) | 35       |      | —        | ns       |                        |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid                             | •            | -        | _    | 80<br>90 | ns<br>ns | Extended<br>Range Only |

| 65               | TrdH2dtI | $\overline{RD}^{\uparrow}$ or $\overline{CS}^{\downarrow}$ to data–out invalid                        |              | 10       | —    | 30       | ns       |                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| PWM Mode61                                   |

|----------------------------------------------|

| Block Diagram61                              |

| Duty Cycle61                                 |

| Example Frequencies/Resolutions (Table)62    |

| PWM Period61                                 |

| Special Event Trigger and A/D Conversions60  |

| CCP. See Capture/Compare/PWM                 |

| CCP1CON                                      |

| CCP2CON                                      |

| CCPR1H Register 15, 17, 57                   |

| CCPR1L Register 17, 57                       |

| CCPR2H Register                              |

| CCPR2L Register 15, 17                       |

| CCPxM0 bit58                                 |

| CCPxM1 bit58                                 |

| CCPxM2 bit58                                 |

| CCPxM3 bit58                                 |

| CCPxX bit                                    |

| CCPxY bit58                                  |

| CKE                                          |

| CKP67                                        |

| Clock Polarity Select bit, CKP67             |

| Code Examples                                |

| Call of a Subroutine in Page 1 from Page 026 |

| EEPROM Data Read43                           |

| EEPROM Data Write43                          |

| FLASH Program Read44                         |

| FLASH Program Write45                        |

| Indirect Addressing27                        |

| Initializing PORTA29                         |

| Saving STATUS, W and PCLATH Registers        |

| Code Protected Operation                     |

| Data EEPROM and FLASH Program Memory45       |

| Code Protection                              |

| Computed GOTO26                              |

| Configuration Bits119                        |

| Configuration Word120                        |

| Conversion Considerations                    |

|                                              |

# D

| D/Ā                                           |         |

|-----------------------------------------------|---------|

| Data EEPROM                                   |         |

| Associated Registers                          | 46      |

| Code Protection                               | 45      |

| Reading                                       |         |

| Special Functions Registers                   | 41      |

| Spurious Write Protection                     | 45      |

| Write Verify                                  | 45      |

| Writing to                                    | 43      |

| Data Memory                                   | 12      |

| Bank Select (RP1:RP0 Bits)                    | 12, 18  |

| General Purpose Registers                     | 12      |

| Register File Map                             | 13, 14  |

| Special Function Registers                    | 15      |

| Data/Address bit, D/A                         | 66      |

| DC and AC Characteristics Graphs and Tables . |         |

| DC Characteristics                            |         |

| Commercial and Industrial                     | 152–156 |

| Extended                                      | 157–160 |

| Development Support                           | 143     |

| Device Differences                            |         |

| Device Overview                               | 5       |

| Direct Addressing                             | 27      |

|                                               |         |

# Е

| Electrical Characteristics                                | . 149 |

|-----------------------------------------------------------|-------|

| Errata<br>External Clock Input (RA4/T0CKI). See Timer0    | 4     |

| External Interrupt Input (RB0/INT). See Interrupt Source: | s     |

| F                                                         |       |

| Firmware Instructions                                     | . 135 |

| FLASH Program Memory                                      | 41    |

| FLASH Program Memory                    | 41            |

|-----------------------------------------|---------------|

| Associated Registers                    | 46            |

| Code Protection                         | 45            |

| Configuration Bits and Read/Write State | 46            |

| Reading                                 | 44            |

| Special Function Registers              | 41            |

| Spurious Write Protection               | 45            |

| Write Protection                        | 46            |

| Write Verify                            | 45            |

| Writing to                              | 44            |

| FSR Register1                           | 5, 16, 17, 27 |

| -                                       |               |

# G

| General Call Address Sequence | 76 |

|-------------------------------|----|

| General Call Address Support  |    |

| General Call Enable bit       | 68 |

# L

| -                                                     |    |   |

|-------------------------------------------------------|----|---|

| I/O Ports                                             | 29 | Э |

| I <sup>2</sup> C                                      | 73 | 3 |

| I <sup>2</sup> C Bus                                  |    |   |

| Connection Considerations                             | -  |   |

| Sample Device Configuration                           |    |   |

| I <sup>2</sup> C Master Mode Reception                |    |   |

| I <sup>2</sup> C Master Mode Repeated START Condition |    |   |

| I <sup>2</sup> C Mode Selection                       | 73 | 3 |

| I <sup>2</sup> C Module                               |    |   |

| Acknowledge Sequence Timing                           |    |   |

| Addressing                                            |    |   |

| Associated Registers                                  |    |   |

| Baud Rate Generator                                   |    |   |

| Block Diagram                                         |    |   |

| BRG Block Diagram                                     |    |   |

| BRG Reset due to SDA Collision                        |    |   |

| BRG Timing                                            |    |   |

| Bus Arbitration                                       |    |   |

| Bus Collision                                         |    |   |

| Acknowledge<br>Repeated START Condition               |    |   |

| Repeated START Condition Timing                       | 92 | - |

| (Case1)                                               | 0  | 2 |

| Repeated START Condition Timing                       | 92 | - |

| (Case2)                                               | 92 | , |

| START Condition                                       |    |   |

| START Condition Timing                                |    |   |

| STOP Condition                                        |    |   |

| STOP Condition Timing (Case1)                         |    |   |

| STOP Condition Timing (Case2)                         |    |   |

| Transmit Timing                                       |    |   |

| Bus Collision Timing                                  |    |   |

| Clock Arbitration                                     | 88 | 3 |

| Clock Arbitration Timing (Master Transmit)            |    |   |

| Conditions to not give ACK Pulse                      |    |   |

| General Call Address Support                          |    |   |

| Master Mode                                           | 78 | 3 |

| Master Mode 7-bit Reception Timing                    | 85 | 5 |

| Master Mode Block Diagram                             | 78 | 3 |

NOTES: