Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-20-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | DIP<br>Pin#         | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|---------------------|--------------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                   | 9            | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                  | 10           | 0             | —                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                   | 1            | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                     |              |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                   | 2            | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                   | 3            | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                   | 4            | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                   | 5            | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                   | 6            | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                   | 7            | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                     |              |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                  | 21           | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                  | 22           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                  | 23           | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                  | 24           | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                  | 25           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                  | 26           | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                  | 27           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                  | 28           | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                     |              |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                  | 11           | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                  | 12           | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                  | 13           | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                  | 14           | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                  | 15           | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                  | 16           | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                  | 17           | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                  | 18           | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19               | 8, 19        | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                  | 20           | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not |              |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be found in Section 4.0 of this data sheet. |

|-------|--------------------------------------------------------------------------------|

| 2.2.4 |                                                                                |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

2.2.2.5 PIR1 Register

The PIR1 register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt bits are clear prior to enabling an interrupt.

|       | R/W-0                                                                                                                                                                                                                               | R/W-0                                                                                                                                                | R-0                                                          | R-0                                                                                            | R/W-0                                                                                | R/W-0                                                                                         | R/W-0                                          | R/W-0       |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-------------|--|--|--|

|       | PSPIF <sup>(1)</sup>                                                                                                                                                                                                                | ADIF                                                                                                                                                 | RCIF                                                         | TXIF                                                                                           | SSPIF                                                                                | CCP1IF                                                                                        | TMR2IF                                         | TMR1IF      |  |  |  |

|       | bit 7                                                                                                                                                                                                                               |                                                                                                                                                      |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

| bit 7 | <ul> <li><b>PSPIF</b><sup>(1)</sup>: Parallel Slave Port Read/Write Interrupt Flag bit</li> <li>1 = A read or a write operation has taken place (must be cleared in software)</li> <li>0 = No read or write has occurred</li> </ul> |                                                                                                                                                      |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

| bit 6 | 1 = An A/D                                                                                                                                                                                                                          | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed<br>0 = The A/D conversion is not complete                                  |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

| bit 5 | 1 = The US                                                                                                                                                                                                                          | <b>RCIF</b> : USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full<br>0 = The USART receive buffer is empty                      |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

| bit 4 | TXIF: USAI<br>1 = The US                                                                                                                                                                                                            | RT Transmi<br>ART transr                                                                                                                             | t Interrupt F<br>nit buffer is<br>nit buffer is i            | lag bit<br>empty                                                                               |                                                                                      |                                                                                               |                                                |             |  |  |  |

| bit 3 | 1 = The SSI<br>from the<br>• SPI<br>- A<br>• I <sup>2</sup> C S                                                                                                                                                                     | P interrupt o<br>e Interrupt S<br>A transmiss<br>Slave<br>A transmiss                                                                                |                                                              | s occurred, a<br>tine. The co<br>n has taken                                                   | and must be<br>nditions that<br>place.                                               | cleared in so                                                                                 |                                                | e returning |  |  |  |

|       | T -<br>T -<br>T -<br>T -<br>A<br>-<br>A<br>-<br>A                                                                                                                                                                                   | The initiated<br>The initiated<br>The initiated<br>The initiated<br>A START co<br>A STOP cor                                                         | I STOP cone<br>I Restart cor<br>I Acknowled<br>Indition occu | ndition was of<br>dition was condition was<br>ge condition<br>Irred while the<br>red while the | completed by<br>completed by<br>completed by<br>was completed by<br>was completed by | y the SSP m<br>the SSP mc<br>y the SSP m<br>eted by the S<br>ule was idle (<br>ile was idle ( | odule.<br>odule.<br>SSP module<br>(Multi-Maste | r system).  |  |  |  |

| bit 2 | CCP1IF: CO                                                                                                                                                                                                                          | •                                                                                                                                                    |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

|       | 0 = No TMF<br><u>Compare m</u><br>1 = A TMR <sup>-</sup>                                                                                                                                                                            | 1 register ca<br>R1 register<br><u>node:</u><br>1 register ca<br>R1 register<br><u>2:</u>                                                            | capture occ                                                  | urred<br>ch occurred                                                                           |                                                                                      | software)<br>eared in soft                                                                    | ware)                                          |             |  |  |  |

| bit 1 | 1 = TMR2 t                                                                                                                                                                                                                          | o PR2 mate                                                                                                                                           | 2 Match Inte<br>ch occurred<br>natch occur                   | (must be cle                                                                                   | it<br>eared in soft                                                                  | ware)                                                                                         |                                                |             |  |  |  |

| bit 0 | 1 = TMR1 r                                                                                                                                                                                                                          | <b>TMR1IF</b> : TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

|       | Note 1: P                                                                                                                                                                                                                           | SPIF is res                                                                                                                                          | erved on PI                                                  | C16F873/87                                                                                     | 76 devices; a                                                                        | always maint                                                                                  | ain this bit c                                 | lear.       |  |  |  |

|       | Legend:                                                                                                                                                                                                                             |                                                                                                                                                      |                                                              |                                                                                                |                                                                                      |                                                                                               |                                                |             |  |  |  |

|       | R = Reada                                                                                                                                                                                                                           | ole bit                                                                                                                                              | W = Writat                                                   |                                                                                                | U = Unimp                                                                            | lemented bit                                                                                  | t, read as '0'                                 |             |  |  |  |

|       | - n = Value                                                                                                                                                                                                                         | at POR                                                                                                                                               | '1' = Bit is                                                 | set                                                                                            | '0' = Bit is                                                                         | cleared                                                                                       | x = Bit is ur                                  | nknown      |  |  |  |

#### REGISTER 2-5: PIR1 REGISTER (ADDRESS 0Ch)

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6                                                                                          | Bit 5        | Bit 4         | Bit 3         | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------------------------------------------------------------------------|--------------|---------------|---------------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE                                                                                           | TOIE         | INTE          | RBIE          | TOIF      | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                                                                           | RCIF         | TXIF          | SSPIF         | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                                                                           | RCIE         | TXIE          | SSPIE         | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            | egister for th                                                                                 | ne Least Sig | nificant Byte | of the 16-bit | TMR1 Regi | ster   |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H  | Holding R            | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |              |               |               |           |        |        |                          | uuuu uuuu                       |

| 10h                    | T1CON  | —                    | —                                                                                              | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC    | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

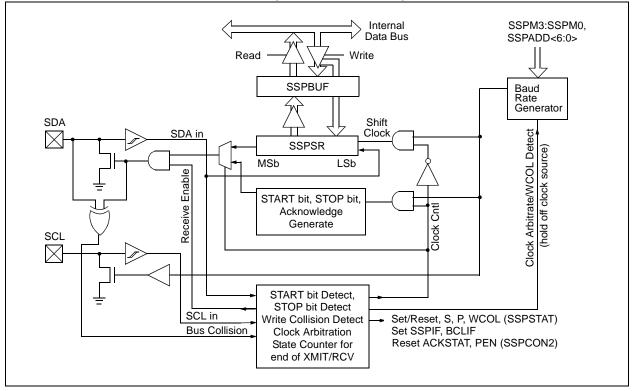

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Figure 9-1 shows a block diagram for the SPI mode, while Figure 9-5 and Figure 9-9 show the block diagrams for the two different  $I^2C$  modes of operation.

The Application Note AN734, "Using the PIC<sup>®</sup> MCU SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication" describes the slave operation of the MSSP module on the PIC16F87X devices. AN735, "Using the PIC<sup>®</sup> MCU MSSP Module for I<sup>2</sup>C<sup>TM</sup> Communications" describes the master operation of the MSSP module on the PIC16F87X devices.

#### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

### FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

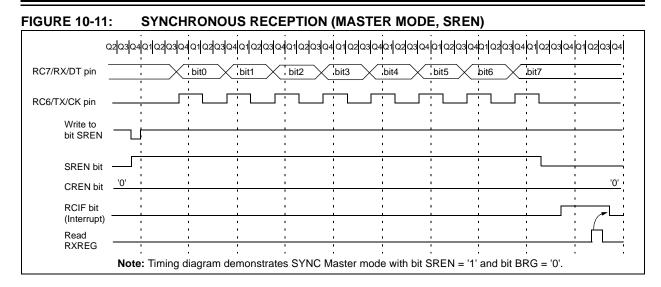

# 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6     | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-----------|-----------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE      | TOIE      | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9       | SREN      | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | x000 0000                       |

| 19h                    | TXREG  | USART Tr             | ansmit R  | egister   |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9       | TXEN      | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Generat | or Regist | ter   |       |        |        |        | 0000 0000             | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1              | CP0 | DEBUG                                                         | _                                                                                                                                                                                                                                                                                                                                                                  | WRT       | CPD       | LVP                | BODEN                                      | CP1     | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |

|------------------|-----|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------------------|--------------------------------------------|---------|-----|-------|------|-------|-------|

| bit13<br>bit 13- | 12, |                                                               | bit0<br><b>CP1:CP0:</b> FLASH Program Memory Code Protection bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                   |           |           |                    |                                            |         |     |       |      |       |       |

| bit 5-4          |     | 10 = 1F00<br>10 = 0F00<br>01 = 1000<br>01 = 0800<br>00 = 0000 | 11 = Code protection off<br>10 = 1F00h to 1FFFh code protected (PIC16F877, 876)<br>10 = 0F00h to 0FFFh code protected (PIC16F874, 873)<br>01 = 1000h to 1FFFh code protected (PIC16F877, 876)<br>01 = 0800h to 0FFFh code protected (PIC16F874, 873)<br>00 = 0000h to 1FFFh code protected (PIC16F877, 876)<br>00 = 0000h to 0FFFh code protected (PIC16F874, 873) |           |           |                    |                                            |         |     |       |      |       |       |

| bit 11           |     |                                                               | cuit Deb                                                                                                                                                                                                                                                                                                                                                           | ugger dis | abled, R  | B6 and             | RB7 are ge<br>RB7 are de                   | •       | •   | •     |      |       |       |

| bit 10           |     | Unimpler                                                      | nented:                                                                                                                                                                                                                                                                                                                                                            | Read as   | '1'       |                    |                                            |         |     |       |      |       |       |

| bit 9            |     | •                                                             | tected p                                                                                                                                                                                                                                                                                                                                                           | rogram n  | nemory i  | may be             | ble<br>written to by<br>be written t       |         |     |       |      |       |       |

| bit 8            |     | <b>CPD:</b> Dat<br>1 = Code<br>0 = Data I                     | protectio                                                                                                                                                                                                                                                                                                                                                          | on off    |           |                    | ł                                          |         |     |       |      |       |       |

| bit 7            |     | 1 = RB3/F                                                     | PGM pin                                                                                                                                                                                                                                                                                                                                                            | has PGN   | 1 functio | n, low v           | iming Enabl<br>oltage prog<br>e used for p | ramming |     | 1     |      |       |       |

| bit 6            |     | <b>BODEN</b> :<br>1 = BOR<br>0 = BOR                          | enabled                                                                                                                                                                                                                                                                                                                                                            | ut Reset  | Enable t  | <sub>Dit</sub> (3) |                                            |         |     |       |      |       |       |

| bit 3            |     | <b>PWRTE</b> :<br>1 = PWR<br>0 = PWR                          | T disable                                                                                                                                                                                                                                                                                                                                                          | d         | nable b   | it(3)              |                                            |         |     |       |      |       |       |

| bit 2            |     | 1 = WDT                                                       | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                                                                                                             |           |           |                    |                                            |         |     |       |      |       |       |

| bit 1-0          |     | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (   | oscillator<br>oscillator<br>oscillator                                                                                                                                                                                                                                                                                                                             |           | Selectio  | n bits             |                                            |         |     |       |      |       |       |

- **Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

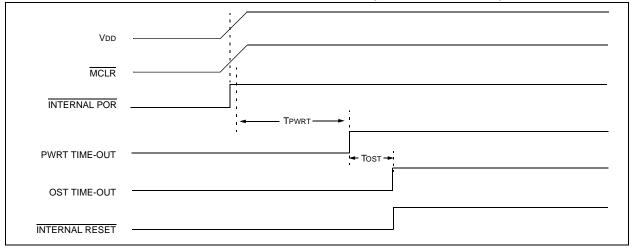

#### 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

### 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

### 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

# 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power            | -up       | Brown-out        | Wake-up from |

|--------------------------|------------------|-----------|------------------|--------------|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        | SLEEP        |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc     |

| RC                       | 72 ms            |           | 72 ms            | _            |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

|          |         |     |     |     |                                    | ,                         |                                 |

|----------|---------|-----|-----|-----|------------------------------------|---------------------------|---------------------------------|

| Register | Devices |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| PIE2     | 873     | 874 | 876 | 877 | -r-0 00                            | -r-0 00                   | -r-u uu                         |

| PCON     | 873     | 874 | 876 | 877 | dd                                 | uu                        | uu                              |

| PR2      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | 1111 1111                       |

| SSPADD   | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| SSPSTAT  | 873     | 874 | 876 | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |

| TXSTA    | 873     | 874 | 876 | 877 | 0000 -010                          | 0000 -010                 | uuuu -uuu                       |

| SPBRG    | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| ADRESL   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| ADCON1   | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| EEDATA   | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| EEADR    | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EEDATH   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EEADRH   | 873     | 874 | 876 | 877 | XXXX XXXX                          | սսսս սսսս                 | uuuu uuuu                       |

| EECON1   | 873     | 874 | 876 | 877 | x x000                             | u u000                    | u uuuu                          |

| EECON2   | 873     | 874 | 876 | 877 |                                    |                           |                                 |

TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

#### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

## 14.13 PICDEM 3 Low Cost PIC16CXXX Demonstration Board

The PICDEM 3 demonstration board is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with an LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 3 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer with an adapter socket, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 3 demonstration board to test firmware. A prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM 3 demonstration board is a LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM 3 demonstration board provides an additional RS-232 interface and Windows software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

## 14.14 PICDEM 17 Demonstration Board

The PICDEM 17 demonstration board is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756A, PIC17C762 and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included and the user may erase it and program it with the other sample programs using the PRO MATE II device programmer, or the PICSTART Plus development programmer, and easily debug and test the sample code. In addition, the PICDEM 17 demonstration board supports downloading of programs to and executing out of external FLASH memory on board. The PICDEM 17 demonstration board is also usable with the MPLAB ICE in-circuit emulator, or the PICMASTER emulator and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 14.15 KEELOQ Evaluation and Programming Tools

KEELOQ evaluation and programming tools support Microchip's HCS Secure Data Products. The HCS evaluation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a programming interface to program test transmitters.

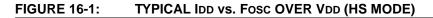

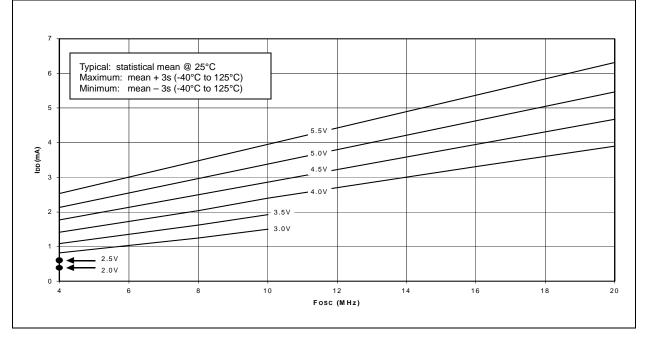

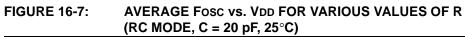

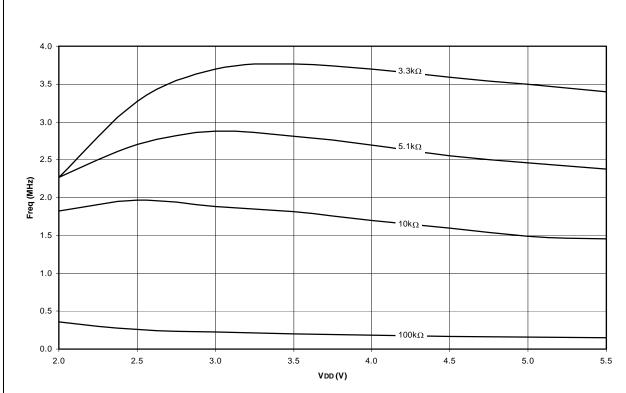

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented is **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

FIGURE 16-8: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF,  $25^{\circ}$ C)

DS30292D-page 180

# 17.0 PACKAGING INFORMATION

# 17.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carried                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

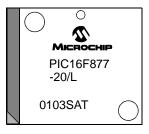

# Package Marking Information (Cont'd)

#### 44-Lead TQFP

#### Example

$\bigcirc$

Example

$\lambda \lambda$

PIC16F877-04/P

0112SAA

MICROCHIP

#### 44-Lead MQFP

### Example

#### 44-Lead PLCC

#### Example

\_\_\_\_\_