Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

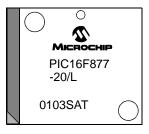

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-20-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

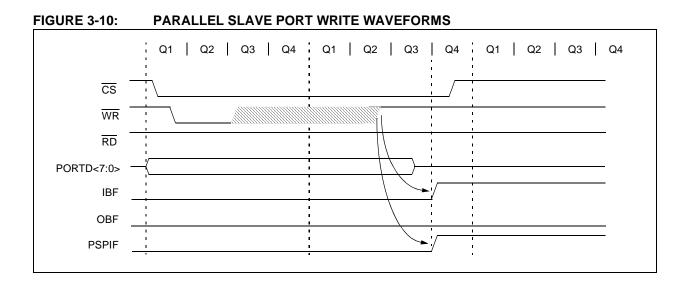

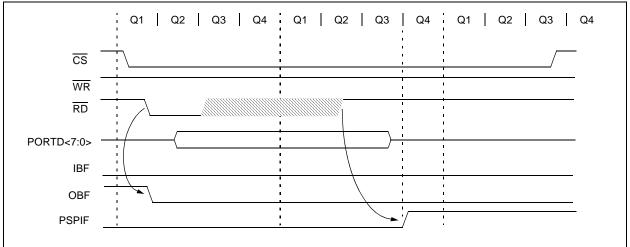

## FIGURE 3-11: PARALLEL SLAVE PORT READ WAVEFORMS

## TABLE 3-11: REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7                | Bit 6                                             | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0   | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------------------|---------------------------------------------------|-------|---------|-------|---------|-------------|---------|-----------------------|---------------------------------|

| 08h     | PORTD  | Port Data            | Port Data Latch when written: Port pins when read |       |         |       |         |             |         | XXXX XXXX             | uuuu uuuu                       |

| 09h     | PORTE  |                      |                                                   |       |         |       | RE2     | RE1         | RE0     | xxx                   | uuu                             |

| 89h     | TRISE  | IBF                  | OBF                                               | IBOV  | PSPMODE | _     | PORTE D | ata Directi | on Bits | 0000 -111             | 0000 -111                       |

| 0Ch     | PIR1   | PSPIF <sup>(1)</sup> | ADIF                                              | RCIF  | TXIF    | SSPIF | CCP1IF  | TMR2IF      | TMR1IF  | 0000 0000             | 0000 0000                       |

| 8Ch     | PIE1   | PSPIE <sup>(1)</sup> | ADIE                                              | RCIE  | TXIE    | SSPIE | CCP1IE  | TMR2IE      | TMR1IE  | 0000 0000             | 0000 0000                       |

| 9Fh     | ADCON1 | ADFM                 | _                                                 | _     | _       | PCFG3 | PCFG2   | PCFG1       | PCFG0   | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Parallel Slave Port. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

## 4.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F87X device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

## TABLE 4-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Со  | nfiguration | Bits | Manageral          | Internal | Internal |           | ICSP Write |  |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|--|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |  |

| 0   | 0           | x    | All program memory | Yes      | No       | No        | No         |  |

| 0   | 1           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |  |

| 0   | 1           | 0    | Protected areas    | Yes      | No       | No        | No         |  |

| 0   | 1           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |  |

| 0   | 1           | 1    | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 0           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |  |

| 1   | 0           | 0    | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 0           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |  |

| 1   | 0           | 1    | Protected areas    | Yes      | No       | No        | No         |  |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |  |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |  |

| TABLE 4-2: | REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH |

|------------|-----------------------------------------------------|

|            |                                                     |

| Address                 | Name   | Bit 7  | Bit 6                                              | Bit 5      | Bit 4     | Bit 3        | Bit 2  | Bit 1 | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|----------------------------------------------------|------------|-----------|--------------|--------|-------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE                                               | TOIE       | INTE      | RBIE         | TOIF   | INTF  | RBIF      | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPRON | Address                                            | s Register | , Low Byt | е            |        |       |           | xxxx xxxx                | uuuu uuuu                       |

| 10Fh                    | EEADRH | —      | — — EEPROM Address, High Byte                      |            |           |              |        |       | xxxx xxxx | uuuu uuuu                |                                 |

| 10Ch                    | EEDATA | EEPRON | EEPROM Data Register, Low Byte                     |            |           |              |        |       |           | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | —      | —                                                  | EEPRO      | M Data Re | egister, Hig | h Byte |       |           | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | _                                                  | _          | —         | WRERR        | WREN   | WR    | RD        | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPRON | EEPROM Control Register2 (not a physical register) |            |           |              |        |       |           | _                        | _                               |

| 8Dh                     | PIE2   | —      | (1)                                                |            | EEIE      | BCLIE        | —      | _     | CCP2IE    | -r-0 00                  | -r-0 00                         |

| 0Dh                     | PIR2   | _      | (1)                                                | _          | EEIF      | BCLIF        | _      | _     | CCP2IF    | -r-0 00                  | -r-0 00                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

| TABLE 5-1: | <b>REGISTERS ASSOCIATED WITH TIMER0</b> |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| Address               | Name       | Bit 7  | Bit 6      | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|------------|----------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Module's F | Register | •     |       |       |       |       | XXXX XXXX                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE     | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | T0CS     | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### **REGISTER 9-2:** SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL SSPOV SSPM0 SSPEN CKP SSPM3 SSPM2 SSPM1 bit 7 bit 0 bit 7 WCOL: Write Collision Detect bit Master mode: 1 = A write to SSPBUF was attempted while the I2C conditions were not valid 0 = No collision Slave mode: 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software) 0 = No collision bit 6 SSPOV: Receive Overflow Indicator bit In SPI mode: 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.) 0 = No overflowIn I<sup>2</sup>C mode: 1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.) 0 = No overflowSSPEN: Synchronous Serial Port Enable bit bit 5 In SPI mode, When enabled, these pins must be properly configured as input or output 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins In I<sup>2</sup>C mode, When enabled, these pins must be properly configured as input or output 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins bit 4 CKP: Clock Polarity Select bit In SPI mode: 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level In I<sup>2</sup>C Slave mode: SCK release control 1 = Enable clock 0 = Holds clock low (clock stretch). (Used to ensure data setup time.) In I<sup>2</sup>C Master mode: Unused in this mode bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits 0000 = SPI Master mode, clock = Fosc/4 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64 0011 = SPI Master mode, clock = TMR2 output/2 0100 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled. 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin. $0110 = I^2C$ Slave mode, 7-bit address $0111 = I^2C$ Slave mode, 10-bit address 1000 = I<sup>2</sup>C Master mode, clock = Fosc / (4 \* (SSPADD+1)) $1011 = I^2C$ Firmware Controlled Master mode (slave idle) 1110 = I<sup>2</sup>C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled 1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled 1001, 1010, 1100, 1101 = Reserved

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|       | R/W-0                  | R/W-0                                                          | R/W-0                       | R/W-0                      | R/W-0                   | R/W-0         | R/W-0         | R/W-0       |

|-------|------------------------|----------------------------------------------------------------|-----------------------------|----------------------------|-------------------------|---------------|---------------|-------------|

|       | GCEN                   | ACKSTAT                                                        | ACKDT                       | ACKEN                      | RCEN                    | PEN           | RSEN          | SEN         |

|       | bit 7                  |                                                                |                             |                            |                         |               |               | bit 0       |

| bit 7 | 1 = Enable             | eneral Call En<br>e interrupt whe                              | en a genera                 |                            |                         | received in   | the SSPSR     | 2           |

| bit 6 | ACKSTAT                | Acknowledg                                                     | e Status bit                | (In I <sup>2</sup> C Maste | er mode onl             | у)            |               |             |

|       | 1 = Acknow             | <u>Transmit mod</u><br>wledge was n<br>wledge was re           | ot received                 |                            |                         |               |               |             |

| bit 5 | ACKDT: A               | cknowledge [                                                   | Data bit (In I <sup>4</sup> | <sup>2</sup> C Master m    | ode only)               |               |               |             |

|       | Value that end of a re | knowledge                                                      |                             | the user initi             | ates an Ack             | nowledge s    | equence at    | the         |

| bit 4 | ACKEN: A               | cknowledge \$                                                  | Sequence E                  | nable bit (In              | I <sup>2</sup> C Master | mode only)    |               |             |

|       | 1 = Initiate<br>Autom  | Receive mode<br>Acknowledge<br>atically cleare<br>wledge seque | e sequence<br>ed by hardw   |                            | I SCL pins a            | and transmit  | ACKDT da      | ta bit.     |

| bit 3 | RCEN: Re               | ceive Enable<br>es Receive mo                                  | bit (In I <sup>2</sup> C M  | laster mode                | only)                   |               |               |             |

| bit 2 | PEN: STC               | P Condition I                                                  | Enable bit (I               | n I <sup>2</sup> C Master  | r mode only             | )             |               |             |

|       | 1 = Initiate           | ase Control:<br>STOP condit<br>condition idle                  |                             | and SCL pir                | ns. Automat             | ically cleare | d by hardwa   | are.        |

| bit 1 | 1 = Initiate           | epeated STAR<br>Repeated ST/<br>ted START co                   | ART conditic                | on on SDA an               |                         |               |               | / hardware. |

| bit 0 | 1 = Initiate           | RT Condition<br>START cond<br>condition idl                    | lition on SD/               |                            |                         |               | ed by hardv   | vare.       |

|       |                        | For bits ACK<br>mode, this bit<br>writes to the \$             | may not be                  | set (no spo                |                         |               |               |             |

|       | Logondi                |                                                                |                             |                            |                         |               |               |             |

|       | Legend:<br>R = Reada   | blo bit                                                        | \\/ _ \\/.                  | itable bit                 |                         | plemented k   | hit road as f | 0'          |

|       | K = Keaua              |                                                                | vv = vvi                    |                            | 0 = 0.000               |               | n, reau as    | 0           |

'1' = Bit is set

'0' = Bit is cleared

## REGISTER 9-3: SSPCON2: SYNC SERIAL PORT CONTROL REGISTER2 (ADDRESS 91h)

- n = Value at POR

x = Bit is unknown

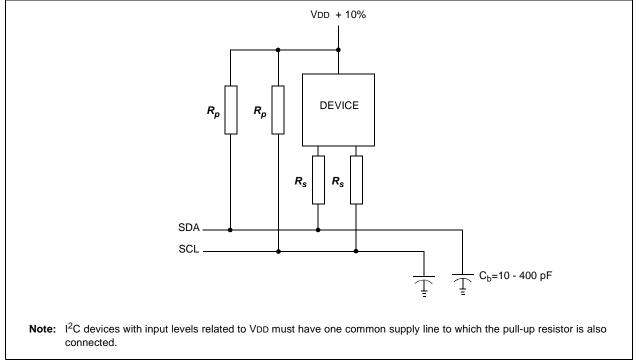

# 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^{2}C$  bus devices, the values of resistors  $R_{p}$  and  $R_{s}$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_{p}$ , due to the specified minimum sink current of 3 mA at VOL max = 0.4V, for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_p$ min =  $(5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-27. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

NOTES:

# 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

## 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6                         | Bit 5                                                                   | Bit 4                                    | Bit 3      | Bit 2   | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|-------------------------------|-------------------------------------------------------------------------|------------------------------------------|------------|---------|--------|--------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                          | TOIE                                                                    | INTE                                     | RBIE       | TOIF    | INTF   | RBIF   | 0000 000x               | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                          | RCIF                                                                    | TXIF                                     | SSPIF      | CCP1IF  | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                          | RCIE                                                                    | TXIE                                     | SSPIE      | CCP1IE  | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                         |

| 1Eh                   | ADRESH | A/D Resul            | A/D Result Register High Byte |                                                                         |                                          |            |         |        |        | xxxx xxxx               | uuuu uuuu                         |

| 9Eh                   | ADRESL | A/D Resul            | t Register                    | Low Byt                                                                 | e                                        |            |         |        |        | xxxx xxxx               | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0                         | CHS2                                                                    | CHS1                                     | CHS0       | GO/DONE | _      | ADON   | 0000 00-0               | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | —                             | _                                                                       | _                                        | PCFG3      | PCFG2   | PCFG1  | PCFG0  | 0- 0000                 | 0- 0000                           |

| 85h                   | TRISA  | —                    | —                             | PORTA                                                                   | Data Directio                            | n Register |         |        |        | 11 1111                 | 11 1111                           |

| 05h                   | PORTA  |                      | —                             | <ul> <li>PORTA Data Latch when written: PORTA pins when read</li> </ul> |                                          |            |         |        | ad     | 0x 0000                 | 0u 0000                           |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF                           | IBOV                                                                    | IBOV PSPMODE — PORTE Data Direction bits |            |         |        |        | 0000 -111               | 0000 -111                         |

| 09h <sup>(1)</sup>    | PORTE  | —                    | —                             |                                                                         | —                                        | —          | RE2     | RE1    | RE0    | xxx                     | uuu                               |

## TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

# 14.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC16F87X and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. The MPLAB ICD utilizes the in-circuit debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 14.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

## 14.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 14.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 14.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| PIC16LF8<br>(Comme             | <b>73/874/87</b><br>ercial, Indu |                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                                                                                                                        |     |       |                                            |  |  |  |

|--------------------------------|----------------------------------|-------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------------|--|--|--|

| PIC16F87<br>PIC16F87<br>(Comme |                                  | /877-20                                   |                                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial |     |       |                                            |  |  |  |

| Param<br>No.                   | Symbol                           | Characteristic/<br>Device                 | Min                                                  | Тур†                                                                                                                                                                                   | Мах | Units | Conditions                                 |  |  |  |

|                                | IPD                              | Power-down Current <sup>(3,5)</sup>       |                                                      |                                                                                                                                                                                        |     |       |                                            |  |  |  |

| D020                           |                                  | 16LF87X                                   | _                                                    | 7.5                                                                                                                                                                                    | 30  | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D020                           |                                  | 16F87X                                    |                                                      | 10.5                                                                                                                                                                                   | 42  | μA    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021                           |                                  | 16LF87X                                   | _                                                    | 0.9                                                                                                                                                                                    | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>0°C to +70°C   |  |  |  |

| D021                           |                                  | 16F87X                                    | _                                                    | 1.5                                                                                                                                                                                    | 16  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021A                          |                                  | 16LF87X                                   |                                                      | 0.9                                                                                                                                                                                    | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

| D021A                          |                                  | 16F87X                                    |                                                      | 1.5                                                                                                                                                                                    | 19  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |  |

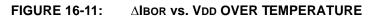

| D023                           | ΔIBOR                            | Brown-out<br>Reset Current <sup>(6)</sup> | _                                                    | 85                                                                                                                                                                                     | 200 | μΑ    | BOR enabled, VDD = 5.0V                    |  |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHARACTERISTICS |       |                                         |                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |       |                                                             |  |

|--------------------|-------|-----------------------------------------|-------------------|------------------------------------------------------|---------|-------|-------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                          | Min               | Тур†                                                 | Max     | Units | Conditions                                                  |  |

|                    | VIL   | Input Low Voltage                       |                   |                                                      |         |       |                                                             |  |

|                    |       | I/O ports                               |                   |                                                      |         |       |                                                             |  |

| D030               |       | with TTL buffer                         | Vss               | —                                                    | 0.15Vdd | V     | For entire VDD range                                        |  |

| D030A              |       |                                         | Vss               | —                                                    | 0.8V    | V     | $4.5V \le VDD \le 5.5V$                                     |  |

| D031               |       | with Schmitt Trigger buffer             | Vss               | —                                                    | 0.2Vdd  | V     |                                                             |  |

| D032               |       | MCLR, OSC1 (in RC mode)                 | Vss               | —                                                    | 0.2Vdd  | V     |                                                             |  |

| D033               |       | OSC1 (in XT, HS and LP)                 | Vss               | —                                                    | 0.3Vdd  | V     | (Note 1)                                                    |  |

|                    |       | Ports RC3 and RC4                       |                   | —                                                    |         |       |                                                             |  |

| D034               |       | with Schmitt Trigger buffer             | Vss               | —                                                    | 0.3Vdd  | V     | For entire VDD range                                        |  |

| D034A              |       | with SMBus                              | -0.5              | —                                                    | 0.6     | V     | for VDD = 4.5 to 5.5V                                       |  |

|                    | Vih   | Input High Voltage                      |                   |                                                      | r       |       | 1                                                           |  |

|                    |       | I/O ports                               |                   | —                                                    |         |       |                                                             |  |

| D040               |       | with TTL buffer                         | 2.0               | —                                                    | Vdd     | -     | $4.5V \leq VDD \leq 5.5V$                                   |  |

| D040A              |       |                                         | 0.25VDD<br>+ 0.8V | _                                                    | Vdd     | V     | For entire VDD range                                        |  |

| D041               |       | with Schmitt Trigger buffer             | 0.8Vdd            | —                                                    | Vdd     | V     | For entire VDD range                                        |  |

| D042               |       | MCLR                                    | 0.8Vdd            | —                                                    | Vdd     | V     |                                                             |  |

| D042A              |       | OSC1 (XT, HS and LP)                    | 0.7Vdd            | —                                                    | Vdd     | V     | (Note 1)                                                    |  |

| D043               |       | OSC1 (in RC mode)<br>Ports RC3 and RC4  | 0.9Vdd            |                                                      | Vdd     | V     |                                                             |  |

| D044               |       | with Schmitt Trigger buffer             | 0.7Vdd            | —                                                    | Vdd     | V     | For entire VDD range                                        |  |

| D044A              |       | with SMBus                              | 1.4               | —                                                    | 5.5     | V     | for VDD = 4.5 to 5.5V                                       |  |

| D070               | IPURB | PORTB Weak Pull-up Current              | 50                | 250                                                  | 400     | μA    | VDD = 5V, VPIN = VSS,<br>-40°С то +85°С                     |  |

|                    | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                   | •                                                    |         |       |                                                             |  |

| D060               |       | I/O ports                               | —                 | —                                                    | ±1      | μΑ    | $Vss \le VPIN \le VDD$ ,<br>Pin at hi-impedance             |  |

| D061               |       | MCLR, RA4/T0CKI                         | _                 | _                                                    | ±5      | uΑ    | $Vss \leq VPIN \leq VDD$                                    |  |

| D063               |       | OSC1                                    | —                 | _                                                    | ±5      | •     | $Vss \le VPIN \le VDD$ , XT, HS<br>and LP osc configuration |  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

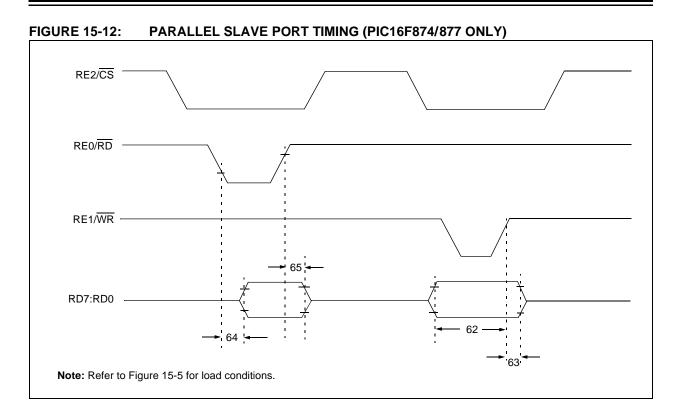

# TABLE 15-6: PARALLEL SLAVE PORT REQUIREMENTS (PIC16F874/877 ONLY)

| Parameter<br>No. | Symbol   | Characteristic                                                                                        |              | Min      | Тур† | Max      | Units    | Conditions             |

|------------------|----------|-------------------------------------------------------------------------------------------------------|--------------|----------|------|----------|----------|------------------------|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (setup time)                  |              | 20<br>25 | _    | _        | ns<br>ns | Extended<br>Range Only |

| 63*              | TwrH2dtl | $\overline{\text{WR}}^{\uparrow}$ or $\overline{\text{CS}}^{\uparrow}$ to data–in invalid (hold time) | Standard(F)  | 20       |      | —        | ns       |                        |

|                  |          |                                                                                                       | Extended(LF) | 35       |      | —        | ns       |                        |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid                             |              | -        | _    | 80<br>90 | ns<br>ns | Extended<br>Range Only |

| 65               | TrdH2dtl | $\overline{RD}^{\uparrow}$ or $\overline{CS}^{\downarrow}$ to data–out invalid                        |              | 10       | —    | 30       | ns       |                        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

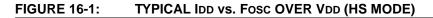

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented is **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at 25°C. 'max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

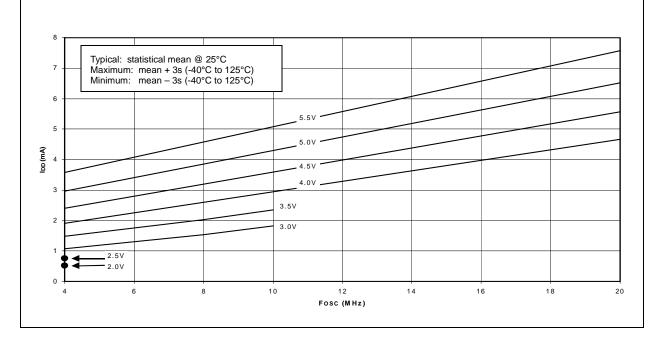

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (HS MODE)

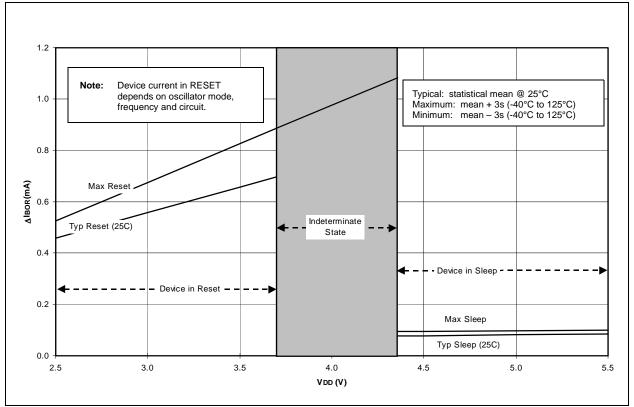

FIGURE 16-12: TYPICAL AND MAXIMUM △ITMR1 vs. VDD OVER TEMPERATURE (-10°C TO 70°C, TIMER1 WITH OSCILLATOR, XTAL=32 kHZ, C1 AND C2=50 pF)

# Package Marking Information (Cont'd)

## 44-Lead TQFP

## Example

$\bigcirc$

Example

$\lambda \lambda$

PIC16F877-04/P

0112SAA

MICROCHIP

## 44-Lead MQFP

## Example

## 44-Lead PLCC

### Example

\_\_\_\_\_

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |  |  |

|------------|----------------|--|--|

|            | CONSIDERATIONS |  |  |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |  |  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|--|--|

| Pins              | 28/40                                               | 28/40                                                      |  |  |

| Timers            | 3                                                   | 3                                                          |  |  |

| Interrupts        | 11 or 12                                            | 13 or 14                                                   |  |  |

| Communication     | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Slave) | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Master/Slave) |  |  |

| Frequency         | Frequency 20 MHz                                    |                                                            |  |  |

| Voltage           | 2.5V - 5.5V                                         | 2.0V - 5.5V                                                |  |  |

| A/D               | 8-bit                                               | 10-bit                                                     |  |  |

| CCP               | 2                                                   | 2                                                          |  |  |

| Program<br>Memory | 4K, 8K<br>EPROM                                     | 4K, 8K<br>FLASH                                            |  |  |

| RAM               | 192, 368<br>bytes                                   | 192, 368<br>bytes                                          |  |  |

| EEPROM data       | None                                                | 128, 256<br>bytes                                          |  |  |

| Other             | _                                                   | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming      |  |  |

# INDEX

Α

| A/D1                                       | 11  |

|--------------------------------------------|-----|

| Acquisition Requirements1                  |     |

| ADCON0 Register                            |     |

| ADCON1 Register                            |     |

| ADIF bit                                   |     |

| Analog Input Model Block Diagram1          |     |

| Analog Port Pins                           |     |

| Associated Registers and Bits              |     |

| Block Diagram                              |     |

| Calculating Acquisition Time1              |     |

| Configuring Analog Port Pins1              |     |

| Configuring the Interrupt1                 |     |

| Configuring the Module1                    |     |

| Conversion Clock                           |     |

| Conversions1                               |     |

| Delays1                                    |     |

| Effects of a RESET1                        |     |

| GO/DONE bit                                |     |

| Internal Sampling Switch (Rss) Impedence   |     |

| Operation During SLEEP1                    |     |

| Result Registers1                          |     |

| Sampling Requirements1                     |     |

| Source Impedence1                          |     |

| Time Delays1                               |     |

| Absolute Maximum Ratings                   |     |

| ACK                                        |     |

| Acknowledge Data bit                       |     |

| Acknowledge Pulse                          |     |

| Acknowledge Sequence Enable bit            |     |

| Acknowledge Status bit                     |     |

| ADRES Register                             |     |

| Analog Port Pins. See A/D                  | • • |

| Analog-to-Digital Converter. See A/D       |     |

| Application Notes                          |     |

| AN552 (Implementing Wake-up on Key Strokes |     |

| Using PIC16CXXX)                           | 31  |

| AN556 (Implementing a Table Read)          |     |

| AN578 (Use of the SSP Module in the I2C    | 20  |

| Multi-Master Environment)                  | 73  |

| Architecture                               | 10  |

| PIC16F873/PIC16F876 Block Diagram          | 5   |

| PIC16F874/PIC16F877 Block Diagram          |     |

| Assembler                                  | 0   |

| MPASM Assembler1                           | 12  |

|                                            | 43  |

| В                                          |     |

| Banking, Data Memory 12,                   | 18  |

| Baud Rate Generator                        |     |

| BCLIF                                      |     |

| BF74, 82,                                  |     |

| Block Diagrams                             | 57  |

| A/D1                                       | 13  |

| A/D Converter                              |     |

|                                            |     |

Analog Input Model

114

Baud Rate Generator

79

Capture Mode

59

Compare Mode

60

I<sup>2</sup>C Master Mode

78

I<sup>2</sup>C Module

73

I<sup>2</sup>C Slave Mode

73

Interrupt Logic

129

PIC16F873/PIC16F876

5

| PIC16F874/PIC16F877                             | 6        |

|-------------------------------------------------|----------|

| PORTA                                           |          |

| RA3:RA0 and RA5 Pins                            |          |

| RA4/T0CKI Pin                                   | 29       |

| PORTB                                           |          |

| RB3:RB0 Port Pins                               |          |

| RB7:RB4 Port Pins                               | 31       |

| PORTC                                           |          |

| Peripheral Output Override (RC 0:2, 5:7)        |          |

| Peripheral Output Override (RC 3:4)             |          |

| PORTD                                           |          |

| PORTD and PORTE (Parallel Slave Port)           |          |

| PORTE                                           | 36       |

| PWM Mode                                        | 61       |

| RESET Circuit                                   | 123      |

| SSP (I <sup>2</sup> C Mode)                     | 73       |

| SSP (SPI Mode)                                  |          |

| Timer0/WDT Prescaler                            | 47       |

| Timer1                                          | 52       |

| Timer2                                          | 55       |

| USART Asynchronous Receive                      | 101      |

| USART Asynchronous Receive (9-bit Mode)         | 103      |

| USART Transmit                                  | 99       |

| Watchdog Timer                                  | 131      |

| BOR. See Brown-out Reset                        |          |

| BRG                                             | 79       |

| BRGH bit                                        |          |

| Brown-out Reset (BOR) 119, 123, 7               | 125, 126 |

| BOR Status (BOR Bit)                            | 25       |

| Buffer Full bit, BF                             | 74       |

| Bus Arbitration                                 | 89       |

| Bus Collision Section                           | 89       |

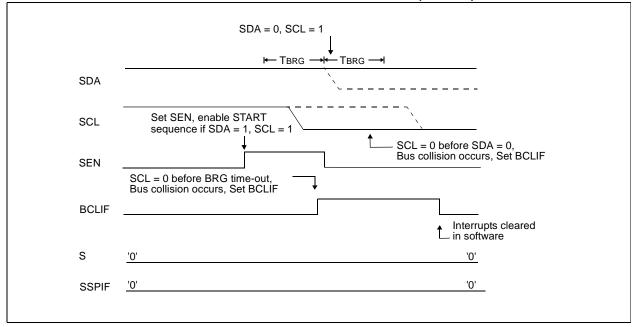

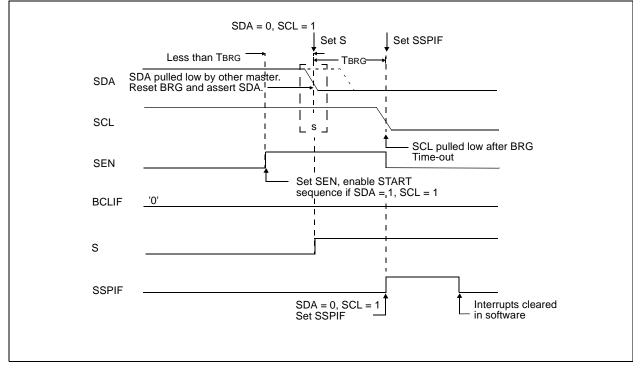

| Bus Collision During a Repeated START Condition | 92       |

| Bus Collision During a START Condition          |          |

| Bus Collision During a STOP Condition           | 93       |

| Bus Collision Interrupt Flag bit, BCLIF         | 24       |

|                                                 |          |

## С

| Capture/Compare/PWM (CCP)              | 57   |

|----------------------------------------|------|

| Associated Registers                   |      |

| Capture, Compare and Timer1            | 62   |

| PWM and Timer2                         | 63   |

| Capture Mode                           | 59   |

| Block Diagram                          | 59   |

| CCP1CON Register                       | 58   |

| CCP1IF                                 | 59   |

| Prescaler                              | 59   |

| CCP Timer Resources                    | 57   |

| CCP1                                   |      |

| RC2/CCP1 Pin                           | 7, 9 |

| CCP2                                   |      |

| RC1/T1OSI/CCP2 Pin                     | 7, 9 |

| Compare                                |      |

| Special Trigger Output of CCP1         | 60   |

| Special Trigger Output of CCP2         | 60   |

| Compare Mode                           | 60   |

| Block Diagram                          | 60   |

| Software Interrupt Mode                |      |

| Special Event Trigger                  | 60   |

| Interaction of Two CCP Modules (table) | 57   |

|                                        |      |

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

## Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

## www.microchip.com

The file transfer site is available by using an FTP service to connect to:

## ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:       | To: Technical Publications Manager Total Pa                                            | ges Sent           |

|-----------|----------------------------------------------------------------------------------------|--------------------|

| RE:       | RE: Reader Response                                                                    |                    |

| From      | From: Name                                                                             |                    |

|           | Company                                                                                |                    |

|           | Address                                                                                |                    |

|           | City / State / ZIP / Country                                                           |                    |

|           | Telephone: () FAX: (                                                                   | )                  |

| Appl      | Application (optional):                                                                |                    |

| Wou       | Would you like a reply?YN                                                              |                    |

| Devi      | Device: PIC16F87X Literature Number: DS30292D                                          |                    |

| Que       | Questions:                                                                             |                    |

| 1. \      | 1. What are the best features of this document?                                        |                    |

|           |                                                                                        |                    |

| _         |                                                                                        |                    |

| 2. ł      | 2. How does this document meet your hardware and software development                  | needs?             |

| -         |                                                                                        |                    |

| -<br>2 [  | 2. Do you find the experimentian of this data sheet easy to follow? If not why         | 5                  |

| 3. I      | 3. Do you find the organization of this data sheet easy to follow? If not, why?        |                    |

| -         |                                                                                        |                    |

| 4. \      | 4. What additions to the data sheet do you think would enhance the structure           | e and subject?     |

| -         |                                                                                        |                    |

|           |                                                                                        |                    |

| 5. \      | 5. What deletions from the data sheet could be made without affecting the o            | verall usefulness? |

| -         |                                                                                        |                    |

| 6. I      | 6. Is there any incorrect or misleading information (what and where)?                  |                    |

| _         |                                                                                        |                    |

| -         |                                                                                        |                    |

| 7. H      | 7. How would you improve this document?                                                |                    |

| -         |                                                                                        |                    |

| -<br>8. H | <ol> <li>How would you improve our software, systems, and silicon products?</li> </ol> |                    |

|           |                                                                                        |                    |