Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-20i-p |

| P | IC1 | 6 | F8 | <b>7</b> X |

|---|-----|---|----|------------|

|   |     | v |    | ,,,,       |

NOTES:

# PIC16F87X

NOTES:

TABLE 8-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address                | Name    | Bit 7                | Bit 6                                                  | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PO<br>BO | R,   | Valu<br>all o<br>RES |      |

|------------------------|---------|----------------------|--------------------------------------------------------|-------------|---------|---------|--------|---------|---------|-------------------|------|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                                   | TOIE        | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                   | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000                 | 0000 |

| 0Dh                    | PIR2    | _                    | _                                                      | _           | _       | _       | _      | _       | CCP2IF  |                   | 0    |                      | 0    |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                   | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000                 | 0000 |

| 8Dh                    | PIE2    | _                    |                                                        | -           |         |         | _      | _       | CCP2IE  |                   | 0    |                      | 0    |

| 87h                    | TRISC   | PORTC D              | Data Direction                                         | n Register  |         |         |        |         |         | 1111              | 1111 | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Regi                                           | ster        |         |         |        |         |         | 0000              | 0000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Perio                                          | od Register |         |         |        |         |         | 1111              | 1111 | 1111                 | 1111 |

| 12h                    | T2CON   | _                    | TOUTPS3                                                | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PW                                             | /M Register | 1 (LSB) |         |        |         |         | xxxx              | xxxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PW                                             | /M Register | 1 (MSB) |         |        |         |         | xxxx              | xxxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | _                    | _                                                      | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00                | 0000 | 00                   | 0000 |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB)                    |             |         |         |        |         |         | uuuu              |      |                      |      |

| 1Ch                    | CCPR2H  | Capture/C            | apture/Compare/PWM Register2 (MSB) xxxx xxxx uuuu uuuu |             |         |         |        |         |         | uuuu              |      |                      |      |

| 1Dh                    | CCP2CON | _                    | _                                                      | CCP2X       | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00                | 0000 | 00                   | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

#### **REGISTER 9-2:** SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0 |   |

|-------|-------|-------|-------|-------|-------|-------|-------|---|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | 1 |

| bit 7 |       |       |       |       |       |       | bit 0 |   |

bit 0

WCOL: Write Collision Detect bit bit 7

Master mode:

- 1 = A write to SSPBUF was attempted while the I2C conditions were not valid

- 0 = No collision

#### Slave mode:

- 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software)

- 0 = No collision

- bit 6 SSPOV: Receive Overflow Indicator bit

#### In SPI mode:

- 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

#### In I<sup>2</sup>C mode:

- 1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

- 0 = No overflow

- bit 5 SSPEN: Synchronous Serial Port Enable bit

#### In SPI mode,

When enabled, these pins must be properly configured as input or output

- 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

#### In I<sup>2</sup>C mode,

When enabled, these pins must be properly configured as input or output

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4 CKP: Clock Polarity Select bit

#### In SPI mode:

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

## In I<sup>2</sup>C Slave mode:

## SCK release control

- 1 = Enable clock

- 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

#### In I<sup>2</sup>C Master mode:

Unused in this mode

- bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI Master mode, clock = Fosc/4

- 0001 = SPI Master mode, clock = Fosc/16

- 0010 = SPI Master mode, clock = Fosc/64

- 0011 = SPI Master mode, clock = TMR2 output/2

- 0100 = SPI Slave mode, clock = SCK pin. SS pin control enabled.

- 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin.

- $0110 = I^2C$  Slave mode, 7-bit address

- $0111 = I^2C$  Slave mode, 10-bit address

- 1000 =  $I^2C$  Master mode, clock = Fosc / (4 \* (SSPADD+1))

- 1011 = I<sup>2</sup>C Firmware Controlled Master mode (slave idle)

- 1110 = I<sup>2</sup>C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled 1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled

- 1001, 1010, 1100, 1101 = Reserved

| Ιe | a | er     | nd |   |

|----|---|--------|----|---|

|    | ч | $\sim$ | ·u | • |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data, when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

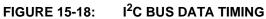

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte.

For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

Note: Following the Repeated START condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

## 9.2.1.2 Slave Reception

Note:

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address                | Name    | Bit 7                  | Bit 6                                                  | Bit 5       | Bit 4       | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR,<br>WDT |

|------------------------|---------|------------------------|--------------------------------------------------------|-------------|-------------|-----------|--------|--------|--------|-----------------------|------------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE                                                   | TOIE        | INTE        | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u                          |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup>   | ADIF                                                   | RCIF        | TXIF        | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                          |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup>   | ADIE                                                   | RCIE        | TXIE        | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                          |

| 0Dh                    | PIR2    | _                      | (2)                                                    | _           | EEIF        | BCLIF     | _      | _      | CCP2IF | -r-0 00               | -r-0 00                            |

| 8Dh                    | PIE2    | _                      | (2)                                                    | _           | EEIE        | BCLIE     | _      | _      | CCP2IE | -r-0 00               | -r-0 00                            |

| 13h                    | SSPBUF  | Synchrono              | ous Serial Po                                          | t Receive I | Buffer/Trar | nsmit Reg | ister  |        |        | xxxx xxxx             | uuuu uuuu                          |

| 14h                    | SSPCON  | WCOL                   | SSPOV                                                  | SSPEN       | CKP         | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000 0000             | 0000 0000                          |

| 91h                    | SSPCON2 | GCEN                   | ACKSTAT                                                | ACKDT       | ACKEN       | RCEN      | PEN    | RSEN   | SEN    | 0000 0000             | 0000 0000                          |

| 93h                    | SSPADD  | I <sup>2</sup> C Slave | <sup>2</sup> C Slave Address/Master Baud Rate Register |             |             |           |        |        |        | 0000 0000             | 0000 0000                          |

| 94h                    | SSPSTAT | SMP                    | CKE                                                    | D/A         | Р           | S         | R/W    | UA     | BF     | 0000 0000             | 0000 0000                          |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

Note 1: These bits are reserved on PIC16F873/876 devices; always maintain these bits clear.

<sup>2:</sup> These bits are reserved on these devices; always maintain these bits clear.

## 10.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

## 10.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 10-6. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 10-9). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 10-10). This is advantageous when slow baud rates are selected, since the BRG is kept in RESET when bits TXEN, CREN and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally, when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hiimpedance. If either bit CREN or bit SREN is set during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic, however, is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting, since bit TXEN is still set. The DT line will immediately switch from hiimpedance Receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

## 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/ $\overline{DONE}$  bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To allow the conversion to occur during SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

#### 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

| Address               | Name   | Bit 7                | Bit 6      | Bit 5    | Bit 4                                                   | Bit 3      | Bit 2    | Bit 1        | Bit 0  | Value on<br>POR,<br>BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|------------|----------|---------------------------------------------------------|------------|----------|--------------|--------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE     | INTE                                                    | RBIE       | TOIF     | INTF         | RBIF   | 0000 000x               | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF     | TXIF                                                    | SSPIF      | CCP1IF   | TMR2IF       | TMR1IF | 0000 0000               | 0000 0000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE     | TXIE                                                    | SSPIE      | CCP1IE   | TMR2IE       | TMR1IE | 0000 0000               | 0000 0000                         |

| 1Eh                   | ADRESH | A/D Resul            | t Register | High Byt | te                                                      |            |          |              |        | xxxx xxxx               | uuuu uuuu                         |

| 9Eh                   | ADRESL | A/D Resul            | t Register | Low Byte | е                                                       |            |          |              |        | xxxx xxxx               | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2     | CHS1                                                    | CHS0       | GO/DONE  | _            | ADON   | 0000 00-0               | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | _          | _        | _                                                       | PCFG3      | PCFG2    | PCFG1        | PCFG0  | 0- 0000                 | 0- 0000                           |

| 85h                   | TRISA  | _                    | _          | PORTA    | Data Directio                                           | n Register |          |              |        | 11 1111                 | 11 1111                           |

| 05h                   | PORTA  | _                    | _          | PORTA    | PORTA Data Latch when written: PORTA pins when read0x 0 |            |          |              |        | 0x 0000                 | 0u 0000                           |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF        | IBOV     | PSPMODE                                                 | _          | PORTE Da | ta Direction | n bits | 0000 -111               | 0000 -111                         |

| 09h <sup>(1)</sup>    | PORTE  | _                    | _          | _        | _                                                       | _          | RE2      | RE1          | RE0    | xxx                     | uuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers/bits are not available on the 28-pin devices.

TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | х   | 1  | 1  | Power-on Reset                                          |

| 0   | х   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | х   | х  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: x = don't care, u = unchanged

TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 1uuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

## 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

### 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- 5: LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

## 13.0 INSTRUCTION SET SUMMARY

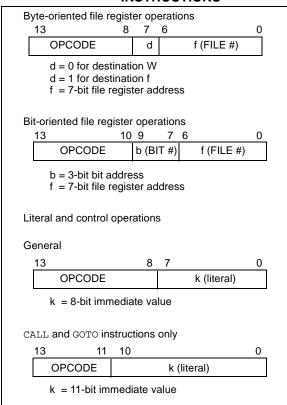

Each PIC16F87X instruction is a 14-bit word, divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F87X instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                |

| W     | Working register (accumulator)                                                                                                                                      |

| b     | Bit address within an 8-bit file register                                                                                                                           |

| k     | Literal field, constant data or label                                                                                                                               |

| х     | Don't care location (= 0 or 1). The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W, $d = 1$ : store result in file register f. Default is $d = 1$ .                                                    |

| PC    | Program Counter                                                                                                                                                     |

| TO    | Time-out bit                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                      |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 13-2 lists the instructions recognized by the MPASM $^{TM}$  assembler.

Figure 13-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16F87X products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

## 13.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                         |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |

| BCF              | Bit Clear f                         |

|------------------|-------------------------------------|

| Syntax:          | [label] BCF f,b                     |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$   |

| Operation:       | $0 \rightarrow (f < b >)$           |

| Status Affected: | None                                |

| Description:     | Bit 'b' in register 'f' is cleared. |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BSF              | Bit Set f                         |

|------------------|-----------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b          |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$         |

| Status Affected: | None                              |

| Description:     | Bit 'b' in register 'f' is set.   |

|                  |                                   |

| ANDLW            | AND Literal with W                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                               |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                             |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2Tcy instruction. |

| ANDWF            | AND W with f                                                                                                                                       |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                                            |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                            |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.  If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2Tcy instruction. |

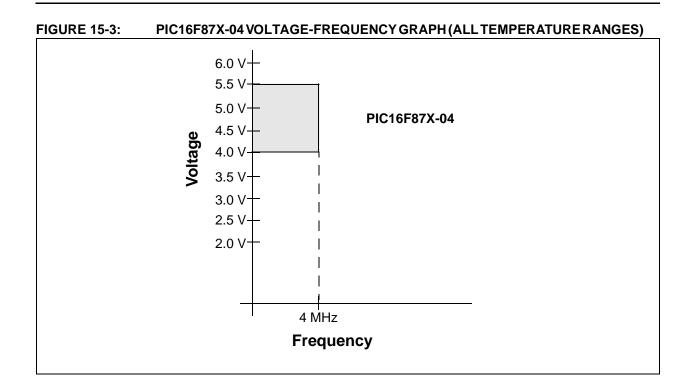

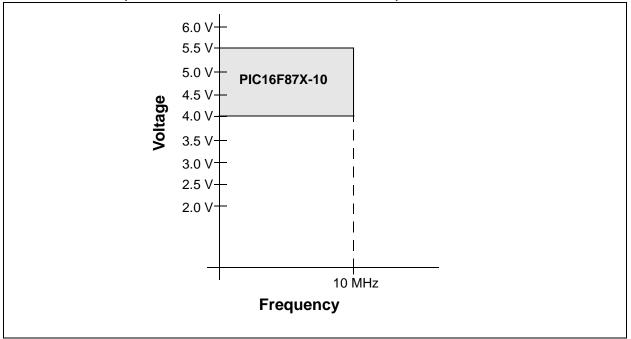

FIGURE 15-4: PIC16F87X-10 VOLTAGE-FREQUENCY GRAPH (EXTENDED TEMPERATURE RANGE ONLY)

#### 15.1 DC Characteristics:

PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| PIC16LF8<br>(Comme               | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for industrial $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for commercial |                                           |                                         |     |     |    |                                                                                                                    |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|-----|-----|----|--------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F873<br>PIC16F873<br>(Comme |                                                                                                                                                                                                                                       | /877-20                                   | 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |     |     |    | ns (unless otherwise stated) $C \le TA \le +85^{\circ}C$ for industrial $C \le TA \le +70^{\circ}C$ for commercial |  |  |

| Param<br>No.                     | Symbol                                                                                                                                                                                                                                | Characteristic/<br>Device                 | Min Typ† Max Units Conditions           |     |     |    |                                                                                                                    |  |  |

|                                  | IDD                                                                                                                                                                                                                                   | Supply Current <sup>(2,5)</sup>           |                                         |     |     |    |                                                                                                                    |  |  |

| D010                             |                                                                                                                                                                                                                                       | 16LF87X                                   | _                                       | 0.6 | 2.0 | mA | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V                                                               |  |  |

| D010                             |                                                                                                                                                                                                                                       | 16F87X                                    | _                                       | 1.6 | 4   | mA | RC osc configurations<br>Fosc = 4 MHz, VDD = 5.5V                                                                  |  |  |

| D010A                            |                                                                                                                                                                                                                                       | 16LF87X                                   | _                                       | 20  | 35  | μΑ | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled                                                 |  |  |

| D013                             |                                                                                                                                                                                                                                       | 16F87X                                    | _                                       | 7   | 15  | mA | HS osc configuration,<br>Fosc = 20 MHz, VDD = 5.5V                                                                 |  |  |

| D015                             | Δlbor                                                                                                                                                                                                                                 | Brown-out<br>Reset Current <sup>(6)</sup> | _                                       | 85  | 200 | μΑ | BOR enabled, VDD = 5.0V                                                                                            |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\overline{OSC1}$  = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20  $\mu$ A to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# 15.3 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |        |                                                                  |                               | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ |      |      |                                           |  |

|--------------------------------------------------------------------|--------|------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------|--|

| Param<br>No.                                                       | Symbol | Characteristic/<br>Device                                        | Min Typ† Max Units Conditions |                                                                                                                                            |      |      |                                           |  |

|                                                                    | VDD    | Supply Voltage                                                   |                               |                                                                                                                                            |      |      |                                           |  |

| D001                                                               |        |                                                                  | 4.0                           | _                                                                                                                                          | 5.5  | V    | LP, XT, RC osc configuration              |  |

| D001A                                                              |        |                                                                  | 4.5                           |                                                                                                                                            | 5.5  | V    | HS osc configuration                      |  |

| D001A                                                              |        |                                                                  | VBOR                          |                                                                                                                                            | 5.5  | V    | BOR enabled, FMAX = 10 MHz <sup>(7)</sup> |  |

| D002                                                               | VDR    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | _                             | 1.5                                                                                                                                        | _    | V    |                                           |  |

| D003                                                               | VPOR   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                             | Vss                                                                                                                                        | _    | V    | See section on Power-on Reset for details |  |

| D004                                                               | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal           | 0.05                          | _                                                                                                                                          | _    | V/ms | See section on Power-on Reset for details |  |

| D005                                                               | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                           | 4.0                                                                                                                                        | 4.35 | V    | BODEN bit in configuration word enabled   |  |

<sup>†</sup> Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- **4:** For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- **6:** The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

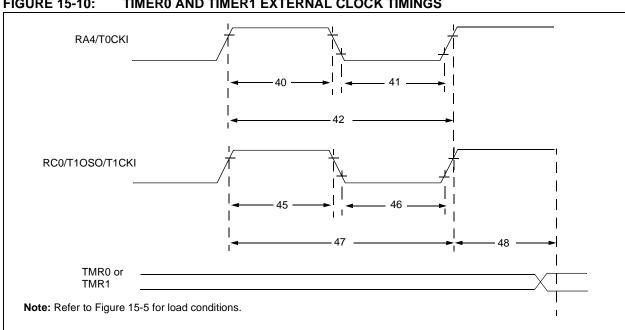

FIGURE 15-10: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 15-4: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Symbol    | Characteristic           |                                                                                 |                       | Min                   | Тур† | Max   | Units | Conditions         |

|--------------|-----------|--------------------------|---------------------------------------------------------------------------------|-----------------------|-----------------------|------|-------|-------|--------------------|

| 40*          | Tt0H      | T0CKI High Pulse Width   |                                                                                 | No Prescaler          | 0.5Tcy + 20           | _    | _     | ns    | Must also meet     |

|              |           |                          |                                                                                 | With Prescaler        | 10                    | _    | _     | ns    | parameter 42       |

| 41*          | Tt0L      | T0CKI Low Pulse          | Width                                                                           | No Prescaler          | 0.5Tcy + 20           | _    | _     | ns    | Must also meet     |

|              |           |                          |                                                                                 | With Prescaler        | 10                    | _    | _     | ns    | parameter 42       |

| 42*          | Tt0P      | T0CKI Period             |                                                                                 | No Prescaler          | Tcy + 40              | _    | _     | ns    |                    |

|              |           |                          |                                                                                 | With Prescaler        | Greater of:           | _    | _     | ns    | N = prescale value |

|              |           |                          |                                                                                 |                       | 20 or <u>Tcy + 40</u> |      |       |       | (2, 4,, 256)       |

|              |           |                          |                                                                                 |                       | N                     |      |       |       |                    |

| 45*          | Tt1H      | T1CKI High Time          | Synchronous, Pre                                                                |                       | 0.5Tcy + 20           | _    | _     | ns    | Must also meet     |

|              |           |                          | Synchronous,                                                                    | Standard(F)           | 15                    | _    | _     | ns    | parameter 47       |

|              |           |                          |                                                                                 | Extended( <b>LF</b> ) | 25                    | _    | _     | ns    |                    |

|              |           |                          | Asynchronous                                                                    | Standard(F)           | 30                    | _    | _     | ns    |                    |

|              |           |                          |                                                                                 | Extended( <b>LF</b> ) | 50                    | _    | _     | ns    |                    |

| 46*          | Tt1L      | T1CKI Low Time           | Synchronous, Pre                                                                |                       | 0.5Tcy + 20           | _    | 1     | ns    | Must also meet     |

|              |           |                          | Synchronous,                                                                    | Standard(F)           | 15                    | _    | _     | ns    | parameter 47       |

|              |           |                          | Prescaler = 2,4,8                                                               | Extended( <b>LF</b> ) | 25                    |      | ı     | ns    |                    |

|              |           |                          | Asynchronous                                                                    | Standard(F)           | 30                    |      | 1     | ns    |                    |

|              |           |                          |                                                                                 | Extended( <b>LF</b> ) | 50                    | _    | _     | ns    |                    |

| 47*          | Tt1P      | T1CKI input              | Synchronous                                                                     | Standard(F)           | Greater of:           | _    | _     | ns    | N = prescale value |

|              |           | period                   |                                                                                 |                       | 30 OR <u>TCY + 40</u> |      |       |       | (1, 2, 4, 8)       |

|              |           |                          |                                                                                 |                       | N                     |      |       |       |                    |

|              |           |                          |                                                                                 | Extended( <b>LF</b> ) | Greater of:           |      |       |       | N = prescale value |

|              |           |                          |                                                                                 |                       | 50 OR <u>TCY + 40</u> |      |       |       | (1, 2, 4, 8)       |

|              |           |                          | A                                                                               | 0(                    | N                     |      |       |       |                    |

|              |           |                          | Asynchronous                                                                    | Standard(F)           | 60                    | _    | _     | ns    |                    |

|              | F.4       | The second of the second | Extended( <b>LF</b> )                                                           |                       | 100<br>DC             | _    | _     | ns    |                    |

|              | Ft1       |                          | er1 oscillator input frequency range<br>illator enabled by setting bit T1OSCEN) |                       |                       | _    | 200   | kHz   |                    |

| 40           | TOVE 74m4 | •                        |                                                                                 |                       | 27000                 |      | 7T000 |       |                    |

| 48           |           | Delay from externa       |                                                                                 |                       | 2Tosc                 | _    | 7Tosc |       |                    |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

TABLE 15-8: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter No. | Symbol  | Characteristic  |              | Min  | Тур | Max | Units | Conditions                         |

|---------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|

| 90            | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for Repeated         |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   |       | START condition                    |

| 91            | Thd:sta | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period, the first clock |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   |       | pulse is generated                 |

| 92            | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                    |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   |       |                                    |

| 93            | Thd:sto | STOP condition  | 100 kHz mode | 4000 | _   | _   | ns    |                                    |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   |       |                                    |

## **INDEX**

| Α                                                                                                                    |                   |

|----------------------------------------------------------------------------------------------------------------------|-------------------|

| A/D111                                                                                                               |                   |

| Acquisition Requirements114                                                                                          |                   |

| ADCON0 Register111                                                                                                   |                   |

| ADCON1 Register112                                                                                                   |                   |

| ADIF bit112                                                                                                          |                   |

| Analog Input Model Block Diagram114                                                                                  |                   |

| Analog Port Pins                                                                                                     |                   |

| Associated Registers and Bits                                                                                        |                   |

| Block Diagram                                                                                                        |                   |

| Calculating Acquisition Time114 Configuring Analog Port Pins115                                                      |                   |

| Configuring the Interrupt113                                                                                         |                   |

| Configuring the Module113                                                                                            |                   |

| Conversion Clock                                                                                                     |                   |

| Conversions116                                                                                                       |                   |

| Delays114                                                                                                            |                   |

| Effects of a RESET117                                                                                                |                   |

| GO/DONE bit112                                                                                                       |                   |

| Internal Sampling Switch (Rss) Impedence114                                                                          |                   |

| Operation During SLEEP117                                                                                            |                   |

| Result Registers116                                                                                                  |                   |

| Sampling Requirements114                                                                                             |                   |

| Source Impedence                                                                                                     | BOR               |

| Time Delays114                                                                                                       | BRG               |

| Absolute Maximum Ratings                                                                                             | BRG               |

| ACK                                                                                                                  | Brov              |

| Acknowledge Pulse                                                                                                    |                   |

| Acknowledge Sequence Enable bit                                                                                      | Buffe             |

| Acknowledge Status bit                                                                                               | Bus               |

| ADRES Register                                                                                                       | Bus               |

| 7.21.20 1.0g.oto:                                                                                                    |                   |

| Analog Port Pins. See A/D                                                                                            | Bus               |

| Analog Port Pins. See A/D Analog-to-Digital Converter. See A/D                                                       | Bus               |

| Analog Port Pins. See A/D Analog-to-Digital Converter. See A/D Application Notes                                     | Bus<br>Bus        |

| Analog-to-Digital Converter. See A/D                                                                                 | Bus               |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus        |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes         AN552 (Implementing Wake-up on Key Strokes            | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes         AN552 (Implementing Wake-up on Key Strokes            | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes         AN552 (Implementing Wake-up on Key Strokes            | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes         AN552 (Implementing Wake-up on Key Strokes            | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes                   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes                   | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes                                                               | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes Using PIC16CXXX)  | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes  Using PIC16CXXX) | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes  Using PIC16CXXX) | Bus<br>Bus<br>Bus |

| Analog-to-Digital Converter. See A/D Application Notes  AN552 (Implementing Wake-up on Key Strokes  Using PIC16CXXX) | Bus<br>Bus<br>Bus |