Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-20i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                              | File<br>Address             | A                                                                     | File<br>ddress | /                   | File<br>Address |                         |              |  |  |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------|----------------|---------------------|-----------------|-------------------------|--------------|--|--|

| Indirect addr. <sup>(*)</sup>  | 00h                         | Indirect addr.(*)                                                     | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h         |  |  |

| TMR0                           | 01h                         | OPTION_REG                                                            | 81h            | TMR0                | 101h            | OPTION_REG              | 181h         |  |  |

| PCL                            | 02h                         | PCL                                                                   | 82h            | PCL                 | 102h            | PCL                     | 182h         |  |  |

| STATUS                         | 03h                         | STATUS                                                                | 83h            | STATUS              | 103h            | STATUS                  | 183h         |  |  |

| FSR                            | 04h                         | FSR                                                                   | 84h            | FSR                 | 104h            | FSR                     | 184h         |  |  |

| PORTA                          | 05h                         | TRISA                                                                 | 85h            |                     | 105h            |                         | 185h         |  |  |

| PORTB                          | 06h                         | TRISB                                                                 | 86h            | PORTB               | 106h            | TRISB                   | 186h         |  |  |

| PORTC                          | 07h                         | TRISC                                                                 | 87h            |                     | 107h            |                         | 187h         |  |  |

| PORTD <sup>(1)</sup>           | 08h                         | TRISD <sup>(1)</sup>                                                  | 88h            |                     | 108h            |                         | 188h         |  |  |

| PORTE <sup>(1)</sup>           | 09h                         | TRISE <sup>(1)</sup>                                                  | 89h            |                     | 109h            |                         | 189h         |  |  |

| PCLATH                         | 0Ah                         | PCLATH                                                                | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah         |  |  |

| INTCON                         | 0Bh                         | INTCON                                                                | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh         |  |  |

| PIR1                           | 0Ch                         | PIE1                                                                  | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł         |  |  |

| PIR2                           | 0Dh                         | PIE2                                                                  | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł         |  |  |

| TMR1L                          | 0Eh                         | PCON                                                                  | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh         |  |  |

| TMR1H                          | 0Fh                         |                                                                       | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh         |  |  |

| T1CON                          | 10h                         |                                                                       | 90h            |                     | 110h            |                         | 190h         |  |  |

| TMR2                           | 11h                         | SSPCON2                                                               | 91h            |                     |                 |                         |              |  |  |

| T2CON                          | 12h                         | PR2                                                                   | 92h            |                     |                 |                         |              |  |  |

| SSPBUF                         | 13h                         | SSPADD                                                                | 93h            |                     |                 |                         |              |  |  |

| SSPCON                         | 14h                         | SSPSTAT                                                               | 94h            |                     |                 |                         |              |  |  |

| CCPR1L                         | 15h                         |                                                                       | 95h            |                     |                 |                         |              |  |  |

| CCPR1H                         | 16h                         |                                                                       | 96h            |                     |                 |                         |              |  |  |

| CCP1CON                        | 17h                         |                                                                       | 97h            |                     |                 |                         |              |  |  |

| RCSTA                          | 18h                         | TXSTA                                                                 | 98h            |                     |                 |                         |              |  |  |

| TXREG                          | 19h                         | SPBRG                                                                 | 99h            |                     |                 |                         |              |  |  |

| RCREG                          | 1Ah                         |                                                                       | 9Ah            |                     |                 |                         |              |  |  |

| CCPR2L                         | 1Bh                         |                                                                       | 9Bh            |                     |                 |                         |              |  |  |

| CCPR2H                         | 1Ch                         |                                                                       | 9Ch            |                     |                 |                         |              |  |  |

| CCP2CON                        | 1Dh                         |                                                                       | 9Dh            |                     |                 |                         |              |  |  |

| ADRESH                         | 1Eh                         | ADRESL                                                                | 9Eh            |                     |                 |                         |              |  |  |

| ADCON0                         | 1Fh                         | ADCON1                                                                | 9Fh            |                     | 1206            |                         | 1A0h         |  |  |

|                                | 20h                         |                                                                       | A0h            |                     | 120h            |                         |              |  |  |

| General<br>Purpose<br>Register |                             | General<br>Purpose<br>Register                                        |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |              |  |  |

| 96 Bytes                       |                             | 96 Bytes                                                              |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h |  |  |

|                                | 754                         |                                                                       |                |                     | 1756            |                         | 4            |  |  |

| Bank 0                         | J 7Fh                       | Bank 1                                                                | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł         |  |  |

| * Not a<br>Note 1: These       | physical reg<br>e registers | data memory locat<br>gister.<br>are not implemen<br>are reserved, mai | ted on the     | e PIC16F873.        |                 |                         |              |  |  |

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                                              | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|--|--|--|--|--|--|

|               | GIE                                                                                                                | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |  |  |  |  |  |  |

|               | bit 7                                                                                                              |                               |               |              |                  |             |                | bit 0      |  |  |  |  |  |  |  |  |

|               |                                                                                                                    |                               |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 7         | GIE: Globa                                                                                                         | al Interrupt E                | nable bit     |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | s all unmas                   |               | ots          |                  |             |                |            |  |  |  |  |  |  |  |  |

| <b>h</b> :+ C |                                                                                                                    | es all interru                |               | L:4          |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 6         | -                                                                                                                  | pheral Interr                 | •             |              | -                |             |                |            |  |  |  |  |  |  |  |  |

|               | <ul> <li>1 = Enables all unmasked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul> |                               |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 5         |                                                                                                                    | 0 Overflow                    | =             |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | s the TMR0                    |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               | 0 = Disable                                                                                                        | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 4         |                                                                                                                    | /INT Externa                  | •             |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 3         |                                                                                                                    | Port Change                   |               | •            |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 0         |                                                                                                                    | s the RB po                   | •             |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | es the RB po                  |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 2         | TOIF: TMR                                                                                                          | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    |                               |               |              | eared in softwa  | re)         |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | register did                  |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

| bit 1         |                                                                                                                    | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |  |  |  |  |  |  |

| bit 0         |                                                                                                                    | Port Change                   | •             |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |  |  |  |  |  |  |

|               |                                                                                                                    | be cleared in<br>of the RB7:R | ,             | ve changed   | stato            |             |                |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |  |  |  |  |  |  |

|               | Legend:                                                                                                            |                               |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

|               | R = Reada                                                                                                          | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |  |  |  |  |  |  |

|               | - n = Value                                                                                                        |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |  |  |  |  |  |  |

|               |                                                                                                                    |                               |               |              |                  |             |                |            |  |  |  |  |  |  |  |  |

#### 2.2.2.8 PCON Register

The Power Control (PCON) Register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT), and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | —   | —   | —   |     | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

**BOR**: Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name                   | Bit# | Buffer                | Function                                                                                                                                          |

|------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 3-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                          | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | ORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                       | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**REGISTER 5-1: OPTION REG REGISTER**

DANA

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|               | R/W-1                                                                                                                                                                                                                                                                                           | R/W-1                                            | R/W-1        | R/W-1         | R/W-1          | R/W-1 R/W-1 |                | R/W-1  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|---------------|----------------|-------------|----------------|--------|--|--|--|--|

|               | RBPU                                                                                                                                                                                                                                                                                            | INTEDG                                           | T0CS         | TOSE          | PSA            | PS2         | PS1            | PS0    |  |  |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                           |                                                  |              |               |                |             |                | bit 0  |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                 |                                                  |              |               |                |             |                |        |  |  |  |  |

| bit 7         | RBPU                                                                                                                                                                                                                                                                                            |                                                  |              |               |                |             |                |        |  |  |  |  |

| bit 6         | INTEDG                                                                                                                                                                                                                                                                                          |                                                  |              |               |                |             |                |        |  |  |  |  |

| bit 5         | 1 = Transit                                                                                                                                                                                                                                                                                     | R0 Clock Sou<br>tion on T0CK<br>al instruction o | l pin        |               |                |             |                |        |  |  |  |  |

| bit 4         | 1 = Increm                                                                                                                                                                                                                                                                                      | R0 Source Ed<br>nent on high-t<br>nent on low-to | o-low trans  | sition on TOC | •              |             |                |        |  |  |  |  |

| bit 3         | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                                                                                                                                         |                                                  |              |               |                |             |                |        |  |  |  |  |

| bit 2-0       | PS2:PS0:                                                                                                                                                                                                                                                                                        | Prescaler Ra                                     | ite Select b | oits          |                |             |                |        |  |  |  |  |

|               | Bit Value                                                                                                                                                                                                                                                                                       | TMR0 Rate                                        | WDT Rat      | e             |                |             |                |        |  |  |  |  |

|               | 000         1:2         1:1 $001$ 1:4         1:2 $010$ 1:8         1:4 $011$ 1:16         1:8 $100$ 1:32         1:16 $101$ 1:64         1:32 $110$ 1:128         1:64 $111$ 1:256         1:128                                                                                               |                                                  |              |               |                |             |                |        |  |  |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                         |                                                  |              |               |                |             |                |        |  |  |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                       | able bit                                         | VV = V       | Vritable bit  | U = Unimple    | emented b   | it, read as '( | )'     |  |  |  |  |

|               | - n = Value                                                                                                                                                                                                                                                                                     | e at POR                                         | '1' = E      | Bit is set    | '0' = Bit is c | leared      | x = Bit is ur  | nknown |  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                 |                                                  |              |               |                |             |                |        |  |  |  |  |

| ily Reference | To avoid an unintended device RESET, the instruction sequence shown in the PIC <sup>®</sup> MCU Mid-Range Fam-<br>ily Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0<br>to the WDT. This sequence must be followed even if the WDT is disabled. |                                                  |              |               |                |             |                |        |  |  |  |  |

Note:

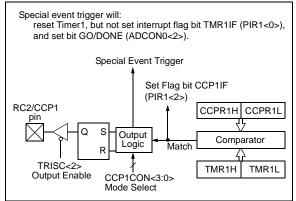

### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

# PIC16F87X

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

### TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|-------------------------------------|--------------|---------------|---------------|------------|----------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE         | INTE          | RBIE          | TOIF       | INTF     | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF         | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF | 0000 0000                | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | _                                   | _            | _             | —             | —          | _        | CCP2IF | 0                        | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE         | TXIE          | SSPIE         | CCP1IE     | TMR2IE   | TMR1IE | 0000 0000                | 0000 0000                       |

| 8Dh                    | PIE2    | —                    | CCP2IE                              |              |               |               |            |          |        |                          | 0                               |

| 87h                    | TRISC   | PORTC D              | ata Direct                          | tion Registe | er            |               |            |          |        | 1111 1111                | 1111 1111                       |

| 0Eh                    | TMR1L   | Holding R            | egister for                         | r the Least  | Significant E | Byte of the 1 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister for                         | r the Most S | Significant B | yte of the 16 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                   | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N | 00 0000                  | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | ompare/F                            | WM Regist    | ter1 (LSB)    |               |            |          |        | XXXX XXXX                | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | ompare/F                            | WM Regist    | ter1 (MSB)    |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |

| 17h                    | CCP1CON | —                    | _                                   | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2     | CCP1M1   | CCP1M0 | 00 0000                  | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |              |               |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | Capture/Compare/PWM Register2 (MSB) |              |               |               |            |          |        |                          | uuuu uuuu                       |

| 1Dh                    | CCP2CON | —                    | —                                   | CCP2X        | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0 | 00 0000                  | 00 0000                         |

$\label{eq:legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.$

Note 1: The PSP is not implemented on the PIC16F873/876; always maintain these bits clear.

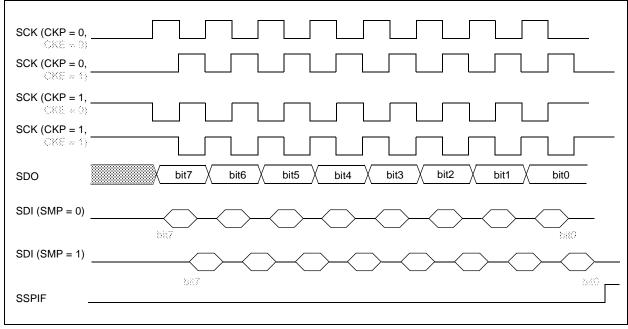

#### 9.1.1 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-5) is to broad-cast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI module is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor".

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then, would give waveforms for SPI communication as shown in Figure 9-6, Figure 9-8 and Figure 9-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5.0 MHz.

Figure 9-6 shows the waveforms for Master mode. When CKE = 1, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

#### FIGURE 9-2: SPI MODE TIMING, MASTER MODE

|    | its as Data<br>s Received | SSPSR $ ightarrow$ SSPBUF | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|----|---------------------------|---------------------------|-----------------------|----------------------------------------|--|--|

| BF | SSPOV                     |                           | ruise                 | if enabled)                            |  |  |

| 0  | 0                         | Yes                       | Yes                   | Yes                                    |  |  |

| 1  | 0                         | No                        | No                    | Yes                                    |  |  |

| 1  | 1                         | No                        | No                    | Yes                                    |  |  |

| 0  | 1                         | Yes                       | No                    | Yes                                    |  |  |

TABLE 9-2: DATA TRANSFER RECEIVED BYTE ACTIONS

Note: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

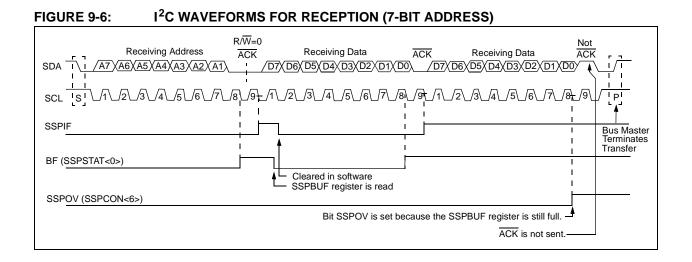

#### 9.2.1.3 Slave Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, the SCL pin should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 9-7). An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting the CKP bit.

## TABLE 10-3: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | F       | Fosc = 20 MHz |                                     |         | osc = 16 N       | IHz | Fosc = 10 MHz |            |                             |  |

|-------------|---------|---------------|-------------------------------------|---------|------------------|-----|---------------|------------|-----------------------------|--|

| RATE<br>(K) | RATE    |               | % SPBRG<br>ERROR value<br>(decimal) |         | %<br>KBAUD ERROR |     | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -       | -             | -                                   | -       | -                | -   | -             | -          | -                           |  |

| 1.2         | 1.221   | 1.75          | 255                                 | 1.202   | 0.17             | 207 | 1.202         | 0.17       | 129                         |  |

| 2.4         | 2.404   | 0.17          | 129                                 | 2.404   | 0.17             | 103 | 2.404         | 0.17       | 64                          |  |

| 9.6         | 9.766   | 1.73          | 31                                  | 9.615   | 0.16             | 25  | 9.766         | 1.73       | 15                          |  |

| 19.2        | 19.531  | 1.72          | 15                                  | 19.231  | 0.16             | 12  | 19.531        | 1.72       | 7                           |  |

| 28.8        | 31.250  | 8.51          | 9                                   | 27.778  | 3.55             | 8   | 31.250        | 8.51       | 4                           |  |

| 33.6        | 34.722  | 3.34          | 8                                   | 35.714  | 6.29             | 6   | 31.250        | 6.99       | 4                           |  |

| 57.6        | 62.500  | 8.51          | 4                                   | 62.500  | 8.51             | 3   | 52.083        | 9.58       | 2                           |  |

| HIGH        | 1.221   | -             | 255                                 | 0.977   | -                | 255 | 0.610         | -          | 255                         |  |

| LOW         | 312.500 | -             | 0                                   | 250.000 | -                | 0   | 156.250       | -          | 0                           |  |

| DAUD                | Fosc = 4 MHz |            |                             | Fosc = 3.6864 MHz |            |                             |  |

|---------------------|--------------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| BAUD<br>RATE<br>(K) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3                 | 0.300        | 0          | 207                         | 0.3               | 0          | 191                         |  |

| 1.2                 | 1.202        | 0.17       | 51                          | 1.2               | 0          | 47                          |  |

| 2.4                 | 2.404        | 0.17       | 25                          | 2.4               | 0          | 23                          |  |

| 9.6                 | 8.929        | 6.99       | 6                           | 9.6               | 0          | 5                           |  |

| 19.2                | 20.833       | 8.51       | 2                           | 19.2              | 0          | 2                           |  |

| 28.8                | 31.250       | 8.51       | 1                           | 28.8              | 0          | 1                           |  |

| 33.6                | -            | -          | -                           | -                 | -          | -                           |  |

| 57.6                | 62.500       | 8.51       | 0                           | 57.6              | 0          | 0                           |  |

| HIGH                | 0.244        | -          | 255                         | 0.225             | -          | 255                         |  |

| LOW                 | 62.500       | -          | 0                           | 57.6              | -          | 0                           |  |

## TABLE 10-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 20 MHz |            |                             | F        | osc = 16 M | Hz                          | Fosc = 10 MHz |            |                             |

|-------------|---------------|------------|-----------------------------|----------|------------|-----------------------------|---------------|------------|-----------------------------|

| RATE<br>(K) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD         | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3         | -             | -          | -                           | -        | -          | -                           | -             | -          | -                           |

| 1.2         | -             | -          | -                           | -        | -          | -                           | -             | -          | -                           |

| 2.4         | -             | -          | -                           | -        | -          | -                           | 2.441         | 1.71       | 255                         |

| 9.6         | 9.615         | 0.16       | 129                         | 9.615    | 0.16       | 103                         | 9.615         | 0.16       | 64                          |

| 19.2        | 19.231        | 0.16       | 64                          | 19.231   | 0.16       | 51                          | 19.531        | 1.72       | 31                          |

| 28.8        | 29.070        | 0.94       | 42                          | 29.412   | 2.13       | 33                          | 28.409        | 1.36       | 21                          |

| 33.6        | 33.784        | 0.55       | 36                          | 33.333   | 0.79       | 29                          | 32.895        | 2.10       | 18                          |

| 57.6        | 59.524        | 3.34       | 20                          | 58.824   | 2.13       | 16                          | 56.818        | 1.36       | 10                          |

| HIGH        | 4.883         | -          | 255                         | 3.906    | -          | 255                         | 2.441         | -          | 255                         |

| LOW         | 1250.000      | -          | 0                           | 1000.000 |            | 0                           | 625.000       | -          | 0                           |

| BAUD        | Fosc = 4 MHz |            |                             | Fosc = 3.6864 MHz |            |                             |  |

|-------------|--------------|------------|-----------------------------|-------------------|------------|-----------------------------|--|

| RATE<br>(K) | KBAUD        | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD             | %<br>ERROR | SPBRG<br>value<br>(decimal) |  |

| 0.3         | -            | -          | -                           | -                 | -          | -                           |  |

| 1.2         | 1.202        | 0.17       | 207                         | 1.2               | 0          | 191                         |  |

| 2.4         | 2.404        | 0.17       | 103                         | 2.4               | 0          | 95                          |  |

| 9.6         | 9.615        | 0.16       | 25                          | 9.6               | 0          | 23                          |  |

| 19.2        | 19.231       | 0.16       | 12                          | 19.2              | 0          | 11                          |  |

| 28.8        | 27.798       | 3.55       | 8                           | 28.8              | 0          | 7                           |  |

| 33.6        | 35.714       | 6.29       | 6                           | 32.9              | 2.04       | 6                           |  |

| 57.6        | 62.500       | 8.51       | 3                           | 57.6              | 0          | 3                           |  |

| HIGH        | 0.977        | -          | 255                         | 0.9               | -          | 255                         |  |

| LOW         | 250.000      | -          | 0                           | 230.4             | -          | 0                           |  |

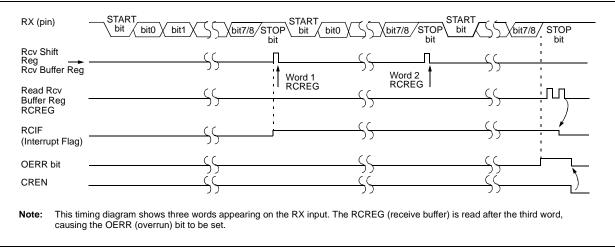

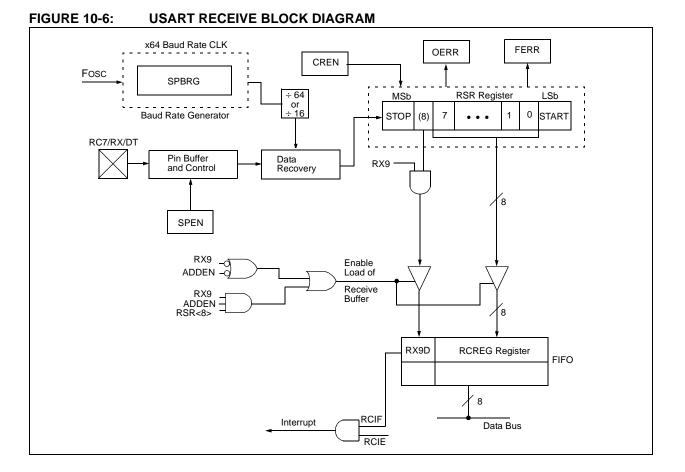

#### FIGURE 10-5: ASYNCHRONOUS RECEPTION

When setting up an Asynchronous Reception, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE is set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                                | Name   | Bit 7                  | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|----------------------------------------|--------|------------------------|-------|-------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh                 | INTCON | GIE                    | PEIE  | TOIE  | INTE  | RBIE      | TOIF      | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                                    | PIR1   | PSPIF <sup>(1)</sup>   | ADIF  | RCIF  | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                                    | RCSTA  | SPEN                   | RX9   | SREN  | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                                    | RCREG  | USART Receive Register |       |       |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                                    | PIE1   | PSPIE <sup>(1)</sup>   | ADIE  | RCIE  | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                                    | TXSTA  | CSRC                   | TX9   | TXEN  | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h SPBRG Baud Rate Generator Register |        |                        |       |       |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

#### TABLE 10-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

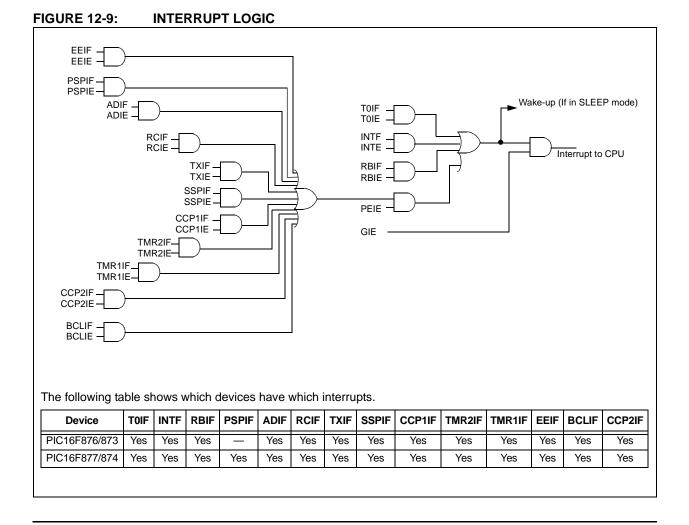

### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

© 1998-2013 Microchip Technology Inc.

# 15.0 ELECTRICAL CHARACTERISTICS

| Absolute Maximum Ratings † | Absolute | Maximum | Ratings † |

|----------------------------|----------|---------|-----------|

|----------------------------|----------|---------|-----------|

| Ambient temperature under bias                                                                              |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3 V to (VDD + 0.3 V)             |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5 V                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14 V                         |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +8.5 V                        |

| Total power dissipation (Note 1)                                                                            | 1.0 W                              |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into Vod pin                                                                                | 250 mA                             |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                                                                | ± 20 mA                            |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              | ± 20 mA                            |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| <b>2:</b> Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80   | mA <u>, may cause latch-up</u> .   |

- 2: Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin, rather than pulling this pin directly to VSS.

- 3: PORTD and PORTE are not implemented on PIC16F873/876 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

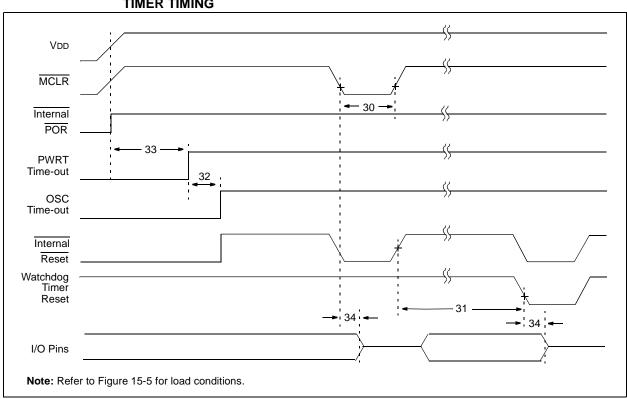

# FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

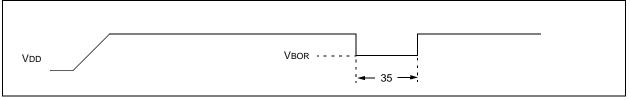

### FIGURE 15-9: BROWN-OUT RESET TIMING

# TABLE 15-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|------------------|--------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30               | TmcL   | MCLR Pulse Width (low)                                 | 2   | -         | _   | μs    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt   | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost   | Oscillation Start-up Timer Period                      | _   | 1024 Tosc |     | —     | Tosc = OSC1 period       |

| 33*              | Tpwrt  | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | —         | 2.1 | μS    |                          |

| 35               | TBOR   | Brown-out Reset pulse width                            | 100 | _         | _   | μs    | $VDD \le VBOR (D005)$    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

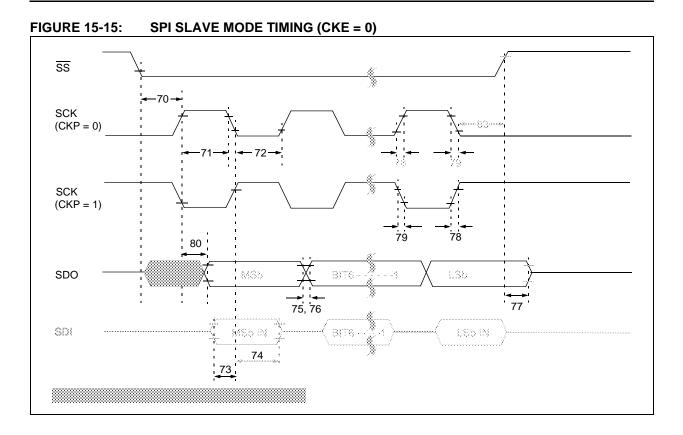

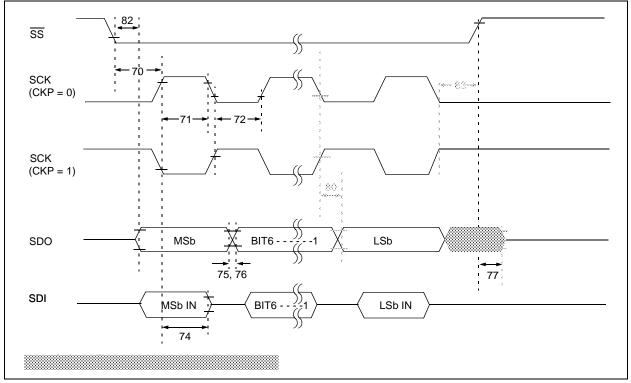

| Param<br>No. | Symbol                | Characteristic                                                        |                                               | Min         | Тур†     | Мах       | Units    | Conditions |

|--------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------------------|-------------|----------|-----------|----------|------------|

| 70*          | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсу                                           | —           | —        | ns        |          |            |

| 71*          | TscH                  | SCK input high time (Slave mode)                                      |                                               | TCY + 20    | —        | —         | ns       |            |

| 72*          | TscL                  | SCK input low time (Slave mode)                                       |                                               | Tcy + 20    | _        | _         | ns       |            |

| 73*          | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK                                   | 100                                           | _           | —        | ns        |          |            |

| 74*          | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK e                                  | 100                                           | _           | —        | ns        |          |            |

| 75*          | TdoR                  | SDO data output rise time                                             | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) |             | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 76*          | TdoF                  | SDO data output fall time                                             |                                               |             | 10       | 25        | ns       |            |

| 77*          | TssH2doZ              | SS↑ to SDO output hi-impedance                                        |                                               | 10          | _        | 50        | ns       |            |

| 78*          | TscR                  | SCK output rise time (Master mode)                                    | Standard(F)<br>Extended(LF)                   |             | 10<br>25 | 25<br>50  | ns<br>ns |            |

| 79*          | TscF                  | SCK output fall time (Master mode)                                    |                                               |             | 10       | 25        | ns       |            |

| 80*          | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | Standard( <b>F</b> )<br>Extended( <b>LF</b> ) | _           | _        | 50<br>145 | ns       |            |

| 81*          | TdoV2scH,<br>TdoV2scL | SDO data output setup to SCK edge                                     | Тсу                                           | _           | —        | ns        |          |            |

| 82*          | TssL2doV              | SDO data output valid after $\overline{SS}\downarrow$ edg             | е                                             | _           | _        | 50        | ns       |            |

| 83*          | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                                   |                                               | 1.5Tcy + 40 | _        | —         | ns       |            |

#### TABLE 15-7: SPI MODE REQUIREMENTS

\* These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

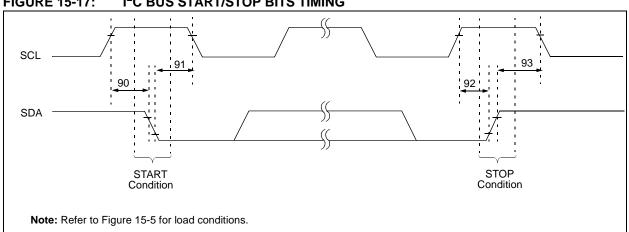

#### I<sup>2</sup>C BUS START/STOP BITS TIMING FIGURE 15-17:

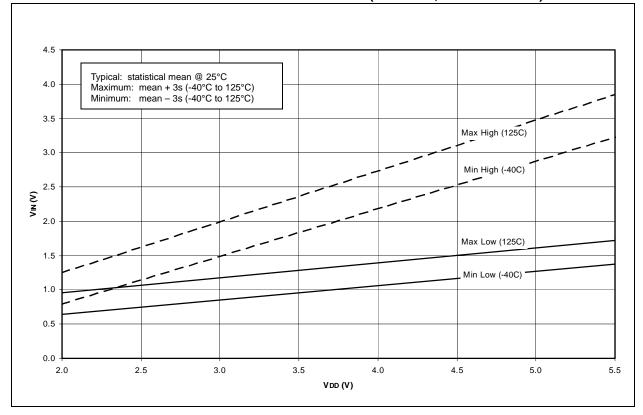

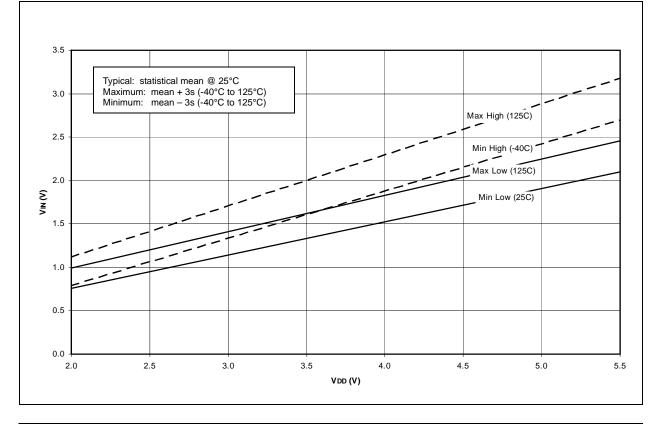

FIGURE 16-21: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO 125°C)

© 1998-2013 Microchip Technology Inc.

## INDEX

Α

| A/D1                                       | 11  |

|--------------------------------------------|-----|

| Acquisition Requirements1                  |     |

| ADCON0 Register                            |     |

| ADCON1 Register                            |     |

| ADIF bit                                   |     |

| Analog Input Model Block Diagram1          |     |

| Analog Port Pins                           |     |

| Associated Registers and Bits              |     |

| Block Diagram                              |     |

| Calculating Acquisition Time1              |     |

| Configuring Analog Port Pins1              |     |

| Configuring the Interrupt1                 |     |

| Configuring the Module1                    |     |

| Conversion Clock                           |     |

| Conversions1                               |     |

| Delays1                                    |     |

| Effects of a RESET1                        |     |

| GO/DONE bit                                |     |

| Internal Sampling Switch (Rss) Impedence   |     |

| Operation During SLEEP1                    |     |

| Result Registers1                          |     |

| Sampling Requirements1                     |     |

| Source Impedence1                          |     |

| Time Delays1                               |     |

| Absolute Maximum Ratings                   |     |

| ACK                                        |     |

| Acknowledge Data bit                       |     |

| Acknowledge Pulse                          |     |

| Acknowledge Sequence Enable bit            |     |

| Acknowledge Status bit                     |     |

| ADRES Register                             |     |

| Analog Port Pins. See A/D                  | • • |

| Analog-to-Digital Converter. See A/D       |     |

| Application Notes                          |     |

| AN552 (Implementing Wake-up on Key Strokes |     |

| Using PIC16CXXX)                           | 31  |

| AN556 (Implementing a Table Read)          |     |

| AN578 (Use of the SSP Module in the I2C    | 20  |

| Multi-Master Environment)                  | 73  |

| Architecture                               | 10  |

| PIC16F873/PIC16F876 Block Diagram          | 5   |

| PIC16F874/PIC16F877 Block Diagram          | 5   |

| Assembler                                  | 0   |

| MPASM Assembler1                           | 12  |

|                                            | 40  |

| В                                          |     |

| Banking, Data Memory 12,                   | 18  |

| Baud Rate Generator                        |     |

| BCLIF                                      |     |

| BF                                         |     |

| Block Diagrams                             | 57  |

| A/D1                                       | 13  |

| A/D Converter                              |     |

|                                            |     |

Analog Input Model

114

Baud Rate Generator

79

Capture Mode

59

Compare Mode

60

I<sup>2</sup>C Master Mode

78

I<sup>2</sup>C Module

73

I<sup>2</sup>C Slave Mode

73

Interrupt Logic

129

PIC16F873/PIC16F876

5

| PIC16F874/PIC16F877                             | 6        |

|-------------------------------------------------|----------|

| PORTA                                           |          |

| RA3:RA0 and RA5 Pins                            |          |

| RA4/T0CKI Pin                                   | 29       |

| PORTB                                           |          |

| RB3:RB0 Port Pins                               |          |

| RB7:RB4 Port Pins                               | 31       |

| PORTC                                           |          |

| Peripheral Output Override (RC 0:2, 5:7)        |          |

| Peripheral Output Override (RC 3:4)             |          |

| PORTD                                           |          |

| PORTD and PORTE (Parallel Slave Port)           |          |

| PORTE                                           | 36       |

| PWM Mode                                        | 61       |