Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874-20i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| FI | GU | IRF | 2-3      | - |

|----|----|-----|----------|---|

|    |    |     | <u> </u> |   |

### PIC16F877/876 REGISTER FILE MAP

| Indirect addr.(*)              | 00h        | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 18              |

|--------------------------------|------------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----------------|

| TMR0                           | 01h        | OPTION_REG                                 | 81h        | TMR0                                       | 101h         | OPTION_REG                                 | 18              |

| PCL                            | 02h        | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182             |

| STATUS                         | 03h        | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183             |

| FSR                            | 04h        | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184             |

| PORTA                          | 05h        | TRISA                                      | 85h        |                                            | 105h         |                                            | 18              |

| PORTB                          | 06h        | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186             |

| PORTC                          | 07h        | TRISC                                      | 87h        |                                            | 107h         |                                            | 187             |

| PORTD <sup>(1)</sup>           | 08h        | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188             |

| PORTE <sup>(1)</sup>           | 09h        | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h         |                                            | 189             |

| PCLATH                         | 0Ah        | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18/             |

| INTCON                         | 0Bh        | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18              |

| PIR1                           | 0Ch        | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch         | EECON1                                     | 180             |

| PIR2                           | 0Dh        | PIE2                                       | 8Dh        | EEADR                                      | 10Dh         | EECON2                                     | 181             |

| TMR1L                          | 0Eh        | PCON                                       | 8Eh        | EEDATH                                     | 10Eh         | Reserved <sup>(2)</sup>                    | 18              |

| TMR1H                          | 0Fh        |                                            | 8Fh        | EEADRH                                     | 10Fh         | Reserved <sup>(2)</sup>                    | 18              |

| T1CON                          | 10h        |                                            | 90h        |                                            | 110h         |                                            | 190             |

| TMR2                           | 11h        | SSPCON2                                    | 91h        |                                            | 111h         |                                            | 19 <sup>.</sup> |

| T2CON                          | 12h        | PR2                                        | 92h        |                                            | 112h         |                                            | 192             |

| SSPBUF                         | 13h        | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193             |

| SSPCON                         | 14h        | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194             |

| CCPR1L                         | 15h        |                                            | 95h        |                                            | 115h         |                                            | 19              |

| CCPR1H                         | 16h        |                                            | 96h        |                                            | 116h         |                                            | 196             |

| CCP1CON                        | 17h        |                                            | 97h        | General                                    | 117h         | General                                    | 197             |

| RCSTA                          | 18h        | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198             |

| TXREG                          | 19h        | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199             |

| RCREG                          | 1Ah        |                                            | 9Ah        | -                                          | 11Ah         |                                            | 19/             |

| CCPR2L                         | 1Bh        |                                            | 9Bh        |                                            | 11Bh         |                                            | 198             |

| CCPR2H                         | 1Ch        |                                            | 9Ch        |                                            | 11Ch         |                                            | 190             |

| CCP2CON                        | 1Dh        |                                            | 9Dh        |                                            | 11Dh         |                                            | 19[             |

| ADRESH                         | 1Eh        | ADRESL                                     | 9Eh        |                                            | 11Eh         |                                            | 19              |

| ADCON0                         | 1Fh        | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 191             |

|                                | 20h        |                                            | A0h        |                                            | 120h         |                                            | 1A              |

| General<br>Purpose<br>Register |            | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |                 |

| 96 Bytes                       |            | UU Dyico                                   | EFh        | 00 Dytos                                   | 16Fh         | 00 Dyi00                                   | 1EI             |

|                                | 7Fh        | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | 1F(<br>1Fl      |

| Bank 0                         |            | Bank 1                                     | FFII       | Bank 2                                     | /. !!        | Bank 3                                     | 11.1            |

| 1 1 m 1 m m 1                  | بارار منعم | a memory location                          | a          |                                            |              |                                            |                 |

2: These registers are reserved, maintain these registers clear.

#### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                              | File<br>Address             | A                                                                     | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>  | 00h                         | Indirect addr.(*)                                                     | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                           | 01h                         | OPTION_REG                                                            | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                            | 02h                         | PCL                                                                   | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                         | 03h                         | STATUS                                                                | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                            | 04h                         | FSR                                                                   | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                          | 05h                         | TRISA                                                                 | 85h            |                     | 105h            |                         | 185h           |

| PORTB                          | 06h                         | TRISB                                                                 | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                          | 07h                         | TRISC                                                                 | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>           | 08h                         | TRISD <sup>(1)</sup>                                                  | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>           | 09h                         | TRISE <sup>(1)</sup>                                                  | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                         | 0Ah                         | PCLATH                                                                | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                         | 0Bh                         | INTCON                                                                | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                           | 0Ch                         | PIE1                                                                  | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                           | 0Dh                         | PIE2                                                                  | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                          | 0Eh                         | PCON                                                                  | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                          | 0Fh                         |                                                                       | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                          | 10h                         |                                                                       | 90h            |                     | 110h            |                         | 190h           |

| TMR2                           | 11h                         | SSPCON2                                                               | 91h            |                     |                 |                         |                |

| T2CON                          | 12h                         | PR2                                                                   | 92h            |                     |                 |                         |                |

| SSPBUF                         | 13h                         | SSPADD                                                                | 93h            |                     |                 |                         |                |

| SSPCON                         | 14h                         | SSPSTAT                                                               | 94h            |                     |                 |                         |                |

| CCPR1L                         | 15h                         |                                                                       | 95h            |                     |                 |                         |                |

| CCPR1H                         | 16h                         |                                                                       | 96h            |                     |                 |                         |                |

| CCP1CON                        | 17h                         |                                                                       | 97h            |                     |                 |                         |                |

| RCSTA                          | 18h                         | TXSTA                                                                 | 98h            |                     |                 |                         |                |

| TXREG                          | 19h                         | SPBRG                                                                 | 99h            |                     |                 |                         |                |

| RCREG                          | 1Ah                         |                                                                       | 9Ah            |                     |                 |                         |                |

| CCPR2L                         | 1Bh                         |                                                                       | 9Bh            |                     |                 |                         |                |

| CCPR2H                         | 1Ch                         |                                                                       | 9Ch            |                     |                 |                         |                |

| CCP2CON                        | 1Dh                         |                                                                       | 9Dh            |                     |                 |                         |                |

| ADRESH                         | 1Eh                         | ADRESL                                                                | 9Eh            |                     |                 |                         |                |

| ADCON0                         | 1Fh                         | ADCON1                                                                | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                | 20h                         |                                                                       | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register |                             | General<br>Purpose<br>Register                                        |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                       |                             | 96 Bytes                                                              |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                | 754                         |                                                                       |                |                     | 1756            |                         | 4              |

| Bank 0                         | J 7Fh                       | Bank 1                                                                | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| * Not a<br>Note 1: These       | physical reg<br>e registers | data memory locat<br>gister.<br>are not implemen<br>are reserved, mai | ted on the     | e PIC16F873.        |                 |                         |                |

| Address              | Name       | Bit 7                | Bit 6                            | Bit 5                      | Bit 4          | Bit 3        | Bit 2             | Bit 1        | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|------------|----------------------|----------------------------------|----------------------------|----------------|--------------|-------------------|--------------|----------|--------------------------|------------------------|

| Bank 1               |            |                      |                                  |                            |                |              |                   |              |          |                          |                        |

| 80h <sup>(3)</sup>   | INDF       | Addressing           | g this location                  | n uses conte               | ents of FSR to | address dat  | a memory (no      | a physical r | egister) | 0000 0000                | 27                     |

| 81h                  | OPTION_REG | RBPU                 | INTEDG                           | TOCS                       | T0SE           | PSA          | PS2               | PS1          | PS0      | 1111 1111                | 19                     |

| 82h <sup>(3)</sup>   | PCL        | Program C            | Counter (PC)                     | Least Signif               | icant Byte     |              |                   |              |          | 0000 0000                | 26                     |

| 83h <sup>(3)</sup>   | STATUS     | IRP                  | RP1                              | RP0                        | TO             | PD           | Z                 | DC           | С        | 0001 1xxx                | 18                     |

| 84h <sup>(3)</sup>   | FSR        | Indirect Da          | rect Data Memory Address Pointer |                            |                |              |                   |              |          |                          | 27                     |

| 85h                  | TRISA      | _                    |                                  | PORTA Da                   | ta Direction R | egister      |                   |              |          | 11 1111                  | 29                     |

| 86h                  | TRISB      | PORTB Da             | ata Direction                    | Register                   |                |              |                   |              |          | 1111 1111                | 31                     |

| 87h                  | TRISC      | PORTC D              | ata Direction                    | Register                   |                |              |                   |              |          | 1111 1111                | 33                     |

| 88h <sup>(4)</sup>   | TRISD      | PORTD D              | ata Direction                    | Register                   |                |              |                   |              |          | 1111 1111                | 35                     |

| 89h <sup>(4)</sup>   | TRISE      | IBF                  | OBF                              | IBOV                       | PSPMODE        |              | PORTE Data        | Direction Bi | its      | 0000 -111                | 37                     |

| 8Ah <sup>(1,3)</sup> | PCLATH     | _                    | _                                | _                          | Write Buffer   | for the uppe | r 5 bits of the F | Program Cou  | unter    | 0 0000                   | 26                     |

| 8Bh <sup>(3)</sup>   | INTCON     | GIE                  | PEIE                             | TOIE                       | INTE           | RBIE         | T0IF              | INTF         | RBIF     | 0000 000x                | 20                     |

| 8Ch                  | PIE1       | PSPIE <sup>(2)</sup> | ADIE                             | RCIE                       | TXIE           | SSPIE        | CCP1IE            | TMR2IE       | TMR1IE   | 0000 0000                | 21                     |

| 8Dh                  | PIE2       | _                    | (5)                              |                            | EEIE           | BCLIE        | _                 |              | CCP2IE   | -r-0 00                  | 23                     |

| 8Eh                  | PCON       | _                    | — — — — — — POR BOR              |                            |                |              |                   |              |          |                          | 25                     |

| 8Fh                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | —                      |

| 90h                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 91h                  | SSPCON2    | GCEN                 | ACKSTAT                          | ACKDT                      | ACKEN          | RCEN         | PEN               | RSEN         | SEN      | 0000 0000                | 68                     |

| 92h                  | PR2        | Timer2 Pe            | riod Register                    | r                          |                |              |                   |              |          | 1111 1111                | 55                     |

| 93h                  | SSPADD     | Synchrono            | ous Serial Po                    | ort (I <sup>2</sup> C mode | ) Address Re   | gister       |                   |              |          | 0000 0000                | 73, 74                 |

| 94h                  | SSPSTAT    | SMP                  | CKE                              | D/A                        | Р              | S            | R/W               | UA           | BF       | 0000 0000                | 66                     |

| 95h                  | _          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 96h                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 97h                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 98h                  | TXSTA      | CSRC                 | TX9                              | TXEN                       | SYNC           | _            | BRGH              | TRMT         | TX9D     | 0000 -010                | 95                     |

| 99h                  | SPBRG      | Baud Rate            | e Generator F                    | Register                   |                |              |                   |              |          | 0000 0000                | 97                     |

| 9Ah                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 9Bh                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 9Ch                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 9Dh                  | —          | Unimplem             | ented                            |                            |                |              |                   |              |          | _                        | _                      |

| 9Eh                  | ADRESL     | A/D Result           | t Register Lo                    | w Byte                     |                |              |                   |              |          | xxxx xxxx                | 116                    |

| 9Fh                  | ADCON1     | ADFM                 | _                                | _                          | —              | PCFG3        | PCFG2             | PCFG1        | PCFG0    | 0 0000                   | 112                    |

#### **TABLE 2-1:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

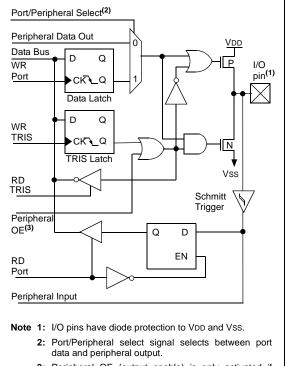

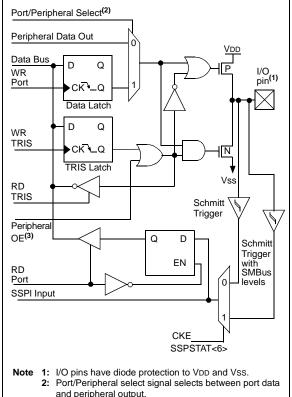

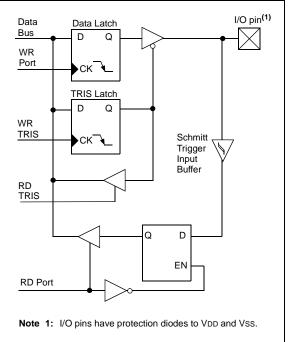

#### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

### FIGURE 3-6:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

#### 3.5 PORTE and TRISE Register

PORTE and TRISE are not implemented on the PIC16F873 or PIC16F876.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6, and RE2/CS/AN7) which are individually configureable as inputs or outputs. These pins have Schmitt Trigger input buffers.

The PORTE pins become the I/O control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make certain that the TRISE<2:0> bits are set, and that the pins are configured as digital inputs. Also ensure that ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

Register 3-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected for analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a Power-on Reset, these pins are configured as analog inputs, and read as '0'.

#### FIGURE 3-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                                                              |

|------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | $\frac{I/O}{RD}$ port pin or read control input in Parallel Slave Port mode or analog input:<br>1 = Idle                                                                                                                              |

| REU/RD/ANS | bito | 51/112 /              | <ul> <li>a line</li> <li>a Read operation. Contents of PORTD register are output to PORTD</li> <li>I/O pins (if chip selected)</li> </ul>                                                                                             |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | <ul> <li>I/O port pin or write control input in Parallel Slave Port mode or analog input:<br/>WR</li> <li>1 = Idle</li> <li>0 = Write operation. Value of PORTD I/O pins is latched into PORTD register (if chip selected)</li> </ul> |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | I/O port pin or chip select control input in Parallel Slave Port mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                                                                  |

TABLE 3-9:PORTE FUNCTIONS

Legend: ST = Schmitt Trigger input, TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

#### TABLE 3-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1                     | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|-------|-------|-------|---------|-------|---------|---------------------------|-------|-----------------------|---------------------------------|

| 09h     | PORTE  | —     | —     | _     | —       | _     | RE2     | RE1                       | RE0   | xxx                   | uuu                             |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | PORTE [ | PORTE Data Direction Bits |       | 0000 -111             | 0000 -111                       |

| 9Fh     | ADCON1 | ADFM  | —     |       | _       | PCFG3 | PCFG2   | PCFG1                     | PCFG0 | 0- 0000               | 0- 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

NOTES:

## 4.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are readable and writable during normal operation over the entire VDD range. These operations take place on a single byte for Data EEPROM memory and a single word for Program memory. A write operation causes an erase-then-write operation to take place on the specified byte or word. A bulk erase operation may not be issued from user code (which includes removing code protection).

Access to program memory allows for checksum calculation. The values written to program memory do not need to be valid instructions. Therefore, up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that form an invalid instruction, results in the execution of a NOP instruction.

The EEPROM Data memory is rated for high erase/ write cycles (specification D120). The FLASH program memory is rated much lower (specification D130), because EEPROM data memory can be used to store frequently updated values. An on-chip timer controls the write time and it will vary with voltage and temperature, as well as from chip to chip. Please refer to the specifications for exact limits (specifications D122 and D133).

A byte or word write automatically erases the location and writes the new value (erase before write). Writing to EEPROM data memory does not impact the operation of the device. Writing to program memory will cease the execution of instructions until the write is complete. The program memory cannot be accessed during the write. During the write operation, the oscillator continues to run, the peripherals continue to function and interrupt events will be detected and essentially "queued" until the write is complete. When the write completes, the next instruction in the pipeline is executed and the branch to the interrupt vector will take place, if the interrupt is enabled and occurred during the write.

Read and write access to both memories take place indirectly through a set of Special Function Registers (SFR). The six SFRs used are:

- EEDATA

- EEDATH

- EEADR

- EEADRH

- EECON1

- EECON2

The EEPROM data memory allows byte read and write operations without interfering with the normal operation of the microcontroller. When interfacing to EEPROM data memory, the EEADR register holds the address to be accessed. Depending on the operation, the EEDATA register holds the data to be written, or the data read, at the address in EEADR. The PIC16F873/874 devices have 128 bytes of EEPROM data memory and therefore, require that the MSb of EEADR remain clear. The EEPROM data memory on these devices do not wrap around to 0, i.e., 0x80 in the EEADR does not map to 0x00. The PIC16F876/877 devices have 256 bytes of EEPROM data memory and therefore, uses all 8-bits of the EEADR.

The FLASH program memory allows non-intrusive read access, but write operations cause the device to stop executing instructions, until the write completes. When interfacing to the program memory, the EEADRH:EEADR registers form a two-byte word, which holds the 13-bit address of the memory location being accessed. The register combination of EEDATH:EEDATA holds the 14-bit data for writes, or reflects the value of program memory after a read operation. Just as in EEPROM data memory accesses, the value of the EEADRH:EEADR registers must be within the valid range of program memory, depending on the device: 0000h to 1FFFh for the PIC16F873/874. or 0000h to 3FFFh for the PIC16F876/877. Addresses outside of this range do not wrap around to 0000h (i.e., 4000h does not map to 0000h on the PIC16F877).

## 4.1 EECON1 and EECON2 Registers

The EECON1 register is the control register for configuring and initiating the access. The EECON2 register is not a physically implemented register, but is used exclusively in the memory write sequence to prevent inadvertent writes.

There are many bits used to control the read and write operations to EEPROM data and FLASH program memory. The EEPGD bit determines if the access will be a program or data memory access. When clear, any subsequent operations will work on the EEPROM data memory. When set, all subsequent operations will operate in the program memory.

Read operations only use one additional bit, RD, which initiates the read operation from the desired memory location. Once this bit is set, the value of the desired memory location will be available in the data registers. This bit cannot be cleared by firmware. It is automatically cleared at the end of the read operation. For EEPROM data memory reads, the data will be available in the EEDATA register in the very next instruction cycle after the RD bit is set. For program memory reads, the data will be loaded into the EEDATH:EEDATA registers, following the second instruction after the RD bit is set.

#### 4.4 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program the memory and insert value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

#### EXAMPLE 4-3: FLASH PROGRAM READ

| BSF   | STATUS, RP1   | ;                        |  |  |  |  |  |  |

|-------|---------------|--------------------------|--|--|--|--|--|--|

| BCF   | STATUS, RPO   | ;Bank 2                  |  |  |  |  |  |  |

| MOVF  | ADDRL, W      | ;Write the               |  |  |  |  |  |  |

| MOVWF | EEADR         | ;address bytes           |  |  |  |  |  |  |

| MOVF  | ADDRH,W       | ;for the desired         |  |  |  |  |  |  |

| MOVWF | EEADRH        | ;address to read         |  |  |  |  |  |  |

| BSF   | STATUS, RPO   | ;Bank 3                  |  |  |  |  |  |  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |  |  |  |  |  |  |

| BSF   | EECON1, RD    | ;Start read operation    |  |  |  |  |  |  |

| NOP   |               | ;Required two NOPs       |  |  |  |  |  |  |

| NOP   |               | ;                        |  |  |  |  |  |  |

| BCF   | STATUS, RPO   | ;Bank 2                  |  |  |  |  |  |  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |  |  |  |  |  |  |

| MOVWF | DATAL         | ;                        |  |  |  |  |  |  |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |  |  |  |  |  |  |

| MOVWF | DATAH         | ;                        |  |  |  |  |  |  |

|       |               |                          |  |  |  |  |  |  |

## 4.5 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory, is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 4-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

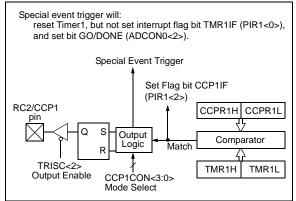

#### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven high

- Driven low

- Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

# PIC16F87X

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6                                                                       | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------|----------------------|-----------------------------------------------------------------------------|--------------|---------------|---------------|------------|----------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                                                        | TOIE         | INTE          | RBIE          | TOIF       | INTF     | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                                        | RCIF         | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF    | 0000 0000                | 0000 0000                       |

| 0Dh                    | PIR2    | —                    | _                                                                           | _            | _             | —             | —          | _        | CCP2IF    | 0                        | 0                               |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | PSPIE <sup>(1)</sup> ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE              |              |               |               |            |          | 0000 0000 | 0000 0000                |                                 |

| 8Dh                    | PIE2    | —                    | _                                                                           | CCP2IE       | 0             | 0             |            |          |           |                          |                                 |

| 87h                    | TRISC   | PORTC D              | ata Direct                                                                  |              | 1111 1111     | 1111 1111     |            |          |           |                          |                                 |

| 0Eh                    | TMR1L   | Holding R            | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |              |               |               |            |          |           |                          | uuuu uuuu                       |

| 0Fh                    | TMR1H   | Holding R            | egister for                                                                 | r the Most S | Significant B | yte of the 16 | 6-bit TMR1 | Register |           | xxxx xxxx                | uuuu uuuu                       |

| 10h                    | T1CON   | —                    | —                                                                           | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N    | 00 0000                  | uu uuuu                         |

| 15h                    | CCPR1L  | Capture/C            | ompare/F                                                                    | WM Regist    | ter1 (LSB)    |               |            |          |           | XXXX XXXX                | uuuu uuuu                       |

| 16h                    | CCPR1H  | Capture/C            | ompare/F                                                                    | WM Regist    | ter1 (MSB)    |               |            |          |           | xxxx xxxx                | uuuu uuuu                       |

| 17h                    | CCP1CON | —                    | —                                                                           | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2     | CCP1M1   | CCP1M0    | 00 0000                  | 00 0000                         |

| 1Bh                    | CCPR2L  | Capture/C            | ompare/F                                                                    | WM Regist    | ter2 (LSB)    | -             |            |          | -         | xxxx xxxx                | uuuu uuuu                       |

| 1Ch                    | CCPR2H  | Capture/C            | ompare/F                                                                    | WM Regist    | ter2 (MSB)    |               |            |          |           | xxxx xxxx                | uuuu uuuu                       |

| 1Dh                    | CCP2CON | —                    | —                                                                           | CCP2X        | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0    | 00 0000                  | 00 0000                         |

$\label{eq:legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.$

Note 1: The PSP is not implemented on the PIC16F873/876; always maintain these bits clear.

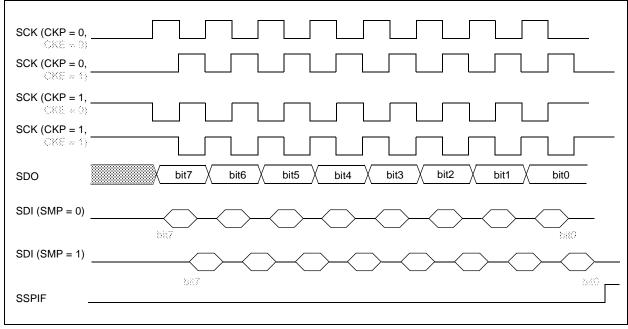

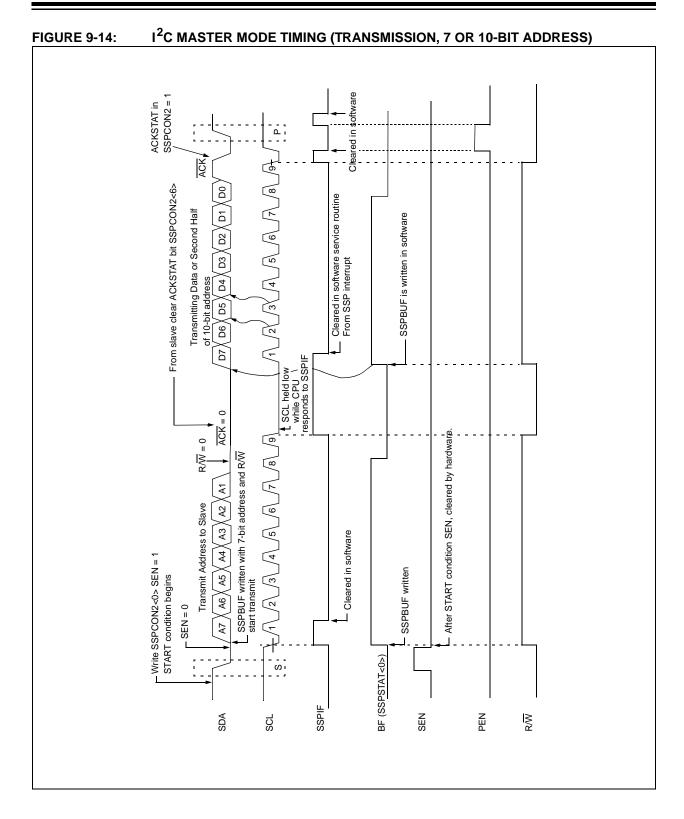

#### 9.1.1 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2, Figure 9-5) is to broad-cast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI module is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor".

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then, would give waveforms for SPI communication as shown in Figure 9-6, Figure 9-8 and Figure 9-9, where the MSb is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5.0 MHz.

Figure 9-6 shows the waveforms for Master mode. When CKE = 1, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

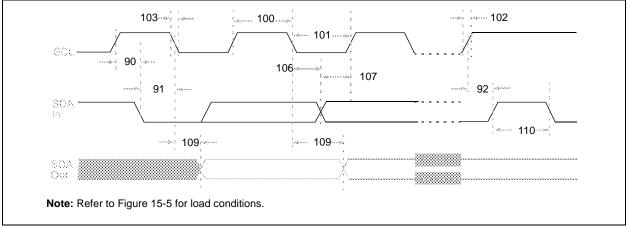

#### FIGURE 9-2: SPI MODE TIMING, MASTER MODE

#### 9.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

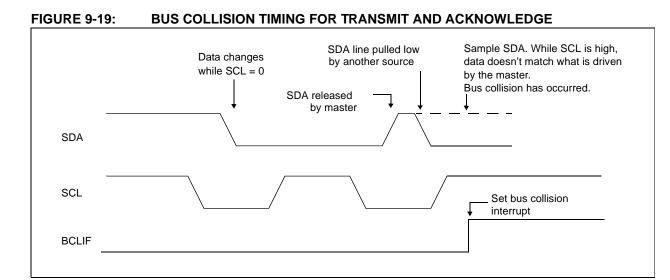

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$ port to its IDLE state (Figure 9-19).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine, and if the  $I^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated START, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

The master will continue to monitor the SDA and SCL pins and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of START and STOP conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

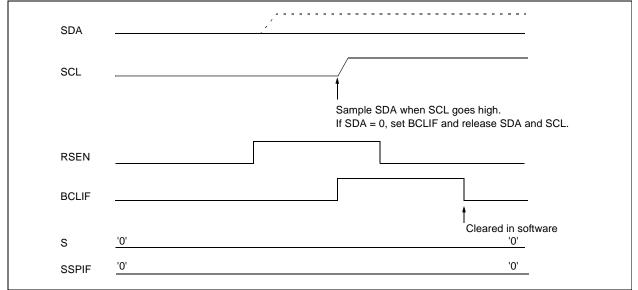

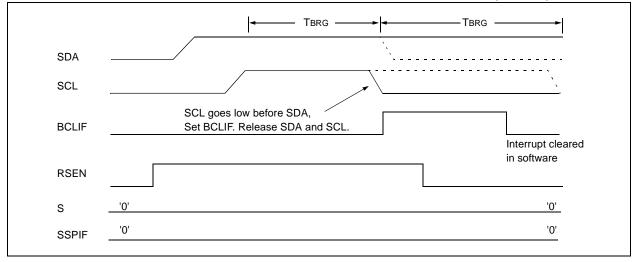

## 9.2.18.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data'0'). If, however, SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data'1' during the Repeated START condition.

If at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete (Figure 9-23).

#### FIGURE 9-23: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 9-24: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

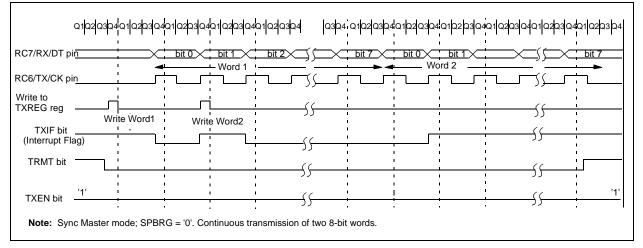

#### 10.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In Asynchronous mode, bit BRGH (TXSTA<2>) also controls the baud rate. In Synchronous mode, bit BRGH is ignored. Table 10-1 shows the formula for computation of the baud rate for different USART modes which only apply in Master mode (internal clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the formula in Table 10-1. From this, the error in baud rate can be determined.

It may be advantageous to use the high baud rate (BRGH = 1), even for slower baud clocks. This is because the FOSC/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 10.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 10-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)      |

|------|-------------------------------------------|----------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate = Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | N/A                        |

X = value in SPBRG (0 to 255)

#### TABLE 10-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7    | Bit 6     | Bit 5 | Bit 4     | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|---------|-------|----------|-----------|-------|-----------|-----------|-------|-------|-------|--------------------------|---------------------------------|

| 98h     | TXSTA | CSRC     | TX9       | TXEN  | SYNC      |           | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                       |

| 18h     | RCSTA | SPEN     | RX9       | SREN  | CREN      | ADDEN     | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                       |

| 99h     | SPBRG | Baud Rat | te Genera |       | 0000 0000 | 0000 0000 |       |       |       |                          |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used by the BRG.

#### TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                        | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|------------------------------|-------------------------|-------|-------|-------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                          | PEIE                    | TOIE  | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>         | ADIF                    | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                         | RX9                     | SREN  | CREN  | _     | FERR   | OERR   | RX9D      | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr                     | USART Transmit Register |       |       |       |        |        |           | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>         | ADIE                    | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                         | TX9                     | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate Generator Register |                         |       |       |       |        |        | 0000 0000 | 0000 0000                |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

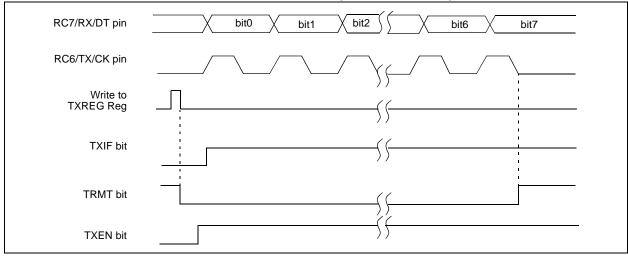

#### FIGURE 10-9: SYNCHRONOUS TRANSMISSION

#### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

|                            | Q1 Q2 Q3 Q4                                                          | Q1 Q2 Q3 Q4       | Q1          |             | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      |

|----------------------------|----------------------------------------------------------------------|-------------------|-------------|-------------|--------------|-------------------|-------------------|------------------|

| OSC1                       | ·/~~~~/                                                              |                   |             | -           |              | <u>;</u> ~~~~~~   |                   |                  |

| CLKOUT <sup>(4)</sup>      | \/\                                                                  |                   | <u> </u>    | Tost(2)     | /            | \                 | ¦/ \              |                  |

| INT pin                    | · · ·                                                                | 1                 |             | · ·         |              | 1<br>1            | 1 I<br>1 I        |                  |

| INTF Flag<br>(INTCON<1>)   |                                                                      | י<br>י<br>י<br>י  | 4           | /           |              | Interrupt Latency | (2)               | <br>  <br> <br>  |

| GIE bit<br>(INTCON<7>)     | 1 I<br>1 I<br>1 I<br>1 I<br>1 I                                      | i<br>             | Processor i | n           |              | ·                 | 1 1<br>1 1<br>1 1 | ו<br>ו<br>ו<br>ו |

| INSTRUCTIO                 | N FLOW                                                               |                   |             | · ·         |              | 1                 | 1 1<br>1 1        | 1                |

| PC                         | Х РС Х                                                               | PC+1              | ХР          | C+2         | PC+2         | X PC + 2          | <u>X 0004h X</u>  | 0005h            |

| Instruction {<br>Fetched { | Inst(PC) = SLEEP                                                     | Inst(PC + 1)      |             | 1           | Inst(PC + 2) | 1<br>1<br>1       | Inst(0004h)       | Inst(0005h)      |

| Instruction                | Inst(PC - 1)                                                         | SLEEP             |             | ,<br>,<br>, | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h)      |

| 2: Tost                    | HS or LP oscillator n<br>τ = 1024Tosc (drawi<br>= '1' assumed. In th | ing not to scale) |             |             |              |                   |                   |                  |

### F

If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

## 12.14 In-Circuit Debugger

When the DEBUG bit in the configuration word is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB® ICD. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-8 shows which features are consumed by the background debugger.

| TABLE 12-8: DE | BUGGER RESOURCES |

|----------------|------------------|

|----------------|------------------|

| I/O pins       | RB6, RB7                                     |

|----------------|----------------------------------------------|

| Stack          | 1 level                                      |

| Program Memory | Address 0000h must be NOP                    |

|                | Last 100h words                              |

| Data Memory    | 0x070 (0x0F0, 0x170, 0x1F0)<br>0x1EB - 0x1EF |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies.

## 12.15 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

## 12.16 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify. It is recommended that only the 4 Least Significant bits of the ID location are used.

15.3

#### DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended) (Continued)

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Extended) |                                  |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |     |       |                                                    |  |  |

|--------------------------------------------------------------------|----------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|-----|-------|----------------------------------------------------|--|--|

| Param<br>No.                                                       | Symbol Characteristic/<br>Device |                                           |                                                                                                                      | Тур† | Max | Units | Conditions                                         |  |  |

|                                                                    | IDD                              | Supply Current <sup>(2,5)</sup>           |                                                                                                                      |      |     |       |                                                    |  |  |

| D010                                                               |                                  |                                           | —                                                                                                                    | 1.6  | 4   | mA    | RC osc configurations<br>Fosc = 4 MHz, VDD = 5.5V  |  |  |

| D013                                                               |                                  |                                           | -                                                                                                                    | 7    | 15  | mA    | HS osc configuration,<br>Fosc = 10 MHz, VDD = 5.5V |  |  |

| D015                                                               | ΔIBOR                            | Brown-out<br>Reset Current <sup>(6)</sup> | —                                                                                                                    | 85   | 200 | μΑ    | BOR enabled, VDD = 5.0V                            |  |  |

|                                                                    | IPD                              | Power-down Current <sup>(3,5)</sup>       |                                                                                                                      |      |     |       |                                                    |  |  |

| D020A                                                              |                                  |                                           |                                                                                                                      | 10.5 | 60  | μΑ    | VDD = 4.0V, WDT enabled                            |  |  |

| D021B                                                              |                                  |                                           |                                                                                                                      | 1.5  | 30  | μA    | VDD = 4.0V, WDT disabled                           |  |  |

| D023                                                               | ΔIBOR                            | Brown-out<br>Reset Current <sup>(6)</sup> | —                                                                                                                    | 85   | 200 | μΑ    | BOR enabled, VDD = 5.0V                            |  |  |

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

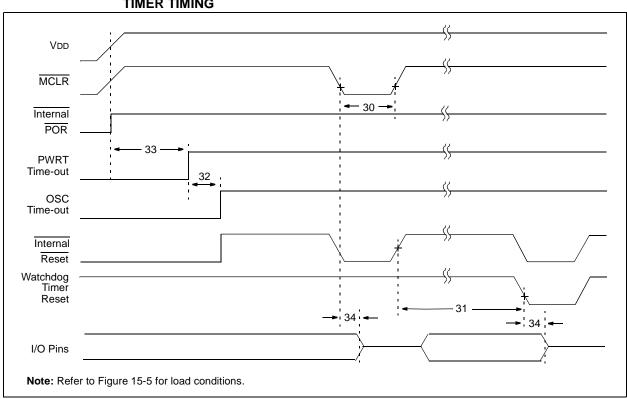

## FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

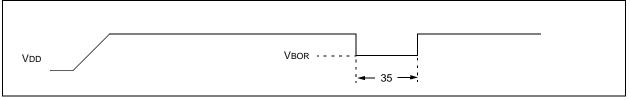

#### FIGURE 15-9: BROWN-OUT RESET TIMING

## TABLE 15-3:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Symbol | Characteristic                                         | Min | Тур†      | Max | Units | Conditions               |

|------------------|--------|--------------------------------------------------------|-----|-----------|-----|-------|--------------------------|

| 30               | TmcL   | MCLR Pulse Width (low)                                 | 2   | -         |     | μs    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt   | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost   | Oscillation Start-up Timer Period                      | _   | 1024 Tosc | _   | —     | Tosc = OSC1 period       |

| 33*              | Tpwrt  | Power-up Timer Period                                  | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz   | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | —         | 2.1 | μS    |                          |

| 35               | TBOR   | Brown-out Reset pulse width                            | 100 | _         |     | μs    | $VDD \le VBOR (D005)$    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Parameter<br>No. | Symbol  | Characteristic  |              |      | Тур | Max | Units | Conditions                         |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|------------------------------------|

| 90               | Tsu:sta | START condition | 100 kHz mode | 4700 | —   | _   | ns    | Only relevant for Repeated         |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | START condition                    |

| 91               | Thd:sta | START condition | 100 kHz mode | 4000 | _   | _   | ns    | After this period, the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       | pulse is generated                 |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                    |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | _   |       |                                    |

| 93               | Thd:sto | STOP condition  | 100 kHz mode | 4000 | -   | _   | ns    |                                    |

|                  |         | Hold time       | 400 kHz mode | 600  | _   | _   |       |                                    |

| TABLE 15-8: | I <sup>2</sup> C BUS START/STOP BITS REQUIREMENTS |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

## FIGURE 15-18: I<sup>2</sup>C BUS DATA TIMING