Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874t-20-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

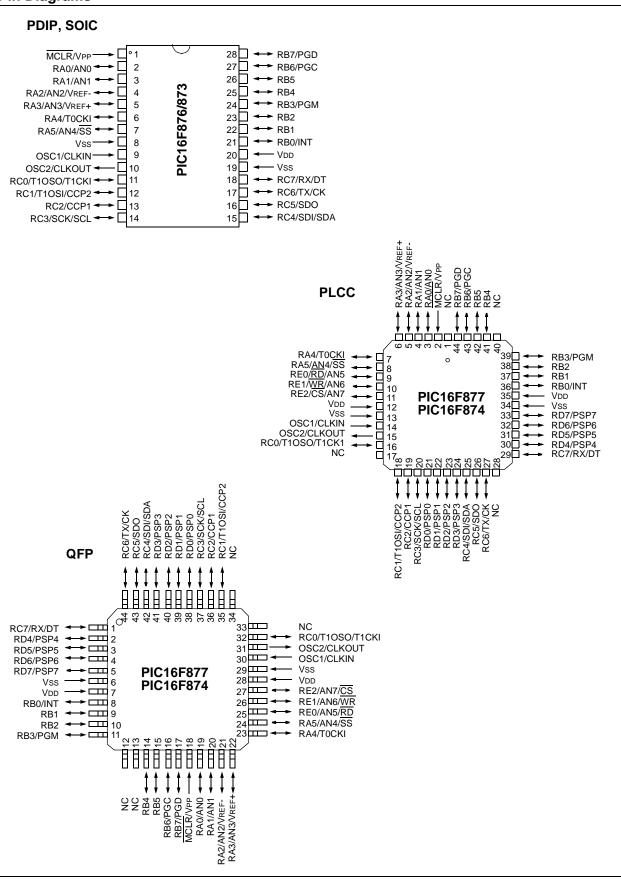

#### **Pin Diagrams**

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin#     | l/O/P<br>Type        | Buffer<br>Type         | Description                                                                                            |

|-------------------|----------------|-------------------|-----------------|----------------------|------------------------|--------------------------------------------------------------------------------------------------------|

|                   |                |                   |                 |                      |                        | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15             | 16                | 32              | I/O                  | ST                     | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16             | 18                | 35              | I/O                  | ST                     | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17             | 19                | 36              | I/O                  | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                        |

| RC3/SCK/SCL       | 18             | 20                | 37              | I/O                  | ST                     | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23             | 25                | 42              | I/O                  | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                        |

| RC5/SDO           | 24             | 26                | 43              | I/O                  | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25             | 27                | 44              | I/O                  | ST                     | RC6 can also be the USART Asynchronous Transmi<br>or Synchronous Clock.                                |

| RC7/RX/DT         | 26             | 29                | 1               | I/O                  | ST                     | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                   |                |                   |                 |                      |                        | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19             | 21                | 38              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD1/PSP1          | 20             | 22                | 39              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD2/PSP2          | 21             | 23                | 40              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD3/PSP3          | 22             | 24                | 41              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD4/PSP4          | 27             | 30                | 2               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD5/PSP5          | 28             | 31                | 3               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD6/PSP6          | 29             | 32                | 4               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD7/PSP7          | 30             | 33                | 5               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

|                   |                |                   |                 |                      |                        | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8              | 9                 | 25              | I/O                  | ST/TTL <sup>(3)</sup>  | RE0 can also be read control for the parallel slave port, or analog input5.                            |

| RE1/WR/AN6        | 9              | 10                | 26              | I/O                  | ST/TTL <sup>(3)</sup>  | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10             | 11                | 27              | I/O                  | ST/TTL <sup>(3)</sup>  | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31          | 13,34             | 6,29            | Р                    | _                      | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32          | 12,35             | 7,28            | Р                    | _                      | Positive supply for logic and I/O pins.                                                                |

| NC                | -              | 1,17,28,<br>40    | 12,13,<br>33,34 |                      | —                      | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |                 | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                |

#### TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | File<br>Address | A                              | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00h             | Indirect addr.(*)              | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01h             | OPTION_REG                     | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 02h             | PCL                            | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 03h             | STATUS                         | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 04h             | FSR                            | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 05h             | TRISA                          | 85h            |                     | 105h            |                         | 185h           |

| PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 06h             | TRISB                          | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 07h             | TRISC                          | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 08h             | TRISD <sup>(1)</sup>           | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 09h             | TRISE <sup>(1)</sup>           | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0Ah             | PCLATH                         | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0Bh             | INTCON                         | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0Ch             | PIE1                           | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0Dh             | PIE2                           | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0Eh             | PCON                           | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0Fh             |                                | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10h             |                                | 90h            |                     | 110h            |                         | 190h           |

| TMR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11h             | SSPCON2                        | 91h            |                     |                 |                         |                |

| T2CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12h             | PR2                            | 92h            |                     |                 |                         |                |

| SSPBUF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13h             | SSPADD                         | 93h            |                     |                 |                         |                |

| SSPCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14h             | SSPSTAT                        | 94h            |                     |                 |                         |                |

| CCPR1L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15h             |                                | 95h            |                     |                 |                         |                |

| CCPR1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16h             |                                | 96h            |                     |                 |                         |                |

| CCP1CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17h             |                                | 97h            |                     |                 |                         |                |

| RCSTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18h             | TXSTA                          | 98h            |                     |                 |                         |                |

| TXREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19h             | SPBRG                          | 99h            |                     |                 |                         |                |

| RCREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1Ah             |                                | 9Ah            |                     |                 |                         |                |

| CCPR2L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Bh             |                                | 9Bh            |                     |                 |                         |                |

| CCPR2H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Ch             |                                | 9Ch            |                     |                 |                         |                |

| CCP2CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1Dh             |                                | 9Dh            |                     |                 |                         |                |

| ADRESH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Eh             | ADRESL                         | 9Eh            |                     |                 |                         |                |

| ADCON0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1Fh             | ADCON1                         | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20h             |                                | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | General<br>Purpose<br>Register |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | 96 Bytes                       |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 754             |                                |                |                     | 1756            |                         | 4              |

| Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | J 7Fh           | Bank 1                         | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| Bank 0 Bank 1 Bank 2 Bank 3 Int 1 Bank 2 Bank 3 Int 2 Bank 3 Int 3 Bank 4 Bank 2 Bank 3 Bank 3 Bank 4 Bank 3 Bank 3 Bank 4 Bank 3 Bank 4 Bank 3 Bank 5 </td |                 |                                |                |                     |                 |                         |                |

#### TABLE 3-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or Synchronous Clock.                          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                                              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|-------|-------|----------------------------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                                                | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register       1111 1111 1111 |       |       |       |       |       |       |                          |                                 |

Legend: x = unknown, u = unchanged

#### 4.2 Reading the EEPROM Data Memory

Reading EEPROM data memory only requires that the desired address to access be written to the EEADR register and clear the EEPGD bit. After the RD bit is set, data will be available in the EEDATA register on the very next instruction cycle. EEDATA will hold this value until another read operation is initiated or until it is written by firmware.

The steps to reading the EEPROM data memory are:

- 1. Write the address to EEDATA. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Clear the EEPGD bit to point to EEPROM data memory.

- 3. Set the RD bit to start the read operation.

- 4. Read the data from the EEDATA register.

|       | LE 4-1. |       |                       |

|-------|---------|-------|-----------------------|

| BSF   | STATUS, | RP1   | ;                     |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | ADDR, W |       | ;Write address        |

| MOVWF | EEADR   |       | ;to read from         |

| BSF   | STATUS, | RP0   | ;Bank 3               |

| BCF   | EECON1, | EEPGD | ;Point to Data memory |

| BSF   | EECON1, | RD    | ;Start read operation |

| BCF   | STATUS, | RP0   | ;Bank 2               |

| MOVF  | EEDATA, | W     | ;W = EEDATA           |

EXAMPLE 4-1: EEPROM DATA READ

#### 4.3 Writing to the EEPROM Data Memory

There are many steps in writing to the EEPROM data memory. Both address and data values must be written to the SFRs. The EEPGD bit must be cleared, and the WREN bit must be set, to enable writes. The WREN bit should be kept clear at all times, except when writing to the EEPROM data. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to EEPROM data memory must also be prefaced with a special sequence of instructions, that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruptions. The firmware should verify that a write is not in progress, before starting another cycle. The steps to write to EEPROM data memory are:

- 1. If step 10 is not implemented, check the WR bit to see if a write is in progress.

- 2. Write the address to EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 3. Write the 8-bit data value to be programmed in the EEDATA register.

- 4. Clear the EEPGD bit to point to EEPROM data memory.

- 5. Set the WREN bit to enable program operations.

- 6. Disable interrupts (if enabled).

- 7. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

- At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) If step 1 is not implemented, then firmware should check for EEIF to be set, or WR to clear, to indicate the end of the program cycle.

| EXAMPLE 4-2: EEPROM DATA WRITE |

|--------------------------------|

|--------------------------------|

| BSF   | STATUS,  | RP1   | ;                        |

|-------|----------|-------|--------------------------|

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BTFSC | EECON1,  | WR    | ;Wait for                |

| GOTO  | \$-1     |       | ;write to finish         |

| BCF   | STATUS,  | RP0   | ;Bank 2                  |

| MOVF  | ADDR, W  |       | ;Address to              |

| MOVWF | EEADR    |       | ;write to                |

| MOVF  | VALUE, W | v     | ;Data to                 |

| MOVWF | EEDATA   |       | ;write                   |

| BSF   | STATUS,  | RP0   | ;Bank 3                  |

| BCF   | EECON1,  | EEPGD | ;Point to Data memory    |

| BSF   | EECON1,  | WREN  | ;Enable writes           |

|       |          |       | ;Only disable interrupts |

| BCF   | INTCON,  | GIE   | ; if already enabled,    |

|       |          |       | ;otherwise discard       |

| MOVLW |          |       | ;Write 55h to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| MOVLW | 0xAA     |       | ;Write AAh to            |

| MOVWF | EECON2   |       | ;EECON2                  |

| BSF   | EECON1,  | WR    | ;Start write operation   |

|       |          |       | ;Only enable interrupts  |

| BSF   | INTCON,  | GIE   | ; if using interrupts,   |

|       |          |       | ;otherwise discard       |

| BCF   | EECON1,  | WREN  | ;Disable writes          |

|       |          |       |                          |

#### SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h) REGISTER 9-1: R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 SMP D/A Р R/W BF CKE S UA bit 7 bit 0 bit 7 SMP: Sample bit SPI Master mode: 1 = Input data sampled at end of data output time 0 = Input data sampled at middle of data output time SPI Slave mode: SMP must be cleared when SPI is used in slave mode In I<sup>2</sup>C Master or Slave mode: 1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for high speed mode (400 kHz) bit 6 CKE: SPI Clock Edge Select (Figure 9-2, Figure 9-3 and Figure 9-4) SPI mode: For CKP = 0 1 = Data transmitted on rising edge of SCK 0 = Data transmitted on falling edge of SCK For CKP = 1 1 = Data transmitted on falling edge of SCK 0 = Data transmitted on rising edge of SCK In I<sup>2</sup>C Master or Slave mode: 1 = Input levels conform to SMBus spec 0 = Input levels conform to I<sup>2</sup>C specs **D/A**: Data/Address bit (I<sup>2</sup>C mode only) bit 5 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address bit 4 P: STOP bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET) 0 = STOP bit was not detected last bit 3 S: START bit (I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.) 1 = Indicates that a START bit has been detected last (this bit is '0' on RESET) 0 = START bit was not detected last bit 2 **R/W**: Read/Write bit Information (I<sup>2</sup>C mode only) This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit or not ACK bit. In I<sup>2</sup>C Slave mode: 1 = Read0 = WriteIn I<sup>2</sup>C Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress Logical OR of this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode. bit 1 **UA**: Update Address (10-bit I<sup>2</sup>C mode only) 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated bit BF: Buffer Full Status bit Receive (SPI and I<sup>2</sup>C modes): 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty Transmit (I<sup>2</sup>C mode only): 1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full 0 = Data transmit complete (does not include the ACK and STOP bits), SSPBUF is empty Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

#### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data, when required (slavetransmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte.

For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| Note: | Following the Repeated START condition<br>(step 7) in 10-bit mode, the user only<br>needs to match the first 7-bit address. The |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | user does not update the SSPADD for the second half of the address.                                                             |

#### 9.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

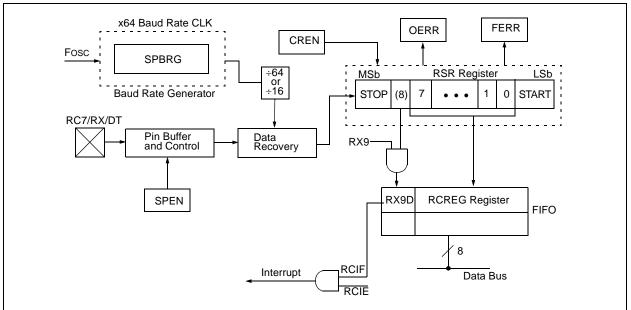

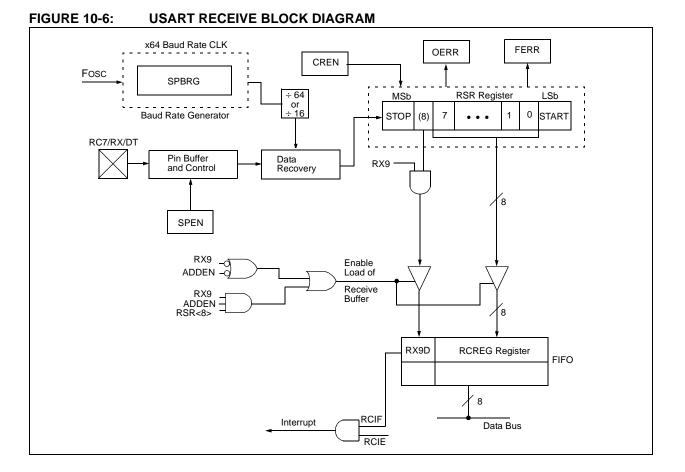

#### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, and no further data will be received. It is therefore, essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

### 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

#### 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion