Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f874t-20-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

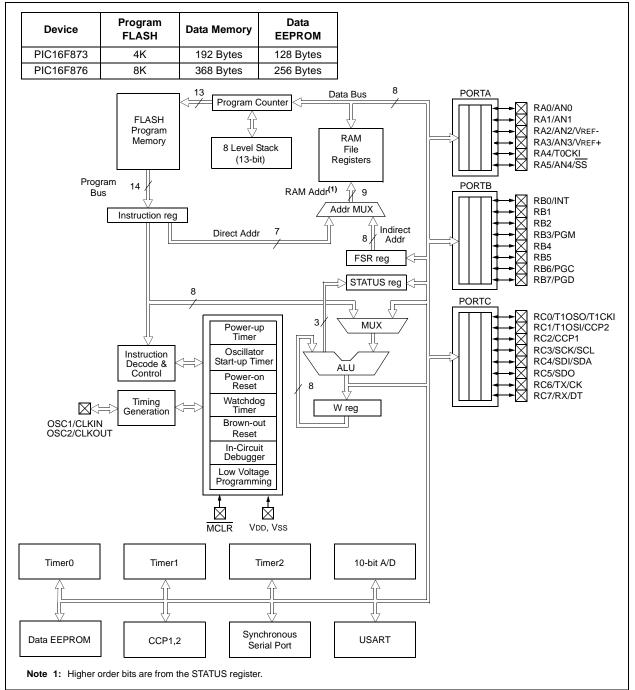

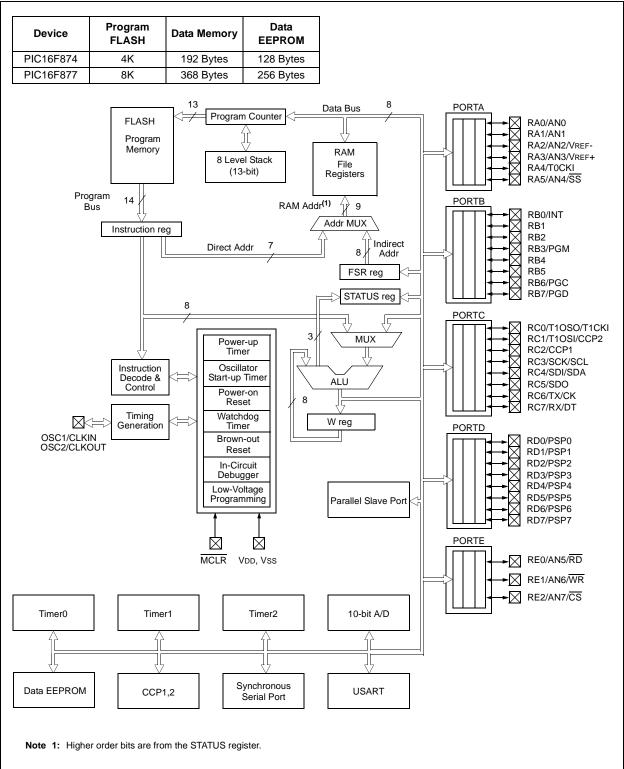

# 1.0 DEVICE OVERVIEW

This document contains device specific information. Additional information may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. There are four devices (PIC16F873, PIC16F874, PIC16F876 and PIC16F877) covered by this data sheet. The PIC16F876/873 devices come in 28-pin packages and the PIC16F877/874 devices come in 40-pin packages. The Parallel Slave Port is not implemented on the 28-pin devices.

The following device block diagrams are sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

© 1998-2013 Microchip Technology Inc.

| TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin# | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|----------------|-------------------|-------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13             | 14                | 30          | I                    | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14             | 15                | 31          | 0                    | —                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1              | 2                 | 18          | I/P                  | ST                     | Master Clear (Reset) input or programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                        |

|                   |                |                   |             |                      |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2              | 3                 | 19          | I/O                  | TTL                    | RA0 can also be analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 3              | 4                 | 20          | I/O                  | TTL                    | RA1 can also be analog input1.                                                                                                                                                                                    |

| RA2/AN2/VREF-     | 4              | 5                 | 21          | I/O                  | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                               |

| RA3/AN3/VREF+     | 5              | 6                 | 22          | I/O                  | TTL                    | RA3 can also be analog input3 or positive<br>analog reference voltage.                                                                                                                                            |

| RA4/T0CKI         | 6              | 7                 | 23          | I/O                  | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                          |

| RA5/SS/AN4        | 7              | 8                 | 24          | I/O                  | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                                |

|                   |                |                   |             |                      |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33             | 36                | 8           | I/O                  | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1               | 34             | 37                | 9           | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB2               | 35             | 38                | 10          | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB3/PGM           | 36             | 39                | 11          | I/O                  | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                                |

| RB4               | 37             | 41                | 14          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB5               | 38             | 42                | 15          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB6/PGC           | 39             | 43                | 16          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                                  |

| RB7/PGD           | 40             | 44                | 17          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                                   |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |             | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2.8 PCON Register

The Power Control (PCON) Register contains flag bits to allow differentiation between a Power-on Reset (POR), a Brown-out Reset (BOR), a Watchdog Reset (WDT), and an external MCLR Reset.

Note: BOR is unknown on POR. It must be set by the user and checked on subsequent RESETS to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a "don't care" and is not predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the configuration word).

#### REGISTER 2-8: PCON REGISTER (ADDRESS 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     |     | —   | —   | —   |     | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR**: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0

**BOR**: Brown-out Reset Status bit 1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

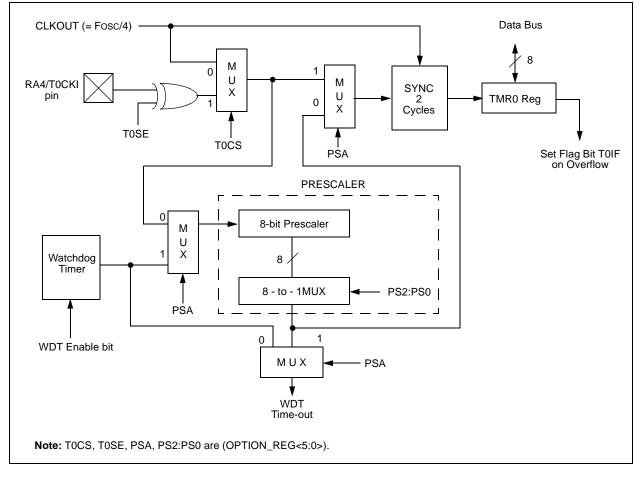

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

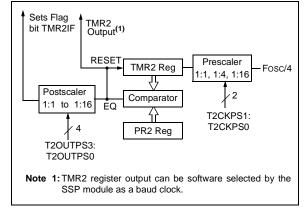

# 7.0 TIMER2 MODULE

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for the PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device RESET.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4, or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon RESET.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut-off by clearing control bit TMR2ON (T2CON<2>), to minimize power consumption.

Register 7-1 shows the Timer2 control register.

Additional information on timer modules is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

#### FIGURE 7-1: TIMER2 BLOCK DIAGRAM

#### REGISTER 7-1: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

|         | U-0               | R/W-0               | R/W-0       | R/W-0        | R/W-0         | R/W-0     | R/W-0        | R/W-0   |

|---------|-------------------|---------------------|-------------|--------------|---------------|-----------|--------------|---------|

|         | _                 | TOUTPS3             | TOUTPS2     | TOUTPS1      | TOUTPS0       | TMR2ON    | T2CKPS1      | T2CKPS0 |

|         | bit 7             | •                   |             |              |               |           |              | bit 0   |

|         |                   |                     |             |              |               |           |              |         |

| bit 7   | Unimplen          | n <b>ented:</b> Rea | d as '0'    |              |               |           |              |         |

| bit 6-3 | TOUTPS3           | :TOUTPS0:           | Timer2 Out  | put Postscal | e Select bits |           |              |         |

|         | 0000 = 1:         | 1 Postscale         |             |              |               |           |              |         |

|         |                   | 2 Postscale         |             |              |               |           |              |         |

|         | •                 | 3 Postscale         |             |              |               |           |              |         |

|         | •                 |                     |             |              |               |           |              |         |

|         | •                 |                     |             |              |               |           |              |         |

|         | 1111 <b>= 1</b> : | 16 Postscale        | <b>;</b>    |              |               |           |              |         |

| bit 2   | -                 | Timer2 On I         | bit         |              |               |           |              |         |

|         | 1 = Timer2        |                     |             |              |               |           |              |         |

|         | 0 = Timer2        |                     |             |              |               |           |              |         |

| bit 1-0 |                   | :T2CKPS0:           | Timer2 Cloc | k Prescale S | Select bits   |           |              |         |

|         | 00 = Pres         |                     |             |              |               |           |              |         |

|         | 1x = Pres         |                     |             |              |               |           |              |         |

|         |                   |                     |             |              |               |           |              |         |

|         | Legend:           |                     |             |              |               |           |              |         |

|         | R = Reada         | able bit            | W = W       | /ritable bit | U = Unim      | plemented | bit, read as | '0'     |

|         | - n = Value       | e at POR            | '1' = B     | it is set    | '0' = Bit i   | s cleared | x = Bit is u | nknown  |

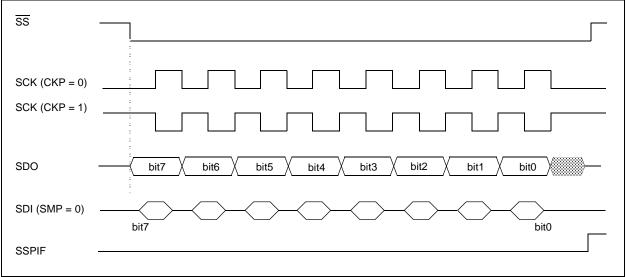

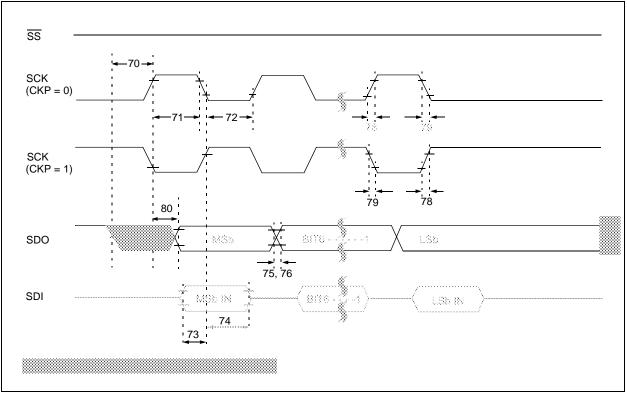

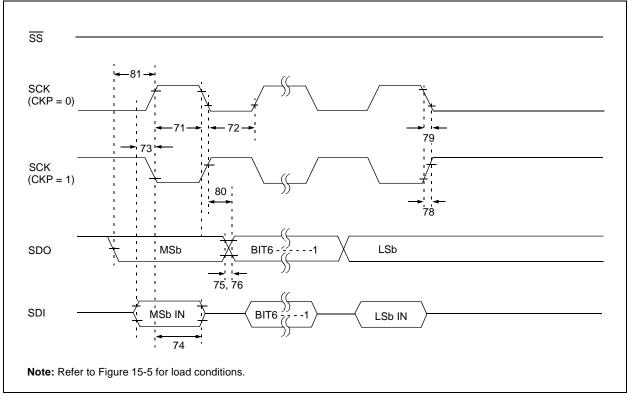

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

## FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

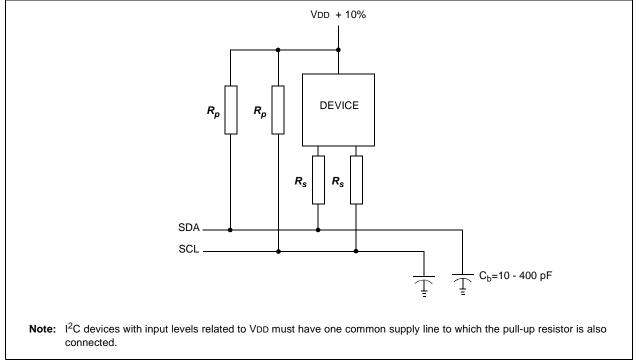

# 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^{2}C$  bus devices, the values of resistors  $R_{p}$  and  $R_{s}$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_{p}$ , due to the specified minimum sink current of 3 mA at VOL max = 0.4V, for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_p$ min =  $(5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-27. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

|       | R/W-0                          | R/W-0         | R/W-0        | R/W-0          | U-0            | R/W-0     | R-1           | R/W-0      |

|-------|--------------------------------|---------------|--------------|----------------|----------------|-----------|---------------|------------|

|       | CSRC                           | TX9           | TXEN         | SYNC           | _              | BRGH      | TRMT          | TX9D       |

|       | bit 7                          |               |              |                |                |           |               | bit 0      |

|       |                                |               |              |                |                |           |               |            |

| bit 7 | CSRC: Cloc                     |               | lect bit     |                |                |           |               |            |

|       | Asynchronou<br>Don't care      | us mode:      |              |                |                |           |               |            |

|       | Synchronou                     | s mode:       |              |                |                |           |               |            |

|       | 1 = Master n                   |               | generated ir | nternally from | n BRG)         |           |               |            |

|       | 0 = Slave m                    | ode (clock fr | om external  | source)        |                |           |               |            |

| bit 6 | TX9: 9-bit Tr                  |               |              |                |                |           |               |            |

|       | 1 = Selects 9<br>0 = Selects 8 |               |              |                |                |           |               |            |

| bit 5 | TXEN: Tran                     | smit Enable   | bit          |                |                |           |               |            |

|       | 1 = Transmit                   |               |              |                |                |           |               |            |

|       | 0 = Transmit                   | tdisabled     |              |                |                |           |               |            |

|       | Note: SREN                     | I/CREN ovei   | rides TXEN   | in SYNC m      | ode.           |           |               |            |

| bit 4 |                                | RT Mode S     | elect bit    |                |                |           |               |            |

|       | 1 = Synchro<br>0 = Asynchro    |               |              |                |                |           |               |            |

| bit 3 | Unimpleme                      |               |              |                |                |           |               |            |

| bit 2 | BRGH: High                     |               |              |                |                |           |               |            |

|       | Asynchrono                     |               | 000000       |                |                |           |               |            |

|       | 1 = High spe                   | ed            |              |                |                |           |               |            |

|       | 0 = Low spe                    |               |              |                |                |           |               |            |

|       | Synchronous<br>Unused in th    |               |              |                |                |           |               |            |

| bit 1 | TRMT: Trans                    |               | aister Statu | s bit          |                |           |               |            |

|       | 1 = TSR em                     |               | 9            |                |                |           |               |            |

|       | 0 = TSR full                   |               |              |                |                |           |               |            |

| bit 0 | <b>TX9D:</b> 9th b             | it of Transmi | t Data, can  | be parity bit  |                |           |               |            |

|       | Logondi                        |               |              |                |                |           |               |            |

|       | Legend:<br>R = Readab          | la hit        | W = Wri      | tahla hit      | U = Unimple    | amonted b | it road as "  | <b>)</b> ' |

|       | - n = Value a                  |               | '1' = Bit    |                | '0' = Bit is c |           | x = Bit is ur |            |

|       |                                |               | i – Dil      | 10 301         |                |           |               | IN IOWIT   |

## 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

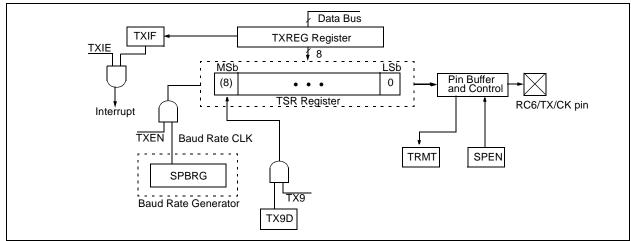

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

#### 11.2 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires a minimum 12TAD per 10-bit conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2Tosc

- 8Tosc

- 32Tosc

- Internal A/D module RC oscillator (2-6 μs)

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$

Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

## TABLE 11-1: TAD VS. MAXIMUM DEVICE OPERATING FREQUENCIES (STANDARD DEVICES (C))

| AD Clock                | Maximum Device Frequency |          |

|-------------------------|--------------------------|----------|

| Operation               | ADCS1:ADCS0              | Max.     |

| 2Tosc                   | 0 0                      | 1.25 MHz |

| 8Tosc                   | 01                       | 5 MHz    |

| 32Tosc                  | 10                       | 20 MHz   |

| RC <sup>(1, 2, 3)</sup> | 11                       | (Note 1) |

Note 1: The RC source has a typical TAD time of 4  $\mu$ s, but can vary between 2-6  $\mu$ s.

2: When the device frequencies are greater than 1 MHz, the RC A/D conversion clock source is only recommended for SLEEP operation.

3: For extended voltage devices (LC), please refer to the Electrical Characteristics (Sections 15.1 and 15.2).

# 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

| Note | 1: When reading the port register, any pin   |

|------|----------------------------------------------|

|      | configured as an analog input channel will   |

|      | read as cleared (a low level). Pins config-  |

|      | ured as digital inputs will convert an ana-  |

|      | log input. Analog levels on a digitally      |

|      | configured input will not affect the conver- |

|      | sion accuracy.                               |

2: Analog levels on any pin that is defined as a digital input (including the AN7:AN0 pins), may cause the input buffer to consume current that is out of the device specifications.

# PIC16F87X

NOTES:

| POR | BOR | то | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 12-4: STATUS BITS AND THEIR SIGNIFICANCE

Legend: x = don't care, u = unchanged

#### TABLE 12-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT Reset                          | 000h                  | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 0001 luuu          | u0               |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| Register   | Devices |     |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|------------|---------|-----|-----|-----|------------------------------------|---------------------------|---------------------------------|

| W          | 873     | 874 | 876 | 877 | XXXX XXXX                          | <u>uuuu</u> uuuu          | uuuu uuuu                       |

| INDF       | 873     | 874 | 876 | 877 | N/A                                | N/A                       | N/A                             |

| TMR0       | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| PCL        | 873     | 874 | 876 | 877 | 0000h                              | 0000h                     | PC + 1 <sup>(2)</sup>           |

| STATUS     | 873     | 874 | 876 | 877 | 0001 1xxx                          | 000q quuu <sup>(3)</sup>  | uuuq quuu <sup>(3)</sup>        |

| FSR        | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTA      | 873     | 874 | 876 | 877 | 0x 0000                            | 0u 0000                   | uu uuuu                         |

| PORTB      | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTC      | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTD      | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| PORTE      | 873     | 874 | 876 | 877 | xxx                                | uuu                       | uuu                             |

| PCLATH     | 873     | 874 | 876 | 877 | 0 0000                             | 0 0000                    | u uuuu                          |

| INTCON     | 873     | 874 | 876 | 877 | x000 0000                          | 0000 000u                 | uuuu uuuu <b>(1)</b>            |

| PIR1       | 873     | 874 | 876 | 877 | r000 0000                          | r000 0000                 | ruuu uuuu <b>(1)</b>            |

|            | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu <b>(1)</b>            |

| PIR2       | 873     | 874 | 876 | 877 | -r-0 00                            | -r-0 00                   | -r-u uu <b>(1)</b>              |

| TMR1L      | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| TMR1H      | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| T1CON      | 873     | 874 | 876 | 877 | 00 0000                            | uu uuuu                   | uu uuuu                         |

| TMR2       | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | սսսս սսսս                       |

| T2CON      | 873     | 874 | 876 | 877 | -000 0000                          | -000 0000                 | -uuu uuuu                       |

| SSPBUF     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| SSPCON     | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | սսսս սսսս                       |

| CCPR1L     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | սսսս սսսս                       |

| CCPR1H     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP1CON    | 873     | 874 | 876 | 877 | 00 0000                            | 00 0000                   | uu uuuu                         |

| RCSTA      | 873     | 874 | 876 | 877 | x000 0000                          | 0000 000x                 | uuuu uuuu                       |

| TXREG      | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| RCREG      | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| CCPR2L     | 873     | 874 | 876 | 877 | xxxx xxxx                          | uuuu uuuu                 | uuuu uuuu                       |

| CCPR2H     | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| CCP2CON    | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

| ADRESH     | 873     | 874 | 876 | 877 | XXXX XXXX                          | uuuu uuuu                 | uuuu uuuu                       |

| ADCON0     | 873     | 874 | 876 | 877 | 0000 00-0                          | 0000 00-0                 | uuuu uu-u                       |

| OPTION_REG | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISA      | 873     | 874 | 876 | 877 | 11 1111                            | 11 1111                   | uu uuuu                         |

| TRISB      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISC      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISD      | 873     | 874 | 876 | 877 | 1111 1111                          | 1111 1111                 | uuuu uuuu                       |

| TRISE      | 873     | 874 | 876 | 877 | 0000 -111                          | 0000 -111                 | uuuu -uuu                       |

| PIE1       | 873     | 874 | 876 | 877 | r000 0000                          | r000 0000                 | ruuu uuuu                       |

|            | 873     | 874 | 876 | 877 | 0000 0000                          | 0000 0000                 | uuuu uuuu                       |

#### TABLE 12-6: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition, r = reserved, maintain clear

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for RESET value for specific condition.

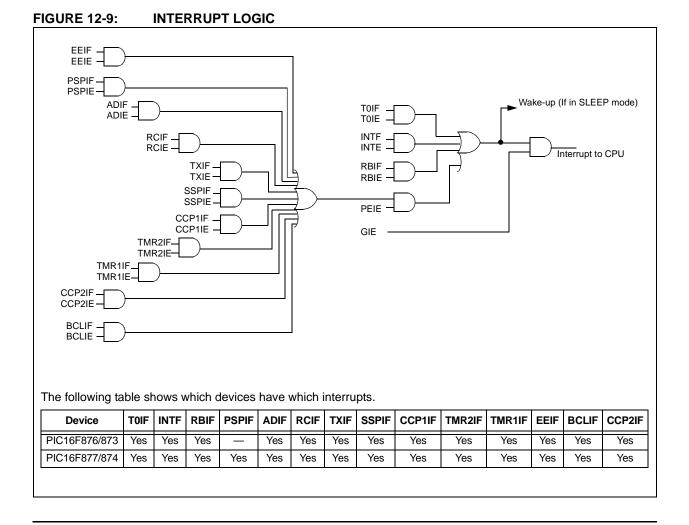

#### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

© 1998-2013 Microchip Technology Inc.

# PIC16F87X

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Description:     | Call Subroutine. First, return<br>address (PC+1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT                         | Clear Watchdog Timer                                                                                                                                                                 |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                        | [label] CLRWDT                                                                                                                                                                       |

| Operands:                      | None                                                                                                                                                                                 |

| Operation:<br>Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \overline{TO}, \ \overline{PD} \end{array}$ |

| Description:                   | CLRWDT instruction resets the<br>Watchdog Timer. It also resets<br>the prescaler of the WDT. Status<br>bits TO and PD are set.                                                       |

| CLRF             | Clear f                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                   |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |  |

| COMF             | Complement f                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                       |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                     |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

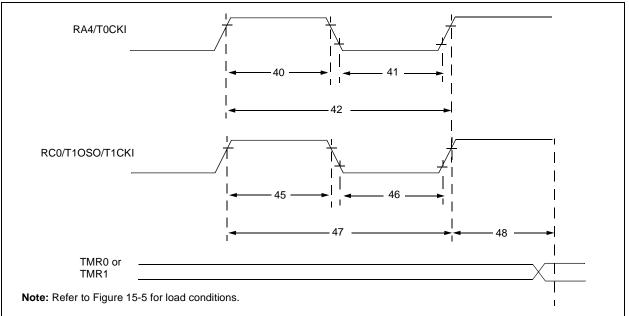

| TABLE 15-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No.                 | Symbol    |                                             | Characteristic       | tic Min        |                       | Тур†  | Max | Units          | Conditions         |

|------------------------------|-----------|---------------------------------------------|----------------------|----------------|-----------------------|-------|-----|----------------|--------------------|

| 40* Tt0H T0CKI High Pulse Wi |           | Width                                       | Vidth No Prescaler   |                | _                     | _     | ns  | Must also meet |                    |

|                              |           | _                                           |                      | With Prescaler | 10                    | _     | _   | ns             | parameter 42       |

| 41*                          | Tt0L      | T0CKI Low Pulse                             | Width                | No Prescaler   | 0.5Tcy + 20           | _     | _   | ns             | Must also meet     |

|                              |           |                                             |                      | With Prescaler | 10                    | _     | _   | ns             | parameter 42       |

| 42*                          | Tt0P      | T0CKI Period                                | 0CKI Period          |                | Tcy + 40              | _     | _   | ns             |                    |

|                              |           |                                             |                      | With Prescaler | Greater of:           | —     | —   | ns             | N = prescale value |

|                              |           |                                             |                      |                | 20 or <u>TCY + 40</u> |       |     |                | (2, 4,, 256)       |

|                              |           |                                             |                      |                | N                     |       |     |                |                    |

| 45*                          | Tt1H      | T1CKI High Time                             | Synchronous, Pr      | escaler = 1    | 0.5Tcy + 20           | —     | I   | -              | Must also meet     |

|                              |           |                                             | Synchronous,         | Standard(F)    | 15                    |       | I   | ns             | parameter 47       |

|                              |           |                                             | Prescaler = $2,4,8$  | Extended(LF)   | 25                    |       | _   | ns             |                    |

|                              |           |                                             | Asynchronous         | Standard(F)    | 30                    |       | _   | ns             |                    |

|                              |           |                                             |                      | Extended(LF)   | 50                    | _     | -   | ns             |                    |

| 46*                          | Tt1L      | T1CKI Low Time                              | Synchronous, Pr      | escaler = 1    | 0.5TCY + 20           | —     | —   | ns             | Must also meet     |

|                              |           |                                             | Synchronous,         | Standard(F)    | 15                    |       | _   | ns             | parameter 47       |

|                              |           |                                             | Prescaler = 2,4,8    | Extended(LF)   | 25                    | —     |     | ns             |                    |

|                              |           |                                             | Asynchronous         | Standard(F)    | 30                    | —     |     | ns             |                    |

|                              |           |                                             |                      | Extended(LF)   | 50                    | —     |     | ns             |                    |

| 47*                          | Tt1P      | T1CKI input                                 | Synchronous          | Standard(F)    | Greater of:           | —     | —   | ns             | N = prescale value |

|                              |           | period                                      |                      |                | 30 or <u>Tcy + 40</u> |       |     |                | (1, 2, 4, 8)       |

|                              |           |                                             |                      |                | N                     |       |     |                |                    |

|                              |           |                                             |                      | Extended(LF)   | Greater of:           |       |     |                | N = prescale value |

|                              |           |                                             |                      |                | 50 OR <u>TCY + 40</u> |       |     |                | (1, 2, 4, 8)       |

|                              |           |                                             |                      | -              | N                     |       |     |                |                    |

|                              |           |                                             | Asynchronous         | Standard(F)    | 60                    |       | _   | ns             |                    |

|                              |           |                                             |                      | Extended(LF)   | 100                   | —     | —   | ns             |                    |

|                              | Ft1       | Timer1 oscillator ir<br>(oscillator enabled |                      | 0              | DC                    | -     | 200 | kHz            |                    |

| 48                           | TCKEZtmr1 | Delay from externa                          | al clock edge to tir | 2Tosc          | —                     | 7Tosc | _   |                |                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

#### FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

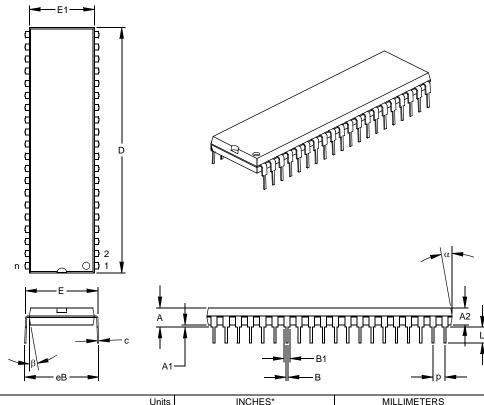

## 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     |       | INCHES* |       | MILLIMETERS |       |       |  |

|----------------------------|-----------|-------|---------|-------|-------------|-------|-------|--|

| Dimensi                    | on Limits | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |  |

| Number of Pins             | n         |       | 40      |       |             | 40    |       |  |

| Pitch                      | р         |       | .100    |       |             | 2.54  |       |  |

| Top to Seating Plane       | А         | .160  | .175    | .190  | 4.06        | 4.45  | 4.83  |  |

| Molded Package Thickness   | A2        | .140  | .150    | .160  | 3.56        | 3.81  | 4.06  |  |

| Base to Seating Plane      | A1        | .015  |         |       | 0.38        |       |       |  |

| Shoulder to Shoulder Width | E         | .595  | .600    | .625  | 15.11       | 15.24 | 15.88 |  |

| Molded Package Width       | E1        | .530  | .545    | .560  | 13.46       | 13.84 | 14.22 |  |

| Overall Length             | D         | 2.045 | 2.058   | 2.065 | 51.94       | 52.26 | 52.45 |  |

| Tip to Seating Plane       | L         | .120  | .130    | .135  | 3.05        | 3.30  | 3.43  |  |

| Lead Thickness             | С         | .008  | .012    | .015  | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1        | .030  | .050    | .070  | 0.76        | 1.27  | 1.78  |  |

| Lower Lead Width           | В         | .014  | .018    | .022  | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eB        | .620  | .650    | .680  | 15.75       | 16.51 | 17.27 |  |

| Mold Draft Angle Top       | α         | 5     | 10      | 15    | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β         | 5     | 10      | 15    | 5           | 10    | 15    |  |

| * 0 / 11' D /              |           |       |         |       |             |       |       |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

# PIC16F87X

NOTES: