Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876-04e-so |

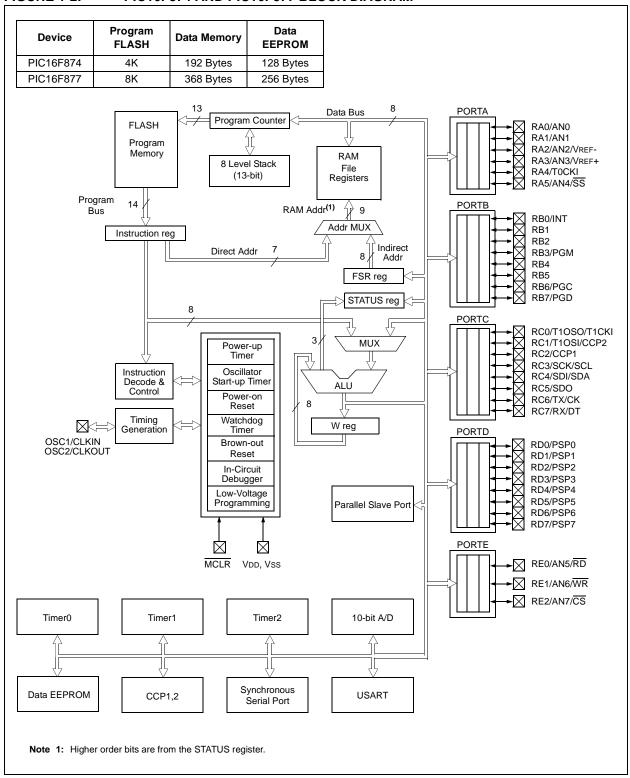

FIGURE 1-2: PIC16F874 AND PIC16F877 BLOCK DIAGRAM

TABLE 1-1: PIC16F873 AND PIC16F876 PINOUT DESCRIPTION

| Pin Name         | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|------------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN       | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT      | 10          | 10           | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP         | 1           | 1            | I/P           | ST                     | Master Clear (Reset) input or programming voltage input. This pin is an active low RESET to the device.                                                                                                      |

|                  |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0          | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1          | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-    | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+    | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI        | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4       | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                  |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software                                                                                                                                                    |

|                  |             |              |               | (1)                    | programmed for internal weak pull-up on all inputs.                                                                                                                                                          |

| RB0/INT          | 21          | 21           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1              | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2              | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3/PGM          | 24          | 24           | I/O           | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4              | 25          | 25           | 1/0           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5              | 26          | 26           | I/O           | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC          | 27          | 27           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming clock.                                                                                                                                |

| RB7/PGD          | 28          | 28           | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                  |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI  | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2   | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1         | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL      | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA      | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO          | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK        | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit or Synchronous Clock.                                                                                                                                        |

| RC7/RX/DT        | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive or Synchronous Data.                                                                                                                                          |

| Vss              | 8, 19       | 8, 19        | Р             | _                      | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD              | 20          | 20           | Р             | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: L= input | O = outr    |              |               | input/output           | P = nower                                                                                                                                                                                                    |

$Legend: \quad I = input$

O = output

I/O = input/output

P = power

— = Not used

TTL = TTL input

ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

**NOTES:**

FIGURE 2-3: PIC16F877/876 REGISTER FILE MAP

|                                            | File<br>Address | ,                                          | File<br>Address |                                            | File<br>Address |                                            | File<br>Address |

|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|-----------------|--------------------------------------------|-----------------|

| Indirect addr.(*)                          | 00h             | Indirect addr.(*)                          | 80h             | Indirect addr.(*)                          | 100h            | Indirect addr.(*)                          | 180h            |

| TMR0                                       | 01h             | OPTION_REG                                 | 81h             | TMR0                                       | 101h            | OPTION_REG                                 | 181h            |

| PCL                                        | 02h             | PCL                                        | 82h             | PCL                                        | 102h            | PCL                                        | 182h            |

| STATUS                                     | 03h             | STATUS                                     | 83h             | STATUS                                     | 103h            | STATUS                                     | 183h            |

| FSR                                        | 04h             | FSR                                        | 84h             | FSR                                        | 104h            | FSR                                        | 184h            |

| PORTA                                      | 05h             | TRISA                                      | 85h             |                                            | 105h            |                                            | 185h            |

| PORTB                                      | 06h             | TRISB                                      | 86h             | PORTB                                      | 106h            | TRISB                                      | 186h            |

| PORTC                                      | 07h             | TRISC                                      | 87h             |                                            | 107h            |                                            | 187h            |

| PORTD <sup>(1)</sup>                       | 08h             | TRISD <sup>(1)</sup>                       | 88h             |                                            | 108h            |                                            | 188h            |

| PORTE <sup>(1)</sup>                       | 09h             | TRISE <sup>(1)</sup>                       | 89h             |                                            | 109h            |                                            | 189h            |

| PCLATH                                     | 0Ah             | PCLATH                                     | 8Ah             | PCLATH                                     | 10Ah            | PCLATH                                     | 18Ah            |

| INTCON                                     | 0Bh             | INTCON                                     | 8Bh             | INTCON                                     | 10Bh            | INTCON                                     | 18Bh            |

| PIR1                                       | 0Ch             | PIE1                                       | 8Ch             | EEDATA                                     | 10Ch            | EECON1                                     | 18Ch            |

| PIR2                                       | 0Dh             | PIE2                                       | 8Dh             | EEADR                                      | 10Dh            | EECON2                                     | 18Dh            |

| TMR1L                                      | 0Eh             | PCON                                       | 8Eh             | EEDATH                                     | 10Eh            | Reserved <sup>(2)</sup>                    | 18Eh            |

| TMR1H                                      | 0Fh             |                                            | 8Fh             | EEADRH                                     | 10Fh            | Reserved <sup>(2)</sup>                    | 18Fh            |

| T1CON                                      | 10h             |                                            | 90h             |                                            | 110h            |                                            | 190h            |

| TMR2                                       | 11h             | SSPCON2                                    | 91h             |                                            | 111h            |                                            | 191h            |

| T2CON                                      | 12h             | PR2                                        | 92h             |                                            | 112h            |                                            | 192h            |

| SSPBUF                                     | 13h             | SSPADD                                     | 93h             |                                            | 113h            |                                            | 193h            |

| SSPCON                                     | 14h             | SSPSTAT                                    | 94h             |                                            | 114h            |                                            | 194h            |

| CCPR1L                                     | 15h             |                                            | 95h             |                                            | 115h            |                                            | 195h            |

| CCPR1H                                     | 16h             |                                            | 96h             |                                            | 116h            |                                            | 196h            |

| CCP1CON                                    | 17h             |                                            | 97h             | General                                    | 117h            | General<br>Purpose                         | 197h            |

| RCSTA                                      | 18h             | TXSTA                                      | 98h             | Purpose<br>Register                        | 118h            | Register                                   | 198h            |

| TXREG                                      | 19h             | SPBRG                                      | 99h             | 16 Bytes                                   | 119h            | 16 Bytes                                   | 199h            |

| RCREG                                      | 1Ah             |                                            | 9Ah             |                                            | 11Ah            |                                            | 19Ah            |

| CCPR2L                                     | 1Bh             |                                            | 9Bh             |                                            | 11Bh            |                                            | 19Bh            |

| CCPR2H                                     | 1Ch             |                                            | 9Ch             |                                            | 11Ch            |                                            | 19Ch            |

| CCP2CON                                    | 1Dh             |                                            | 9Dh             |                                            | 11 Dh           |                                            | 19Dh            |

| ADRESH                                     | 1Eh             | ADRESL                                     | 9Eh             |                                            | 11Eh            |                                            | 19Eh            |

| ADCON0                                     | 1Fh             | ADCON1                                     | 9Fh             |                                            | 11Fh            |                                            | 19Fh            |

|                                            | 20h             |                                            | A0h             |                                            | 120h            |                                            | 1A0h            |

| General<br>Purpose<br>Register<br>96 Bytes |                 | General<br>Purpose<br>Register<br>80 Bytes | EFh             | General<br>Purpose<br>Register<br>80 Bytes | . 16Fh          | General<br>Purpose<br>Register<br>80 Bytes | 1EFh            |

|                                            |                 | accesses<br>70h-7Fh                        | F0h             | accesses<br>70h-7Fh                        | 170h            | accesses<br>70h - 7Fh                      | 1F0h            |

| Bank 0                                     | 7Fh             | Bank 1                                     | FFh             | Bank 2                                     | 17Fh            | Bank 3                                     | 1FFh            |

| Bank 0                                     |                 | Dalik i                                    |                 | Dalik Z                                    |                 | Daile                                      |                 |

Unimplemented data memory locations, read as '0'.

<sup>\*</sup> Not a physical register.

**Note 1:** These registers are not implemented on the PIC16F876.

<sup>2:</sup> These registers are reserved, maintain these registers clear.

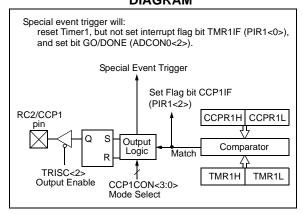

#### 8.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · Driven high

- · Driven low

- · Remains unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

# FIGURE 8-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 8.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the PORTC I/O data latch.

#### 8.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 8.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen, the CCP1 pin is not affected. The CCPIF bit is set, causing a CCP interrupt (if enabled).

#### 8.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated, which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special event trigger output of CCP2 resets the TMR1 register pair and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

#### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data, when required (slave-transmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit  $R/\overline{W}$  (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte.

For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

Note: Following the Repeated START condition (step 7) in 10-bit mode, the user only needs to match the first 7-bit address. The user does not update the SSPADD for the second half of the address.

#### 9.2.1.2 Slave Reception

Note:

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

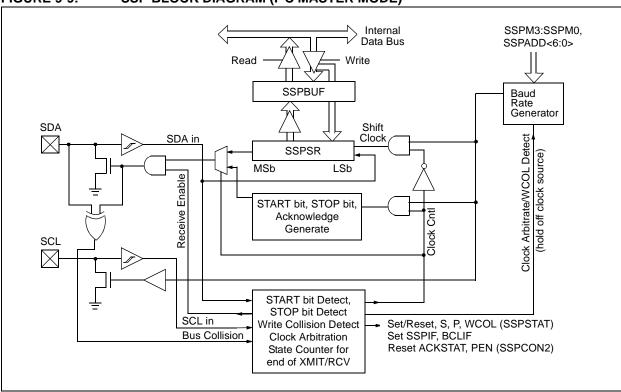

#### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- · START condition

- STOP condition

- Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated START

FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- · Data Transfer

- · A START Condition

- A Repeated START Condition

- · An Acknowledge Condition

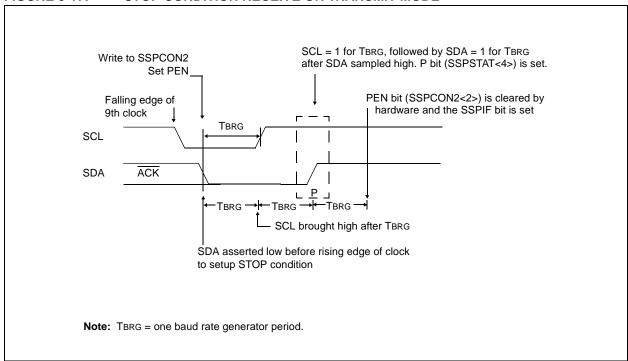

#### 9.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-17).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

#### 9.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

FIGURE 9-17: STOP CONDITION RECEIVE OR TRANSMIT MODE

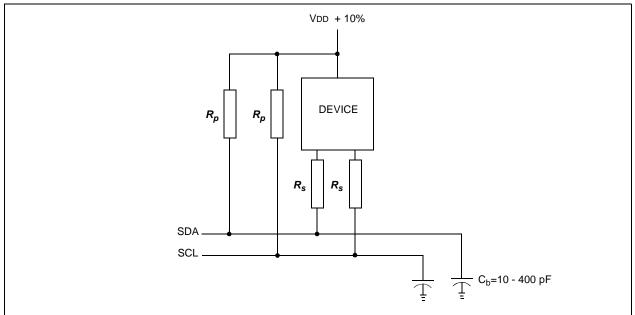

## 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^2C$  bus devices, the values of resistors  $R_p$  and  $R_s$  in Figure 9-27 depend on the following parameters:

- · Supply voltage

- · Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_p$ , due to the specified minimum sink current of 3 mA at Vol max = 0.4V, for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_p$  min = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-27. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in I<sup>2</sup>C mode (master or slave).

#### FIGURE 9-27: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

**Note:** I<sup>2</sup>C devices with input levels related to VDD must have one common supply line to which the pull-up resistor is also connected.

# 10.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, serial EEPROMs etc.

The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### REGISTER 10-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0 | R-1  | R/W-0 |

|-------|-------|-------|-------|-----|-------|------|-------|

| CSRC  | TX9   | TXEN  | SYNC  | _   | BRGH  | TRMT | TX9D  |

| bit 7 |       |       |       |     |       |      | bit 0 |

bit 7 CSRC: Clock Source Select bit

Asynchronous mode:

Don't care

Synchronous mode:

1 = Master mode (clock generated internally from BRG)

0 = Slave mode (clock from external source)

bit 6 TX9: 9-bit Transmit Enable bit

1 =Selects 9-bit transmission

0 = Selects 8-bit transmission

bit 5 TXEN: Transmit Enable bit

1 = Transmit enabled

0 = Transmit disabled

Note: SREN/CREN overrides TXEN in SYNC mode.

bit 4 SYNC: USART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

bit 3 Unimplemented: Read as '0'

bit 2 BRGH: High Baud Rate Select bit

Asynchronous mode:

1 = High speed

0 = Low speed

Synchronous mode:

Unused in this mode

bit 1 TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0 **TX9D:** 9th bit of Transmit Data, can be parity bit

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0  | R-0  | R-x   |

|-------|-------|-------|-------|-------|------|------|-------|

| SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR | OERR | RX9D  |

| bit 7 |       |       |       |       |      |      | bit 0 |

bit 7 SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RC7/RX/DT and RC6/TX/CK pins as serial port pins)

0 = Serial port disabled

bit 6 RX9: 9-bit Receive Enable bit

1 =Selects 9-bit reception

0 = Selects 8-bit reception

bit 5 SREN: Single Receive Enable bit

Asynchronous mode:

Don't care

Synchronous mode - master:

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - slave:

Don't care

bit 4 CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables continuous receive

0 = Disables continuous receive

Synchronous mode:

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)

0 = Disables continuous receive

bit 3 ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enables interrupt and load of the receive buffer when RSR<8> is set

0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit

bit 2 **FERR**: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

bit 1 OERR: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

bit 0 **RX9D:** 9th bit of Received Data (can be parity bit, but must be calculated by user firmware)

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

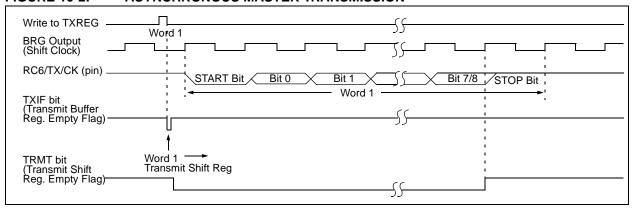

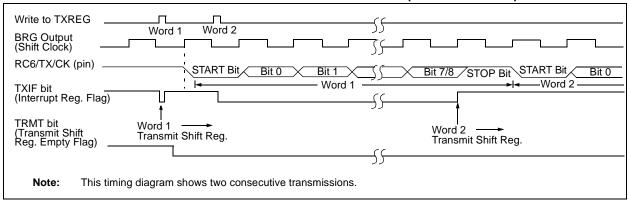

When setting up an Asynchronous Transmission, follow these steps:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH (Section 10.1).

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit TXIE.

- If 9-bit transmission is desired, then set transmit bit TX9.

- Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Load data to the TXREG register (starts transmission).

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### FIGURE 10-2: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 10-3: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 10-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address                | Name                                   | Bit 7                | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|----------------------------------------|----------------------|----------|--------|-------|-------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE     | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9      | SREN   | CREN  | _     | FERR   | OERR   | RX9D      | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG                                  | USART Tra            | nsmit Re | gister |       |       |        |        |           | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9      | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |          |        |       |       |        |        | 0000 0000 | 0000 0000                |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

## 10.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode. Bit SREN is a "don't care" in Slave mode.

If receive is enabled by setting bit CREN prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Reception, follow these steps:

Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- 9. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address                | Name                                   | Bit 7                | Bit 6    | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|----------------------------------------|----------------------|----------|---------|-------|-------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE     | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF      | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF     | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9      | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D      | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG                                  | USART R              | eceive R | egister |       |       |        |        |           | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE     | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9      | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |          |         |       |       |        |        | 0000 0000 | 0000 0000                |                                 |

$\label{eq:local_local_local} \textbf{Legend: } \textbf{x} = \textbf{unknown, - = unimplemented, read as '0'}. \textbf{Shaded cells are not used for synchronous slave reception.}$

Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices, always maintain these bits clear.

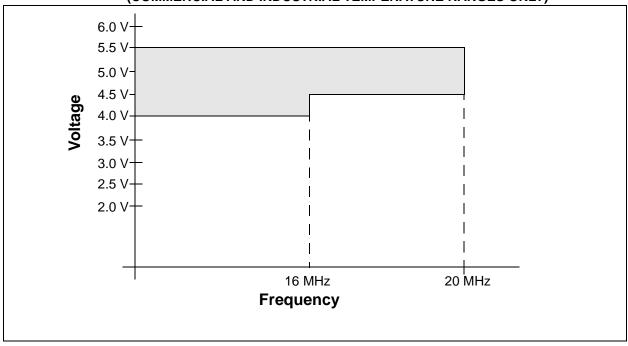

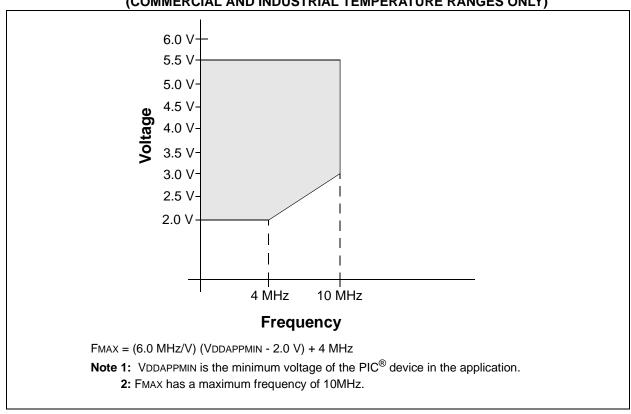

FIGURE 15-1: PIC16F87X-20 VOLTAGE-FREQUENCY GRAPH (COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES ONLY)

FIGURE 15-2: PIC16LF87X-04 VOLTAGE-FREQUENCY GRAPH (COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES ONLY)

TABLE 15-9: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Param<br>No. | Sym     | Characte               | eristic      | Min        | Max  | Units | Conditions                                  |

|--------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100          | Thigh   | Clock high time        | 100 kHz mode | 4.0        | _    | μ\$   | Device must operate at a minimum of 1.5 MHz |

|              |         |                        | 400 kHz mode | 0.6        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|              |         |                        | SSP Module   | 0.5Tcy     | _    |       |                                             |

| 101          | Tlow    | Clock low time         | 100 kHz mode | 4.7        | _    | μS    | Device must operate at a minimum of 1.5 MHz |

|              |         |                        | 400 kHz mode | 1.3        | _    | μS    | Device must operate at a minimum of 10 MHz  |

|              |         |                        | SSP Module   | 0.5TcY     | _    |       |                                             |

| 102          | Tr      | SDA and SCL rise       | 100 kHz mode | _          | 1000 | ns    |                                             |

|              |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10 to 400 pF     |

| 103          | Tf      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                             |

|              |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10 to 400 pF     |

| 90           | Tsu:sta | START condition        | 100 kHz mode | 4.7        | _    | μS    | Only relevant for Repeated                  |

|              |         | setup time             | 400 kHz mode | 0.6        | _    | μS    | START condition                             |

| 91           | Thd:sta | START condition hold   | 100 kHz mode | 4.0        | _    | μS    | After this period, the first clock          |

|              |         | time                   | 400 kHz mode | 0.6        | _    | μS    | pulse is generated                          |

| 106          | Thd:dat | Data input hold time   | 100 kHz mode | 0          | _    | ns    |                                             |

|              |         |                        | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| 107          | Tsu:dat | Data input setup time  | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|              |         |                        | 400 kHz mode | 100        |      | ns    |                                             |

| 92           | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | _    | μS    |                                             |

|              |         | time                   | 400 kHz mode | 0.6        | _    | μS    |                                             |

| 109          | Taa     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | (Note 1)                                    |

|              |         | clock                  | 400 kHz mode | _          | _    | ns    |                                             |

| 110          | Tbuf    | Bus free time          | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |

|              |         |                        | 400 kHz mode | 1.3        | _    | μS    | before a new transmission can start         |

| <u>-</u>     | Cb      | Bus capacitive loading |              |            | 400  | pF    |                                             |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast mode (400 kHz) I<sup>2</sup>C bus device can be used in a standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement that Tsu:dat ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ Tsu:dat = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

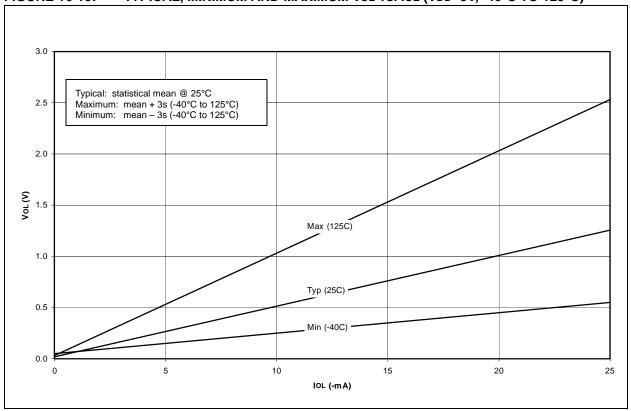

FIGURE 16-19: TYPICAL, MINIMUM AND MAXIMUM Vol vs. Iol (VDD=3V, -40°C TO 125°C)

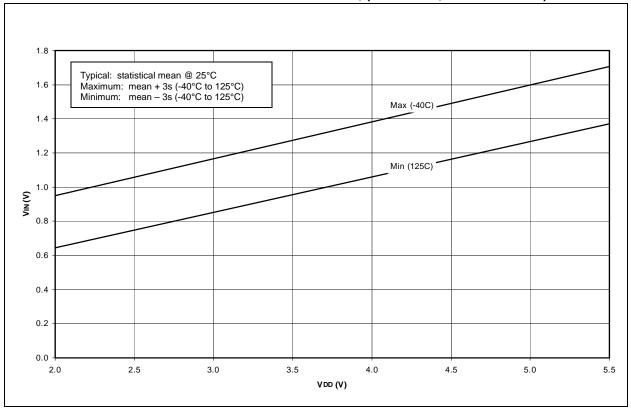

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. VDD, (TTL INPUT, -40°C TO 125°C)

#### **APPENDIX A: REVISION HISTORY**

| Version | Date | Revision Description                                                                                                                                                                                            |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 1998 | This is a new data sheet. However, these devices are similar to the PIC16C7X devices found in the PIC16C7X Data Sheet (DS30390). Data Memory Map for PIC16F873/874, moved ADFM bit from ADCON1<5> to ADCON1<7>. |

| В       | 1999 | FLASH EEPROM access information.                                                                                                                                                                                |

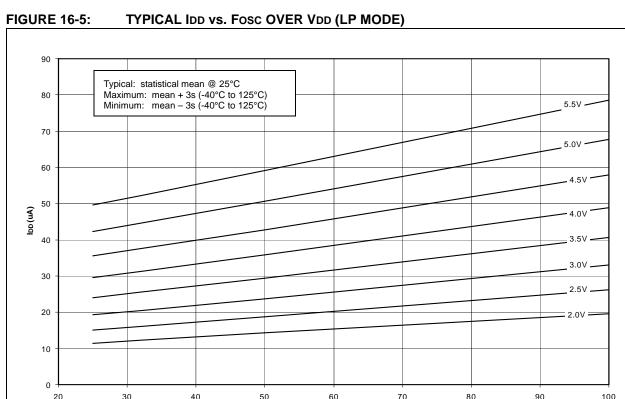

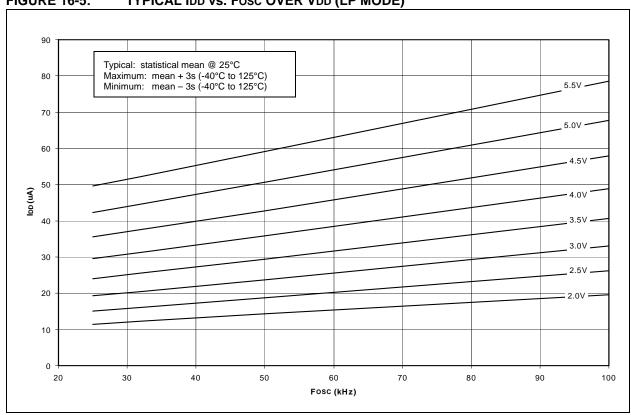

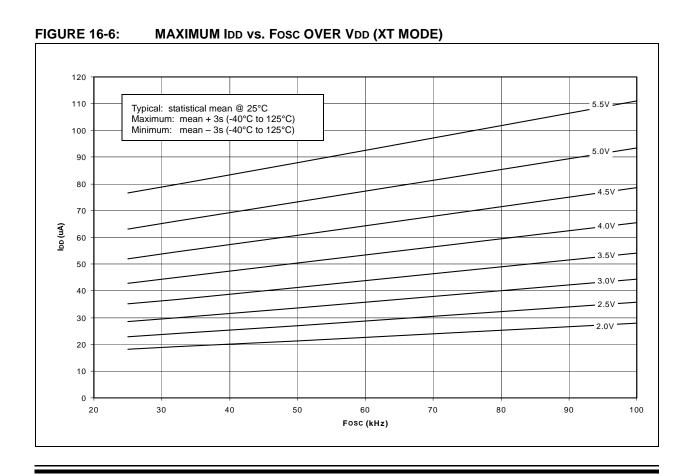

| С       | 2000 | DC characteristics updated. DC performance graphs added.                                                                                                                                                        |

| D       | 2013 | Added a note to each package drawing.                                                                                                                                                                           |

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Difference             | PIC16F876/873                                             | PIC16F877/874                                               |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------|

| A/D                    | 5 channels,<br>10-bits                                    | 8 channels,<br>10-bits                                      |

| Parallel<br>Slave Port | no                                                        | yes                                                         |

| Packages               | 28-pin PDIP,<br>28-pin windowed<br>CERDIP, 28-pin<br>SOIC | 40-pin PDIP,<br>44-pin TQFP,<br>44-pin MQFP,<br>44-pin PLCC |

#### PIC16F87X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device | X /XX XXX  Temperature Package Pattern Range                                                                                                                       | Examples:  a) PIC16F877 - 20/P 301 = Commercial temp., PDIP package, 4 MHz, normal VDD limits, QTP pattern #301.  b) PIC16LF876 - 04I/SO = Industrial temp., SOIC |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device             | PIC16F87X <sup>(1)</sup> , PIC16F87XT <sup>(2)</sup> ; VDD range 4.0V to 5.5V PIC16LF87X <sup>(1)</sup> , PIC16LF87XT <sup>(2)</sup> ; VDD range 2.0V to 5.5V      | package, 200 kHz, Extended VDD limits.  c) PIC16F877 - 10E/P = Extended temp., PDIP package, 10MHz, normal VDD limits.                                            |

| Frequency Range    | 04 = 4 MHz<br>10 = 10 MHz<br>20 = 20 MHz                                                                                                                           |                                                                                                                                                                   |

| Temperature Range  | blank = $0^{\circ}$ C to $+70^{\circ}$ C (Commercial)<br>I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended) |                                                                                                                                                                   |

| Package            | PQ = MQFP (Metric PQFP) PT = TQFP (Thin Quad Flatpack) SO = SOIC SP = Skinny plastic DIP P = PDIP L = PLCC                                                         | Note 1: F = CMOS FLASH     LF = Low Power CMOS FLASH 2: T = in tape and reel - SOIC, PLCC,     MQFP, TQFP packages only.                                          |

<sup>\*</sup> JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

#### **Sales and Support**

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

**NOTES:**