Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876-10e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0  | Device Overview                                                             |     |

|------|-----------------------------------------------------------------------------|-----|

| 2.0  | Memory Organization                                                         | 11  |

| 3.0  | I/O Ports                                                                   |     |

| 4.0  | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0  | Timer0 Module                                                               |     |

| 6.0  | Timer1 Module                                                               | 51  |

| 7.0  | Timer2 Module                                                               |     |

| 8.0  | Capture/Compare/PWM Modules                                                 |     |

| 9.0  | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0 | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0 | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0 | Special Features of the CPU                                                 | 119 |

| 13.0 | Instruction Set Summary                                                     | 135 |

|      | Development Support                                                         |     |

|      | Electrical Characteristics                                                  |     |

|      | DC and AC Characteristics Graphs and Tables                                 |     |

| 17.0 | Packaging Information                                                       |     |

|      | ndix A: Revision History                                                    |     |

|      | ndix B: Device Differences                                                  |     |

| Appe | ndix C: Conversion Considerations                                           | 198 |

|      | (                                                                           |     |

|      | ine Support                                                                 |     |

|      | ler Response                                                                |     |

| PIC1 | 6F87X Product Identification System                                         |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| TABLE 1-1: | PIC16F873 AND PIC16F876 PINOUT DESCRIPTION   |

|------------|----------------------------------------------|

| IADLE I-I. | FIG 10F0/3 AND FIG 10F0/0 FINOUT DESCRIFTION |

| Pin Name          | DIP SOIC<br>Pin# Pin# |       | I/O/P<br>Type | Buffer<br>Type              | Description                                                                                                                                                                                                  |

|-------------------|-----------------------|-------|---------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 9                     | 9     | I             | ST/CMOS <sup>(3)</sup>      | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT       | 10                    | 10    | 0             | _                           | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp          | 1                     | 1     | I/P           | ST                          | Master Clear (Reset) input or programming voltage input. This<br>pin is an active low RESET to the device.                                                                                                   |

|                   |                       |       |               |                             | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0           | 2                     | 2     | I/O           | TTL                         | RA0 can also be analog input0.                                                                                                                                                                               |

| RA1/AN1           | 3                     | 3     | I/O           | TTL                         | RA1 can also be analog input1.                                                                                                                                                                               |

| RA2/AN2/VREF-     | 4                     | 4     | I/O           | TTL                         | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                          |

| RA3/AN3/VREF+     | 5                     | 5     | I/O           | TTL                         | RA3 can also be analog input3 or positive analog reference voltage.                                                                                                                                          |

| RA4/T0CKI         | 6                     | 6     | I/O           | ST                          | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                             |

| RA5/SS/AN4        | 7                     | 7     | I/O           | TTL                         | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                           |

|                   |                       |       |               |                             | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 21                    | 21    | I/O           | TTL/ST <sup>(1)</sup>       | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1               | 22                    | 22    | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB2               | 23                    | 23    | I/O           | TTL                         |                                                                                                                                                                                                              |

| RB3/PGM           | 24                    | 24    | I/O           | TTL                         | RB3 can also be the low voltage programming input.                                                                                                                                                           |

| RB4               | 25                    | 25    | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB5               | 26                    | 26    | I/O           | TTL                         | Interrupt-on-change pin.                                                                                                                                                                                     |

| RB6/PGC           | 27                    | 27    | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial<br>programming clock.                                                                                                                             |

| RB7/PGD           | 28                    | 28    | I/O           | TTL/ST <sup>(2)</sup>       | Interrupt-on-change pin or In-Circuit Debugger pin. Serial programming data.                                                                                                                                 |

|                   |                       |       |               |                             | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI   | 11                    | 11    | I/O           | ST                          | RC0 can also be the Timer1 oscillator output or Timer1<br>clock input.                                                                                                                                       |

| RC1/T1OSI/CCP2    | 12                    | 12    | I/O           | ST                          | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1          | 13                    | 13    | I/O           | ST                          | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL       | 14                    | 14    | I/O           | ST                          | RC3 can also be the synchronous serial clock input/outpu<br>for both SPI and I <sup>2</sup> C modes.                                                                                                         |

| RC4/SDI/SDA       | 15                    | 15    | I/O           | ST                          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO           | 16                    | 16    | I/O           | ST                          | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK         | 17                    | 17    | I/O           | ST                          | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT         | 18                    | 18    | I/O           | ST                          | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                       |

| Vss               | 8, 19                 | 8, 19 | Р             | _                           | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| Vdd               | 20                    | 20    | Р             | _                           | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input | 0 = outp<br>— = Not   |       |               | input/output<br>= TTL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

This buffer is a Schmitt Trigger input when used in Serial Programming mode.

This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

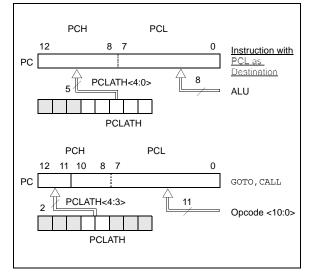

# 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |

|---------|---------------------------|--------------------------------------------------------------|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |

| _       | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |

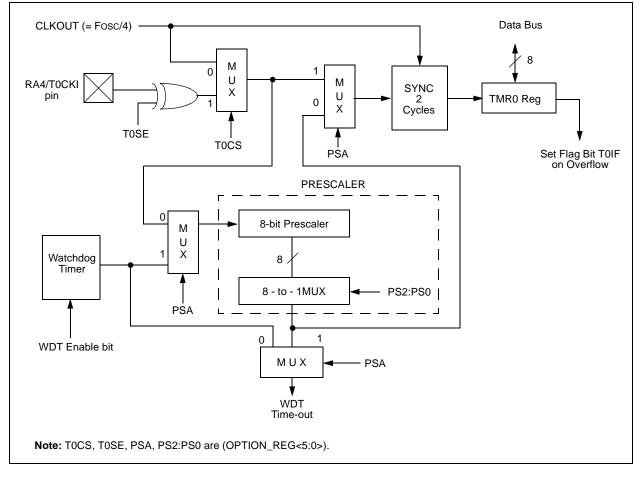

# 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

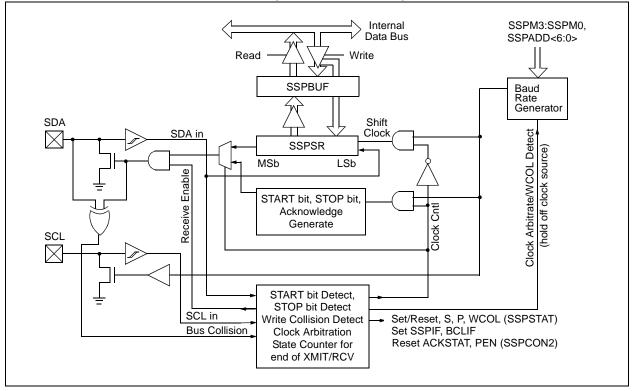

# 9.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

Figure 9-1 shows a block diagram for the SPI mode, while Figure 9-5 and Figure 9-9 show the block diagrams for the two different  $I^2C$  modes of operation.

The Application Note AN734, "Using the PIC<sup>®</sup> MCU SSP for Slave I<sup>2</sup>C<sup>TM</sup> Communication" describes the slave operation of the MSSP module on the PIC16F87X devices. AN735, "Using the PIC<sup>®</sup> MCU MSSP Module for I<sup>2</sup>C<sup>TM</sup> Communications" describes the master operation of the MSSP module on the PIC16F87X devices.

#### 9.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a RESET, or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle, with both the S and P bits clear.

In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (an SSP interrupt will occur if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- Acknowledge transmit

- Repeated START

#### FIGURE 9-9: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### 9.2.6 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a RESET or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In Multi-Master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- Address Transfer

- Data Transfer

- A START Condition

- A Repeated START Condition

- An Acknowledge Condition

#### TABLE 10-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                | Name   | Bit 7                              | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|------------------------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                                | PEIE      | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup>               | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                               | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h                    | TXREG  | USART Tr                           | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup>               | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                               | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | SPBRG Baud Rate Generator Register |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission. **Note 1:** Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

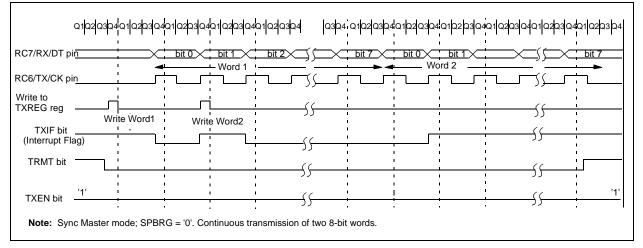

#### FIGURE 10-9: SYNCHRONOUS TRANSMISSION

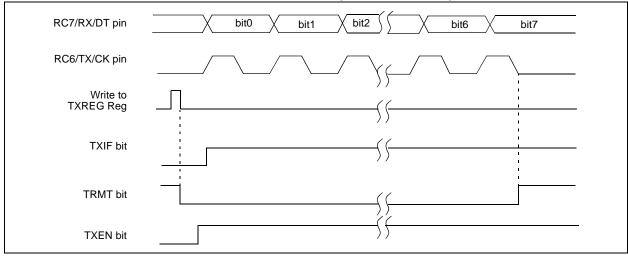

#### FIGURE 10-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 12.4 Power-On Reset (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.2V - 1.7V). To take advantage of the POR, tie the MCLR pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met. Brown-out Reset may be used to meet the start-up conditions. For additional information, refer to Application Note, AN007, "Power-up Trouble Shooting", (DS00007).

#### 12.5 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an accept-able level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature and process variation. See DC parameters for details (TPWRT, parameter #33).

## 12.6 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a delay of 1024 oscillator cycles (from OSC1 input) after the PWRT delay is over (if PWRT is enabled). This helps to ensure that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or Wake-up from SLEEP.

#### 12.7 Brown-out Reset (BOR)

The configuration bit, BODEN, can enable or disable the Brown-out Reset circuit. If VDD falls below VBOR (parameter D005, about 4V) for longer than TBOR (parameter #35, about 100 $\mu$ S), the brown-out situation will reset the device. If VDD falls below VBOR for less than TBOR, a RESET may not occur.

Once the brown-out occurs, the device will remain in Brown-out Reset until VDD rises above VBOR. The Power-up Timer then keeps the device in RESET for TPWRT (parameter #33, about 72mS). If VDD should fall below VBOR during TPWRT, the Brown-out Reset process will restart when VDD rises above VBOR with the Power-up Timer Reset. The Power-up Timer is always enabled when the Brown-out Reset circuit is enabled, regardless of the state of the PWRT configuration bit.

#### 12.8 Time-out Sequence

On power-up, the time-out sequence is as follows: The PWRT delay starts (if enabled) when a POR Reset occurs. Then OST starts counting 1024 oscillator cycles when PWRT ends (LP, XT, HS). When the OST ends, the device comes out of RESET.

If MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately. This is useful for testing purposes or to synchronize more than one PIC16F87X device operating in parallel.

Table 12-5 shows the RESET conditions for the STA-TUS, PCON and PC registers, while Table 12-6 shows the RESET conditions for all the registers.

# 12.9 Power Control/Status Register (PCON)

The Power Control/Status Register, PCON, has up to two bits depending upon the device.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent RESETS to see if bit BOR cleared, indicating a BOR occurred. When the Brown-out Reset is disabled, the state of the BOR bit is unpredictable and is, therefore, not valid at any time.

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

| Occillator Configuration | Power            | -up       | Brown-out        | Wake-up from<br>SLEEP |  |

|--------------------------|------------------|-----------|------------------|-----------------------|--|

| Oscillator Configuration | PWRTE = 0        | PWRTE = 1 | Brown-out        |                       |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc              |  |

| RC                       | 72 ms            |           | 72 ms            | _                     |  |

#### TABLE 12-3: TIME-OUT IN VARIOUS SITUATIONS

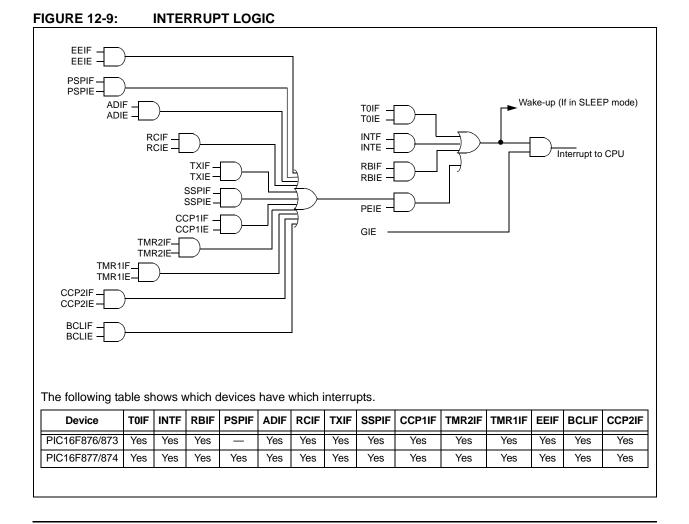

#### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

<sup>© 1998-2013</sup> Microchip Technology Inc.

## 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

#### 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

# 13.0 INSTRUCTION SET SUMMARY

Each PIC16F87X instruction is a 14-bit word, divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F87X instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                |

| PC    | Program Counter                                                                                                                                                                 |

| то    | Time-out bit                                                                                                                                                                    |

| PD    | Power-down bit                                                                                                                                                                  |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | То                                                                                | maintain     | upward | compatibility | with |  |  |  |  |

|-------|-----------------------------------------------------------------------------------|--------------|--------|---------------|------|--|--|--|--|

|       | future PIC16F87X products, <u>do not use</u> the<br>OPTION and TRIS instructions. |              |        |               |      |  |  |  |  |

|       | OF.                                                                               | I I ON and . |        |               |      |  |  |  |  |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                     |        |        |      |             |   |  |  |

|------------------------------------------------------------|--------|--------|------|-------------|---|--|--|

| 13                                                         | 8      | 7      | 6    |             | 0 |  |  |

| OPCODE                                                     |        | d      |      | f (FILE #)  |   |  |  |

| d = 0 for desi<br>d = 1 for desi                           |        |        |      |             |   |  |  |

| f = 7-bit file r                                           |        |        | dres | S           |   |  |  |

| Bit-oriented file reg                                      | •      | •      |      |             | _ |  |  |

| 13                                                         | 10     | 9      | 7    | 6           | 0 |  |  |

| OPCODE                                                     |        | b (Bl  | T #) | f (FILE #)  |   |  |  |

| b = 3-bit bit a<br>f = 7-bit file r<br>Literal and control | egiste | er ad  |      | S           |   |  |  |

| General                                                    |        |        |      |             |   |  |  |

| 13                                                         |        | 8      | 7    |             | 0 |  |  |

| OPCODE                                                     |        |        |      | k (literal) |   |  |  |

| k = 8-bit immediate value                                  |        |        |      |             |   |  |  |

| CALL and GOTO instructions only                            |        |        |      |             |   |  |  |

| 13 11                                                      | 10     |        |      |             | 0 |  |  |

| OPCODE                                                     |        |        | k (  | literal)    |   |  |  |

| k = 11-bit im                                              | media  | ate va | alue |             |   |  |  |

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# PIC16F87X

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                              |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                             |

| Status Affected: | None                                                                                                                                                                           |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>0, the result is placed in the W<br>register. If 'd' is 1, the result is<br>placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                            |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit lit-<br>eral 'k'. The result is placed in<br>the W register. |  |  |  |  |  |

# PIC16F87X

#### 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial) |        |                                           |                                                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                        |     |    |                                            |  |  |

|--------------------------------------------------------------|--------|-------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|--------------------------------------------|--|--|

| PIC16F87<br>PIC16F87<br>(Comme                               |        | /877-20                                   |                                                                              | ndard Operating Conditions (unless otherwise stated<br>erating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial<br>$0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercian |     |    |                                            |  |  |

| Param<br>No.                                                 | Symbol | Characteristic/<br>Device                 | Min Typ† Max Units Conditions                                                |                                                                                                                                                                                             |     |    |                                            |  |  |

| -                                                            | IPD    | Power-down Current <sup>(3,5)</sup>       |                                                                              |                                                                                                                                                                                             |     |    |                                            |  |  |

| D020                                                         |        | 16LF87X                                   | _                                                                            | 7.5                                                                                                                                                                                         | 30  | μΑ | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D020                                                         |        | 16F87X                                    |                                                                              | 10.5                                                                                                                                                                                        | 42  | μΑ | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021                                                         |        | 16LF87X                                   | _                                                                            | 0.9                                                                                                                                                                                         | 5   | μΑ | VDD = 3.0V, WDT enabled,<br>0°C to +70°C   |  |  |

| D021                                                         |        | 16F87X                                    | _                                                                            | 1.5                                                                                                                                                                                         | 16  | μΑ | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021A                                                        |        | 16LF87X                                   |                                                                              | 0.9                                                                                                                                                                                         | 5   | μΑ | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021A                                                        |        | 16F87X                                    | 1.5         19         μA         VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |                                                                                                                                                                                             |     |    |                                            |  |  |

| D023                                                         | ΔIBOR  | Brown-out<br>Reset Current <sup>(6)</sup> | _                                                                            | 85                                                                                                                                                                                          | 200 | μΑ | BOR enabled, VDD = 5.0V                    |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| DC CHA       | RACTE | RISTICS                                 | Operating         | i temp | erature | -40°C<br>0°C | hs (unless otherwise stated)<br>$S \le TA \le +85^{\circ}C$ for industrial<br>$S \le TA \le +70^{\circ}C$ for commercial<br>is described in DC specification |

|--------------|-------|-----------------------------------------|-------------------|--------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                          | Min               | Тур†   | Max     | Units        | Conditions                                                                                                                                                   |

|              | VIL   | Input Low Voltage                       |                   |        |         |              |                                                                                                                                                              |

|              |       | I/O ports                               |                   |        |         |              |                                                                                                                                                              |

| D030         |       | with TTL buffer                         | Vss               | —      | 0.15Vdd | V            | For entire VDD range                                                                                                                                         |

| D030A        |       |                                         | Vss               | —      | 0.8V    | V            | $4.5V \le VDD \le 5.5V$                                                                                                                                      |

| D031         |       | with Schmitt Trigger buffer             | Vss               | —      | 0.2Vdd  | V            |                                                                                                                                                              |

| D032         |       | MCLR, OSC1 (in RC mode)                 | Vss               | —      | 0.2Vdd  | V            |                                                                                                                                                              |

| D033         |       | OSC1 (in XT, HS and LP)                 | Vss               | —      | 0.3Vdd  | V            | (Note 1)                                                                                                                                                     |

|              |       | Ports RC3 and RC4                       |                   | —      |         |              |                                                                                                                                                              |

| D034         |       | with Schmitt Trigger buffer             | Vss               | —      | 0.3Vdd  | V            | For entire VDD range                                                                                                                                         |

| D034A        |       | with SMBus                              | -0.5              | —      | 0.6     | V            | for VDD = 4.5 to 5.5V                                                                                                                                        |

|              | Vih   | Input High Voltage                      |                   |        | r       |              | 1                                                                                                                                                            |

|              |       | I/O ports                               |                   | —      |         |              |                                                                                                                                                              |

| D040         |       | with TTL buffer                         | 2.0               | —      | Vdd     | -            | $4.5V \leq VDD \leq 5.5V$                                                                                                                                    |

| D040A        |       |                                         | 0.25VDD<br>+ 0.8V | _      | Vdd     | V            | For entire VDD range                                                                                                                                         |

| D041         |       | with Schmitt Trigger buffer             | 0.8Vdd            | —      | Vdd     | V            | For entire VDD range                                                                                                                                         |

| D042         |       | MCLR                                    | 0.8Vdd            | —      | Vdd     | V            |                                                                                                                                                              |

| D042A        |       | OSC1 (XT, HS and LP)                    | 0.7Vdd            | —      | Vdd     | V            | (Note 1)                                                                                                                                                     |

| D043         |       | OSC1 (in RC mode)<br>Ports RC3 and RC4  | 0.9Vdd            |        | Vdd     | V            |                                                                                                                                                              |

| D044         |       | with Schmitt Trigger buffer             | 0.7Vdd            | —      | Vdd     | V            | For entire VDD range                                                                                                                                         |

| D044A        |       | with SMBus                              | 1.4               | —      | 5.5     | V            | for VDD = 4.5 to 5.5V                                                                                                                                        |

| D070         | IPURB | PORTB Weak Pull-up Current              | 50                | 250    | 400     | μA           | VDD = 5V, VPIN = VSS,<br>-40°С то +85°С                                                                                                                      |

|              | lı∟   | Input Leakage Current <sup>(2, 3)</sup> |                   | •      |         |              |                                                                                                                                                              |

| D060         |       | I/O ports                               | —                 | —      | ±1      | μΑ           | $Vss \le VPIN \le VDD$ ,<br>Pin at hi-impedance                                                                                                              |

| D061         |       | MCLR, RA4/T0CKI                         | _                 | _      | ±5      | uΑ           | $Vss \leq VPIN \leq VDD$                                                                                                                                     |

| D063         |       | OSC1                                    | —                 | _      | ±5      | •            | $Vss \le VPIN \le VDD$ , XT, HS<br>and LP osc configuration                                                                                                  |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

# TABLE 15-12:PIC16F87X-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)PIC16F87X-10 (EXTENDED)PIC16F87X-20 (COMMERCIAL, INDUSTRIAL)PIC16LF87X-04 (COMMERCIAL, INDUSTRIAL)

| Param<br>No. | Sym   | Characteristic                              |          | Min         | Тур†       | Мах          | Units | Conditions                                                                                                  |

|--------------|-------|---------------------------------------------|----------|-------------|------------|--------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                                  |          | _           | _          | 10-bits      | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL   | Integral linearity error                    |          | _           | _          | < ± 1        | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                        |

| A04          | Edl   | Differential linearity err                  | or       | _           | _          | < ± 1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A06          | EOFF  | Offset error                                |          | _           | _          | < ± 2        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A07          | Egn   | Gain error                                  |          | _           | _          | < ± 1        | LSb   | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                        |

| A10          | _     | Monotonicity <sup>(3)</sup>                 |          | _           | guaranteed | _            | _     | $V\text{SS} \leq V\text{AIN} \leq V\text{REF}$                                                              |

| A20          | Vref  | Reference voltage (VREF+ - VREF-)           |          | 2.0         | _          | Vdd + 0.3    | V     | Absolute minimum electrical spec. To ensure 10-bit accuracy.                                                |

| A21          | Vref+ | Reference voltage High                      |          | AVDD - 2.5V |            | AVDD + 0.3V  | V     |                                                                                                             |

| A22          | VREF- | Reference voltage low                       |          | AVss - 0.3V |            | VREF+ - 2.0V | V     |                                                                                                             |

| A25          | VAIN  | Analog input voltage                        |          | Vss - 0.3 V | —          | Vref + 0.3 V | V     |                                                                                                             |

| A30          | Zain  | Recommended impeda<br>analog voltage source | ance of  | _           | —          | 10.0         | kΩ    |                                                                                                             |

| A40          | IAD   | A/D conversion                              | Standard | _           | 220        | _            | μΑ    | Average current consumption                                                                                 |

|              |       | current (VDD)                               | Extended | _           | 90         | _            | μΑ    | when A/D is on (Note 1)                                                                                     |

| A50          | IREF  | VREF input current <b>(No</b>               | te 2)    | 10          | _          | 1000         | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD<br>to VAIN to charge CHOLD, see<br>Section 11.1. |

|              |       |                                             |          | —           | —          | 10           | μA    | During A/D Conversion cycle                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage, and has no missing codes.

# 17.0 PACKAGING INFORMATION

# 17.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                    |

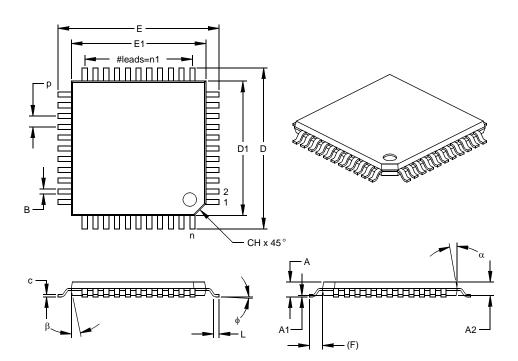

# 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units    | INCHES |      |      | MILLIMETERS* |       |       |

|--------------------------|----------|--------|------|------|--------------|-------|-------|

| Dimension                | n Limits | MIN    | NOM  | MAX  | MIN          | NOM   | MAX   |

| Number of Pins           | n        |        | 44   |      |              | 44    |       |

| Pitch                    | р        |        | .031 |      |              | 0.80  |       |

| Pins per Side            | n1       |        | 11   |      |              | 11    |       |

| Overall Height           | А        | .039   | .043 | .047 | 1.00         | 1.10  | 1.20  |

| Molded Package Thickness | A2       | .037   | .039 | .041 | 0.95         | 1.00  | 1.05  |

| Standoff §               | A1       | .002   | .004 | .006 | 0.05         | 0.10  | 0.15  |

| Foot Length              | L        | .018   | .024 | .030 | 0.45         | 0.60  | 0.75  |

| Footprint (Reference)    | (F)      |        | .039 |      | 1.00         |       |       |

| Foot Angle               | φ        | 0      | 3.5  | 7    | 0            | 3.5   | 7     |

| Overall Width            | Е        | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Overall Length           | D        | .463   | .472 | .482 | 11.75        | 12.00 | 12.25 |

| Molded Package Width     | E1       | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Molded Package Length    | D1       | .390   | .394 | .398 | 9.90         | 10.00 | 10.10 |

| Lead Thickness           | С        | .004   | .006 | .008 | 0.09         | 0.15  | 0.20  |

| Lead Width               | В        | .012   | .015 | .017 | 0.30         | 0.38  | 0.44  |

| Pin 1 Corner Chamfer     | СН       | .025   | .035 | .045 | 0.64         | 0.89  | 1.14  |

| Mold Draft Angle Top     | α        | 5      | 10   | 15   | 5            | 10    | 15    |

| Mold Draft Angle Bottom  | β        | 5      | 10   | 15   | 5            | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-026 Drawing No. C04-076

# APPENDIX C: CONVERSION CONSIDERATIONS

Considerations for converting from previous versions of devices to the ones listed in this data sheet are listed in Table C-1.

| TABLE C-1: | CONVERSION     |

|------------|----------------|

|            | CONSIDERATIONS |

| Characteristic    | PIC16C7X                                            | PIC16F87X                                                  |

|-------------------|-----------------------------------------------------|------------------------------------------------------------|

| Pins              | 28/40                                               | 28/40                                                      |

| Timers            | 3                                                   | 3                                                          |

| Interrupts        | 11 or 12                                            | 13 or 14                                                   |

| Communication     | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Slave) | PSP, USART,<br>SSP (SPI, I <sup>2</sup> C<br>Master/Slave) |

| Frequency         | 20 MHz                                              | 20 MHz                                                     |

| Voltage           | 2.5V - 5.5V                                         | 2.0V - 5.5V                                                |

| A/D               | 8-bit                                               | 10-bit                                                     |

| CCP               | 2                                                   | 2                                                          |

| Program<br>Memory | 4K, 8K<br>EPROM                                     | 4K, 8K<br>FLASH                                            |

| RAM               | 192, 368<br>bytes                                   | 192, 368<br>bytes                                          |

| EEPROM data       | None                                                | 128, 256<br>bytes                                          |

| Other             | _                                                   | In-Circuit<br>Debugger,<br>Low Voltage<br>Programming      |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:       | To: Technical Publications Manager Total Pa                                            | ges Sent           |

|-----------|----------------------------------------------------------------------------------------|--------------------|