Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876-20-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PIC <sup>®</sup> MCU Mid-Range Reference<br>Manual (DS33023) | PIC16F873               | PIC16F874               | PIC16F876               | PIC16F877               |

|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Operating Frequency                                                          | DC - 20 MHz             |

| RESETS (and Delays)                                                          | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) |

| FLASH Program Memory<br>(14-bit words)                                       | 4K                      | 4K                      | 8K                      | 8K                      |

| Data Memory (bytes)                                                          | 192                     | 192                     | 368                     | 368                     |

| EEPROM Data Memory                                                           | 128                     | 128                     | 256                     | 256                     |

| Interrupts                                                                   | 13                      | 14                      | 13                      | 14                      |

| I/O Ports                                                                    | Ports A,B,C             | Ports A,B,C,D,E         | Ports A,B,C             | Ports A,B,C,D,E         |

| Timers                                                                       | 3                       | 3                       | 3                       | 3                       |

| Capture/Compare/PWM Modules                                                  | 2                       | 2                       | 2                       | 2                       |

| Serial Communications                                                        | MSSP, USART             | MSSP, USART             | MSSP, USART             | MSSP, USART             |

| Parallel Communications                                                      | —                       | PSP                     | —                       | PSP                     |

| 10-bit Analog-to-Digital Module                                              | 5 input channels        | 8 input channels        | 5 input channels        | 8 input channels        |

| Instruction Set                                                              | 35 instructions         | 35 instructions         | 35 instructions         | 35 instructions         |

| Address               | Name                                                      | Bit 7                                                        | Bit 6                                                        | Bit 5         | Bit 4          | Bit 3        | Bit 2         | Bit 1          | Bit 0    | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|-----------------------|-----------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|---------------|----------------|--------------|---------------|----------------|----------|--------------------------|------------------------|

| Bank 2                |                                                           |                                                              |                                                              |               |                |              |               |                |          |                          |                        |

| 100h <sup>(3)</sup>   | INDF                                                      | Addressing                                                   | g this location                                              | n uses conte  | ents of FSR to | address data | a memory (no  | t a physical r | egister) | 0000 0000                | 27                     |

| 101h                  | TMR0                                                      | Timer0 Mo                                                    | dule Registe                                                 | er            |                |              |               |                |          | XXXX XXXX                | 47                     |

| 102h <sup>(3)</sup>   | PCL                                                       | Program C                                                    | Counter's (PC                                                | c) Least Sigr | nificant Byte  |              |               |                |          | 0000 0000                | 26                     |

| 103h <sup>(3)</sup>   | STATUS                                                    | IRP                                                          | RP1                                                          | RP0           | TO             | PD           | Z             | DC             | С        | 0001 1xxx                | 18                     |

| 104h <sup>(3)</sup>   | FSR                                                       | SR Indirect Data Memory Address Pointer                      |                                                              |               |                |              |               |                |          |                          |                        |

| 105h                  | _                                                         | Unimplem                                                     | ented                                                        |               |                |              |               |                |          |                          | _                      |

| 106h                  | PORTB PORTB Data Latch when written: PORTB pins when read |                                                              |                                                              |               |                |              |               |                |          | xxxx xxxx                | 31                     |

| 107h                  | — Unimplemented                                           |                                                              |                                                              |               |                |              |               |                |          | _                        | _                      |

| 108h                  | _                                                         | Unimplem                                                     | ented                                                        |               |                |              |               |                |          |                          | _                      |

| 109h                  | _                                                         | Unimplemented                                                |                                                              |               |                |              |               |                |          |                          | _                      |

| 10Ah <sup>(1,3)</sup> | PCLATH                                                    | _                                                            | — — Write Buffer for the upper 5 bits of the Program Counter |               |                |              |               |                |          |                          | 26                     |

| 10Bh <sup>(3)</sup>   | INTCON                                                    | GIE                                                          | GIE PEIE TOIE INTE RBIE TOIF INTF RBIF                       |               |                |              |               |                |          |                          | 20                     |

| 10Ch                  | EEDATA                                                    | EEPROM Data Register Low Byte                                |                                                              |               |                |              |               |                |          | xxxx xxxx                | 41                     |

| 10Dh                  | EEADR                                                     | EEPROM Address Register Low Byte                             |                                                              |               |                |              |               |                |          | xxxx xxxx                | 41                     |

| 10Eh                  | EEDATH                                                    | —                                                            | EEPROM Data Register High Byte                               |               |                |              |               |                |          |                          | 41                     |

| 10Fh                  | EEADRH                                                    | _                                                            | _                                                            |               | EEPROM A       | ddress Regis | ter High Byte |                |          | xxxx xxxx                | 41                     |

| Bank 3                |                                                           |                                                              |                                                              |               |                |              |               |                |          |                          |                        |

| 180h <sup>(3)</sup>   | INDF                                                      | Addressing                                                   | g this location                                              | n uses conte  | ents of FSR to | address data | a memory (no  | t a physical r | egister) | 0000 0000                | 27                     |

| 181h                  | OPTION_REG                                                | RBPU                                                         | INTEDG                                                       | TOCS          | T0SE           | PSA          | PS2           | PS1            | PS0      | 1111 1111                | 19                     |

| 182h <sup>(3)</sup>   | PCL                                                       | Program C                                                    | Counter (PC)                                                 | Least Signi   | ficant Byte    |              | •             |                |          | 0000 0000                | 26                     |

| 183h <sup>(3)</sup>   | STATUS                                                    | IRP                                                          | RP1                                                          | RP0           | TO             | PD           | Z             | DC             | С        | 0001 1xxx                | 18                     |

| 184h <sup>(3)</sup>   | FSR                                                       | Indirect Da                                                  | ata Memory A                                                 | Address Poir  | nter           |              |               |                |          | xxxx xxxx                | 27                     |

| 185h                  | _                                                         | Unimplem                                                     | ented                                                        |               |                |              |               |                |          |                          | _                      |

| 186h                  | TRISB                                                     | PORTB Da                                                     | ata Direction                                                | Register      |                |              |               |                |          | 1111 1111                | 31                     |

| 187h                  | _                                                         | Unimplem                                                     |                                                              |               |                |              |               |                |          |                          | _                      |

| 188h                  | —                                                         | Unimplem                                                     | ented                                                        |               |                |              |               |                |          | _                        |                        |

| 189h                  | —                                                         | Unimplemented                                                |                                                              |               |                |              |               |                |          | _                        |                        |

| 18Ah <sup>(1,3)</sup> | PCLATH                                                    | — — Write Buffer for the upper 5 bits of the Program Counter |                                                              |               |                |              |               |                |          | 0 0000                   | 26                     |

| 18Bh <sup>(3)</sup>   | INTCON                                                    | GIE                                                          | PEIE                                                         | T0IE          | INTE           | RBIE         | T0IF          | INTF           | RBIF     | 0000 000x                | 20                     |

| 18Ch                  | EECON1                                                    | EEPGD                                                        | —                                                            | RD            | x x000         | 41, 42       |               |                |          |                          |                        |

| 18Dh                  | EECON2                                                    | EEPROM                                                       | Control Regi                                                 | ster2 (not a  | physical regis | ster)        |               |                |          |                          | 41                     |

| 18Eh                  | —                                                         | Reserved                                                     | maintain clea                                                | ar            |                |              |               |                |          | 0000 0000                | _                      |

| 18Fh                  | _                                                         | Reserved                                                     | maintain clea                                                | ar            |                |              |               |                |          | 0000 0000                | _                      |

| TABLE 2-1: | SPECIAL FUNCTION REGISTER SUMMARY | (CONTINUED) | ) |

|------------|-----------------------------------|-------------|---|

|------------|-----------------------------------|-------------|---|

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose

contents are transferred to the upper byte of the program counter. 2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                                                              | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|--|--|--|--|

|               | GIE                                                                                                                | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |  |  |  |  |

|               | bit 7                                                                                                              |                               |               |              |                  |             |                | bit 0      |  |  |  |  |

|               |                                                                                                                    |                               |               |              |                  |             |                |            |  |  |  |  |

| bit 7         | GIE: Globa                                                                                                         | al Interrupt E                | nable bit     |              |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    | s all unmas                   |               | ots          |                  |             |                |            |  |  |  |  |

| <b>h</b> :+ C |                                                                                                                    | es all interru                |               | L:4          |                  |             |                |            |  |  |  |  |

| bit 6         | -                                                                                                                  | pheral Interr                 | •             |              | -                |             |                |            |  |  |  |  |

|               | <ul> <li>1 = Enables all unmasked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul> |                               |               |              |                  |             |                |            |  |  |  |  |

| bit 5         | T0IE: TMR0 Overflow Interrupt Enable bit                                                                           |                               |               |              |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    | s the TMR0                    |               |              |                  |             |                |            |  |  |  |  |

|               | 0 = Disable                                                                                                        | es the TMR                    | ) interrupt   |              |                  |             |                |            |  |  |  |  |

| bit 4         |                                                                                                                    | /INT Externa                  | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |  |  |  |  |

| bit 3         |                                                                                                                    | Port Change                   |               | •            |                  |             |                |            |  |  |  |  |

| bit 0         |                                                                                                                    | s the RB po                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    | es the RB po                  |               |              |                  |             |                |            |  |  |  |  |

| bit 2         | TOIF: TMR                                                                                                          | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    |                               |               |              | eared in softwa  | re)         |                |            |  |  |  |  |

|               |                                                                                                                    | register did                  |               |              |                  |             |                |            |  |  |  |  |

| bit 1         |                                                                                                                    | /INT Externa                  | •             | •            |                  | 1           | >              |            |  |  |  |  |

|               |                                                                                                                    | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |  |  |  |  |

| bit 0         |                                                                                                                    | Port Change                   | •             |              |                  |             |                |            |  |  |  |  |

|               |                                                                                                                    | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |  |  |  |  |

|               |                                                                                                                    | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |  |  |  |  |

|               |                                                                                                                    | be cleared in<br>of the RB7:R | ,             | ve changed   | stato            |             |                |            |  |  |  |  |

|               |                                                                                                                    |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |  |  |  |  |

|               | Legend:                                                                                                            |                               |               |              |                  |             |                |            |  |  |  |  |

|               | R = Reada                                                                                                          | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |  |  |  |  |

|               | - n = Value                                                                                                        |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |  |  |  |  |

|               |                                                                                                                    |                               |               |              |                  |             |                | -          |  |  |  |  |

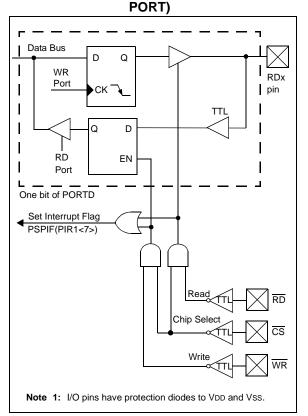

#### 3.6 Parallel Slave Port

The Parallel Slave Port (PSP) is not implemented on the PIC16F873 or PIC16F876.

PORTD operates as an 8-bit wide Parallel Slave Port or microprocessor port, when control bit PSPMODE (TRISE<4>) is set. In Slave mode, it is asynchronously readable and writable by the external world through RD control input pin RE0/RD and WR control input pin RE1/WR.

The PSP can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG3:PCFG0 (ADCON1<3:0>) must be set to configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches: one for data output, and one for data input. The user writes 8-bit data to the PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the external device is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), the Input Buffer Full (IBF) status flag bit (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 3-10). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The Input Buffer Overflow (IBOV) status flag bit (TRISE<5>) is set if a second write to the PSP is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the CS and RD lines are first detected low. The Output Buffer Full (OBF) status flag bit (TRISE<6>) is cleared immediately (Figure 3-11), indicating that the PORTD latch is waiting to be read by the external bus. When either the CS or RD pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware. When not in PSP mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE

| TABLE 5-1: | <b>REGISTERS ASSOCIATED WITH TIMER0</b> |

|------------|-----------------------------------------|

|------------|-----------------------------------------|

| Address               | Name       | Bit 7  | Bit 6                    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|------------|--------|--------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 01h,101h              | TMR0       | Timer0 | Timer0 Module's Register |       |       |       |       |       |       | XXXX XXXX                | uuuu uuuu                       |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE                     | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                       |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG                   | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### **REGISTER 9-2:** SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL SSPOV SSPM0 SSPEN CKP SSPM3 SSPM2 SSPM1 bit 7 bit 0 bit 7 WCOL: Write Collision Detect bit Master mode: 1 = A write to SSPBUF was attempted while the I2C conditions were not valid 0 = No collision Slave mode: 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software) 0 = No collision bit 6 SSPOV: Receive Overflow Indicator bit In SPI mode: 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.) 0 = No overflowIn I<sup>2</sup>C mode: 1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.) 0 = No overflowSSPEN: Synchronous Serial Port Enable bit bit 5 In SPI mode, When enabled, these pins must be properly configured as input or output 1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins In I<sup>2</sup>C mode, When enabled, these pins must be properly configured as input or output 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins bit 4 CKP: Clock Polarity Select bit In SPI mode: 1 = Idle state for clock is a high level 0 = Idle state for clock is a low level In I<sup>2</sup>C Slave mode: SCK release control 1 = Enable clock 0 = Holds clock low (clock stretch). (Used to ensure data setup time.) In I<sup>2</sup>C Master mode: Unused in this mode bit 3-0 SSPM3:SSPM0: Synchronous Serial Port Mode Select bits 0000 = SPI Master mode, clock = Fosc/4 0001 = SPI Master mode, clock = Fosc/16 0010 = SPI Master mode, clock = Fosc/64 0011 = SPI Master mode, clock = TMR2 output/2 0100 = SPI Slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled. 0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin. $0110 = I^2C$ Slave mode, 7-bit address $0111 = I^2C$ Slave mode, 10-bit address 1000 = I<sup>2</sup>C Master mode, clock = Fosc / (4 \* (SSPADD+1)) $1011 = I^2C$ Firmware Controlled Master mode (slave idle) 1110 = I<sup>2</sup>C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled 1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled 1001, 1010, 1100, 1101 = Reserved

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

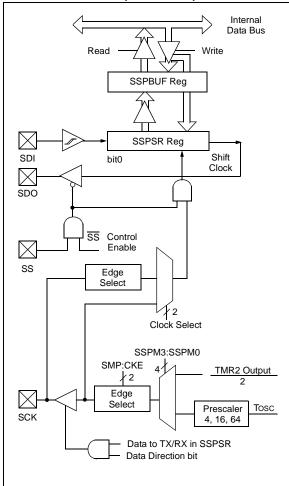

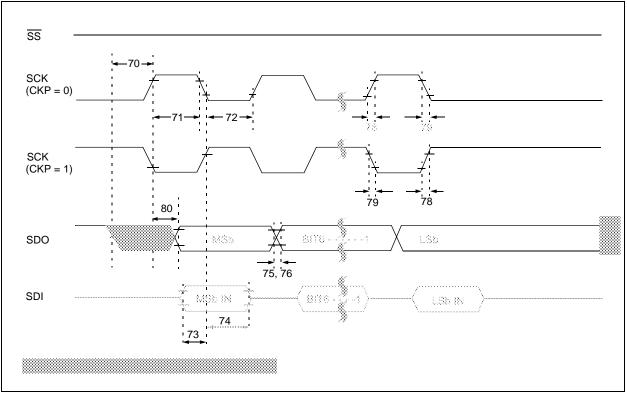

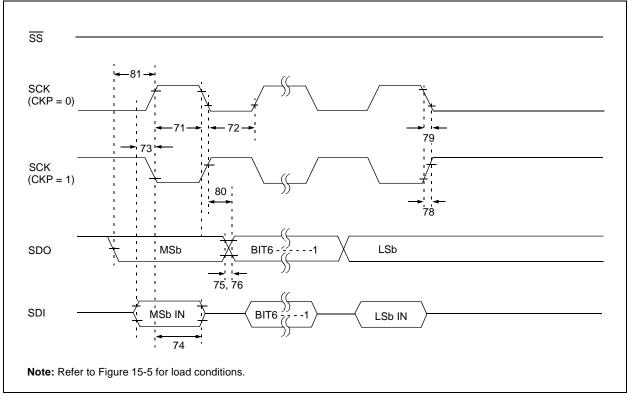

### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

#### TABLE 9-1: REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6      | Bit 5      | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on:<br>MCLR, WDT |

|------------------------|---------|----------------------|------------|------------|---------|-----------|-------------|--------|--------|-----------------------|------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE       | TOIE       | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 000x             | 0000 000u              |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF       | RCIF       | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 0000             | 0000 0000              |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE       | RCIE       | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 0000             | 0000 0000              |

| 13h                    | SSPBUF  | Synchrono            | ous Serial | Port Recei | ve Buff | er/Transm | it Register |        |        | xxxx xxxx             | uuuu uuuu              |

| 14h                    | SSPCON  | WCOL                 | SSPOV      | SSPEN      | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 0000             | 0000 0000              |

| 94h                    | SSPSTAT | SMP                  | CKE        | D/A        | Р       | S         | R/W         | UA     | BF     | 0000 0000             | 0000 0000              |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode. **Note 1:** These bits are reserved on PCI16F873/876 devices; always maintain these bits clear.

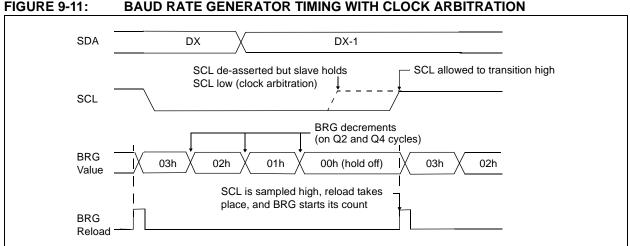

#### BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

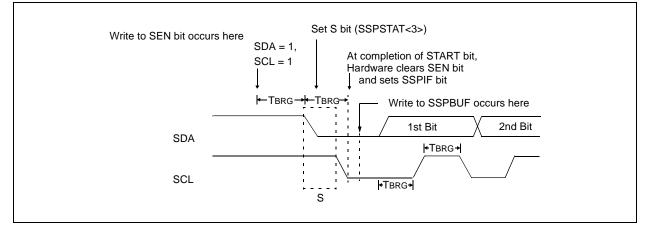

#### 9.2.9 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the START condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out (TBRG), the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the START condition, and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (TBRG), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware. The baud rate generator is suspended, leaving the SDA line held low, and the START condition is complete.

Note: If, at the beginning of START condition, the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

#### 9.2.9.1 WCOL Status Flag

If the user writes the SSPBUF when a START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

#### **FIGURE 9-12:** FIRST START BIT TIMING

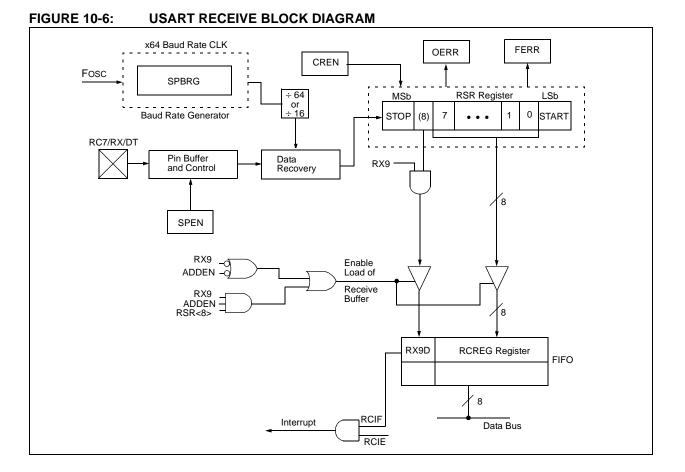

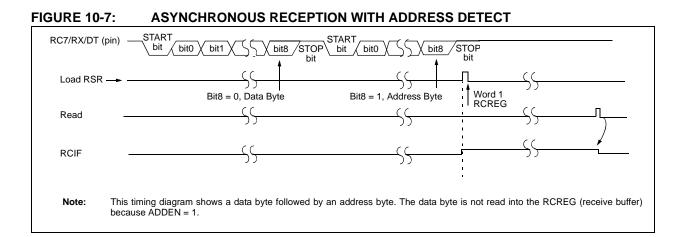

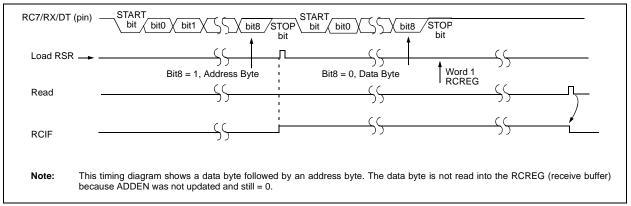

## 10.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

When setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

#### FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name                                  | Bit 7                | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|---------------------------------------|----------------------|----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                | GIE                  | PEIE     | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                    | PIR1                                  | PSPIF <sup>(1)</sup> | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                 | SPEN                 | RX9      | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG                                 | USART Re             | ceive Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                  | PSPIE <sup>(1)</sup> | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                 | CSRC                 | TX9      | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | 9h SPBRG Baud Rate Generator Register |                      |          |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth

receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name                                   | Bit 7                | Bit 6     | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|----------------------------------------|----------------------|-----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON                                 | GIE                  | PEIE      | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA                                  | SPEN                 | RX9       | SREN   | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG                                  | USART R              | eceive Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA                                  | CSRC                 | TX9       | TXEN   | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | 99h SPBRG Baud Rate Generator Register |                      |           |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# TABLE 12-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq. | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|------------------|------------------|------------------|

| LP       | 32 kHz           | 33 pF            | 33 pF            |

|          | 200 kHz          | 15 pF            | 15 pF            |

| XT       | 200 kHz          | 47-68 pF         | 47-68 pF         |

|          | 1 MHz            | 15 pF            | 15 pF            |

|          | 4 MHz            | 15 pF            | 15 pF            |

| HS       | 4 MHz            | 15 pF            | 15 pF            |

|          | 8 MHz            | 15-33 pF         | 15-33 pF         |

|          | 20 MHz           | 15-33 pF         | 15-33 pF         |

**These values are for design guidance only.** See notes following this table.

| Crystals Used |                            |          |  |  |  |  |

|---------------|----------------------------|----------|--|--|--|--|

| 32 kHz        | Epson C-001R32.768K-A      | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz         | ± 20 PPM |  |  |  |  |

| 1 MHz         | ECS ECS-10-13-1            | ± 50 PPM |  |  |  |  |

| 4 MHz         | ECS ECS-40-20-1            | ± 50 PPM |  |  |  |  |

| 8 MHz         | EPSON CA-301 8.000M-C      | ± 30 PPM |  |  |  |  |

| 20 MHz        | EPSON CA-301 20.000M-<br>C | ± 30 PPM |  |  |  |  |

- **Note 1:** Higher capacitance increases the stability of oscillator, but also increases the startup time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- R<sub>s</sub> may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

- 4: When migrating from other PIC<sup>®</sup> MCU devices, oscillator performance should be verified.

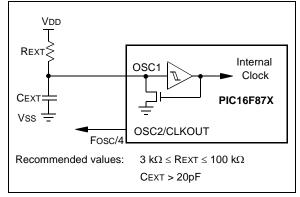

### 12.2.3 RC OSCILLATOR

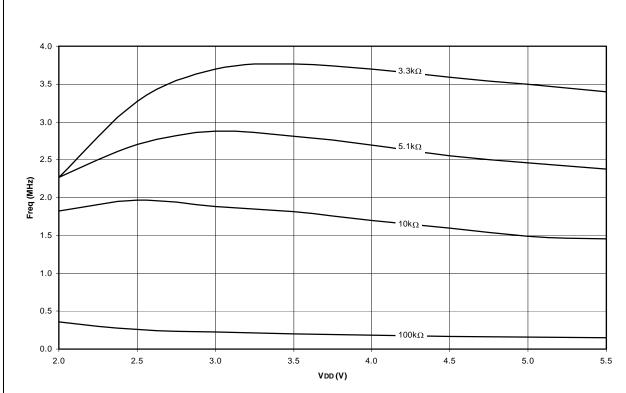

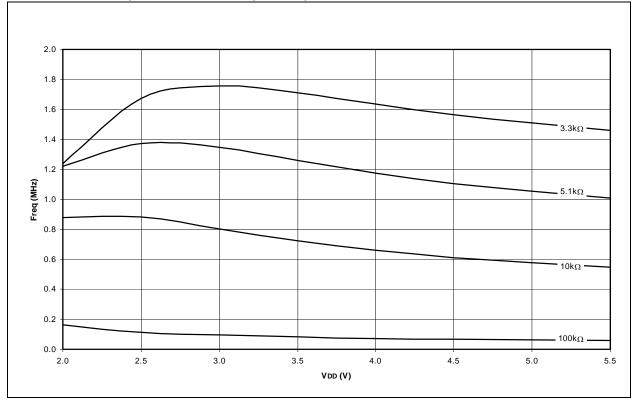

For timing insensitive applications, the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 12-3 shows how the R/C combination is connected to the PIC16F87X.

## 13.0 INSTRUCTION SET SUMMARY

Each PIC16F87X instruction is a 14-bit word, divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16F87X instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| ТО    | Time-out bit                                                                                                                                                                      |

| PD    | Power-down bit                                                                                                                                                                    |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | То                                           | maintain upward |  | compatibility | with |  |  |  |

|-------|----------------------------------------------|-----------------|--|---------------|------|--|--|--|

|       | future PIC16F87X products, <u>do not use</u> |                 |  |               |      |  |  |  |

|       | OPTION and TRIS instructions.                |                 |  |               |      |  |  |  |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file r                                 | egist  | er op   | eratio | ons         |   |

|------------------------------------------------------|--------|---------|--------|-------------|---|

| 13                                                   | 8      | 7       | 6      |             | 0 |

| OPCODE                                               |        | d       |        | f (FILE #)  |   |

| d = 0 for dest<br>d = 1 for dest<br>f = 7-bit file r | tinati | on f    | dres   | s           |   |

| Bit-oriented file reg                                | jister | oper    | ation  | s           |   |

| 13                                                   | 10     | 9       | 7      | 6           | 0 |

| OPCODE                                               |        | b (Bl   | T #)   | f (FILE #)  |   |

| f = 7-bit file r<br>Literal and control<br>General   | U      |         |        | -           |   |

| 13                                                   |        | 8       | 7      |             | 0 |

| OPCODE                                               |        |         |        | k (literal) |   |

| k = 8-bit imm                                        |        |         |        |             |   |

| 13 11                                                | 10     |         |        |             | 0 |

| OPCODE                                               |        |         | k (    | literal)    |   |

| k = 11-bit im                                        | medi   | iate va | alue   |             |   |

A description of each instruction is available in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

# PIC16F87X

|                         |                                  | >                                | >         >         >                                              |                                                                                                                                             |                                          |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   | >                                 | >                      | >                                      | >                                  | >                                                 | >                                                   | _                           |

|-------------------------|----------------------------------|----------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------|------------------------------------------------------|---------------------------------------------|-----------------------------------------------|----------------------------------|----------------------------------|-------------------------------------------------|-----------------------------------|-----------------------------------|------------------------|----------------------------------------|------------------------------------|---------------------------------------------------|-----------------------------------------------------|-----------------------------|

|                         | +                                | >                                | · · ·                                                              | >                                                                                                                                           |                                          |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   | >                                 | >                      |                                        |                                    |                                                   |                                                     |                             |

|                         | +                                | >                                | <b>`</b>                                                           | >                                                                                                                                           |                                          |                                | >                                                    |                                             |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         | +                                | >                                | >                                                                  | >                                                                                                                                           |                                          |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         | +                                |                                  |                                                                    |                                                                                                                                             |                                          |                                |                                                      |                                             |                                               | >                                |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         | >                                |                                  | >                                                                  | >                                                                                                                                           |                                          |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 | >                                 |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  |                                                                    | 1                                                                                                                                           |                                          |                                | >                                                    | >                                           | >                                             |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           |                                               |                                  | >                                |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         | -                                |                                  | >                                                                  | >                                                                                                                                           |                                          | >                              | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           | >                                             |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        | *                              | >                                                    | >                                           | ÷,                                            | ≁                                |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | **/                                                                                                                                         |                                          |                                | **/                                                  | **/                                         |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           | >                                             |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        | *                              | >                                                    | >                                           |                                               | ÷,                               |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           | >                                             |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           |                                          |                                | >                                                    | >                                           |                                               |                                  |                                  | `                                               |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

|                         |                                  |                                  | >                                                                  | >                                                                                                                                           | >                                        |                                | >                                                    | >                                           |                                               |                                  |                                  |                                                 |                                   |                                   |                        |                                        |                                    |                                                   |                                                     |                             |

| MDI A B® C17 C Commiler | PLAB <sup>®</sup> C17 C Compiler | PLAB <sup>®</sup> C18 C Compiler | PASM <sup>TM</sup> Assembler/<br>PLINK <sup>TM</sup> Object Linker | MPLAB <sup>®</sup> ICE In-Circuit Emulator                                                                                                  | ICEPIC <sup>TM</sup> In-Circuit Emulator | PLAB®ICD In-Circuit<br>ebugger | PICSTART® Plus Entry Level<br>Development Programmer | PRO MATE® II<br>Universal Device Programmer | PICDEM <sup>TM</sup> 1 Demonstration<br>Board | PICDEM™ 2 Demonstration<br>Board | PICDEM™ 3 Demonstration<br>Board | PICDEM <sup>TM</sup> 14A Demonstration<br>Board | PICDEM™ 17 Demonstration<br>Board | EELoo <sup>®</sup> Evaluation Kit | EELoo® Transponder Kit | iicrolD <sup>TM</sup> Programmer's Kit | ts κHz microlD'™<br>eveloper's Kit | 125 kHz Anticollision microlD™<br>Developer's Kit | 13.56 MHz Anticollision<br>microlD™ Developer's Kit | MCP2510 CAN Developer's Kit |