Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876-20i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                             |     |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                         | 11  |

| 3.0   | I/O Ports                                                                   |     |

| 4.0   | Data EEPROM and FLASH Program Memory                                        | 41  |

| 5.0   | Timer0 Module                                                               |     |

| 6.0   | Timer1 Module                                                               |     |

| 7.0   | Timer2 Module                                                               |     |

| 8.0   | Capture/Compare/PWM Modules                                                 |     |

| 9.0   | Master Synchronous Serial Port (MSSP) Module                                |     |

| 10.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 11.0  | Analog-to-Digital Converter (A/D) Module                                    | 111 |

| 12.0  | Special Features of the CPU                                                 | 119 |

| 13.0  | Instruction Set Summary                                                     | 135 |

|       | Development Support                                                         |     |

|       | Electrical Characteristics                                                  |     |

| 16.0  | DC and AC Characteristics Graphs and Tables                                 | 177 |

| 17.0  | Packaging Information                                                       | 189 |

| Appe  | ndix A: Revision History                                                    | 197 |

| Appe  | ndix B: Device Differences                                                  | 197 |

|       | ndix C: Conversion Considerations                                           |     |

| Index | (                                                                           | 199 |

|       | ine Support                                                                 |     |

| Read  | ler Response                                                                | 208 |

| PIC1  | 6F87X Product Identification System                                         | 209 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| FI | GU | IRF | 2-3      | - |

|----|----|-----|----------|---|

|    |    |     | <u> </u> |   |

### PIC16F877/876 REGISTER FILE MAP

| Indirect addr.(*)              | 00h        | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 18              |

|--------------------------------|------------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----------------|

| TMR0                           | 01h        | OPTION_REG                                 | 81h        | TMR0                                       | 101h         | OPTION_REG                                 | 18              |

| PCL                            | 02h        | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182             |

| STATUS                         | 03h        | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183             |

| FSR                            | 04h        | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184             |

| PORTA                          | 05h        | TRISA                                      | 85h        |                                            | 105h         |                                            | 18              |

| PORTB                          | 06h        | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186             |

| PORTC                          | 07h        | TRISC                                      | 87h        |                                            | 107h         |                                            | 187             |

| PORTD <sup>(1)</sup>           | 08h        | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188             |

| PORTE <sup>(1)</sup>           | 09h        | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h         |                                            | 189             |

| PCLATH                         | 0Ah        | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18/             |

| INTCON                         | 0Bh        | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18              |

| PIR1                           | 0Ch        | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch         | EECON1                                     | 180             |

| PIR2                           | 0Dh        | PIE2                                       | 8Dh        | EEADR                                      | 10Dh         | EECON2                                     | 181             |

| TMR1L                          | 0Eh        | PCON                                       | 8Eh        | EEDATH                                     | 10Eh         | Reserved <sup>(2)</sup>                    | 18              |

| TMR1H                          | 0Fh        |                                            | 8Fh        | EEADRH                                     | 10Fh         | Reserved <sup>(2)</sup>                    | 18              |

| T1CON                          | 10h        |                                            | 90h        |                                            | 110h         |                                            | 190             |

| TMR2                           | 11h        | SSPCON2                                    | 91h        |                                            | 111h         |                                            | 19 <sup>.</sup> |

| T2CON                          | 12h        | PR2                                        | 92h        |                                            | 112h         |                                            | 192             |

| SSPBUF                         | 13h        | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193             |

| SSPCON                         | 14h        | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194             |

| CCPR1L                         | 15h        |                                            | 95h        |                                            | 115h         |                                            | 19              |

| CCPR1H                         | 16h        |                                            | 96h        |                                            | 116h         |                                            | 196             |

| CCP1CON                        | 17h        |                                            | 97h        | General                                    | 117h         | General                                    | 197             |

| RCSTA                          | 18h        | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198             |

| TXREG                          | 19h        | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199             |

| RCREG                          | 1Ah        |                                            | 9Ah        | -                                          | 11Ah         |                                            | 19/             |

| CCPR2L                         | 1Bh        |                                            | 9Bh        |                                            | 11Bh         |                                            | 198             |

| CCPR2H                         | 1Ch        |                                            | 9Ch        |                                            | 11Ch         |                                            | 190             |

| CCP2CON                        | 1Dh        |                                            | 9Dh        |                                            | 11Dh         |                                            | 19[             |

| ADRESH                         | 1Eh        | ADRESL                                     | 9Eh        |                                            | 11Eh         |                                            | 19              |

| ADCON0                         | 1Fh        | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 191             |

|                                | 20h        |                                            | A0h        |                                            | 120h         |                                            | 1A              |

| General<br>Purpose<br>Register |            | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |                 |

| 96 Bytes                       |            | UU Dyico                                   | EFh        | 00 Dytos                                   | 16Fh         | 00 Dyi00                                   | 1EI             |

|                                | 7Fh        | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | 1F(<br>1Fl      |

| Bank 0                         |            | Bank 1                                     | FFII       | Bank 2                                     | /. !!        | Bank 3                                     | 11.1            |

| 1 1 m 1 m m 1                  | بارار منعم | a memory location                          | a          | . 101                                      |              |                                            |                 |

2: These registers are reserved, maintain these registers clear.

#### 2.2.2.3 INTCON Register

The INTCON Register is a readable and writable register, which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. **Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

|               | R/W-0                                                                             | R/W-0                         | R/W-0         | R/W-0        | R/W-0            | R/W-0       | R/W-0          | R/W-x      |

|---------------|-----------------------------------------------------------------------------------|-------------------------------|---------------|--------------|------------------|-------------|----------------|------------|

|               | GIE                                                                               | PEIE                          | T0IE          | INTE         | RBIE             | T0IF        | INTF           | RBIF       |

|               | bit 7                                                                             |                               |               |              |                  |             |                | bit 0      |

|               |                                                                                   |                               |               |              |                  |             |                |            |

| bit 7         | GIE: Globa                                                                        | al Interrupt E                | nable bit     |              |                  |             |                |            |

|               |                                                                                   | s all unmas                   |               | ots          |                  |             |                |            |

| <b>h</b> :+ C |                                                                                   | es all interru                |               | L:4          |                  |             |                |            |

| bit 6         | -                                                                                 | pheral Interr                 | •             |              | -                |             |                |            |

|               |                                                                                   | s all unmas                   |               | •            | 5                |             |                |            |

| bit 5         |                                                                                   | 0 Overflow                    | =             |              |                  |             |                |            |

|               |                                                                                   | s the TMR0                    |               |              |                  |             |                |            |

|               | 0 = Disable                                                                       | es the TMR                    | ) interrupt   |              |                  |             |                |            |

| bit 4         |                                                                                   | /INT Externa                  | •             |              |                  |             |                |            |

|               |                                                                                   | es the RB0/II<br>es the RB0/I |               |              |                  |             |                |            |

| bit 3         |                                                                                   | Port Change                   |               | •            |                  |             |                |            |

| bit 0         |                                                                                   | s the RB po                   | •             |              |                  |             |                |            |

|               |                                                                                   | es the RB po                  |               |              |                  |             |                |            |

| bit 2         | TOIF: TMR                                                                         | 0 Overflow I                  | Interrupt Fla | ag bit       |                  |             |                |            |

|               |                                                                                   |                               |               |              | eared in softwa  | re)         |                |            |

|               |                                                                                   | register did                  |               |              |                  |             |                |            |

| bit 1         |                                                                                   | /INT Externa                  | •             | •            |                  | 1           | >              |            |

|               |                                                                                   | 30/INT exter                  | •             | •            | must be cleared  | a in softwa | re)            |            |

| bit 0         |                                                                                   | Port Change                   | •             |              |                  |             |                |            |

|               |                                                                                   | •                             | •             | •            | l state; a misma | tch conditi | ion will cont  | nue to set |

|               |                                                                                   | •                             |               | nd the mism  | atch condition a | and allow t | he bit to be   | cleared    |

|               | (must be cleared in software).<br>0 = None of the RB7:RB4 pins have changed state |                               |               |              |                  |             |                |            |

|               |                                                                                   |                               | una hiris ila | e changeu    | SIGIE            |             |                |            |

|               | Legend:                                                                           |                               |               |              |                  |             |                |            |

|               | R = Reada                                                                         | ble bit                       | VV = V        | Vritable bit | U = Unimpl       | emented b   | oit, read as ' | 0'         |

|               | - n = Value                                                                       |                               |               | Bit is set   | '0' = Bit is c   |             | x = Bit is u   |            |

|               |                                                                                   |                               |               |              |                  |             |                | -          |

| Name                   | Bit# | Buffer                | Function                                                                                                                                          |

|------------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                                                        |

| RB1                    | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB2                    | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                                                    |

| RB3/PGM <sup>(3)</sup> | bit3 | TTL                   | Input/output pin or programming pin in LVP mode. Internal software programmable weak pull-up.                                                     |

| RB4                    | bit4 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB5                    | bit5 | TTL                   | Input/output pin (with interrupt-on-change). Internal software programmable weak pull-up.                                                         |

| RB6/PGC                | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming clock. |

| RB7/PGD                | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt-on-change) or In-Circuit Debugger pin.<br>Internal software programmable weak pull-up. Serial programming data.  |

#### TABLE 3-3: PORTB FUNCTIONS

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** Low Voltage ICSP Programming (LVP) is enabled by default, which disables the RB3 I/O function. LVP must be disabled to enable RB3 as an I/O pin and allow maximum compatibility to the other 28-pin and 40-pin mid-range devices.

#### TABLE 3-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address   | Name       | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------|------------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 06h, 106h | PORTB      | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | XXXX XXXX                | uuuu uuuu                       |

| 86h, 186h | TRISB      | PORTB | PORTB Data Direction Register |       |       |       |       |       |       | 1111 1111                | 1111 1111                       |

| 81h, 181h | OPTION_REG | RBPU  | INTEDG                        | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

#### 4.9 FLASH Program Memory Write Protection

The configuration word contains a bit that write protects the FLASH program memory, called WRT. This bit can only be accessed when programming the PIC16F87X device via ICSP. Once write protection is enabled, only an erase of the entire device will disable it. When enabled, write protection prevents any writes to FLASH program memory. Write protection does not affect program memory reads.

#### TABLE 4-1: READ/WRITE STATE OF INTERNAL FLASH PROGRAM MEMORY

| Со  | nfiguration | Bits | Manageral          | Internal | Internal |           |            |

|-----|-------------|------|--------------------|----------|----------|-----------|------------|

| CP1 | CP0         | WRT  | Memory Location    | Read     | Write    | ICSP Read | ICSP Write |

| 0   | 0           | x    | All program memory | Yes      | No       | No        | No         |

| 0   | 1           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 0   | 1           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 0   | 1           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 0   | 1           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 0    | Unprotected areas  | Yes      | No       | Yes       | No         |

| 1   | 0           | 0    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 0           | 1    | Unprotected areas  | Yes      | Yes      | Yes       | No         |

| 1   | 0           | 1    | Protected areas    | Yes      | No       | No        | No         |

| 1   | 1           | 0    | All program memory | Yes      | No       | Yes       | Yes        |

| 1   | 1           | 1    | All program memory | Yes      | Yes      | Yes       | Yes        |

| TABLE 4-2: | REGISTERS ASSOCIATED WITH DATA EEPROM/PROGRAM FLASH |

|------------|-----------------------------------------------------|

|            |                                                     |

| Address                 | Name   | Bit 7  | Bit 6                                              | Bit 5       | Bit 4     | Bit 3        | Bit 2     | Bit 1 | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-------------------------|--------|--------|----------------------------------------------------|-------------|-----------|--------------|-----------|-------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh, 18Bh | INTCON | GIE    | PEIE                                               | TOIE        | INTE      | RBIE         | TOIF      | INTF  | RBIF   | 0000 000x                | 0000 000u                       |

| 10Dh                    | EEADR  | EEPRON | Address                                            | s Register  | , Low Byt | е            |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Fh                    | EEADRH | —      | —                                                  | —           | EEPRON    | Address,     | High Byte | )     |        | xxxx xxxx                | uuuu uuuu                       |

| 10Ch                    | EEDATA | EEPRON | l Data Re                                          | egister, Lo | w Byte    |              |           |       |        | xxxx xxxx                | uuuu uuuu                       |

| 10Eh                    | EEDATH | —      | —                                                  | EEPRO       | M Data Re | egister, Hig | h Byte    |       |        | xxxx xxxx                | uuuu uuuu                       |

| 18Ch                    | EECON1 | EEPGD  | _                                                  | _           | —         | WRERR        | WREN      | WR    | RD     | x x000                   | x u000                          |

| 18Dh                    | EECON2 | EEPRON | EEPROM Control Register2 (not a physical register) |             |           |              |           |       |        | _                        | _                               |

| 8Dh                     | PIE2   | —      | (1)                                                |             | EEIE      | BCLIE        | —         | _     | CCP2IE | -r-0 00                  | -r-0 00                         |

| 0Dh                     | PIR2   | _      | (1)                                                | _           | EEIF      | BCLIF        | _         | _     | CCP2IF | -r-0 00                  | -r-0 00                         |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

Note 1: These bits are reserved; always maintain these bits clear.

### 6.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt-on-overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 6.4.1).

In Asynchronous Counter mode, Timer1 cannot be used as a time-base for capture or compare operations.

#### 6.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

## 6.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator, rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for use with a 32 kHz crystal. Table 6-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 6-1:CAPACITOR SELECTION FOR<br/>THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                    | Freq.                          | C2           |           |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------|-----------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                          | 32 kHz                         | 33 pF        | 33 pF     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 100 kHz                        | 15 pF        | 15 pF     |  |  |  |  |

|                                                                                                                                                                                                                                                                                                             | 200 kHz                        | 15 pF        | 15 pF     |  |  |  |  |

| These va                                                                                                                                                                                                                                                                                                    | lues are for o                 | design guida | nce only. |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                            |                                |              |           |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                  | Epson C-001R32.768K-A ± 20 PP  |              |           |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                     | Epson C-2 100.00 KC-P ± 20 PPN |              |           |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                     | STD XTL                        | 200.000 kHz  | ± 20 PPM  |  |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                |              |           |  |  |  |  |

### 6.6 Resetting Timer1 using a CCP Trigger Output

If the CCP1 or CCP2 module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer1 is running in Asynchronous Counter mode, this RESET operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL register pair effectively becomes the period register for Timer1.

#### 6.7 Resetting of Timer1 Register Pair (TMR1H, TMR1L)

TMR1H and TMR1L registers are not reset to 00h on a POR, or any other RESET, except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset, or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other RESETS, the register is unaffected.

#### 6.8 Timer1 Prescaler

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

### TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

| Address                | Name   | Bit 7                | Bit 6          | Bit 5     | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------------|-----------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON | GIE                  | PEIE           | TOIE      | INTE      | RBIE      | T0IF   | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF           | RCIF      | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE           | RCIE      | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh                    | TMR1L  | Holding R            |                | xxxx xxxx | uuuu uuuu |           |        |        |        |                          |                                 |

| 0Fh                    | TMR1H  | Holding R            | egister for th |           | xxxx xxxx | uuuu uuuu |        |        |        |                          |                                 |

| 10h                    | T1CON  | —                    | —              | T1CKPS1   | T1CKPS0   | T1OSCEN   | T1SYNC | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

# PIC16F87X

#### 8.3.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

#### TABLE 8-3: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1        | 1         | 1         |

| PR2 Value                  | 0xFFh    | 0xFFh    | 0xFFh     | 0x3Fh    | 0x1Fh     | 0x17h     |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8        | 7         | 5.5       |

#### TABLE 8-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address                | Name    | Bit 7                | Bit 6       | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1    | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |  |

|------------------------|---------|----------------------|-------------|--------------|---------------|---------------|------------|----------|--------|--------------------------|---------------------------------|--|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE        | TOIE         | INTE          | RBIE          | TOIF       | INTF     | RBIF   | 0000 000x                | 0000 000u                       |  |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF         | TXIF          | SSPIF         | CCP1IF     | TMR2IF   | TMR1IF | 0000 0000                | 0000 0000                       |  |

| 0Dh                    | PIR2    | —                    | _           | _            | _             | —             | —          | _        | CCP2IF | 0                        | 0                               |  |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE         | TXIE          | SSPIE         | CCP1IE     | TMR2IE   | TMR1IE | 0000 0000                | 0000 0000                       |  |

| 8Dh                    | PIE2    | —                    | CCP2IE -    |              |               |               |            |          |        | 0                        | 0                               |  |

| 87h                    | TRISC   | PORTC D              | ata Direct  | 1111 1111    | 1111 1111     |               |            |          |        |                          |                                 |  |

| 0Eh                    | TMR1L   | Holding R            | egister for |              | xxxx xxxx     | uuuu uuuu     |            |          |        |                          |                                 |  |

| 0Fh                    | TMR1H   | Holding R            | egister for | r the Most S | Significant B | yte of the 16 | 6-bit TMR1 | Register |        | xxxx xxxx                | uuuu uuuu                       |  |

| 10h                    | T1CON   | —                    | _           | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS   | TMR10N | 00 0000                  | uu uuuu                         |  |

| 15h                    | CCPR1L  | Capture/C            | ompare/F    | WM Regist    | ter1 (LSB)    |               |            |          |        | XXXX XXXX                | uuuu uuuu                       |  |

| 16h                    | CCPR1H  | Capture/C            | ompare/F    | WM Regist    | ter1 (MSB)    |               |            |          |        | xxxx xxxx                | uuuu uuuu                       |  |

| 17h                    | CCP1CON | —                    | _           | CCP1X        | CCP1Y         | CCP1M3        | CCP1M2     | CCP1M1   | CCP1M0 | 00 0000                  | 00 0000                         |  |

| 1Bh                    | CCPR2L  | Capture/C            | ompare/F    | xxxx xxxx    | uuuu uuuu     |               |            |          |        |                          |                                 |  |

| 1Ch                    | CCPR2H  | Capture/C            | ompare/F    |              | xxxx xxxx     | uuuu uuuu     |            |          |        |                          |                                 |  |

| 1Dh                    | CCP2CON | —                    | —           | CCP2X        | CCP2Y         | CCP2M3        | CCP2M2     | CCP2M1   | CCP2M0 | 00 0000                  | 00 0000                         |  |

$\label{eq:legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.$

Note 1: The PSP is not implemented on the PIC16F873/876; always maintain these bits clear.

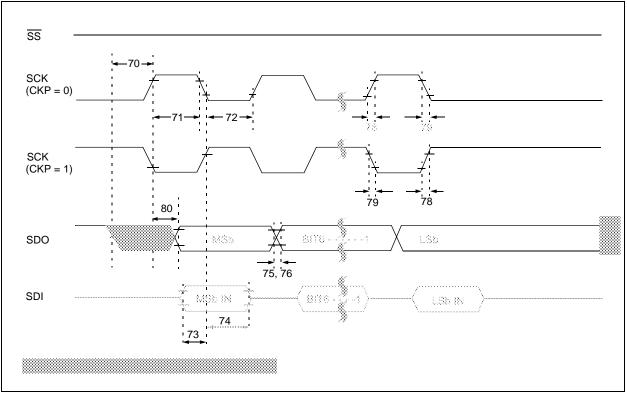

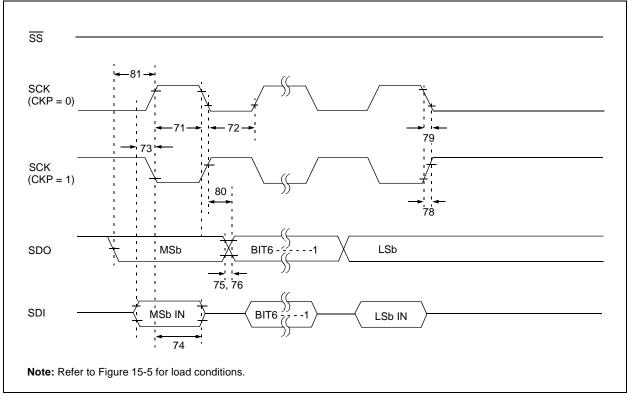

### 9.1 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPCON<5:0> and SSPSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data input sample phase (middle or end of data output time)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

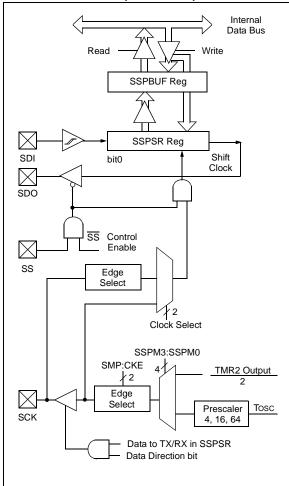

Figure 9-4 shows the block diagram of the MSSP module when in SPI mode.

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set and register ADCON1 (see Section 11.0: A/D Module) must be set in a way that pin RA5 is configured as a digital I/O

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### FIGURE 9-1: MSSP BLOCK DIAGRAM (SPI MODE)

#### 9.2.1 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs. The MSSP module will override the input state with the output data, when required (slavetransmitter).

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the MSSP module not to give this ACK pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

If the BF bit is set, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF and SSPOV are set. Table 9-2 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, is shown in timing parameter #100 and parameter #101 of the electrical specifications.

#### 9.2.1.1 Addressing

Once the MSSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register on the falling edge of the 8th SCL pulse.

- b) The buffer full bit, BF, is set on the falling edge of the 8th SCL pulse.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the 9th SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte.

For a 10-bit address, the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for a 10-bit address is as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with the second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address. This will clear bit UA and release the SCL line.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

| Note: | Following the Repeated START condition<br>(step 7) in 10-bit mode, the user only<br>needs to match the first 7-bit address. The |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | user does not update the SSPADD for the second half of the address.                                                             |

#### 9.2.1.2 Slave Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set, or bit SSPOV (SSPCON<6>) is set. This is an error condition due to user firmware.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note: The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occurred, the ACK is not sent and the SSPBUF is updated.

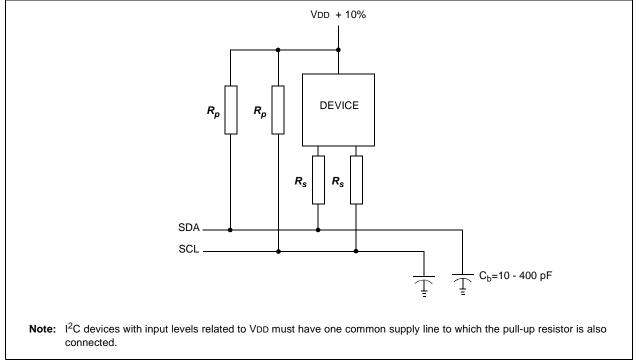

## 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^{2}C$  bus devices, the values of resistors  $R_{p}$  and  $R_{s}$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_{p}$ , due to the specified minimum sink current of 3 mA at VOL max = 0.4V, for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_p$ min =  $(5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-27. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

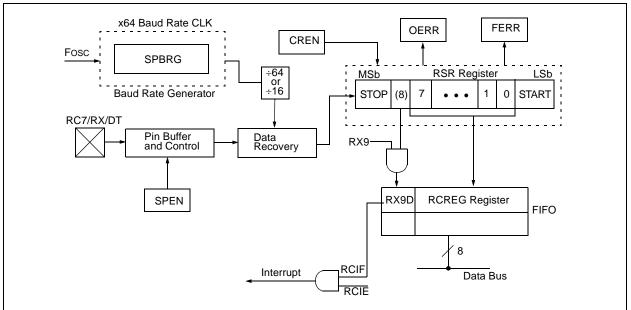

#### 10.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 10-4. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter, operating at x16 times the baud rate; whereas, the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full, the overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, and no further data will be received. It is therefore, essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a STOP bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG will load bits RX9D and FERR with new values, therefore, it is essential for the user to read the RCSTA register before reading the RCREG register in order not to lose the old FERR and RX9D information.

#### 10.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>), or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set, CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit, which is reset by the hardware. In this case, it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register (i.e., it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full, then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The ninth

receive bit is buffered the same way as the receive data. Reading the RCREG register will load bit RX9D with a new value, therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

When setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 10.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

| Address                | Name   | Bit 7                | Bit 6      | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|------------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE      | INTE      | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x                | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9        | SREN      | CREN      | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah                    | RCREG  | USART R              | eceive Re  | gister    |           |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9        | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | e Generate | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |

#### TABLE 10-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

## REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1              | CP0 | DEBUG                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                      | WRT      | CPD       | LVP                | BODEN                                      | CP1                 | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |  |

|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------------------|--------------------------------------------|---------------------|-----|-------|------|-------|-------|--|

| bit13<br>bit 13- | 12, |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                        | -        | n Memor   | y Code             | Protection b                               | <sub>Dits</sub> (2) |     |       |      |       | bit0  |  |

| bit 5-4          |     | 10 = 0F00<br>01 = 1000<br>01 = 0800<br>00 = 0000                                                                                                                                                    | 10 = 1F00h to 1FFFh code protected (PIC16F877, 876)<br>10 = 0F00h to 0FFFh code protected (PIC16F874, 873)<br>01 = 1000h to 1FFFh code protected (PIC16F877, 876)<br>01 = 0800h to 0FFFh code protected (PIC16F874, 873)<br>00 = 0000h to 1FFFh code protected (PIC16F877, 876)<br>00 = 0000h to 0FFFh code protected (PIC16F874, 873) |          |           |                    |                                            |                     |     |       |      |       |       |  |

| bit 11           |     | <b>DEBUG:</b> In-Circuit Debugger Mode<br>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger. |                                                                                                                                                                                                                                                                                                                                        |          |           |                    |                                            |                     |     |       |      |       |       |  |

| bit 10           |     | Unimpler                                                                                                                                                                                            | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                             |          |           |                    |                                            |                     |     |       |      |       |       |  |

| bit 9            |     | WRT: FLASH Program Memory Write Enable<br>1 = Unprotected program memory may be written to by EECON control<br>0 = Unprotected program memory may not be written to by EECON control                |                                                                                                                                                                                                                                                                                                                                        |          |           |                    |                                            |                     |     |       |      |       |       |  |

| bit 8            |     | 1 = Code                                                                                                                                                                                            | <b>CPD:</b> Data EE Memory Code Protection<br>1 = Code protection off<br>0 = Data EEPROM memory code protected                                                                                                                                                                                                                         |          |           |                    |                                            |                     |     |       |      |       |       |  |

| bit 7            |     | 1 = RB3/F                                                                                                                                                                                           | PGM pin                                                                                                                                                                                                                                                                                                                                | has PGN  | 1 functio | n, low v           | iming Enabl<br>oltage prog<br>e used for p | ramming             |     | 1     |      |       |       |  |

| bit 6            |     | <b>BODEN</b> :<br>1 = BOR<br>0 = BOR                                                                                                                                                                | enabled                                                                                                                                                                                                                                                                                                                                | ut Reset | Enable t  | <sub>Dit</sub> (3) |                                            |                     |     |       |      |       |       |  |

| bit 3            |     | <b>PWRTE</b> :<br>1 = PWR<br>0 = PWR                                                                                                                                                                | T disable                                                                                                                                                                                                                                                                                                                              | ed       | nable b   | it(3)              |                                            |                     |     |       |      |       |       |  |

| bit 2            |     | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                                                                                                                                                               | enabled                                                                                                                                                                                                                                                                                                                                |          | nable bit |                    |                                            |                     |     |       |      |       |       |  |

| bit 1-0          |     | FOSC1:F<br>11 = RC (<br>10 = HS (<br>01 = XT (<br>00 = LP (                                                                                                                                         | oscillator<br>oscillator<br>oscillator                                                                                                                                                                                                                                                                                                 |          | Selectio  | n bits             |                                            |                     |     |       |      |       |       |  |

- **Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

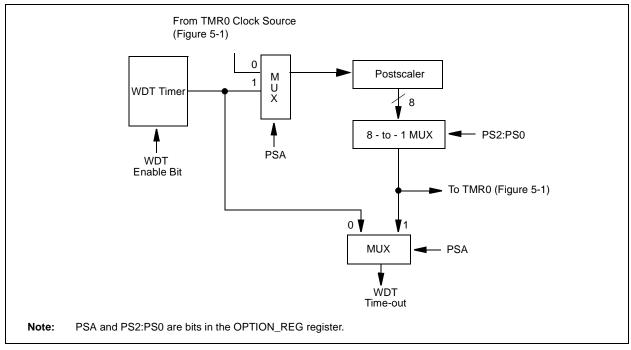

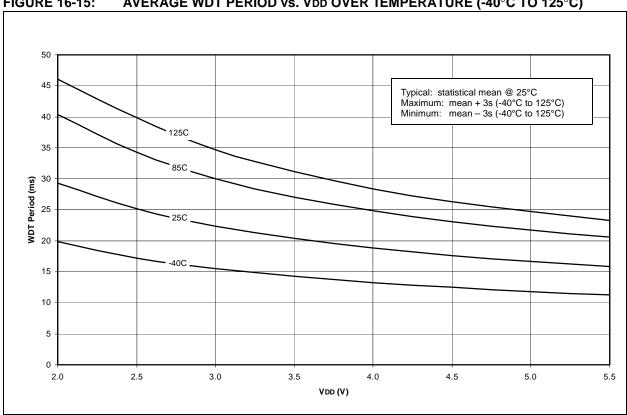

### 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer. **Note 1:** See Register 12-1 for operation of these bits.

### 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

#### 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

## PIC16F87X

NOTES:

#### FIGURE 15-13: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

#### FIGURE 15-14: SPI MASTER MODE TIMING (CKE = 1, SMP = 1)

# **PIC16F87X**

#### FIGURE 16-15: AVERAGE WDT PERIOD vs. VDD OVER TEMPERATURE (-40°C TO 125°C)

## PIC16F87X

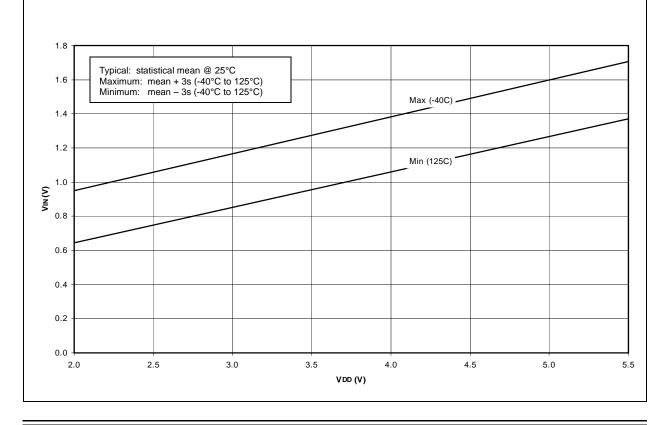

FIGURE 16-20: MINIMUM AND MAXIMUM VIN vs. Vdd, (TTL INPUT, -40°C TO 125°C)