#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 (STATUS<6>) and RP0 (STATUS<5>) are the bank select bits.

| RP1:RP0 | Bank |

|---------|------|

| 00      | 0    |

| 01      | 1    |

| 10      | 2    |

| 11      | 3    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank may be mirrored in another bank for code reduction and quicker access.

| Note: | EEPROM Data Memory description can be found in Section 4.0 of this data sheet. |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------|--|--|--|--|--|

| 2.2.4 |                                                                                |  |  |  |  |  |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register (FSR).

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                               | Bit 5         | Bit 4          | Bit 3          | Bit 2             | Bit 1          | Bit 0     | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|----------------------|-------------------------------------|---------------|----------------|----------------|-------------------|----------------|-----------|--------------------------|------------------------|

| Bank 0               |         |                      |                                     |               |                |                |                   |                |           |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | g this locatio                      | n uses conte  | ents of FSR to | address dat    | a memory (no      | t a physical r | egister)  | 0000 0000                | 27                     |

| 01h                  | TMR0    | Timer0 Mc            | dule Registe                        | er            |                |                |                   |                |           | xxxx xxxx                | 47                     |

| 02h <sup>(3)</sup>   | PCL     | Program C            | Counter (PC)                        | Least Signif  | icant Byte     |                |                   |                |           | 0000 0000                | 26                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1                                 | RP0           | TO             | PD             | Z                 | DC             | С         | 0001 1xxx                | 18                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ata Memory /                        | Address Poir  | nter           |                |                   |                |           | xxxx xxxx                | 27                     |

| 05h                  | PORTA   | _                    | _                                   | PORTA Da      | ta Latch whe   | n written: POI | RTA pins whe      | n read         |           | 0x 0000                  | 29                     |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh                        | en written: P | ORTB pins w    | /hen read      |                   |                |           | xxxx xxxx                | 31                     |

| 07h                  | PORTC   | PORTC D              | ata Latch wh                        | en written: F | ORTC pins v    | vhen read      |                   |                |           | xxxx xxxx                | 33                     |

| 08h <sup>(4)</sup>   | PORTD   | PORTD D              | ata Latch wh                        | en written: F | ORTD pins v    | vhen read      |                   |                |           | xxxx xxxx                | 35                     |

| 09h <sup>(4)</sup>   | PORTE   | _                    | _                                   | _             | _              | _              | RE2               | RE1            | RE0       | xxx                      | 36                     |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    |                                     |               | Write Buffer   | for the upper  | r 5 bits of the I | Program Cou    | unter     | 0 0000                   | 26                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE                                | T0IE          | INTE           | RBIE           | T0IF              | INTF           | RBIF      | 0000 000x                | 20                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                | RCIF          | TXIF           | SSPIF          | CCP1IF            | TMR2IF         | TMR1IF    | 0000 0000                | 22                     |

| 0Dh                  | PIR2    | —                    | (5)                                 | _             | EEIF           | BCLIF          | —                 |                | CCP2IF    | -r-0 00                  | 24                     |

| 0Eh                  | TMR1L   | Holding re           | gister for the                      | Least Signif  | ficant Byte of | the 16-bit TM  | IR1 Register      |                |           | xxxx xxxx                | 52                     |

| 0Fh                  | TMR1H   | Holding re           | gister for the                      | Most Signifi  | cant Byte of t | the 16-bit TM  | R1 Register       |                |           | xxxx xxxx                | 52                     |

| 10h                  | T1CON   | _                    | _                                   | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC            | TMR1CS         | TMR10N    | 00 0000                  | 51                     |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe                        | er            |                |                |                   |                |           | 0000 0000                | 55                     |

| 12h                  | T2CON   | _                    | TOUTPS3                             | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON            | T2CKPS1        | T2CKPS0   | -000 0000                | 55                     |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po                       | rt Receive B  | uffer/Transm   | it Register    |                   |                |           | xxxx xxxx                | 70, 73                 |

| 14h                  | SSPCON  | WCOL                 | SSPOV                               | SSPEN         | CKP            | SSPM3          | SSPM2             | SSPM1          | SSPM0     | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI                          | M Register1   | (LSB)          |                |                   |                |           | XXXX XXXX                | 57                     |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI                          | M Register1   | (MSB)          |                |                   |                |           | XXXX XXXX                | 57                     |

| 17h                  | CCP1CON | _                    | _                                   | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2            | CCP1M1         | CCP1M0    | 00 0000                  | 58                     |

| 18h                  | RCSTA   | SPEN                 | RX9                                 | SREN          | CREN           | ADDEN          | FERR              | OERR           | RX9D      | 0000 000x                | 96                     |

| 19h                  | TXREG   | USART Tr             | USART Transmit Data Register        |               |                |                |                   |                | 0000 0000 | 99                       |                        |

| 1Ah                  | RCREG   | USART Re             | USART Receive Data Register         |               |                |                |                   |                |           | 0000 0000                | 101                    |

| 1Bh                  | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |               |                |                |                   |                |           | xxxx xxxx                | 57                     |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI                          | M Register2   | (MSB)          |                |                   |                |           | xxxx xxxx                | 57                     |

| 1Dh                  | CCP2CON | _                    | _                                   | CCP2X         | CCP2Y          | CCP2M3         | CCP2M2            | CCP2M1         | CCP2M0    | 00 0000                  | 58                     |

| 1Eh                  | ADRESH  | A/D Result           | t Register Hi                       | gh Byte       |                |                |                   |                |           | xxxx xxxx                | 116                    |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                               | CHS2          | CHS1           | CHS0           | GO/DONE           | _              | ADON      | 0000 00-0                | 111                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

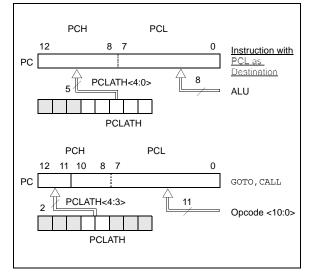

# 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any RESET, the upper bits of the PC will be cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The PIC16F87X family has an 8-level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

# 2.4 Program Memory Paging

All PIC16F87X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is popped off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the return instructions (which POPs the address from the stack).

| Note: | The contents of the PCLATH register are    |

|-------|--------------------------------------------|

|       | unchanged after a RETURN or RETFIE         |

|       | instruction is executed. The user must     |

|       | rewrite the contents of the PCLATH regis-  |

|       | ter for any subsequent subroutine calls or |

|       | GOTO instructions.                         |

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

#### EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

|         | ORG 0x500<br>BCF PCLATH,4 |                                                              |  |  |  |  |  |

|---------|---------------------------|--------------------------------------------------------------|--|--|--|--|--|

|         | BSF PCLATH, 3             | ;Select page 1<br>;(800h-FFFh)                               |  |  |  |  |  |

|         | CALL SUB1_P1<br>:         | ;Call subroutine in ;page 1 (800h-FFFh)                      |  |  |  |  |  |

| SUB1 P1 | ORG 0x900                 | ;page 1 (800h-FFFh)                                          |  |  |  |  |  |

| 2021_11 | :                         | ;called subroutine<br>;page 1 (800h-FFFh)                    |  |  |  |  |  |

|         | :<br>RETURN               | ;return to<br>;Call subroutine<br>;in page 0<br>;(000h-7FFh) |  |  |  |  |  |

### TABLE 3-5:PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                            |

|-----------------|------|-------------|-----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input.                               |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output. |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/<br>PWM1 output.                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.               |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                     |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output.                                       |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit or Synchronous Clock.                          |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous Receive or Synchronous Data.                            |

Legend: ST = Schmitt Trigger input

### TABLE 3-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7 | Bit 6                                   | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on:<br>POR,<br>BOR | Value on all<br>other<br>RESETS |

|---------|-------|-------|-----------------------------------------|-------|-------|-------|-----------|-----------|-------|--------------------------|---------------------------------|

| 07h     | PORTC | RC7   | RC6                                     | RC5   | RC4   | RC3   | RC2       | RC1       | RC0   | xxxx xxxx                | uuuu uuuu                       |

| 87h     | TRISC | PORTC | PORTC Data Direction Register 1111 1111 |       |       |       | 1111 1111 | 1111 1111 |       |                          |                                 |

Legend: x = unknown, u = unchanged

At the completion of the write cycle, the WR bit is cleared and the EEIF interrupt flag bit is set. (EEIF must be cleared by firmware.) Since the microcontroller does not execute instructions during the write cycle, the firmware does not necessarily have to check either EEIF, or WR, to determine if the write had finished.

EXAMPLE 4-4: FLASH PROGRAM WRITE

| BSF   | STATUS, RI | P1 ;                         |

|-------|------------|------------------------------|

| BCF   |            | P0 ;Bank 2                   |

| MOVF  | ADDRL, W   | ;Write address               |

| MOVWF | EEADR      | ; of desired                 |

| MOVF  | ADDRH, W   | ;program memory              |

| MOVWF | EEADRH     | ;location                    |

| MOVF  | VALUEL, W  | ;Write value to              |

| MOVWF | EEDATA     | ;program at                  |

| MOVF  | VALUEH, W  | ;desired memory              |

| MOVWF | EEDATH     | ;location                    |

| BSF   | STATUS, R  | P0 ;Bank 3                   |

| BSF   | EECON1, EE | PGD ;Point to Program memory |

| BSF   | EECON1, WI | REN ;Enable writes           |

|       |            | ;Only disable interrupts     |

| BCF   | INTCON, G  | IE ; if already enabled,     |

|       |            | ;otherwise discard           |

| MOVLW | 0x55       | ;Write 55h to                |

| MOVWF | EECON2     | ; EECON2                     |

| MOVLW | 0xAA       | ;Write AAh to                |

| MOVWF | EECON2     | ; EECON2                     |

| BSF   | EECON1, W  | R ;Start write operation     |

| NOP   |            | ;Two NOPs to allow micro     |

| NOP   |            | ;to setup for write          |

|       |            | ;Only enable interrupts      |

| BSF   | INTCON, G  | IE ;if using interrupts,     |

|       |            | ;otherwise discard           |

| BCF   | EECON1, W  | REN ;Disable writes          |

# 4.6 Write Verify

The PIC16F87X devices do not automatically verify the value written during a write operation. Depending on the application, good programming practice may dictate that the value written to memory be verified against the original value. This should be used in applications where excessive writes can stress bits near the specified endurance limits.

### 4.7 Protection Against Spurious Writes

There are conditions when the device may not want to write to the EEPROM data memory or FLASH program memory. To protect against these spurious write conditions, various mechanisms have been built into the PIC16F87X devices. On power-up, the WREN bit is cleared and the Power-up Timer (if enabled) prevents writes.

The write initiate sequence, and the WREN bit together, help prevent any accidental writes during brown-out, power glitches, or firmware malfunction.

# 4.8 Operation While Code Protected

The PIC16F87X devices have two code protect mechanisms, one bit for EEPROM data memory and two bits for FLASH program memory. Data can be read and written to the EEPROM data memory, regardless of the state of the code protection bit, CPD. When code protection is enabled and CPD cleared, external access via ICSP is disabled, regardless of the state of the program memory code protect bits. This prevents the contents of EEPROM data memory from being read out of the device.

The state of the program memory code protect bits, CP0 and CP1, do not affect the execution of instructions out of program memory. The PIC16F87X devices can always read the values in program memory, regardless of the state of the code protect bits. However, the state of the code protect bits and the WRT bit will have different effects on writing to program memory. Table 4-1 shows the effect of the code protect bits and the WRT bit on program memory.

Once code protection has been enabled for either EEPROM data memory or FLASH program memory, only a full erase of the entire device will disable code protection.

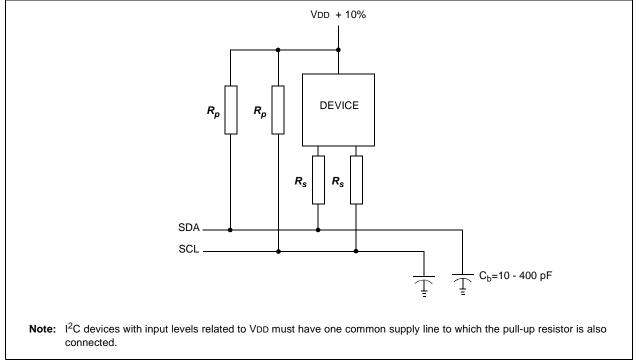

# 9.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^{2}C$  bus devices, the values of resistors  $R_{p}$  and  $R_{s}$  in Figure 9-27 depend on the following parameters:

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current)

The supply voltage limits the minimum value of resistor  $R_{p}$ , due to the specified minimum sink current of 3 mA at VOL max = 0.4V, for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA,  $R_p$ min =  $(5.5-0.4)/0.003 = 1.7 \text{ k}\Omega$ . VDD as a function of  $R_p$  is shown in Figure 9-27. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $R_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 9-27).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

# 11.5 A/D Operation During SLEEP

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed, the GO/DONE bit will be cleared and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

| Note: | For the A/D module to operate in SLEEP,   |

|-------|-------------------------------------------|

|       | the A/D clock source must be set to RC    |

|       | (ADCS1:ADCS0 = 11). To allow the con-     |

|       | version to occur during SLEEP, ensure the |

|       | SLEEP instruction immediately follows the |

|       | instruction that sets the GO/DONE bit.    |

## 11.6 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the A/D module to be turned off, and any conversion is aborted. All A/D input pins are configured as analog inputs.

The value that is in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

| Address               | Name   | Bit 7                | Bit 6                  | Bit 5                                               | Bit 4         | Bit 3      | Bit 2    | Bit 1       | Bit 0     | Value on<br>POR,<br>BOR | V <u>alue o</u> n<br>MCLR,<br>WDT |

|-----------------------|--------|----------------------|------------------------|-----------------------------------------------------|---------------|------------|----------|-------------|-----------|-------------------------|-----------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                   | TOIE                                                | INTE          | RBIE       | TOIF     | INTF        | RBIF      | 0000 000x               | 0000 000u                         |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                   | RCIF                                                | TXIF          | SSPIF      | CCP1IF   | TMR2IF      | TMR1IF    | 0000 0000               | 0000 0000                         |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                   | RCIE                                                | TXIE          | SSPIE      | CCP1IE   | TMR2IE      | TMR1IE    | 0000 0000               | 0000 0000                         |

| 1Eh                   | ADRESH | A/D Resul            | ult Register High Byte |                                                     |               |            |          |             | xxxx xxxx | uuuu uuuu               |                                   |

| 9Eh                   | ADRESL | A/D Resul            | t Register             | Low Byt                                             | e             |            |          |             |           | xxxx xxxx               | uuuu uuuu                         |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0                  | CHS2                                                | CHS1          | CHS0       | GO/DONE  | _           | ADON      | 0000 00-0               | 0000 00-0                         |

| 9Fh                   | ADCON1 | ADFM                 | —                      | _                                                   | _             | PCFG3      | PCFG2    | PCFG1       | PCFG0     | 0- 0000                 | 0- 0000                           |

| 85h                   | TRISA  | —                    | —                      | PORTA                                               | Data Directio | n Register |          |             |           | 11 1111                 | 11 1111                           |

| 05h                   | PORTA  |                      | —                      | PORTA Data Latch when written: PORTA pins when read |               |            |          | 0x 0000     | 0u 0000   |                         |                                   |

| 89h <sup>(1)</sup>    | TRISE  | IBF                  | OBF                    | IBOV                                                | PSPMODE       | _          | PORTE Da | ta Directio | n bits    | 0000 -111               | 0000 -111                         |

| 09h <sup>(1)</sup>    | PORTE  | —                    | —                      |                                                     | —             | —          | RE2      | RE1         | RE0       | xxx                     | uuu                               |

# TABLE 11-2: REGISTERS/BITS ASSOCIATED WITH A/D

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These registers/bits are not available on the 28-pin devices.

#### 12.13 Power-down Mode (SLEEP)

Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit (STATUS<3>) is cleared, the TO (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD or VSS, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D and disable external clocks. Pull all I/O pins that are hi-impedance inputs, high or low externally, to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTB should also be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 12.13.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External RESET input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change or peripheral interrupt.

External MCLR Reset will cause a device RESET. All other events are considered a continuation of program execution and cause a "wake-up". The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The TO bit is cleared if a WDT time-out occurred and caused wake-up.

The following peripheral interrupts can wake the device from SLEEP:

- 1. PSP read or write (PIC16F874/877 only).

- 2. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 3. CCP Capture mode interrupt.

- 4. Special event trigger (Timer1 in Asynchronous mode using an external clock).

- 5. SSP (START/STOP) bit detect interrupt.

- SSP transmit or receive in Slave mode (SPI/I<sup>2</sup>C).

- 7. USART RX or TX (Synchronous Slave mode).

- 8. A/D conversion (when A/D clock source is RC).

- 9. EEPROM write operation completion

Other peripherals cannot generate interrupts since during SLEEP, no on-chip clocks are present. When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 12.13.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake-up from SLEEP. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# PIC16F87X

| MOVF             | Move f                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                       |

| Operation:       | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register f are<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f itself.<br>d = 1 is useful to test a file register,<br>since status flag Z is affected. |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [ label ] NOP |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| MOVLW            | Move Literal to W                                                                                |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                         |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                             |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded<br>into W register. The don't cares<br>will assemble as 0's. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                   |  |  |  |  |

|------------------|---------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                          |  |  |  |  |

| Operands:        | None                                                    |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$ |  |  |  |  |

| Status Affected: | None                                                    |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVWF f                   |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                          |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>eight bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a two-cycle instruction. |  |  |  |  |  |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                               |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                               |  |  |  |  |  |  |  |

# SLEEP

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                        |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Operands:        | None                                                                                                                                                                                                                                 |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                           |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                               |  |  |  |  |

| Description:     | The power-down status bit, $\overline{\text{PD}}$ is cleared. Time-out status bit, $\overline{\text{TO}}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into SLEEP mode with the oscillator stopped. |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                     |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                             |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                       |  |  |  |  |  |  |

| Operation:       | $TOS\toPC$                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |  |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                   |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from Literal                                                                                                      |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \rightarrow (W)$                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                       |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |  |  |  |  |  |

| Operands:           | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                      |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |  |  |  |  |  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |

# PIC16F87X

NOTES:

# 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$             |                                                      |                               |      |      |                                               |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------------------|------------------------------------------------------|-------------------------------|------|------|-----------------------------------------------|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                               |      |      |                                               |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                                        | Min                                                  | Min Typ† Max Units Conditions |      |      |                                               |

|                                                                                  | Vdd    | Supply Voltage                                                   |                                                      |                               |      |      |                                               |

| D001                                                                             |        | 16LF87X                                                          | 2.0                                                  |                               | 5.5  | V    | LP, XT, RC osc configuration<br>(DC to 4 MHz) |

| D001                                                                             |        | 16F87X                                                           | 4.0                                                  | _                             | 5.5  | V    | LP, XT, RC osc configuration                  |

| D001A                                                                            |        |                                                                  | 4.5                                                  |                               | 5.5  | V    | HS osc configuration                          |

|                                                                                  |        |                                                                  | VBOR                                                 |                               | 5.5  | V    | BOR enabled, FMAX = 14 MHz <sup>(7)</sup>     |

| D002                                                                             | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | —                                                    | 1.5                           |      | V    |                                               |

| D003                                                                             | Vpor   | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                    | Vss                           | _    | V    | See section on Power-on Reset for details     |

| D004                                                                             | Svdd   | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05                                                 | —                             | —    | V/ms | See section on Power-on Reset for details     |

| D005                                                                             | VBOR   | Brown-out Reset<br>Voltage                                       | 3.7                                                  | 4.0                           | 4.35 | V    | BODEN bit in configuration word<br>enabled    |

Legend: Rows with standard voltage device data only are shaded for improved readability.

- † Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

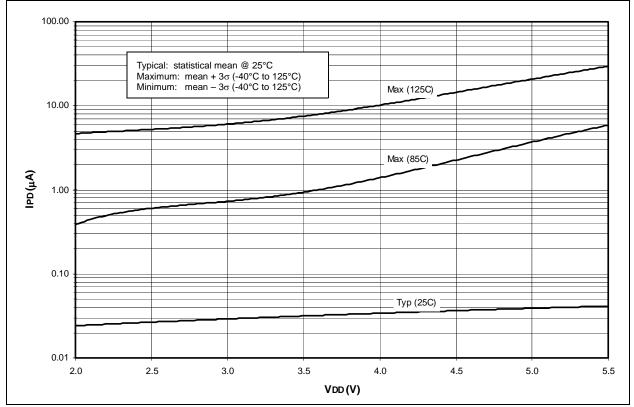

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

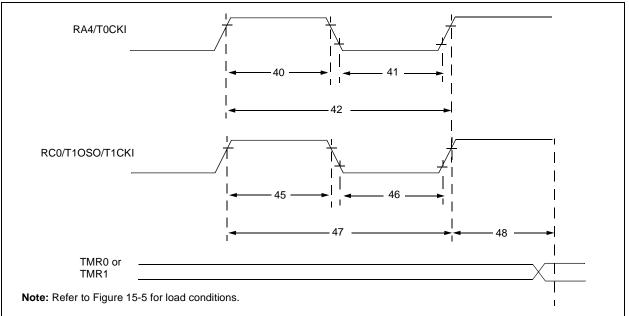

| TABLE 15-4: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Symbol    |                                             | Characteristic      |                | Min                   | Тур† | Max | Units | Conditions         |  |

|--------------|-----------|---------------------------------------------|---------------------|----------------|-----------------------|------|-----|-------|--------------------|--|

| 40*          | Tt0H      | T0CKI High Pulse                            | Width               | No Prescaler   | 0.5TCY + 20           | _    | _   | ns    | Must also meet     |  |

|              |           |                                             |                     | With Prescaler | 10                    | _    | _   | ns    | parameter 42       |  |

| 41*          | Tt0L      | T0CKI Low Pulse                             | Width               | No Prescaler   | 0.5Tcy + 20           | _    | _   | ns    | Must also meet     |  |

|              |           |                                             |                     | With Prescaler | 10                    | _    | _   | ns    | parameter 42       |  |

| 42*          | Tt0P      | T0CKI Period                                |                     | No Prescaler   | Tcy + 40              | _    | _   | ns    |                    |  |

|              |           |                                             |                     | With Prescaler | Greater of:           | —    | —   | ns    | N = prescale value |  |

|              |           |                                             |                     |                | 20 or <u>TCY + 40</u> |      |     |       | (2, 4,, 256)       |  |

|              |           |                                             |                     |                | N                     |      |     |       |                    |  |

| 45*          | Tt1H      | T1CKI High Time                             | Synchronous, Pr     | escaler = 1    | 0.5Tcy + 20           | —    | I   | -     | Must also meet     |  |

|              |           |                                             | Synchronous,        | Standard(F)    | 15                    |      | I   | ns    | parameter 47       |  |

|              |           |                                             | Prescaler = $2,4,8$ | Extended(LF)   | 25                    |      | _   | ns    |                    |  |

|              |           |                                             | Asynchronous        | Standard(F)    | 30                    |      | _   | ns    |                    |  |

|              |           |                                             |                     | Extended(LF)   | 50                    | _    | -   | ns    |                    |  |

| 46*          | Tt1L      | T1CKI Low Time                              | Synchronous, Pr     | escaler = 1    | 0.5TCY + 20           | —    | —   | ns    | Must also meet     |  |

|              |           |                                             | Synchronous,        | Standard(F)    | 15                    |      | _   | ns    | parameter 47       |  |

|              |           |                                             | Prescaler = 2,4,8   | Extended(LF)   | 25                    | —    |     | ns    |                    |  |

|              |           |                                             | Asynchronous        | Standard(F)    | 30                    | —    |     | ns    |                    |  |

|              |           |                                             |                     | Extended(LF)   | 50                    | —    |     | ns    |                    |  |

| 47*          | Tt1P      | T1CKI input                                 | Synchronous         | Standard(F)    | Greater of:           | —    | —   | ns    | N = prescale value |  |

|              |           | period                                      |                     |                | 30 or <u>Tcy + 40</u> |      |     |       | (1, 2, 4, 8)       |  |

|              |           |                                             |                     |                | N                     |      |     |       |                    |  |

|              |           |                                             |                     | Extended(LF)   | Greater of:           |      |     |       | N = prescale value |  |

|              |           |                                             |                     |                | 50 OR <u>TCY + 40</u> |      |     |       | (1, 2, 4, 8)       |  |

|              |           |                                             |                     | -              | N                     |      |     |       |                    |  |

|              |           |                                             | Asynchronous        | Standard(F)    | 60                    |      | _   | ns    |                    |  |

|              |           |                                             |                     | Extended(LF)   | 100                   | —    | —   | ns    |                    |  |

|              | Ft1       | Timer1 oscillator ir<br>(oscillator enabled |                     | 0              | DC                    | -    | 200 | kHz   |                    |  |

| 48           | TCKEZtmr1 | Delay from externa                          | 2Tosc               | —              | 7Tosc                 | _    |     |       |                    |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

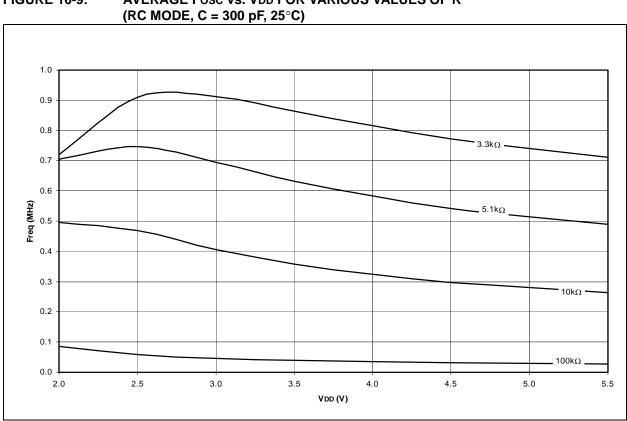

**FIGURE 16-9:** AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R

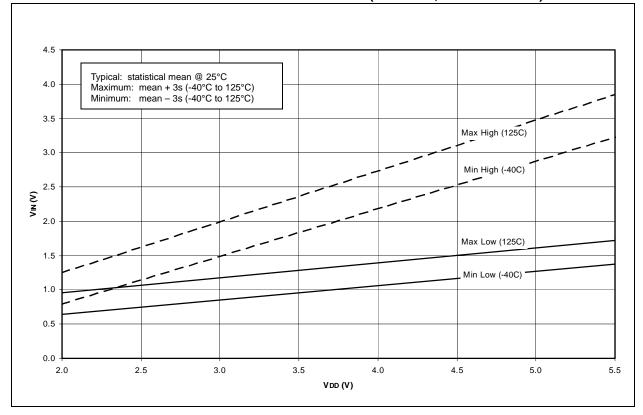

FIGURE 16-21: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO 125°C)

© 1998-2013 Microchip Technology Inc.

# 17.0 PACKAGING INFORMATION

# 17.1 Package Marking Information

#### 28-Lead PDIP (Skinny DIP)

Example

28-Lead SOIC

Example

| Legen | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|-------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                    |

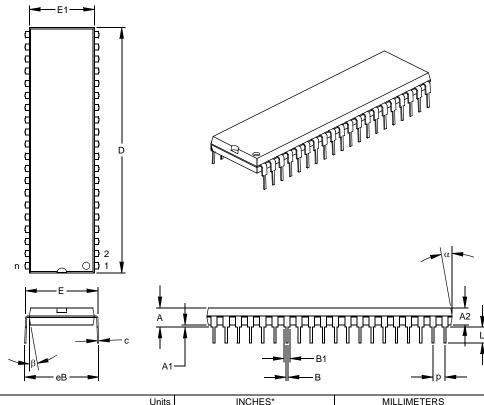

# 40-Lead Plastic Dual In-line (P) - 600 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            |     | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|-----|---------|-------|-------------|-------|-------|-------|

| Dimensi                    | MIN | NOM     | MAX   | MIN         | NOM   | MAX   |       |

| Number of Pins             | n   |         | 40    |             |       | 40    |       |

| Pitch                      | р   |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | А   | .160    | .175  | .190        | 4.06  | 4.45  | 4.83  |

| Molded Package Thickness   | A2  | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Base to Seating Plane      | A1  | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е   | .595    | .600  | .625        | 15.11 | 15.24 | 15.88 |

| Molded Package Width       | E1  | .530    | .545  | .560        | 13.46 | 13.84 | 14.22 |

| Overall Length             | D   | 2.045   | 2.058 | 2.065       | 51.94 | 52.26 | 52.45 |

| Tip to Seating Plane       | L   | .120    | .130  | .135        | 3.05  | 3.30  | 3.43  |

| Lead Thickness             | С   | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1  | .030    | .050  | .070        | 0.76  | 1.27  | 1.78  |

| Lower Lead Width           | В   | .014    | .018  | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing §      | eB  | .620    | .650  | .680        | 15.75 | 16.51 | 17.27 |

| Mold Draft Angle Top       | α   | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom β  |     | 5       | 10    | 15          | 5     | 10    | 15    |

| * 0 / 11' D /              |     |         |       |             |       |       |       |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-011

Drawing No. C04-016

### W

| Wake-up from SLEEP 119, 132                |

|--------------------------------------------|

| Interrupts 125, 126                        |

| MCLR Reset126                              |

| Timing Diagram133                          |

| WDT Reset 126                              |

| Watchdog Timer (WDT) 119, 131              |

| Block Diagram131                           |

| Enable (WDTE Bit)131                       |

| Postscaler. See Postscaler, WDT            |

| Programming Considerations131              |

| RC Oscillator131                           |

| Time-out Period131                         |

| WDT Reset, Normal Operation 123, 125, 126  |

| WDT Reset, SLEEP 123, 125, 126             |

| Waveform for General Call Address Sequence |

| WCOL                                       |

| WCOL Status Flag80                         |

| Write Collision Detect bit, WCOL67         |

| Write Verify                               |

| Data EEPROM and FLASH Program Memory45     |

| WWW, On-Line Support4                      |

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- Listing of seminars and events