Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 368 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f876t-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin#     | l/O/P<br>Type        | Buffer<br>Type         | Description                                                                                            |

|-------------------|----------------|-------------------|-----------------|----------------------|------------------------|--------------------------------------------------------------------------------------------------------|

|                   |                |                   |                 |                      |                        | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15             | 16                | 32              | I/O                  | ST                     | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16             | 18                | 35              | I/O                  | ST                     | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17             | 19                | 36              | I/O                  | ST                     | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                        |

| RC3/SCK/SCL       | 18             | 20                | 37              | I/O                  | ST                     | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23             | 25                | 42              | I/O                  | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                        |

| RC5/SDO           | 24             | 26                | 43              | I/O                  | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25             | 27                | 44              | I/O                  | ST                     | RC6 can also be the USART Asynchronous Transmi<br>or Synchronous Clock.                                |

| RC7/RX/DT         | 26             | 29                | 1               | I/O                  | ST                     | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                   |                |                   |                 |                      |                        | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19             | 21                | 38              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD1/PSP1          | 20             | 22                | 39              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD2/PSP2          | 21             | 23                | 40              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD3/PSP3          | 22             | 24                | 41              | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD4/PSP4          | 27             | 30                | 2               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD5/PSP5          | 28             | 31                | 3               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD6/PSP6          | 29             | 32                | 4               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

| RD7/PSP7          | 30             | 33                | 5               | I/O                  | ST/TTL <sup>(3)</sup>  |                                                                                                        |

|                   |                |                   |                 |                      |                        | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8              | 9                 | 25              | I/O                  | ST/TTL <sup>(3)</sup>  | RE0 can also be read control for the parallel slave port, or analog input5.                            |

| RE1/WR/AN6        | 9              | 10                | 26              | I/O                  | ST/TTL <sup>(3)</sup>  | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10             | 11                | 27              | I/O                  | ST/TTL <sup>(3)</sup>  | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31          | 13,34             | 6,29            | Р                    | _                      | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32          | 12,35             | 7,28            | Р                    | _                      | Positive supply for logic and I/O pins.                                                                |

| NC                | -              | 1,17,28,<br>40    | 12,13,<br>33,34 |                      | —                      | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |                 | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                |

#### TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION (CONTINUED)

**Note 1:** This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## 2.0 MEMORY ORGANIZATION

There are three memory blocks in each of the PIC16F87X MCUs. The Program Memory and Data Memory have separate buses so that concurrent access can occur and is detailed in this section. The EEPROM data memory block is detailed in Section 4.0.

Additional information on device memory may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

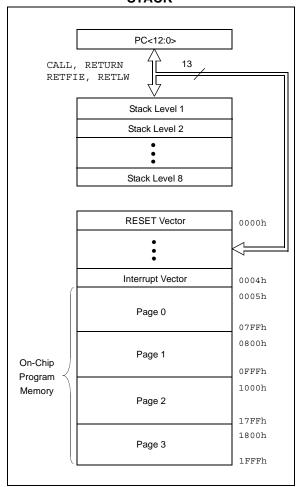

#### FIGURE 2-1: PIC16F877/876 PROGRAM MEMORY MAP AND STACK

## 2.1 **Program Memory Organization**

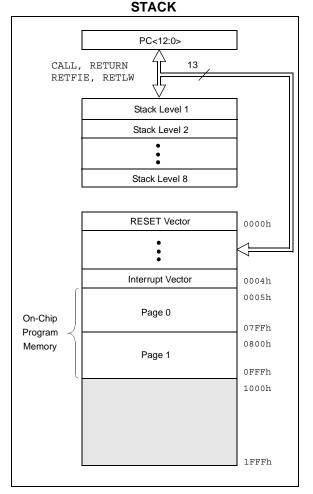

The PIC16F87X devices have a 13-bit program counter capable of addressing an  $8K \times 14$  program memory space. The PIC16F877/876 devices have  $8K \times 14$  words of FLASH program memory, and the PIC16F873/874 devices have  $4K \times 14$ . Accessing a location above the physically implemented address will cause a wraparound.

The RESET vector is at 0000h and the interrupt vector is at 0004h.

## FIGURE 2-2: PIC16F874/873 PROGRAM MEMORY MAP AND

## 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 2-1. The Special Function Registers can be classified into two sets: core (CPU) and peripheral. Those registers associated with the core functions are described in detail in this section. Those related to the operation of the peripheral features are described in detail in the peripheral features section.

TABLE 2-1:

SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                | Bit 6                                                                                         | Bit 5         | Bit 4          | Bit 3          | Bit 2             | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Details<br>on<br>page: |

|----------------------|---------|----------------------|-----------------------------------------------------------------------------------------------|---------------|----------------|----------------|-------------------|-------------|---------|--------------------------|------------------------|

| Bank 0               |         |                      |                                                                                               |               |                |                |                   |             |         |                          |                        |

| 00h <sup>(3)</sup>   | INDF    | Addressing           | ddressing this location uses contents of FSR to address data memory (not a physical register) |               |                |                |                   |             |         |                          |                        |

| 01h                  | TMR0    | Timer0 Mc            | dule Registe                                                                                  | er            |                |                |                   |             |         | xxxx xxxx                | 47                     |

| 02h <sup>(3)</sup>   | PCL     | Program C            | Counter (PC)                                                                                  | Least Signif  | icant Byte     |                |                   |             |         | 0000 0000                | 26                     |

| 03h <sup>(3)</sup>   | STATUS  | IRP                  | RP1                                                                                           | RP0           | TO             | PD             | Z                 | DC          | С       | 0001 1xxx                | 18                     |

| 04h <sup>(3)</sup>   | FSR     | Indirect Da          | ata Memory /                                                                                  | Address Poir  | nter           |                |                   |             |         | xxxx xxxx                | 27                     |

| 05h                  | PORTA   | _                    | _                                                                                             | PORTA Da      | ta Latch whei  | n written: POI | RTA pins whe      | n read      |         | 0x 0000                  | 29                     |

| 06h                  | PORTB   | PORTB Da             | ata Latch wh                                                                                  | en written: P | ORTB pins w    | /hen read      |                   |             |         | xxxx xxxx                | 31                     |

| 07h                  | PORTC   | PORTC D              | ata Latch wh                                                                                  | en written: F | ORTC pins v    | vhen read      |                   |             |         | xxxx xxxx                | 33                     |

| 08h <sup>(4)</sup>   | PORTD   | PORTD D              | ata Latch wh                                                                                  | en written: F | ORTD pins v    | vhen read      |                   |             |         | xxxx xxxx                | 35                     |

| 09h <sup>(4)</sup>   | PORTE   | _                    | _                                                                                             | _             | _              | _              | RE2               | RE1         | RE0     | xxx                      | 36                     |

| 0Ah <sup>(1,3)</sup> | PCLATH  | _                    |                                                                                               |               | Write Buffer   | for the upper  | r 5 bits of the I | Program Cou | unter   | 0 0000                   | 26                     |

| 0Bh <sup>(3)</sup>   | INTCON  | GIE                  | PEIE                                                                                          | T0IE          | INTE           | RBIE           | T0IF              | INTF        | RBIF    | 0000 000x                | 20                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF                                                                                          | RCIF          | TXIF           | SSPIF          | CCP1IF            | TMR2IF      | TMR1IF  | 0000 0000                | 22                     |

| 0Dh                  | PIR2    | —                    | (5)                                                                                           | _             | EEIF           | BCLIF          | —                 |             | CCP2IF  | -r-0 00                  | 24                     |

| 0Eh                  | TMR1L   | Holding re           | Holding register for the Least Significant Byte of the 16-bit TMR1 Register                   |               |                |                |                   |             |         | xxxx xxxx                | 52                     |

| 0Fh                  | TMR1H   | Holding re           | gister for the                                                                                | Most Signifi  | cant Byte of t | the 16-bit TM  | R1 Register       |             |         | xxxx xxxx                | 52                     |

| 10h                  | T1CON   | _                    | _                                                                                             | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC            | TMR1CS      | TMR10N  | 00 0000                  | 51                     |

| 11h                  | TMR2    | Timer2 Mo            | dule Registe                                                                                  | er            |                |                |                   |             |         | 0000 0000                | 55                     |

| 12h                  | T2CON   | _                    | TOUTPS3                                                                                       | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON            | T2CKPS1     | T2CKPS0 | -000 0000                | 55                     |

| 13h                  | SSPBUF  | Synchrono            | ous Serial Po                                                                                 | rt Receive B  | uffer/Transm   | it Register    |                   |             |         | xxxx xxxx                | 70, 73                 |

| 14h                  | SSPCON  | WCOL                 | SSPOV                                                                                         | SSPEN         | CKP            | SSPM3          | SSPM2             | SSPM1       | SSPM0   | 0000 0000                | 67                     |

| 15h                  | CCPR1L  | Capture/C            | ompare/PWI                                                                                    | M Register1   | (LSB)          |                |                   |             |         | XXXX XXXX                | 57                     |

| 16h                  | CCPR1H  | Capture/C            | ompare/PWI                                                                                    | M Register1   | (MSB)          |                |                   |             |         | XXXX XXXX                | 57                     |

| 17h                  | CCP1CON | _                    | _                                                                                             | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2            | CCP1M1      | CCP1M0  | 00 0000                  | 58                     |

| 18h                  | RCSTA   | SPEN                 | RX9                                                                                           | SREN          | CREN           | ADDEN          | FERR              | OERR        | RX9D    | 0000 000x                | 96                     |

| 19h                  | TXREG   | USART Tr             | ansmit Data                                                                                   | Register      |                |                |                   |             |         | 0000 0000                | 99                     |

| 1Ah                  | RCREG   | USART Re             | eceive Data I                                                                                 | Register      |                |                |                   |             |         | 0000 0000                | 101                    |

| 1Bh                  | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB)                                                           |               |                |                |                   |             |         | xxxx xxxx                | 57                     |

| 1Ch                  | CCPR2H  | Capture/C            | ompare/PWI                                                                                    | M Register2   | (MSB)          |                |                   |             |         | xxxx xxxx                | 57                     |

| 1Dh                  | CCP2CON | _                    | _                                                                                             | CCP2X         | CCP2Y          | CCP2M3         | CCP2M2            | CCP2M1      | CCP2M0  | 00 0000                  | 58                     |

| 1Eh                  | ADRESH  | A/D Result           | t Register Hi                                                                                 | gh Byte       |                |                |                   |             |         | xxxx xxxx                | 116                    |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0                                                                                         | CHS2          | CHS1           | CHS0           | GO/DONE           | _           | ADON    | 0000 00-0                | 111                    |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

3: These registers can be addressed from any bank.

4: PORTD, PORTE, TRISD, and TRISE are not physically implemented on PIC16F873/876 devices; read as '0'.

5: PIR2<6> and PIE2<6> are reserved on these devices; always maintain these bits clear.

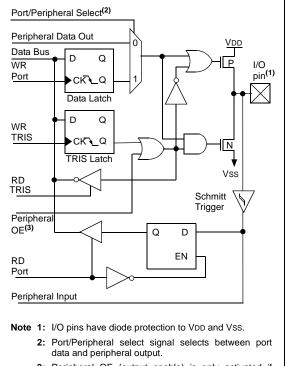

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

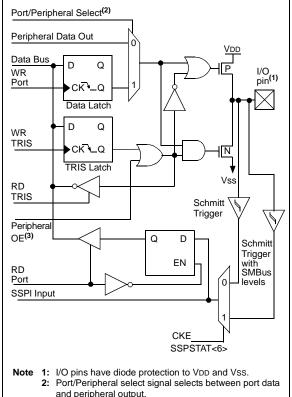

When the  $I^2C$  module is enabled, the PORTC<4:3> pins can be configured with normal  $I^2C$  levels, or with SMBus levels by using the CKE bit (SSPSTAT<6>).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination, should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### FIGURE 3-5: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<2:0>, RC<7:5>

**3:** Peripheral OE (output enable) is only activated if peripheral select is active.

## FIGURE 3-6:

#### PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE) RC<4:3>

Peripheral OE (output enable) is only activated if peripheral select is active.

## 7.1 Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device RESET (POR, MCLR Reset, WDT Reset, or BOR)

TMR2 is not cleared when T2CON is written.

## 7.2 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the SSP module, which optionally uses it to generate shift clock.

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6                    | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|-----------------------|--------|----------------------|--------------------------|---------|---------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                     | TOIE    | INTE    | RBIE    | T0IF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF                     | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE                     | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 Mod           | Timer2 Module's Register |         |         |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                    | TOUTPS3                  | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri          | Timer2 Period Register   |         |         |         |        |         |         | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module. **Note 1:** Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POF<br>BO | R,   | Valu<br>all o<br>RES | ther |

|------------------------|---------|----------------------|-------------------------------------|-------------|---------|---------|--------|---------|---------|--------------------|------|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE        | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 (             | 000x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000               | 0000 | 0000                 | 0000 |

| 0Dh                    | PIR2    | _                    | —                                   | _           | _       | —       | _      | _       | CCP2IF  |                    | 0    |                      | 0    |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000               | 0000 | 0000                 | 0000 |

| 8Dh                    | PIE2    | —                    | —                                   | —           | _       | —       | _      | —       | CCP2IE  |                    | 0    |                      | 0    |

| 87h                    | TRISC   | PORTC D              | Data Directio                       | n Register  |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Regi                        | ster        |         |         |        |         |         | 0000               | 0000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Perio                       | od Register |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 12h                    | T2CON   | —                    | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 (             | 0000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PW                          | /M Register | 1 (LSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PW                          | /M Register | 1 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | —                    |                                     | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 (               | 0000 | 00                   | 0000 |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |             |         |         |        |         |         |                    | xxxx | uuuu                 | uuuu |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PW                          | /M Register | 2 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 1Dh                    | CCP2CON | —                    | —                                   | CCP2X       | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 (               | 0000 | 00                   | 0000 |

| <b>TABLE 8-5</b> : | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--------------------|-------------------------------------------------|

|--------------------|-------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

#### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address                | Name    | Bit 7                  | Bit 6                                                    | Bit 5        | Bit 4       | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR,<br>WDT |

|------------------------|---------|------------------------|----------------------------------------------------------|--------------|-------------|-----------|--------|--------|--------|-----------------------|------------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE                                                     | TOIE         | INTE        | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u                          |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup>   | ADIF                                                     | RCIF         | TXIF        | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                          |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup>   | ADIE                                                     | RCIE         | TXIE        | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                          |

| 0Dh                    | PIR2    | _                      | (2)                                                      | _            | EEIF        | BCLIF     | _      | _      | CCP2IF | -r-0 00               | -r-0 00                            |

| 8Dh                    | PIE2    | _                      | (2)                                                      | _            | EEIE        | BCLIE     | _      | —      | CCP2IE | -r-0 00               | -r-0 00                            |

| 13h                    | SSPBUF  | Synchrono              | ous Serial Por                                           | rt Receive I | Buffer/Trar | nsmit Reg | ister  |        |        | xxxx xxxx             | uuuu uuuu                          |

| 14h                    | SSPCON  | WCOL                   | SSPOV                                                    | SSPEN        | CKP         | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000 0000             | 0000 0000                          |

| 91h                    | SSPCON2 | GCEN                   | ACKSTAT                                                  | ACKDT        | ACKEN       | RCEN      | PEN    | RSEN   | SEN    | 0000 0000             | 0000 0000                          |

| 93h                    | SSPADD  | I <sup>2</sup> C Slave | I <sup>2</sup> C Slave Address/Master Baud Rate Register |              |             |           |        |        |        | 0000 0000             | 0000 0000                          |

| 94h                    | SSPSTAT | SMP                    | CKE                                                      | D/A          | Р           | S         | R/W    | UA     | BF     | 0000 0000             | 0000 0000                          |

## TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

**Note 1:** These bits are reserved on PIC16F873/876 devices; always maintain these bits clear.

2: These bits are reserved on these devices; always maintain these bits clear.

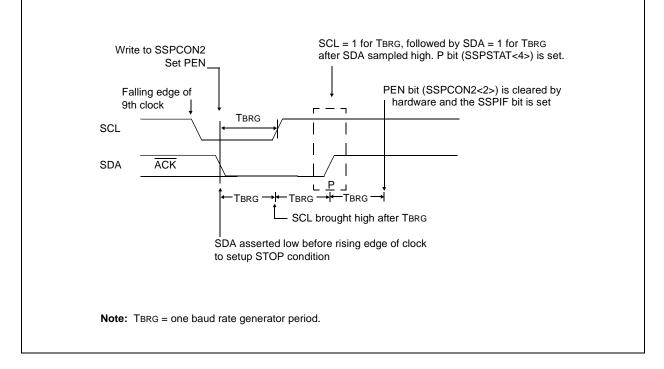

## 9.2.14 STOP CONDITION TIMING

A STOP bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one TBRG (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 9-17).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a STOP bit is detected (i.e., bus is free).

#### 9.2.14.1 WCOL Status Flag

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

## PIC16F87X

NOTES:

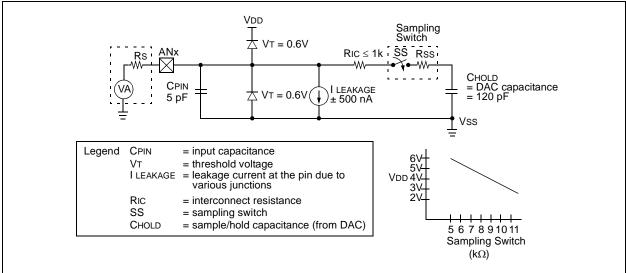

## 11.1 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-2. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the impedance is decreased, the acquisition time may be decreased.

## EQUATION 11-1: ACQUISITION TIME

After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 11-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the  $PIC^{\textcircled{R}}$  MCU Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient    |

|------|---------------------------------------------------------------------------------------------|

|      | = $TAMP + TC + TCOFF$                                                                       |

|      | $= 2\mu s + TC + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$                         |

| TC   | = CHOLD (RIC + RSS + RS) $In(1/2047)$                                                       |

|      | = $-120 \text{pF} (1 \text{k}\Omega + 7 \text{k}\Omega + 10 \text{k}\Omega) \ln(0.0004885)$ |

|      | $= 16.47 \mu s$                                                                             |

| TACQ | = $2\mu s + 16.47\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$                |

|      | $= 19.72 \mu s$                                                                             |

| L    |                                                                                             |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

- **4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time, the holding capacitor is not connected to the selected A/D input channel.

#### FIGURE 11-2: ANALOG INPUT MODEL

## 12.0 SPECIAL FEATURES OF THE CPU

All PIC16F87X devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87X devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the  $PIC^{\mathbb{R}}$  MCU Mid-Range Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

## REGISTER 12-1: CONFIGURATION WORD (ADDRESS 2007h)<sup>(1)</sup>

| CP1              | CP0 | DEBUG                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                  | WRT     | CPD | LVP | BODEN | CP1 | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |

|------------------|-----|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|-------|-----|-----|-------|------|-------|-------|

| bit13<br>bit 13- | 12, |                                                                                                                | CP1:CP0: FLASH Program Memory Code Protection bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                  |         |     |     |       |     |     |       |      |       | bit0  |

| bit 5-4          |     | 10 = 1F00<br>10 = 0F00<br>01 = 1000<br>01 = 0800<br>00 = 0000                                                  | 11 = Code protection off<br>10 = 1F00h to 1FFFh code protected (PIC16F877, 876)<br>10 = 0F00h to 0FFFh code protected (PIC16F874, 873)<br>01 = 1000h to 1FFFh code protected (PIC16F877, 876)<br>01 = 0800h to 0FFFh code protected (PIC16F874, 873)<br>00 = 0000h to 1FFFh code protected (PIC16F877, 876)<br>00 = 0000h to 0FFFh code protected (PIC16F874, 873) |         |     |     |       |     |     |       |      |       |       |

| bit 11           |     | 1 = In-Cir                                                                                                     | <b>DEBUG:</b> In-Circuit Debugger Mode<br>1 = In-Circuit Debugger disabled, RB6 and RB7 are general purpose I/O pins<br>0 = In-Circuit Debugger enabled, RB6 and RB7 are dedicated to the debugger.                                                                                                                                                                |         |     |     |       |     |     |       |      |       |       |

| bit 10           |     | Unimpler                                                                                                       | nented:                                                                                                                                                                                                                                                                                                                                                            | Read as | '1' |     |       |     |     |       |      |       |       |

| bit 9            |     | 1 = Unpro                                                                                                      | WRT: FLASH Program Memory Write Enable<br>1 = Unprotected program memory may be written to by EECON control<br>0 = Unprotected program memory may not be written to by EECON control                                                                                                                                                                               |         |     |     |       |     |     |       |      |       |       |

| bit 8            |     | <b>CPD:</b> Data EE Memory Code Protection<br>1 = Code protection off<br>0 = Data EEPROM memory code protected |                                                                                                                                                                                                                                                                                                                                                                    |         |     |     |       |     |     |       |      |       |       |

| bit 7            |     | 1 = RB3/F                                                                                                      | <b>LVP</b> : Low Voltage In-Circuit Serial Programming Enable bit<br>1 = RB3/PGM pin has PGM function, low voltage programming enabled<br>0 = RB3 is digital I/O, HV on MCLR must be used for programming                                                                                                                                                          |         |     |     |       |     |     |       |      |       |       |

| bit 6            |     | 1 = BOR                                                                                                        | BODEN: Brown-out Reset Enable bit <sup>(3)</sup><br>1 = BOR enabled<br>0 = BOR disabled                                                                                                                                                                                                                                                                            |         |     |     |       |     |     |       |      |       |       |

| bit 3            |     | 1 = PWR                                                                                                        | <b>PWRTE</b> : Power-up Timer Enable bit <sup>(3)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                                   |         |     |     |       |     |     |       |      |       |       |

| bit 2            |     | 1 = WDT                                                                                                        | WDTE: Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                                                                                                             |         |     |     |       |     |     |       |      |       |       |

| bit 1-0          |     | 11 = RC 0<br>10 = HS 0<br>01 = XT 0                                                                            | FOSC1:FOSC0: Oscillator Selection bits<br>11 = RC oscillator<br>10 = HS oscillator<br>01 = XT oscillator<br>00 = LP oscillator                                                                                                                                                                                                                                     |         |     |     |       |     |     |       |      |       |       |

- **Note 1:** The erased (unprogrammed) value of the configuration word is 3FFFh.

- 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

- **3:** Enabling Brown-out Reset automatically enables Power-up Timer (PWRT), regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled any time Brown-out Reset is enabled.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| INCF                                                                                                                                                                                | CF Increment f                                                  |                  | Inclusive OR W with f                                                                                                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                                                                                                                             | [ <i>label</i> ] INCF f,d                                       | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                            |  |  |  |  |

| Operands:                                                                                                                                                                           | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                       |  |  |  |  |

| Operation:                                                                                                                                                                          | (f) + 1 $\rightarrow$ (destination)                             | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                              |  |  |  |  |

| Status Affected: Z                                                                                                                                                                  |                                                                 | Status Affected: | Z                                                                                                                                                                     |  |  |  |  |

| Description: The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |                                                                 | Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1<br>the result is placed back in<br>register 'f'. |  |  |  |  |

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                               |                                                      |     |    |                                                                    |  |  |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------|-------------------------------|------------------------------------------------------|-----|----|--------------------------------------------------------------------|--|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                      |                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |    |                                                                    |  |  |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                            | Min Typ† Max Units Conditions |                                                      |     |    |                                                                    |  |  |

|                                                                                  | IDD    | Supply Current <sup>(2,5)</sup>                      |                               |                                                      |     |    |                                                                    |  |  |

| D010                                                                             |        | 16LF87X                                              | —                             | 0.6                                                  | 2.0 | mA | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V               |  |  |

| D010                                                                             |        | 16F87X                                               | —                             | 1.6                                                  | 4   | mA | RC osc configurations<br>Fosc = 4 MHz, VDD = 5.5V                  |  |  |

| D010A                                                                            |        | 16LF87X                                              | —                             | 20                                                   | 35  | μA | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V,<br>WDT disabled |  |  |

| D013                                                                             |        | 16F87X                                               | —                             | 7                                                    | 15  | mA | HS osc configuration,<br>Fosc = 20 MHz, VDD = 5.5V                 |  |  |

| D015                                                                             | ∆IBOR  | Brown-out<br>Reset Current <sup>(6)</sup>            | —                             | 85                                                   | 200 | μΑ | BOR enabled, VDD = 5.0V                                            |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

- **Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

# PIC16F87X

## 15.1 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| <b>PIC16LF873/874/876/877-04</b><br>(Commercial, Industrial)                     |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                                                      |     |       |                                            |  |  |

|----------------------------------------------------------------------------------|--------|------------------------------------------------------|-----|------------------------------------------------------|-----|-------|--------------------------------------------|--|--|

| PIC16F873/874/876/877-04<br>PIC16F873/874/876/877-20<br>(Commercial, Industrial) |        |                                                      |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |       |                                            |  |  |

| Param<br>No.                                                                     | Symbol | Characteristic/<br>Device                            | Min | Тур†                                                 | Мах | Units | Conditions                                 |  |  |

| -                                                                                | IPD    | Power-down Current <sup>(3,5)</sup>                  |     |                                                      |     |       |                                            |  |  |

| D020                                                                             |        | 16LF87X                                              | _   | 7.5                                                  | 30  | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D020                                                                             |        | 16F87X                                               | _   | 10.5                                                 | 42  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021                                                                             |        | 16LF87X                                              | _   | 0.9                                                  | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>0°C to +70°C   |  |  |

| D021                                                                             |        | 16F87X                                               | _   | 1.5                                                  | 16  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021A                                                                            |        | 16LF87X                                              |     | 0.9                                                  | 5   | μΑ    | VDD = 3.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D021A                                                                            |        | 16F87X                                               |     | 1.5                                                  | 19  | μΑ    | VDD = 4.0V, WDT enabled,<br>-40°C to +85°C |  |  |

| D023                                                                             | ΔIBOR  | Brown-out<br>Reset Current <sup>(6)</sup>            | _   | 85                                                   | 200 | μΑ    | BOR enabled, VDD = 5.0V                    |  |  |

Legend: Rows with standard voltage device data only are shaded for improved readability.

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only, and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading, switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD;

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

## 15.4 DC Characteristics: PIC16F873/874/876/877-04 (Extended) PIC16F873/874/876/877-10 (Extended) (Continued)

| DC CHARACTERISTICS |       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$<br>Operating voltage VDD range as described in DC specification<br>(Section 15.1) |              |   |       |            |                                                                        |  |  |

|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---|-------|------------|------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym   | Characteristic                                                                                                                                                                                             | Min Typ† Max |   | Units | Conditions |                                                                        |  |  |

|                    | Vol   | Output Low Voltage                                                                                                                                                                                         |              |   |       |            |                                                                        |  |  |

| D080A              |       | I/O ports                                                                                                                                                                                                  | —            | — | 0.6   | V          | IOL = 7.0 mA, VDD = 4.5V                                               |  |  |

| D083A              |       | OSC2/CLKOUT (RC osc config)                                                                                                                                                                                | —            | — | 0.6   | V          | IOL = 1.2 mA, VDD = 4.5V                                               |  |  |

|                    | Voн   | Output High Voltage                                                                                                                                                                                        |              |   |       |            |                                                                        |  |  |

| D090A              |       | I/O ports <sup>(3)</sup>                                                                                                                                                                                   | Vdd - 0.7    | — | _     | V          | Юн = -2.5 mA, VDD = 4.5V                                               |  |  |

| D092A              |       | OSC2/CLKOUT (RC osc config)                                                                                                                                                                                | Vdd - 0.7    | — |       | V          | Юн = -1.0 mA, VDD = 4.5V                                               |  |  |

| D150*              | Vod   | Open Drain High Voltage                                                                                                                                                                                    | —            | — | 8.5   | V          | RA4 pin                                                                |  |  |

|                    |       |                                                                                                                                                                                                            |              |   |       |            |                                                                        |  |  |

| D100               | Cosc2 | OSC2 pin                                                                                                                                                                                                   | _            | — | 15    | pF         | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |  |  |

| D101               | Сю    | All I/O pins and OSC2 (RC mode)                                                                                                                                                                            | _            | _ | 50    | pF         |                                                                        |  |  |

| D102               | Св    | SCL, SDA (I <sup>2</sup> C mode)                                                                                                                                                                           | —            | — | 400   | pF         |                                                                        |  |  |

|                    |       | Data EEPROM Memory                                                                                                                                                                                         |              |   |       |            |                                                                        |  |  |

| D120               | ED    | Endurance                                                                                                                                                                                                  | 100K         | — | _     | E/W        | 25°C at 5V                                                             |  |  |

| D121               | Vdrw  | VDD for read/write                                                                                                                                                                                         | Vmin         | — | 5.5   | V          | Using EECON to read/write<br>VMIN = min. operating voltage             |  |  |

| D122               | TDEW  | ······                                                                                                                                                                                                     | _            | 4 | 8     | ms         |                                                                        |  |  |

|                    |       | Program FLASH Memory                                                                                                                                                                                       |              |   |       |            |                                                                        |  |  |

| D130               | Eр    | Endurance                                                                                                                                                                                                  | 1000         | — |       | E/W        | 25°C at 5V                                                             |  |  |

| D131               | Vpr   | VDD for read                                                                                                                                                                                               | VMIN         | — | 5.5   | V          | VMIN = min operating voltage                                           |  |  |

| D132A              |       | VDD for erase/write                                                                                                                                                                                        | VMIN         | — | 5.5   | V          | Using EECON to read/write,<br>VMIN = min. operating voltage            |  |  |

| D133               | TPEW  | Erase/Write cycle time                                                                                                                                                                                     | —            | 4 | 8     | ms         |                                                                        |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16F87X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.