Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 2-4: PIC16F874/873 REGISTER FILE MAP

| ,                              | File<br>Address             | A                                                                     | File<br>ddress | /                   | File<br>Address |                         | File<br>Addres |

|--------------------------------|-----------------------------|-----------------------------------------------------------------------|----------------|---------------------|-----------------|-------------------------|----------------|

| Indirect addr. <sup>(*)</sup>  | 00h                         | Indirect addr.(*)                                                     | 80h            | Indirect addr.(*)   | 100h            | Indirect addr.(*)       | 180h           |

| TMR0                           | 01h                         | OPTION_REG                                                            | 81h            | TMR0                | 101h            | OPTION_REG              | 181h           |

| PCL                            | 02h                         | PCL                                                                   | 82h            | PCL                 | 102h            | PCL                     | 182h           |

| STATUS                         | 03h                         | STATUS                                                                | 83h            | STATUS              | 103h            | STATUS                  | 183h           |

| FSR                            | 04h                         | FSR                                                                   | 84h            | FSR                 | 104h            | FSR                     | 184h           |

| PORTA                          | 05h                         | TRISA                                                                 | 85h            |                     | 105h            |                         | 185h           |

| PORTB                          | 06h                         | TRISB                                                                 | 86h            | PORTB               | 106h            | TRISB                   | 186h           |

| PORTC                          | 07h                         | TRISC                                                                 | 87h            |                     | 107h            |                         | 187h           |

| PORTD <sup>(1)</sup>           | 08h                         | TRISD <sup>(1)</sup>                                                  | 88h            |                     | 108h            |                         | 188h           |

| PORTE <sup>(1)</sup>           | 09h                         | TRISE <sup>(1)</sup>                                                  | 89h            |                     | 109h            |                         | 189h           |

| PCLATH                         | 0Ah                         | PCLATH                                                                | 8Ah            | PCLATH              | 10Ah            | PCLATH                  | 18Ah           |

| INTCON                         | 0Bh                         | INTCON                                                                | 8Bh            | INTCON              | 10Bh            | INTCON                  | 18Bh           |

| PIR1                           | 0Ch                         | PIE1                                                                  | 8Ch            | EEDATA              | 10Ch            | EECON1                  | 18Cł           |

| PIR2                           | 0Dh                         | PIE2                                                                  | 8Dh            | EEADR               | 10Dh            | EECON2                  | 18Dł           |

| TMR1L                          | 0Eh                         | PCON                                                                  | 8Eh            | EEDATH              | 10Eh            | Reserved <sup>(2)</sup> | 18Eh           |

| TMR1H                          | 0Fh                         |                                                                       | 8Fh            | EEADRH              | 10Fh            | Reserved <sup>(2)</sup> | 18Fh           |

| T1CON                          | 10h                         |                                                                       | 90h            |                     | 110h            |                         | 190h           |

| TMR2                           | 11h                         | SSPCON2                                                               | 91h            |                     |                 |                         |                |

| T2CON                          | 12h                         | PR2                                                                   | 92h            |                     |                 |                         |                |

| SSPBUF                         | 13h                         | SSPADD                                                                | 93h            |                     |                 |                         |                |

| SSPCON                         | 14h                         | SSPSTAT                                                               | 94h            |                     |                 |                         |                |

| CCPR1L                         | 15h                         |                                                                       | 95h            |                     |                 |                         |                |

| CCPR1H                         | 16h                         |                                                                       | 96h            |                     |                 |                         |                |

| CCP1CON                        | 17h                         |                                                                       | 97h            |                     |                 |                         |                |

| RCSTA                          | 18h                         | TXSTA                                                                 | 98h            |                     |                 |                         |                |

| TXREG                          | 19h                         | SPBRG                                                                 | 99h            |                     |                 |                         |                |

| RCREG                          | 1Ah                         |                                                                       | 9Ah            |                     |                 |                         |                |

| CCPR2L                         | 1Bh                         |                                                                       | 9Bh            |                     |                 |                         |                |

| CCPR2H                         | 1Ch                         |                                                                       | 9Ch            |                     |                 |                         |                |

| CCP2CON                        | 1Dh                         |                                                                       | 9Dh            |                     |                 |                         |                |

| ADRESH                         | 1Eh                         | ADRESL                                                                | 9Eh            |                     |                 |                         |                |

| ADCON0                         | 1Fh                         | ADCON1                                                                | 9Fh            |                     | 1206            |                         | 1A0h           |

|                                | 20h                         |                                                                       | A0h            |                     | 120h            |                         |                |

| General<br>Purpose<br>Register |                             | General<br>Purpose<br>Register                                        |                | accesses<br>20h-7Fh |                 | accesses<br>A0h - FFh   |                |

| 96 Bytes                       |                             | 96 Bytes                                                              |                | 2011 11 11          | 16Fh<br>170h    |                         | 1EFt<br>1F0h   |

|                                | 754                         |                                                                       |                |                     | 1756            |                         | 4              |

| Bank 0                         | J 7Fh                       | Bank 1                                                                | FFh            | Bank 2              | 17Fh            | Bank 3                  | 1FFł           |

| * Not a<br>Note 1: These       | physical reg<br>e registers | data memory locat<br>gister.<br>are not implemen<br>are reserved, mai | ted on the     | e PIC16F873.        |                 |                         |                |

## 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PIC<sup>®</sup> MCU Mid-Range Reference Manual, (DS33023).

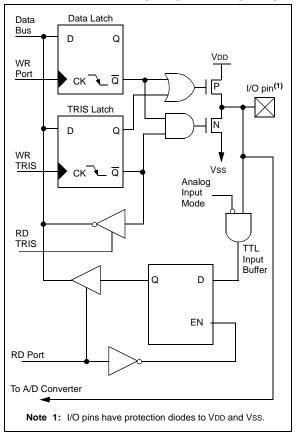

### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, the value is modified and then written to the port data latch.

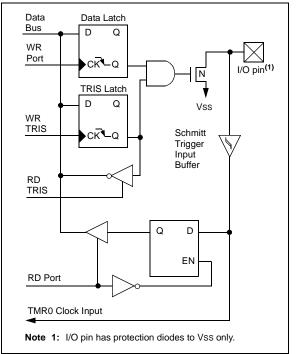

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

| Note: | On a Power-on Reset, these pins are con-  |

|-------|-------------------------------------------|

|       | figured as analog inputs and read as '0'. |

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | Bank0                 |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0x06    |     | ; | Configure all pins    |

| MOVWF | ADCON1  |     | ; | as digital inputs     |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6>are always  |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

|       |         |     |   |                       |

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

## FIGURE 3-2:

#### BLOCK DIAGRAM OF RA4/T0CKI PIN

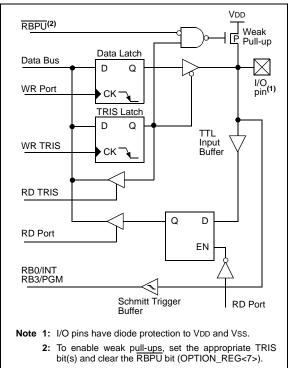

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the Low Voltage Programming function: RB3/PGM, RB6/PGC and RB7/PGD. The alternate functions of these pins are described in the Special Features Section.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

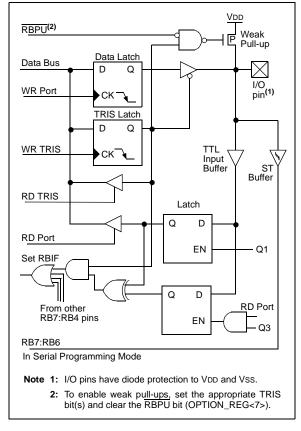

Four of the PORTB pins, RB7:RB4, have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with software configureable pull-ups on these four pins, allow easy interface to a keypad and make it possible for wake-up on key depression. Refer to the Embedded Control Handbook, *"Implementing Wake-up on Key Strokes"* (AN552).

RB0/INT is an external interrupt input pin and is configured using the INTEDG bit (OPTION\_REG<6>).

RB0/INT is discussed in detail in Section 12.10.1.

#### FIGURE 3-4: BLOCK DIAGRAM OF RB7:RB4 PINS

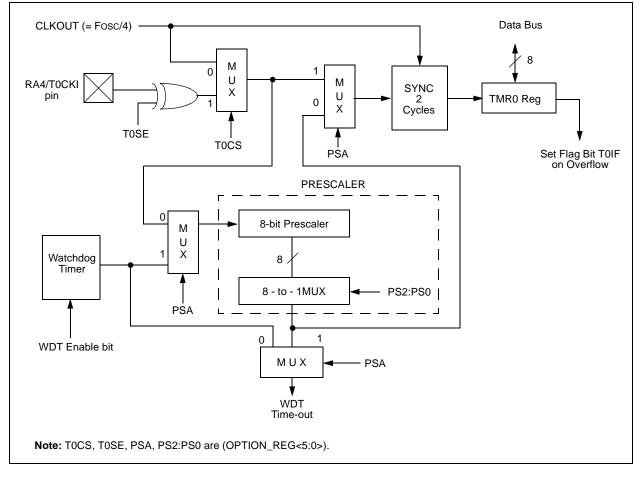

## 5.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 5-1 is a block diagram of the Timer0 module and the prescaler shared with the WDT.

Additional information on the Timer0 module is available in the PIC<sup>®</sup> MCU Mid-Range Family Reference Manual (DS33023).

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register. Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In Counter mode, Timer0 will increment either on every rising, or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 5.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler is not readable or writable. Section 5.3 details the operation of the prescaler.

## 5.1 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP.

FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| REGISTER 0-1: | CUPICON                                                                                                            | REGIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | ON REGIS     | SIER (ADDI | (E33: 1/1   | vidnj        |        |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|------------|-------------|--------------|--------|--|--|

|               | U-0                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0      | R/W-0        | R/W-0      | R/W-0       | R/W-0        | R/W-0  |  |  |

|               | —                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CCPxX      | CCPxY        | CCPxM3     | CCPxM2      | CCPxM1       | CCPxM0 |  |  |

|               | bit 7                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |              |            |             |              | bit 0  |  |  |

|               |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |              |            |             |              |        |  |  |

| bit 7-6       | •                                                                                                                  | Jnimplemented: Read as '0' CCPxX:CCPxY: PWM Least Significant bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |              |            |             |              |        |  |  |

| bit 5-4       |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Least Sign | ificant bits |            |             |              |        |  |  |

|               | <u>Capture m</u><br>Unused                                                                                         | ode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |              |            |             |              |        |  |  |

|               | <u>Compare mode:</u><br>Unused                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |              |            |             |              |        |  |  |

|               | <u>PWM mode:</u><br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |              |            |             |              |        |  |  |

| bit 3-0       | CCPxM3:C                                                                                                           | CPxM0: C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPx Mode S | Select bits  |            |             |              |        |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>una<br>1011 = Co<br>res | <ul> <li>0000 = Capture/Compare/PWM disabled (resets CCPx module)</li> <li>0100 = Capture mode, every falling edge</li> <li>0101 = Capture mode, every rising edge</li> <li>0110 = Capture mode, every 4th rising edge</li> <li>0111 = Capture mode, every 16th rising edge</li> <li>1000 = Compare mode, every 16th rising edge</li> <li>1001 = Compare mode, set output on match (CCPxIF bit is set)</li> <li>1001 = Compare mode, clear output on match (CCPxIF bit is set)</li> <li>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)</li> <li>1011 = Compare mode, trigger special event (CCPxIF bit is set, CCPx pin is unaffected); CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled)</li> <li>11xx = PWM mode</li> </ul> |            |              |            |             |              |        |  |  |

|               | Legend:                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |              |            |             |              |        |  |  |

|               | R = Reada                                                                                                          | ble bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VV = V     | Vritable bit | U = Unim   | plemented l | bit, read as | ʻ0'    |  |  |

'1' = Bit is set

- n = Value at POR

## REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

| Address                | Name    | Bit 7                | Bit 6                               | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>POF<br>BO | R,   | Valu<br>all o<br>RES | ther |

|------------------------|---------|----------------------|-------------------------------------|-------------|---------|---------|--------|---------|---------|--------------------|------|----------------------|------|

| 0Bh,8Bh,<br>10Bh, 18Bh | INTCON  | GIE                  | PEIE                                | TOIE        | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 (             | 000x | 0000                 | 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF        | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000               | 0000 | 0000                 | 0000 |

| 0Dh                    | PIR2    | _                    | —                                   | _           | _       | —       | _      | _       | CCP2IF  |                    | 0    |                      | 0    |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE        | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000               | 0000 | 0000                 | 0000 |

| 8Dh                    | PIE2    | —                    | —                                   | —           | _       | —       | _      | —       | CCP2IE  |                    | 0    |                      | 0    |

| 87h                    | TRISC   | PORTC D              | PORTC Data Direction Register       |             |         |         |        |         |         |                    |      | 1111                 | 1111 |

| 11h                    | TMR2    | Timer2 M             | odule's Regi                        | ster        |         |         |        |         |         | 0000               | 0000 | 0000                 | 0000 |

| 92h                    | PR2     | Timer2 M             | odule's Perio                       | od Register |         |         |        |         |         | 1111 :             | 1111 | 1111                 | 1111 |

| 12h                    | T2CON   | —                    | TOUTPS3                             | TOUTPS2     | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 (             | 0000 | -000                 | 0000 |

| 15h                    | CCPR1L  | Capture/C            | Compare/PW                          | /M Register | 1 (LSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 16h                    | CCPR1H  | Capture/C            | Compare/PW                          | /M Register | 1 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 17h                    | CCP1CON | —                    |                                     | CCP1X       | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00 (               | 0000 | 00                   | 0000 |

| 1Bh                    | CCPR2L  | Capture/C            | Capture/Compare/PWM Register2 (LSB) |             |         |         |        |         |         |                    | xxxx | uuuu                 | uuuu |

| 1Ch                    | CCPR2H  | Capture/C            | Compare/PW                          | /M Register | 2 (MSB) |         |        |         |         | XXXX X             | xxxx | uuuu                 | uuuu |

| 1Dh                    | CCP2CON | —                    | —                                   | CCP2X       | CCP2Y   | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00 (               | 0000 | 00                   | 0000 |

| <b>TABLE 8-5</b> : | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--------------------|-------------------------------------------------|

|--------------------|-------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16F873/876; always maintain these bits clear.

#### 9.2.3 SLEEP OPERATION

While in SLEEP mode, the I<sup>2</sup>C module can receive addresses or data. When an address match or complete byte transfer occurs, wake the processor from SLEEP (if the SSP interrupt is enabled).

#### 9.2.4 EFFECTS OF A RESET

A RESET disables the SSP module and terminates the current transfer.

| Address                | Name    | Bit 7                                                    | Bit 6          | Bit 5        | Bit 4       | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR,<br>WDT |

|------------------------|---------|----------------------------------------------------------|----------------|--------------|-------------|-----------|--------|--------|--------|-----------------------|------------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                                                      | PEIE           | TOIE         | INTE        | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x             | 0000 000u                          |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup>                                     | ADIF           | RCIF         | TXIF        | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                          |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup>                                     | ADIE           | RCIE         | TXIE        | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                          |

| 0Dh                    | PIR2    | _                                                        | (2)            | _            | EEIF        | BCLIF     | _      | _      | CCP2IF | -r-0 00               | -r-0 00                            |

| 8Dh                    | PIE2    | _                                                        | (2)            | _            | EEIE        | BCLIE     | _      | —      | CCP2IE | -r-0 00               | -r-0 00                            |

| 13h                    | SSPBUF  | Synchrono                                                | ous Serial Por | rt Receive I | Buffer/Trar | nsmit Reg | ister  |        |        | xxxx xxxx             | uuuu uuuu                          |

| 14h                    | SSPCON  | WCOL                                                     | SSPOV          | SSPEN        | CKP         | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000 0000             | 0000 0000                          |

| 91h                    | SSPCON2 | GCEN                                                     | ACKSTAT        | ACKDT        | ACKEN       | RCEN      | PEN    | RSEN   | SEN    | 0000 0000             | 0000 0000                          |

| 93h                    | SSPADD  | I <sup>2</sup> C Slave Address/Master Baud Rate Register |                |              |             |           |        |        |        | 0000 0000             | 0000 0000                          |

| 94h                    | SSPSTAT | SMP                                                      | CKE            | D/A          | Р           | S         | R/W    | UA     | BF     | 0000 0000             | 0000 0000                          |

## TABLE 9-3: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode.

**Note 1:** These bits are reserved on PIC16F873/876 devices; always maintain these bits clear.

2: These bits are reserved on these devices; always maintain these bits clear.

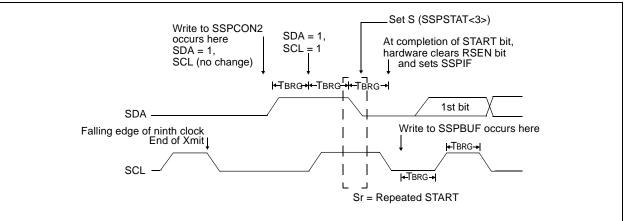

### 9.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the  $I^2C$ module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG, while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- **Note 1:** If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode), or eight bits of data (7-bit mode).

#### 9.2.10.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

**Note:** Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

#### FIGURE 9-13: REPEAT START CONDITION WAVEFORM

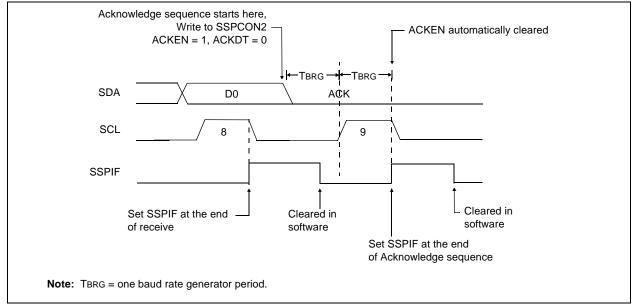

#### 9.2.13 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit is presented on the SDA pin. If the user wishes to generate an Acknowledge, the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The baud rate generator then counts for one rollover period (TBRG), and the SCL pin is de-asserted high. When the SCL pin is sampled high (clock arbitration), the baud rate generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode (Figure 9-16).

#### 9.2.13.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 9-16: ACKNOWLEDGE SEQUENCE WAVEFORM

|       | SPEN<br>bit 7                                                                                                      | RX9                                                                  |               |               |                |              |                |           |

|-------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------|---------------|----------------|--------------|----------------|-----------|

|       | bit 7                                                                                                              |                                                                      | SREN          | CREN          | ADDEN          | FERR         | OERR           | RX9D      |

|       |                                                                                                                    |                                                                      |               |               |                |              |                | bit C     |

| bit 7 | 1 = Serial p                                                                                                       | ial Port Ena<br>port enabled                                         | l (configures | RC7/RX/D      | T and RC6/T    | X/CK pins a  | as serial port | pins)     |

| bit 6 | 1 = Selects                                                                                                        | Receive Ena<br>9-bit recep<br>8-bit recep                            | tion          |               |                |              |                |           |

| bit 5 | SREN: Sin                                                                                                          | gle Receive                                                          | Enable bit    |               |                |              |                |           |

|       | Asynchron<br>Don't care                                                                                            | ous mode:                                                            |               |               |                |              |                |           |

|       | 1 = Enable<br>0 = Disable                                                                                          | <u>us mode - n</u><br>s single rec<br>es single rec<br>cleared after | eive          | s complete.   |                |              |                |           |

|       | <u>Synchrono</u><br>Don't care                                                                                     | <u>us mode - s</u>                                                   | lave:         |               |                |              |                |           |

| bit 4 | CREN: Cor                                                                                                          | ntinuous Re                                                          | ceive Enabl   | e bit         |                |              |                |           |

|       |                                                                                                                    | <u>ous mode:</u><br>s continuou<br>es continuou                      |               |               |                |              |                |           |

|       |                                                                                                                    |                                                                      |               | til enable bi | t CREN is cle  | eared (CRE   | N overrides    | SREN)     |

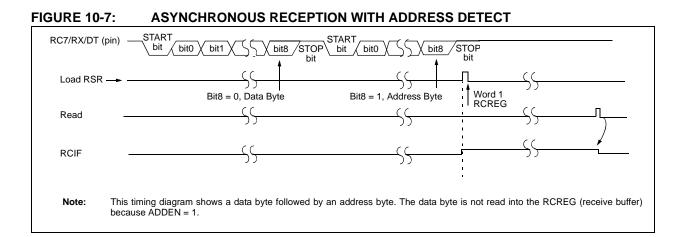

| bit 3 | ADDEN: A                                                                                                           | ddress Dete                                                          | ect Enable b  | it            |                |              |                |           |

|       | 1 = Enable<br>RSR<8                                                                                                | s address d<br>⊳ is set                                              |               | ables interru | ipt and load o |              |                |           |

| bit 2 | FERR: Fra                                                                                                          | ming Error b<br>g error (can                                         | pit           |               | RCREG regi     |              |                | 1 9       |

| bit 1 | <b>OERR</b> : Overrun Error bit<br>1 = Overrun error (can be cleared by clearing bit CREN)<br>0 = No overrun error |                                                                      |               |               |                |              |                |           |

| bit 0 | <b>RX9D:</b> 9th                                                                                                   | bit of Rece                                                          | ived Data (c  | an be parity  | bit, but mus   | t be calcula | ted by user    | firmware) |

|       | Legend:                                                                                                            |                                                                      |               |               |                |              |                |           |

|       | R = Reada                                                                                                          | ble bit                                                              | W = W         | /ritable bit  | U = Unim       | plemented    | bit, read as   | ʻ0'       |

'1' = Bit is set

'0' = Bit is cleared

## REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

- n = Value at POR

x = Bit is unknown

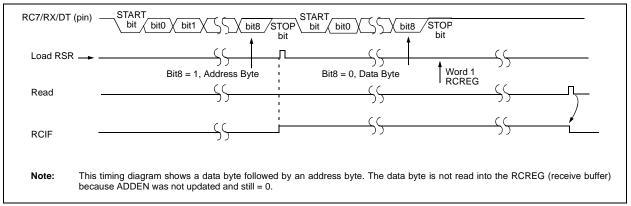

### FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6                        | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|------------------------------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                         | TOIE   | INTE  | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                         | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                          | SREN   | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART Re             | ceive Re                     | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                         | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                          | TXEN   | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Baud Rate Generator Register |        |       |       |        |        |        |                          | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

## 10.4 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 10.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes is identical, except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

When setting up a Synchronous Slave Transmission, follow these steps:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- 8. If using interrupts, ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set.

#### TABLE 10-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address                | Name   | Bit 7                | Bit 6                       | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on all<br>other<br>RESETS |

|------------------------|--------|----------------------|-----------------------------|---------|-------|-------|--------|--------|--------|-----------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE                        | TOIE    | INTE  | RBIE  | TOIF   | INTF   | R0IF   | 0000 000x             | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF                        | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000             | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9                         | SREN    | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x             | x000 0000                       |

| 19h                    | TXREG  | USART Tr             | ansmit R                    | egister |       |       |        |        |        | 0000 0000             | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE                        | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000             | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9                         | TXEN    | SYNC  | —     | BRGH   | TRMT   | TX9D   | 0000 -010             | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | aud Rate Generator Register |         |       |       |        |        |        |                       | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

NOTES:

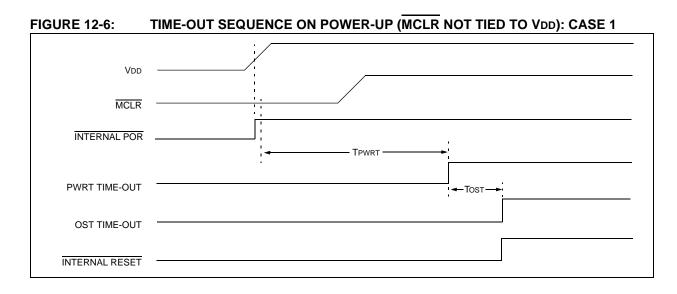

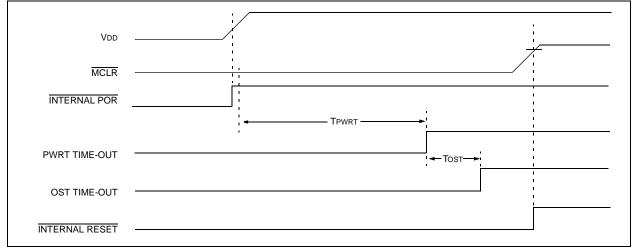

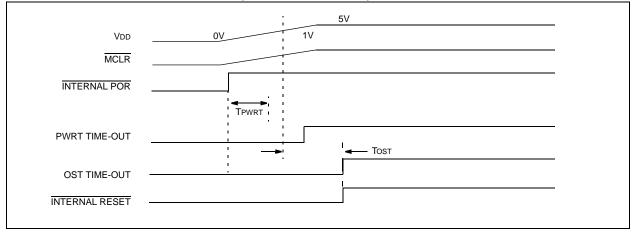

## FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

## FIGURE 12-8: SLOW RISE TIME (MCLR TIED TO VDD)

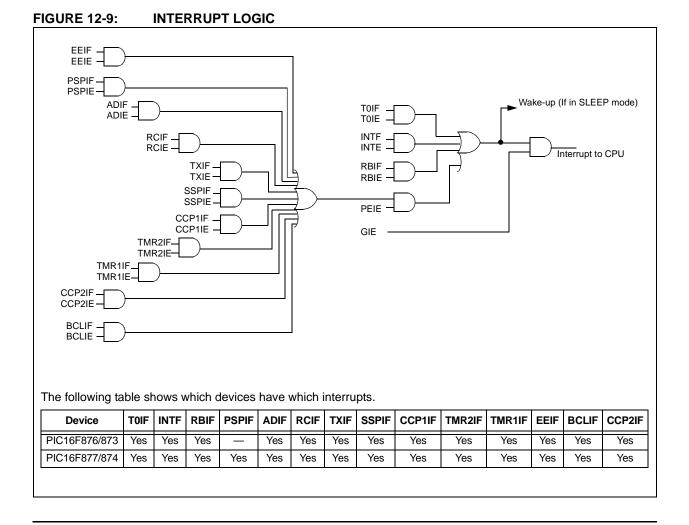

### 12.10 Interrupts

The PIC16F87X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set, regard- |

|-------|-------------------------------------------------|

|       | less of the status of their corresponding       |

|       | mask bit, or the GIE bit.                       |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set, regardless of the status of the GIE bit. The GIE bit is cleared on RESET.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt, and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers, PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers, PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit, PEIE bit, or GIE bit.

© 1998-2013 Microchip Technology Inc.

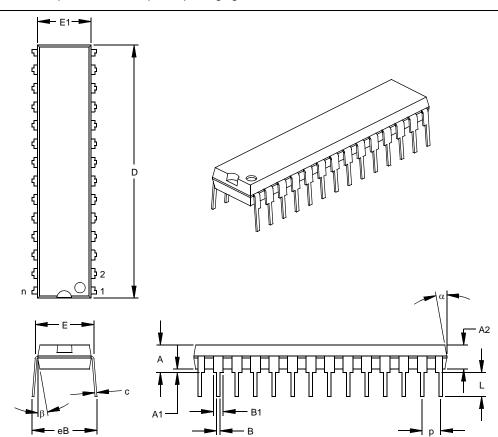

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units      | INCHES* |       | MILLIMETERS |       |       |       |

|----------------------------|------------|---------|-------|-------------|-------|-------|-------|

| Dimens                     | ion Limits | MIN     | NOM   | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n          |         | 28    |             |       | 28    |       |

| Pitch                      | р          |         | .100  |             |       | 2.54  |       |

| Top to Seating Plane       | Α          | .140    | .150  | .160        | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2         | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1         | .015    |       |             | 0.38  |       |       |

| Shoulder to Shoulder Width | E          | .300    | .310  | .325        | 7.62  | 7.87  | 8.26  |

| Molded Package Width       | E1         | .275    | .285  | .295        | 6.99  | 7.24  | 7.49  |

| Overall Length             | D          | 1.345   | 1.365 | 1.385       | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L          | .125    | .130  | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С          | .008    | .012  | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1         | .040    | .053  | .065        | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В          | .016    | .019  | .022        | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | § eB       | .320    | .350  | .430        | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α          | 5       | 10    | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β          | 5       | 10    | 15          | 5     | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

Notes:

## APPENDIX A: REVISION HISTORY

| Version | Date | Revision Description                                                                                                                                                                                                                    |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A       | 1998 | This is a new data sheet.<br>However, these devices are<br>similar to the PIC16C7X<br>devices found in the<br>PIC16C7X Data Sheet<br>(DS30390). Data Memory<br>Map for PIC16F873/874,<br>moved ADFM bit from<br>ADCON1<5> to ADCON1<7>. |

| В       | 1999 | FLASH EEPROM access<br>information.                                                                                                                                                                                                     |

| С       | 2000 | DC characteristics updated.<br>DC performance graphs<br>added.                                                                                                                                                                          |

| D       | 2013 | Added a note to each package drawing.                                                                                                                                                                                                   |

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices in this data sheet are listed in Table B-1.

| Difference             | PIC16F876/873                                             | PIC16F877/874                                               |  |

|------------------------|-----------------------------------------------------------|-------------------------------------------------------------|--|

| A/D                    | 5 channels,<br>10-bits                                    | 8 channels,<br>10-bits                                      |  |

| Parallel<br>Slave Port | no                                                        | yes                                                         |  |

| Packages               | 28-pin PDIP,<br>28-pin windowed<br>CERDIP, 28-pin<br>SOIC | 40-pin PDIP,<br>44-pin TQFP,<br>44-pin MQFP,<br>44-pin PLCC |  |

NOTES:

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12