Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f877-04e-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PIC <sup>®</sup> MCU Mid-Range Reference<br>Manual (DS33023) | PIC16F873               | PIC16F874               | PIC16F876               | PIC16F877               |

|------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Operating Frequency                                                          | DC - 20 MHz             |

| RESETS (and Delays)                                                          | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) | POR, BOR<br>(PWRT, OST) |

| FLASH Program Memory<br>(14-bit words)                                       | 4K                      | 4K                      | 8K                      | 8K                      |

| Data Memory (bytes)                                                          | 192                     | 192                     | 368                     | 368                     |

| EEPROM Data Memory                                                           | 128                     | 128                     | 256                     | 256                     |

| Interrupts                                                                   | 13                      | 14                      | 13                      | 14                      |

| I/O Ports                                                                    | Ports A,B,C             | Ports A,B,C,D,E         | Ports A,B,C             | Ports A,B,C,D,E         |

| Timers                                                                       | 3                       | 3                       | 3                       | 3                       |

| Capture/Compare/PWM Modules                                                  | 2                       | 2                       | 2                       | 2                       |

| Serial Communications                                                        | MSSP, USART             | MSSP, USART             | MSSP, USART             | MSSP, USART             |

| Parallel Communications                                                      | —                       | PSP                     | —                       | PSP                     |

| 10-bit Analog-to-Digital Module                                              | 5 input channels        | 8 input channels        | 5 input channels        | 8 input channels        |

| Instruction Set                                                              | 35 instructions         | 35 instructions         | 35 instructions         | 35 instructions         |

| TABLE 1-2: PIC16F874 AND PIC16F877 PINOUT DESCRIPTION |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin Name          | DIP<br>Pin#    | PLCC<br>Pin#      | QFP<br>Pin# | I/O/P<br>Type        | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|----------------|-------------------|-------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13             | 14                | 30          | I                    | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14             | 15                | 31          | 0                    | —                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1              | 2                 | 18          | I/P                  | ST                     | Master Clear (Reset) input or programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                        |

|                   |                |                   |             |                      |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2              | 3                 | 19          | I/O                  | TTL                    | RA0 can also be analog input0.                                                                                                                                                                                    |

| RA1/AN1           | 3              | 4                 | 20          | I/O                  | TTL                    | RA1 can also be analog input1.                                                                                                                                                                                    |

| RA2/AN2/VREF-     | 4              | 5                 | 21          | I/O                  | TTL                    | RA2 can also be analog input2 or negative analog reference voltage.                                                                                                                                               |

| RA3/AN3/VREF+     | 5              | 6                 | 22          | I/O                  | TTL                    | RA3 can also be analog input3 or positive<br>analog reference voltage.                                                                                                                                            |

| RA4/T0CKI         | 6              | 7                 | 23          | I/O                  | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                          |

| RA5/SS/AN4        | 7              | 8                 | 24          | I/O                  | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                                |

|                   |                |                   |             |                      |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33             | 36                | 8           | I/O                  | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1               | 34             | 37                | 9           | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB2               | 35             | 38                | 10          | I/O                  | TTL                    |                                                                                                                                                                                                                   |

| RB3/PGM           | 36             | 39                | 11          | I/O                  | TTL                    | RB3 can also be the low voltage programming input.                                                                                                                                                                |

| RB4               | 37             | 41                | 14          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB5               | 38             | 42                | 15          | I/O                  | TTL                    | Interrupt-on-change pin.                                                                                                                                                                                          |

| RB6/PGC           | 39             | 43                | 16          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming clock.                                                                                                                                  |

| RB7/PGD           | 40             | 44                | 17          | I/O                  | TTL/ST <sup>(2)</sup>  | Interrupt-on-change pin or In-Circuit Debugger pin.<br>Serial programming data.                                                                                                                                   |

| Legend: I = input | 0 = 0<br>— = N | utput<br>lot used |             | I/O = inp<br>TTL = T | out/output<br>TL input | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| FI | GU | IRF | 2-3      | - |

|----|----|-----|----------|---|

|    |    |     | <u> </u> |   |

### PIC16F877/876 REGISTER FILE MAP

| Indirect addr.(*)              | 00h        | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 18              |

|--------------------------------|------------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|-----------------|

| TMR0                           | 01h        | OPTION_REG                                 | 81h        | TMR0                                       | 101h         | OPTION_REG                                 | 18              |

| PCL                            | 02h        | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182             |

| STATUS                         | 03h        | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183             |

| FSR                            | 04h        | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184             |

| PORTA                          | 05h        | TRISA                                      | 85h        |                                            | 105h         |                                            | 18              |

| PORTB                          | 06h        | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186             |

| PORTC                          | 07h        | TRISC                                      | 87h        |                                            | 107h         |                                            | 187             |

| PORTD <sup>(1)</sup>           | 08h        | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188             |

| PORTE <sup>(1)</sup>           | 09h        | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h         |                                            | 189             |

| PCLATH                         | 0Ah        | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18/             |

| INTCON                         | 0Bh        | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18              |

| PIR1                           | 0Ch        | PIE1                                       | 8Ch        | EEDATA                                     | 10Ch         | EECON1                                     | 180             |

| PIR2                           | 0Dh        | PIE2                                       | 8Dh        | EEADR                                      | 10Dh         | EECON2                                     | 181             |

| TMR1L                          | 0Eh        | PCON                                       | 8Eh        | EEDATH                                     | 10Eh         | Reserved <sup>(2)</sup>                    | 18              |

| TMR1H                          | 0Fh        |                                            | 8Fh        | EEADRH                                     | 10Fh         | Reserved <sup>(2)</sup>                    | 18              |

| T1CON                          | 10h        |                                            | 90h        |                                            | 110h         |                                            | 190             |

| TMR2                           | 11h        | SSPCON2                                    | 91h        |                                            | 111h         |                                            | 19 <sup>.</sup> |

| T2CON                          | 12h        | PR2                                        | 92h        |                                            | 112h         |                                            | 192             |

| SSPBUF                         | 13h        | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193             |

| SSPCON                         | 14h        | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194             |

| CCPR1L                         | 15h        |                                            | 95h        |                                            | 115h         |                                            | 19              |

| CCPR1H                         | 16h        |                                            | 96h        |                                            | 116h         |                                            | 196             |

| CCP1CON                        | 17h        |                                            | 97h        | General                                    | 117h         | General                                    | 197             |

| RCSTA                          | 18h        | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198             |

| TXREG                          | 19h        | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199             |

| RCREG                          | 1Ah        |                                            | 9Ah        | -                                          | 11Ah         |                                            | 19/             |

| CCPR2L                         | 1Bh        |                                            | 9Bh        |                                            | 11Bh         |                                            | 198             |

| CCPR2H                         | 1Ch        |                                            | 9Ch        |                                            | 11Ch         |                                            | 190             |

| CCP2CON                        | 1Dh        |                                            | 9Dh        |                                            | 11Dh         |                                            | 19[             |

| ADRESH                         | 1Eh        | ADRESL                                     | 9Eh        |                                            | 11Eh         |                                            | 19              |

| ADCON0                         | 1Fh        | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 191             |

|                                | 20h        |                                            | A0h        |                                            | 120h         |                                            | 1A              |

| General<br>Purpose<br>Register |            | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |              | General<br>Purpose<br>Register<br>80 Bytes |                 |

| 96 Bytes                       |            | UU Dyico                                   | EFh        | 00 Dytos                                   | 16Fh         | 00 Dyi00                                   | 1EI             |

|                                | 7Fh        | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | 1F(<br>1Fl      |

| Bank 0                         |            | Bank 1                                     | FFII       | Bank 2                                     | /. !!        | Bank 3                                     | 11.1            |

| 1 1 m 1 m 1                    | بارار منعم | a memory location                          | a          |                                            |              |                                            |                 |

2: These registers are reserved, maintain these registers clear.

# 4.0 DATA EEPROM AND FLASH PROGRAM MEMORY

The Data EEPROM and FLASH Program Memory are readable and writable during normal operation over the entire VDD range. These operations take place on a single byte for Data EEPROM memory and a single word for Program memory. A write operation causes an erase-then-write operation to take place on the specified byte or word. A bulk erase operation may not be issued from user code (which includes removing code protection).

Access to program memory allows for checksum calculation. The values written to program memory do not need to be valid instructions. Therefore, up to 14-bit numbers can be stored in memory for use as calibration parameters, serial numbers, packed 7-bit ASCII, etc. Executing a program memory location containing data that form an invalid instruction, results in the execution of a NOP instruction.

The EEPROM Data memory is rated for high erase/ write cycles (specification D120). The FLASH program memory is rated much lower (specification D130), because EEPROM data memory can be used to store frequently updated values. An on-chip timer controls the write time and it will vary with voltage and temperature, as well as from chip to chip. Please refer to the specifications for exact limits (specifications D122 and D133).

A byte or word write automatically erases the location and writes the new value (erase before write). Writing to EEPROM data memory does not impact the operation of the device. Writing to program memory will cease the execution of instructions until the write is complete. The program memory cannot be accessed during the write. During the write operation, the oscillator continues to run, the peripherals continue to function and interrupt events will be detected and essentially "queued" until the write is complete. When the write completes, the next instruction in the pipeline is executed and the branch to the interrupt vector will take place, if the interrupt is enabled and occurred during the write.

Read and write access to both memories take place indirectly through a set of Special Function Registers (SFR). The six SFRs used are:

- EEDATA

- EEDATH

- EEADR

- EEADRH

- EECON1

- EECON2

The EEPROM data memory allows byte read and write operations without interfering with the normal operation of the microcontroller. When interfacing to EEPROM data memory, the EEADR register holds the address to be accessed. Depending on the operation, the EEDATA register holds the data to be written, or the data read, at the address in EEADR. The PIC16F873/874 devices have 128 bytes of EEPROM data memory and therefore, require that the MSb of EEADR remain clear. The EEPROM data memory on these devices do not wrap around to 0, i.e., 0x80 in the EEADR does not map to 0x00. The PIC16F876/877 devices have 256 bytes of EEPROM data memory and therefore, uses all 8-bits of the EEADR.

The FLASH program memory allows non-intrusive read access, but write operations cause the device to stop executing instructions, until the write completes. When interfacing to the program memory, the EEADRH:EEADR registers form a two-byte word, which holds the 13-bit address of the memory location being accessed. The register combination of EEDATH:EEDATA holds the 14-bit data for writes, or reflects the value of program memory after a read operation. Just as in EEPROM data memory accesses, the value of the EEADRH:EEADR registers must be within the valid range of program memory, depending on the device: 0000h to 1FFFh for the PIC16F873/874. or 0000h to 3FFFh for the PIC16F876/877. Addresses outside of this range do not wrap around to 0000h (i.e., 4000h does not map to 0000h on the PIC16F877).

# 4.1 EECON1 and EECON2 Registers

The EECON1 register is the control register for configuring and initiating the access. The EECON2 register is not a physically implemented register, but is used exclusively in the memory write sequence to prevent inadvertent writes.

There are many bits used to control the read and write operations to EEPROM data and FLASH program memory. The EEPGD bit determines if the access will be a program or data memory access. When clear, any subsequent operations will work on the EEPROM data memory. When set, all subsequent operations will operate in the program memory.

Read operations only use one additional bit, RD, which initiates the read operation from the desired memory location. Once this bit is set, the value of the desired memory location will be available in the data registers. This bit cannot be cleared by firmware. It is automatically cleared at the end of the read operation. For EEPROM data memory reads, the data will be available in the EEDATA register in the very next instruction cycle after the RD bit is set. For program memory reads, the data will be loaded into the EEDATH:EEDATA registers, following the second instruction after the RD bit is set.

#### 4.4 Reading the FLASH Program Memory

Reading FLASH program memory is much like that of EEPROM data memory, only two NOP instructions must be inserted after the RD bit is set. These two instruction cycles that the NOP instructions execute, will be used by the microcontroller to read the data out of program the memory and insert value into the EEDATH:EEDATA registers. Data will be available following the second NOP instruction. EEDATH and EEDATA will hold their value until another read operation is initiated, or until they are written by firmware.

The steps to reading the FLASH program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Set the EEPGD bit to point to FLASH program memory.

- 3. Set the RD bit to start the read operation.

- 4. Execute two NOP instructions to allow the microcontroller to read out of program memory.

- 5. Read the data from the EEDATH:EEDATA registers.

#### EXAMPLE 4-3: FLASH PROGRAM READ

| BSF   | STATUS, RP1   | ;                        |

|-------|---------------|--------------------------|

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | ADDRL, W      | ;Write the               |

| MOVWF | EEADR         | ;address bytes           |

| MOVF  | ADDRH,W       | ;for the desired         |

| MOVWF | EEADRH        | ;address to read         |

| BSF   | STATUS, RPO   | ;Bank 3                  |

| BSF   | EECON1, EEPGD | ;Point to Program memory |

| BSF   | EECON1, RD    | ;Start read operation    |

| NOP   |               | ;Required two NOPs       |

| NOP   |               | ;                        |

| BCF   | STATUS, RPO   | ;Bank 2                  |

| MOVF  | EEDATA, W     | ;DATAL = EEDATA          |

| MOVWF | DATAL         | ;                        |

| MOVF  | EEDATH,W      | ;DATAH = EEDATH          |

| MOVWF | DATAH         | ;                        |

|       |               |                          |

## 4.5 Writing to the FLASH Program Memory

Writing to FLASH program memory is unique, in that the microcontroller does not execute instructions while programming is taking place. The oscillator continues to run and all peripherals continue to operate and queue interrupts, if enabled. Once the write operation completes (specification D133), the processor begins executing code from where it left off. The other important difference when writing to FLASH program memory, is that the WRT configuration bit, when clear, prevents any writes to program memory (see Table 4-1).

Just like EEPROM data memory, there are many steps in writing to the FLASH program memory. Both address and data values must be written to the SFRs. The EEPGD bit must be set, and the WREN bit must be set to enable writes. The WREN bit should be kept clear at all times, except when writing to the FLASH Program memory. The WR bit can only be set if the WREN bit was set in a previous operation, i.e., they both cannot be set in the same operation. The WREN bit should then be cleared by firmware after the write. Clearing the WREN bit before the write actually completes will not terminate the write in progress.

Writes to program memory must also be prefaced with a special sequence of instructions that prevent inadvertent write operations. This is a sequence of five instructions that must be executed without interruption for each byte written. These instructions must then be followed by two NOP instructions to allow the microcontroller to setup for the write operation. Once the write is complete, the execution of instructions starts with the instruction after the second NOP.

The steps to write to program memory are:

- 1. Write the address to EEADRH:EEADR. Make sure that the address is not larger than the memory size of the PIC16F87X device.

- 2. Write the 14-bit data value to be programmed in the EEDATH:EEDATA registers.

- 3. Set the EEPGD bit to point to FLASH program memory.

- 4. Set the WREN bit to enable program operations.

- 5. Disable interrupts (if enabled).

- 6. Execute the special five instruction sequence:

- Write 55h to EECON2 in two steps (first to W, then to EECON2)

- Write AAh to EECON2 in two steps (first to W, then to EECON2)

- Set the WR bit

- 7. Execute two NOP instructions to allow the microcontroller to setup for write operation.

- 8. Enable interrupts (if using interrupts).

- 9. Clear the WREN bit to disable program operations.

#### 5.2 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of TOCKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

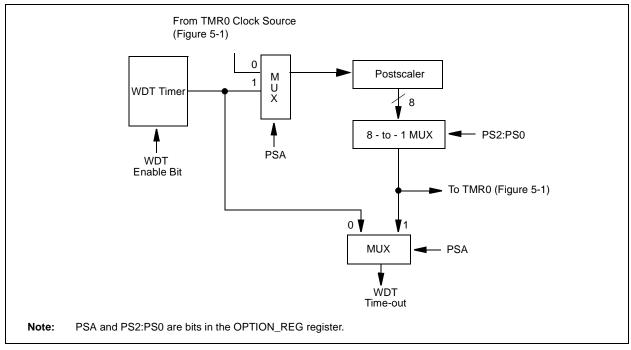

#### 5.3 Prescaler

There is only one prescaler available, which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. A prescaler assignment for the

**REGISTER 5-1: OPTION REG REGISTER**

DANA

Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. This prescaler is not readable or writable (see Figure 5-1).

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF1, MOVWF1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0, when the prescaler is assigned to Timer0, will clear the prescaler count, but will not change the prescaler assignment.

|               | R/W-1                                                                                                                                                                                                                                                                                           | R/W-1                                                       | R/W-1                                                                     | R/W-1         | R/W-1          | R/W-1     | R/W-1          | R/W-1  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|---------------|----------------|-----------|----------------|--------|--|--|

|               | RBPU                                                                                                                                                                                                                                                                                            | INTEDG                                                      | T0CS                                                                      | TOSE          | PSA            | PS2       | PS1            | PS0    |  |  |

|               | bit 7                                                                                                                                                                                                                                                                                           |                                                             |                                                                           |               |                |           |                | bit 0  |  |  |

|               |                                                                                                                                                                                                                                                                                                 |                                                             |                                                                           |               |                |           |                |        |  |  |

| bit 7         | RBPU                                                                                                                                                                                                                                                                                            |                                                             |                                                                           |               |                |           |                |        |  |  |

| bit 6         | INTEDG                                                                                                                                                                                                                                                                                          |                                                             |                                                                           |               |                |           |                |        |  |  |

| bit 5         | 1 = Transit                                                                                                                                                                                                                                                                                     | R0 Clock Sou<br>tion on T0CK<br>al instruction o            | l pin                                                                     |               |                |           |                |        |  |  |

| bit 4         | 1 = Increm                                                                                                                                                                                                                                                                                      | R0 Source Ed<br>nent on high-t<br>nent on low-to            | o-low trans                                                               | sition on TOC | •              |           |                |        |  |  |

| bit 3         | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                                                                                                                                         |                                                             |                                                                           |               |                |           |                |        |  |  |

| bit 2-0       | PS2:PS0:                                                                                                                                                                                                                                                                                        | Prescaler Ra                                                | ite Select b                                                              | oits          |                |           |                |        |  |  |

|               | Bit Value                                                                                                                                                                                                                                                                                       | TMR0 Rate                                                   | WDT Rat                                                                   | e             |                |           |                |        |  |  |

|               | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                                                                                                                                                            | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 | -             |                |           |                |        |  |  |

|               | Legend:                                                                                                                                                                                                                                                                                         |                                                             |                                                                           |               |                |           |                |        |  |  |

|               | R = Reada                                                                                                                                                                                                                                                                                       | able bit                                                    | VV = V                                                                    | Vritable bit  | U = Unimple    | emented b | it, read as '( | )'     |  |  |

|               | - n = Value                                                                                                                                                                                                                                                                                     | e at POR                                                    | '1' = E                                                                   | Bit is set    | '0' = Bit is c | leared    | x = Bit is ur  | nknown |  |  |

|               |                                                                                                                                                                                                                                                                                                 |                                                             |                                                                           |               |                |           |                |        |  |  |

| ily Reference | To avoid an unintended device RESET, the instruction sequence shown in the PIC <sup>®</sup> MCU Mid-Range Fam-<br>ily Reference Manual (DS33023) must be executed when changing the prescaler assignment from Timer0<br>to the WDT. This sequence must be followed even if the WDT is disabled. |                                                             |                                                                           |               |                |           |                |        |  |  |

Note:

# PIC16F87X

| REGISTER 0-1: | CUPICON                                                                                                                        | CCPICON REGISTER/CCP2CON REGISTER (ADDRESS: 1717/101)                                                                                        |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|------------|--|--|--|--|

|               | U-0                                                                                                                            | U-0                                                                                                                                          | R/W-0                                                                                                                             | R/W-0                                                                                                               | R/W-0                                                                                             | R/W-0                                         | R/W-0         | R/W-0      |  |  |  |  |

|               | —                                                                                                                              | _                                                                                                                                            | CCPxX                                                                                                                             | CCPxY                                                                                                               | CCPxM3                                                                                            | CCPxM2                                        | CCPxM1        | CCPxM0     |  |  |  |  |

|               | bit 7                                                                                                                          |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               | bit 0      |  |  |  |  |

|               |                                                                                                                                |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

| bit 7-6       | Unimplem                                                                                                                       |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

| bit 5-4       |                                                                                                                                | CCPxX:CCPxY: PWM Least Significant bits                                                                                                      |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

|               | <u>Capture m</u><br>Unused                                                                                                     | <u>Capture mode</u> :<br>Unused                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

|               | <u>Compare mode:</u><br>Unused                                                                                                 |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

|               | PWM mode:<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR                               |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

| bit 3-0       | CCPxM3:C                                                                                                                       | CPxM0: C                                                                                                                                     | CPx Mode S                                                                                                                        | Select bits                                                                                                         |                                                                                                   |                                               |               |            |  |  |  |  |

|               | 0100 = Ca<br>0101 = Ca<br>0110 = Ca<br>0111 = Ca<br>1000 = Co<br>1001 = Co<br>1010 = Co<br>1011 = Co<br>1011 = Co<br>1011 = Co | pture mode<br>pture mode<br>pture mode<br>mpare mod<br>mpare mod<br>affected)<br>mpare mod<br>affected)<br>mpare mode<br>ets TMR1;<br>abled) | , every fallir<br>, every risin<br>, every 4th r<br>, every 16th<br>e, set outpu<br>e, clear outp<br>e, generate<br>e, trigger sp | ng edge<br>g edge<br>rising edge<br>t rising edge<br>t on match (<br>out on match<br>software int<br>ecial event (0 | ets CCPx mod<br>CCPxIF bit is<br>(CCPxIF bit<br>errupt on mat<br>CCPxIF bit is s<br>starts an A/D | set)<br>is set)<br>ch (CCPxIF<br>set, CCPx pi | in is unaffec | ted); CCP1 |  |  |  |  |

|               | Legend:                                                                                                                        |                                                                                                                                              |                                                                                                                                   |                                                                                                                     |                                                                                                   |                                               |               |            |  |  |  |  |

|               | R = Reada                                                                                                                      | ble bit                                                                                                                                      | VV = V                                                                                                                            | Vritable bit                                                                                                        | U = Unim                                                                                          | plemented l                                   | bit, read as  | ʻ0'        |  |  |  |  |

'1' = Bit is set

- n = Value at POR

# REGISTER 8-1: CCP1CON REGISTER/CCP2CON REGISTER (ADDRESS: 17h/1Dh)

x = Bit is unknown

'0' = Bit is cleared

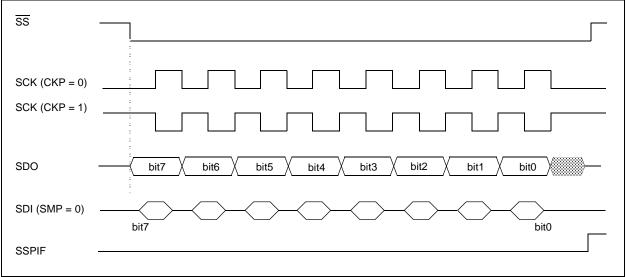

#### 9.1.2 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the interrupt flag bit SSPIF (PIR1<3>) is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications. While in SLEEP mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from SLEEP.

- Note 1: When the <u>SPI</u> module is in Slave mode with <u>SS</u> pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the <u>SS</u> pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE = '1', then SS pin control must be enabled.

# SCK (CKP = 0) SCK (CKP = 1) SD0 SD0 SD1 (SMP = 0) B17 SD1 SD1

#### FIGURE 9-3: SPI MODE TIMING (SLAVE MODE WITH CKE = 0)

# PIC16F87X

|       | SPEN<br>bit 7                       | RX9                                                                  |                   |               |                |              |                |           |  |

|-------|-------------------------------------|----------------------------------------------------------------------|-------------------|---------------|----------------|--------------|----------------|-----------|--|

|       | hit 7                               |                                                                      | SREN              | CREN          | ADDEN          | FERR         | OERR           | RX9D      |  |

|       |                                     |                                                                      |                   |               |                |              |                | bit C     |  |

| bit 7 | 1 = Serial p                        | ial Port Ena<br>port enabled                                         | l (configures     | RC7/RX/D      | T and RC6/T    | X/CK pins a  | as serial port | pins)     |  |

| bit 6 | 1 = Selects                         | Receive Ena<br>9-bit recep<br>8-bit recep                            | tion              |               |                |              |                |           |  |

| bit 5 | SREN: Sin                           | gle Receive                                                          | Enable bit        |               |                |              |                |           |  |

|       | Asynchron<br>Don't care             | ous mode:                                                            |                   |               |                |              |                |           |  |

|       | 1 = Enable<br>0 = Disable           | <u>us mode - n</u><br>s single rec<br>es single rec<br>cleared after | eive              | s complete.   |                |              |                |           |  |

|       | <u>Synchrono</u><br>Don't care      | <u>us mode - s</u>                                                   | lave:             |               |                |              |                |           |  |

| bit 4 | CREN: Continuous Receive Enable bit |                                                                      |                   |               |                |              |                |           |  |

|       |                                     | <u>ous mode:</u><br>s continuou<br>es continuou                      |                   |               |                |              |                |           |  |

|       |                                     |                                                                      |                   | til enable bi | t CREN is cle  | eared (CRE   | N overrides    | SREN)     |  |

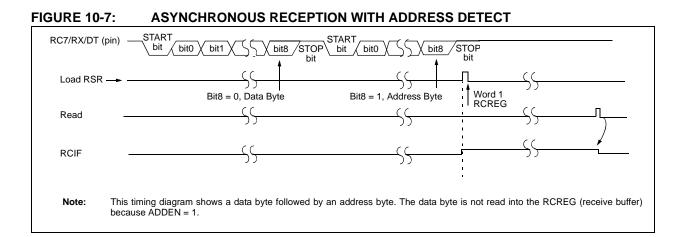

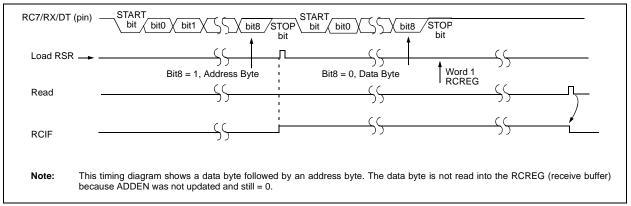

| bit 3 | ADDEN: A                            | ddress Dete                                                          | ect Enable b      | it            |                |              |                |           |  |

|       | 1 = Enable<br>RSR<8                 | s address d<br>⊳ is set                                              |                   | ables interru | ipt and load o |              |                |           |  |

| bit 2 | FERR: Fra                           | ming Error b<br>g error (can                                         | pit               |               | RCREG regi     |              |                | 1 9       |  |

| bit 1 |                                     | -                                                                    | bit<br>be cleared | by clearing   | bit CREN)      |              |                |           |  |

| bit 0 | <b>RX9D:</b> 9th                    | bit of Rece                                                          | ived Data (c      | an be parity  | bit, but mus   | t be calcula | ted by user    | firmware) |  |

|       | Legend:                             |                                                                      |                   |               |                |              |                |           |  |

|       | R = Reada                           | ble bit                                                              | W = W             | /ritable bit  | U = Unim       | plemented    | bit, read as   | ʻ0'       |  |

'1' = Bit is set

'0' = Bit is cleared

# REGISTER 10-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

- n = Value at POR

x = Bit is unknown

#### 10.2 USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one START bit, eight or nine data bits, and one STOP bit). The most common data format is 8-bits. An on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The transmitter and receiver are functionally independent, but use the same data format and baud rate. The baud rate generator produces a clock, either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

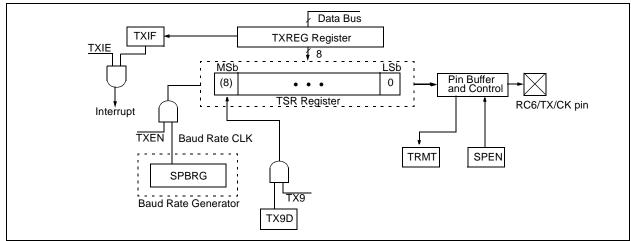

#### 10.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 10-1. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory, so it is not available to the user.

- 2: Flag bit TXIF is set when enable bit TXEN is set. TXIF is cleared by loading TXREG.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally, when transmission is first started, the TSR register is empty. At that point, transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 10-3). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit may be loaded in the TSR register.

#### FIGURE 10-1: USART TRANSMIT BLOCK DIAGRAM

#### FIGURE 10-8: ASYNCHRONOUS RECEPTION WITH ADDRESS BYTE FIRST

#### TABLE 10-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address                | Name   | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>RESETS |

|------------------------|--------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE     | TOIE      | INTE      | RBIE  | TOIF   | INTF   | R0IF   | x000 0000x               | 0000 000u                       |

| 0Ch                    | PIR1   | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h                    | RCSTA  | SPEN                 | RX9      | SREN      | CREN      | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 1Ah                    | RCREG  | USART Re             | ceive Re | gister    |           |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch                    | PIE1   | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h                    | TXSTA  | CSRC                 | TX9      | TXEN      | SYNC      | —     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h                    | SPBRG  | Baud Rate            | Generato | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception. Note 1: Bits PSPIE and PSPIF are reserved on PIC16F873/876 devices; always maintain these bits clear.

# 12.0 SPECIAL FEATURES OF THE CPU

All PIC16F87X devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code Protection

- ID Locations

- In-Circuit Serial Programming

- Low Voltage In-Circuit Serial Programming

- In-Circuit Debugger

PIC16F87X devices have a Watchdog Timer, which can be shut-off only through configuration bits. It runs off its own RC oscillator for added reliability.

There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only. It is designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry. SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer Wake-up, or through an interrupt.

Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

Additional information on special features is available in the  $PIC^{\mathbb{R}}$  MCU Mid-Range Reference Manual, (DS33023).

#### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. The erased, or unprogrammed value of the configuration word is 3FFFh. These bits are mapped in program memory location 2007h.

It is important to note that address 2007h is beyond the user program memory space, which can be accessed only during programming.

### 12.12 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/ CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

The WDT can be permanently disabled by clearing configuration bit WDTE (Section 12.1).

WDT time-out period values may be found in the Electrical Specifications section under parameter #31. Values for the WDT prescaler (actually a postscaler, but shared with the Timer0 prescaler) may be assigned using the OPTION\_REG register.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

- 2: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

#### FIGURE 12-10: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION_REG   | RBPU  | INTEDG               | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer. **Note 1:** See Register 12-1 for operation of these bits.

#### 12.17 In-Circuit Serial Programming

PIC16F87X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware to be programmed.

When using ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect, both from an onstate to off-state. For all other cases of ICSP, the part may be programmed at the normal operating voltages. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

For complete details of serial programming, please refer to the EEPROM Memory Programming Specification for the PIC16F87X (DS39025).

#### 12.18 Low Voltage ICSP Programming

The LVP bit of the configuration word enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB3/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR pin. To enter Programming mode, VDD must be applied to the RB3/PGM, provided the LVP bit is set. The LVP bit defaults to on ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in Low Voltage ICSP mode, the RB3 pin can no longer be used as a general purpose I/O pin.

- 3: When using low voltage ICSP programming (LVP) and the pull-ups on PORTB are enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3 and ensure the proper operation of the device.

- 4: RB3 should not be allowed to float if LVP is enabled. An external pull-down device should be used to default the device to normal operating mode. If RB3 floats high, the PIC16F87X device will enter Programming mode.

- LVP mode is enabled by default on all devices shipped from Microchip. It can be disabled by clearing the LVP bit in the CONFIG register.

- 6: Disabling LVP will provide maximum compatibility to other PIC16CXXX devices.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB3/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR. The LVP bit can only be charged when using high voltage on MCLR.

It should be noted, that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied at 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means calibration values, unique user IDs, or user code can be reprogrammed or added.

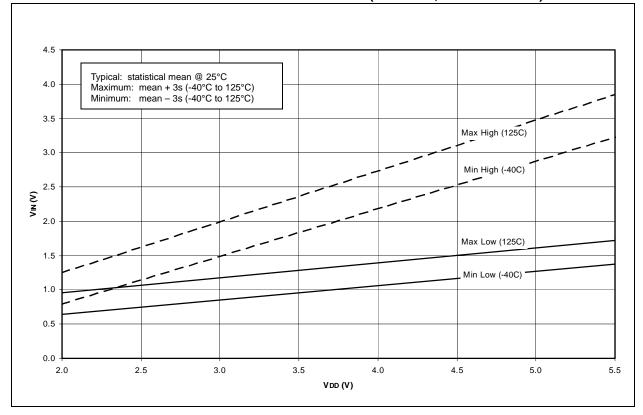

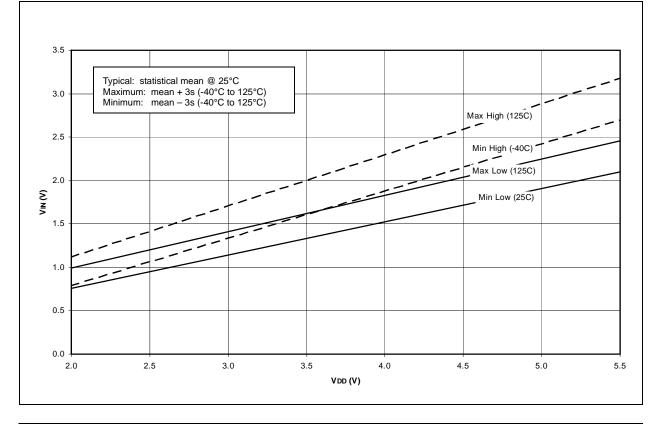

#### 15.2 DC Characteristics: PIC16F873/874/876/877-04 (Commercial, Industrial) PIC16F873/874/876/877-20 (Commercial, Industrial) PIC16LF873/874/876/877-04 (Commercial, Industrial) (Continued)

| DC CHA       | RACTEF | RISTICS                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $0^{\circ}C \le TA \le +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC specification(Section 15.1) |      |     |       |                                                                        |

|--------------|--------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                             | Min                                                                                                                                                                                                                                                              | Тур† | Max | Units | Conditions                                                             |

|              | Vol    | Output Low Voltage                         |                                                                                                                                                                                                                                                                  |      |     |       |                                                                        |

| D080         |        | I/O ports                                  |                                                                                                                                                                                                                                                                  |      | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

| D083         |        | OSC2/CLKOUT (RC osc config)                | —                                                                                                                                                                                                                                                                | —    | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                            |

|              | Voh    | Output High Voltage                        |                                                                                                                                                                                                                                                                  |      |     |       |                                                                        |

| D090         |        | I/O ports <sup>(3)</sup>                   | Vdd - 0.7                                                                                                                                                                                                                                                        |      | _   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                           |

| D092         |        | OSC2/CLKOUT (RC osc config)                | Vdd - 0.7                                                                                                                                                                                                                                                        | _    | —   | V     | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                           |

| D150*        | Vod    | Open-Drain High Voltage                    |                                                                                                                                                                                                                                                                  | _    | 8.5 | V     | RA4 pin                                                                |

|              |        | Capacitive Loading Specs on<br>Output Pins |                                                                                                                                                                                                                                                                  |      |     |       |                                                                        |